CMOS 32-BIT SINGLE CHIP MICROCOMPUTER

# E0C33208/204/202 TECHNICAL MANUAL

E0C33208/204/202 Technical Hardware E0C33 Family ASIC Macro Manual

# E0C33208/204/202 Technical Manual

This manual describes the hardware specifications of the Seiko Epson original 32-bit microcomputers E0C33208, E0C33204 and E0C33202.

#### E0C33208/204/202 Technical Hardware

Describes the hardware specifications of the E0C33208/204/202 except for details of the peripheral circuits.

### **E0C33 Family ASIC Macro Manual**

Describes details of all the peripheral circuit blocks for the E0C33 Family microcomputers.

Refer to the "E0C33 000 Core CPU Manual" for details of the E0C330 00 32-bit RISC CPU .

# E0C33208/204/202 Technical Hardware

### **Table of Contents**

| 1 Oı | Outline                                        |    |

|------|------------------------------------------------|----|

|      | 1.1 Features                                   | 1  |

|      | 1.2 Block Diagram                              | 3  |

|      | 1.3 Pin Description                            |    |

|      | 1.3.1 Pin Layout Diagram (plastic package)     |    |

|      | 1.3.2 Pin Functions                            | 6  |

| 2 Pc | ower Supply                                    | 12 |

|      | 2.1 Power Supply Pins                          | 12 |

|      | 2.2 Operating Voltage (VDD)                    | 12 |

|      | 2.3 Power Supply for I/O Interface (VDDE)      | 12 |

|      | 2.4 Power Supply for Analog Circuits (AVDDE)   | 13 |

| 3 In | nternal Memory                                 | 14 |

| •    | 3.1 RAM                                        |    |

|      | 3.2 ROM and Boot Address                       |    |

| 4.5  |                                                |    |

| 4 P  | eripheral Circuits                             |    |

|      | 4.1 List of Peripheral Circuits                |    |

|      | 4.2 I/O Memory Map                             | 16 |

| 5 Pc | ower-Down Control                              | 57 |

| 6 Ba | asic External Wiring Diagram                   | 59 |

| 7 Pr | recautions On Mounting                         | 60 |

| 8 EI | lectrical Characteristics                      | 62 |

|      | 8.1 Absolute Maximum Rating                    | 62 |

|      | 8.2 Recommended Operating Conditions           |    |

|      | 8.3 DC Characteristics                         | 64 |

|      | 8.4 Current Consumption                        | 66 |

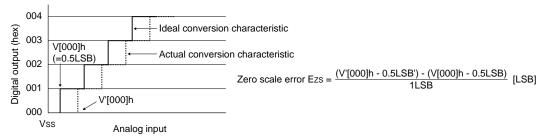

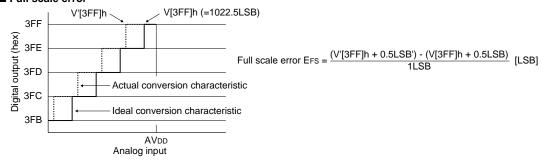

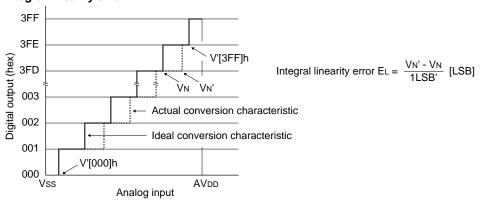

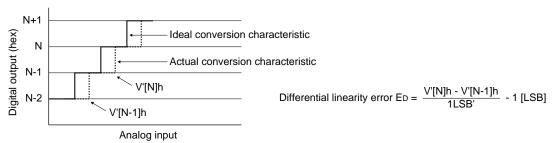

|      | 8.5 A/D Converter Characteristics              | 67 |

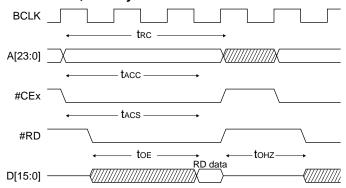

|      | 8.6 AC Characteristics                         | 69 |

|      | 8.6.1 Symbol Description                       |    |

|      | 8.6.2 AC Characteristics Measurement Condition |    |

|      | 8.6.3 AC Characteristic Tables                 |    |

|      | 8.7 Oscillation Characteristics                |    |

|      | 8.8 PLL Characteristics                        |    |

|      |                                                |    |

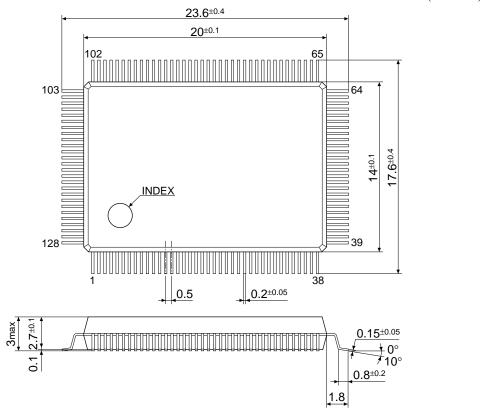

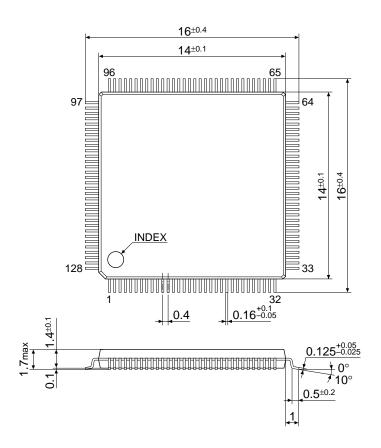

| 9 Pa | ackage                                         |    |

|      | 9.1 Plastic Package                            | 87 |

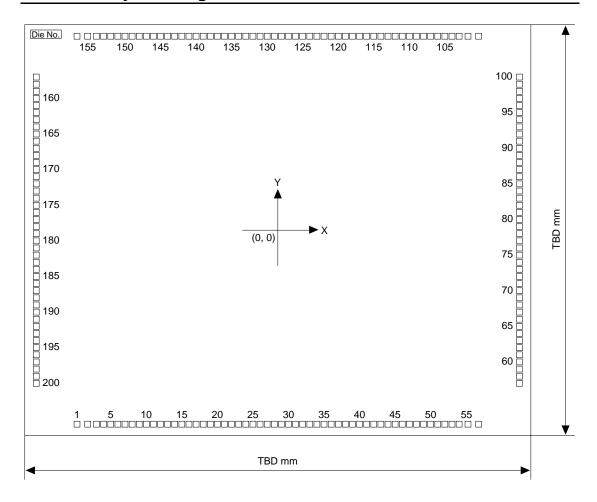

| 10 F | Pad Layout                                     | 89 |

|      | 10.1 Pad Layout Diagram                        | 89 |

|      | 10.2 Pad Coordinate                            | 90 |

#### **TABLE OF CONTENTS**

| Appendix A <reference> External Device Interface Timings</reference> |     |

|----------------------------------------------------------------------|-----|

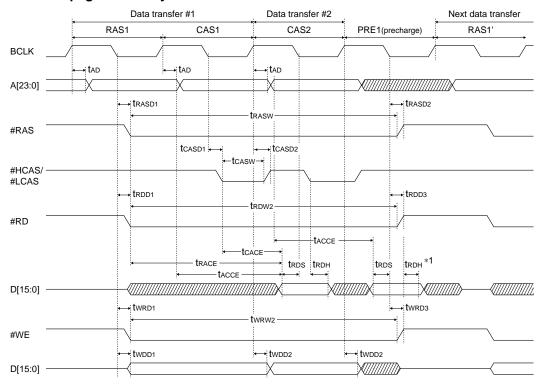

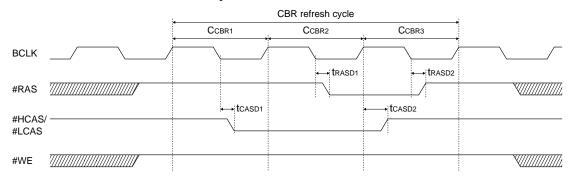

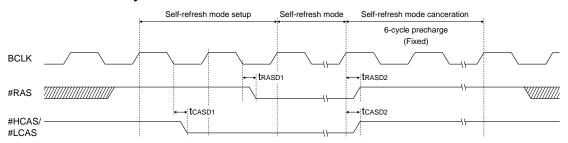

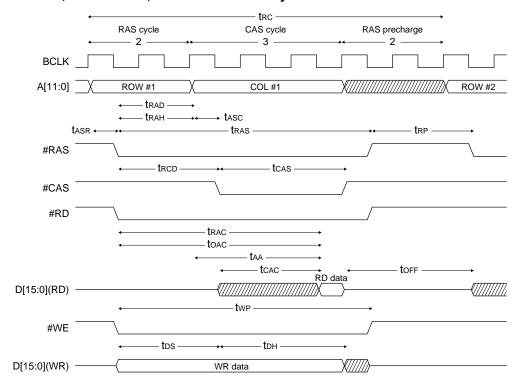

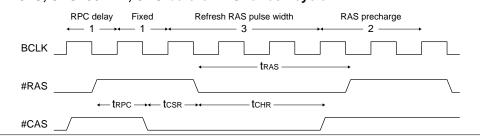

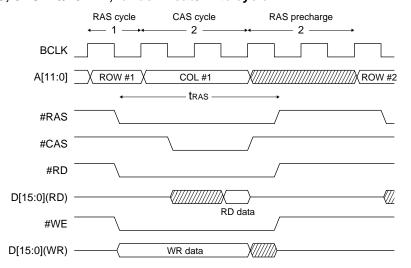

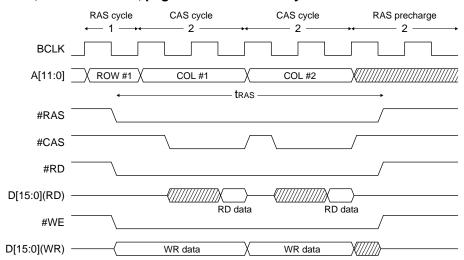

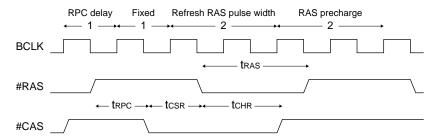

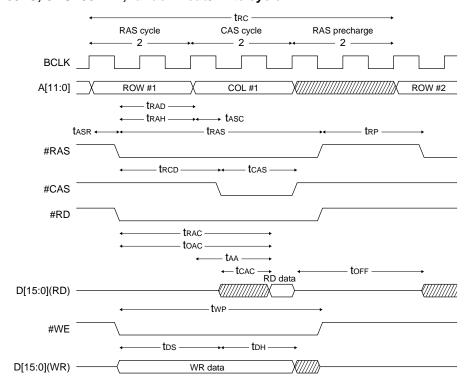

| A.1 DRAM (70nS)                                                      | 93  |

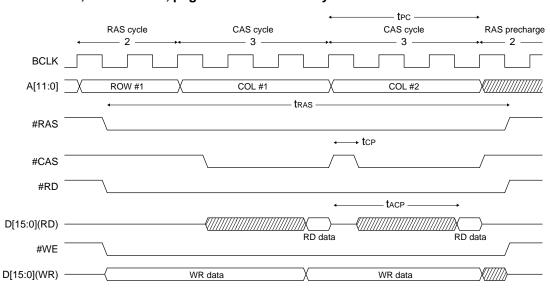

| A.2 DRAM (60nS)                                                      | 96  |

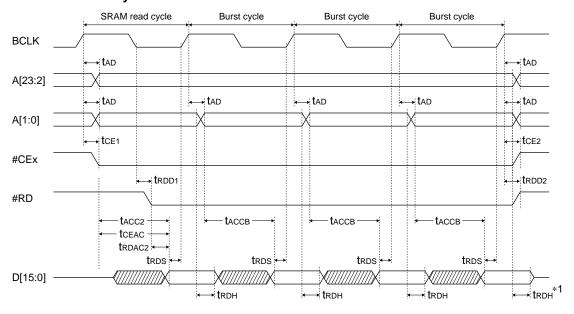

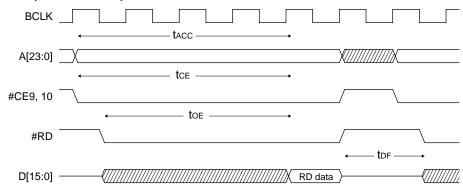

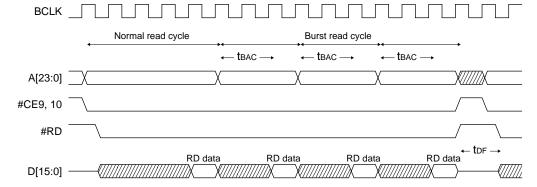

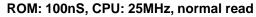

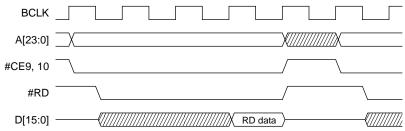

| A.3 ROM and Burst ROM                                                | 100 |

| A.4 SRAM (55nS)                                                      | 102 |

| A.5 SRAM (70nS)                                                      | 104 |

| A.6 8255A                                                            | 106 |

| R Pin Characteristics                                                | 107 |

1

### 1 Outline

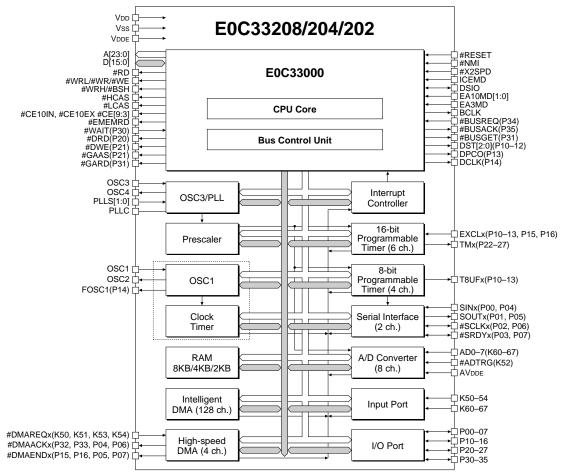

The E0C33208/204/202 is a Seiko Epson original 32-bit microcomputer that features high speed, low power and low-voltage operation. It is designed for portable equipment that needs advanced data processing.

The E0C33208/204/202 consists of the E0C33000 32-bit RISC type CPU as the core, a bus control unit, a DMA controller, an interrupt controller, timers, serial interface circuits, an optional A/D converter, and RAM. It also includes a high-speed oscillation circuit, PLL and low-speed oscillation circuit allowing high-speed operation and low-power operation and a clock timer that provides excellent clock functions.

The E0C33208/204/202 also provides a DSP function, by using the internal MAC (multiplication and accumulation) operation function with the A/D converter, it makes it possible to design simply speech recognition and voice synthesis systems.

Each model has a different internal RAM size, package and data bus interface as shown in Table 1.1.

| Table 1.1 Model Configuration |              |              |              |  |  |  |  |  |  |

|-------------------------------|--------------|--------------|--------------|--|--|--|--|--|--|

| Model                         | Package      | Internal RAM | Data bus I/F |  |  |  |  |  |  |

| E0C33208F0A                   | QFP5-128pin  | 8K bytes     | TTL          |  |  |  |  |  |  |

| E0C33204F0A                   | QFP5-128pin  | 4K bytes     | TTL          |  |  |  |  |  |  |

| E0C33202F0A                   | QFP5-128pin  | 2K bytes     | TTL          |  |  |  |  |  |  |

| E0C33208F0E                   | QFP5-128pin  | 8K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

| E0C33204F0E                   | QFP5-128pin  | 4K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

| E0C33202F0E                   | QFP5-128pin  | 2K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

| E0C33208F1E                   | QFP15-128pin | 8K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

| E0C33204F1E                   | QFP15-128pin | 4K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

| E0C33202F1E                   | QFP15-128pin | 2K bytes     | CMOS/LVTTL   |  |  |  |  |  |  |

Table 1.1 Model Configuration

The E0C3320xF0A that is configured with a TTL level data bus interface must be used only for  $5\,$  V data bus interface systems.

This manual explains the common functions using E0C33208/204/202 as the model name. Note that the independent functions available only for one or the other model (E0C33208, E0C33204 or E0C33202) are described with the specific model name.

### 1.1 Features

#### Core CPU

Seiko Epson original 32-bit RISC CPU E0C33000 built-in

- Basic instruction set: 105 instructions (16-bit fixed size)

- Sixteen 32-bit general-purpose register

- · 32-bit ALU and 8-bit shifter

- · Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

- 16.7 ns of minimum instruction execution time at 60 MHz operation

### Internal memory

RAM: 8K bytes (E0C33208) 4K bytes (E0C33204) 2K bytes (E0C33202)

#### Internal peripheral circuits

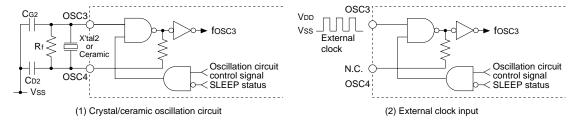

Oscillation circuit: High-speed (OSC3) oscillation circuit 33 MHz max.

Crystal/ceramic oscillator or external clock input

Low-speed (OSC1) oscillation circuit 32.768 kHz typ.

Crystal oscillator or external clock input

Timers: 8-bit timer 4 channels

16-bit timer 6 channels

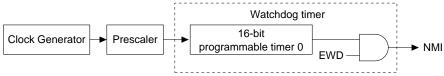

Watchdog timer (16-bit timer 0's function)

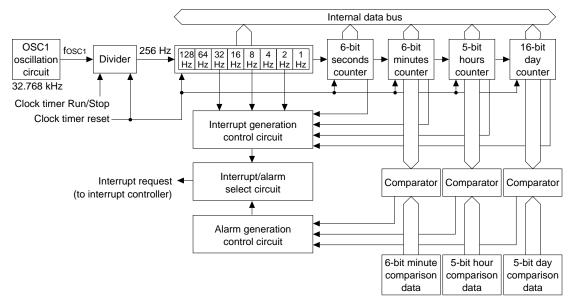

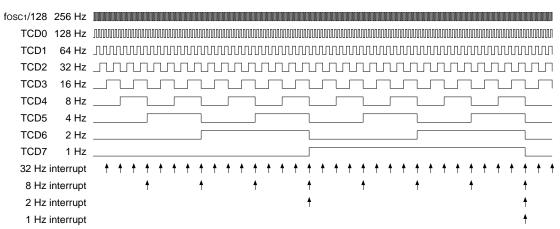

Clock timer 1 channel (with alarm function)

Serial interface: 2 channels (clock-synchronous system, asynchronous system and IrDA interface

are selectable)

A/D converter:  $10 \text{ bits} \times 8 \text{ channels}$

DMA controller: High-speed DMA 4 channels

Intelligent DMA 128 channels

Interrupt controller: Possible to invoke DMA

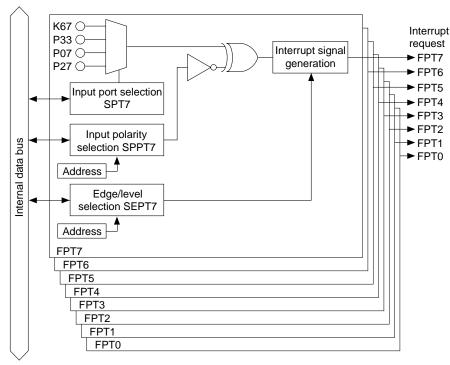

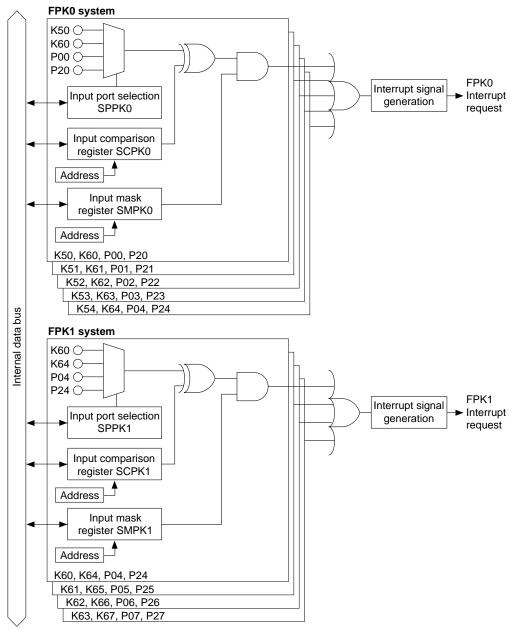

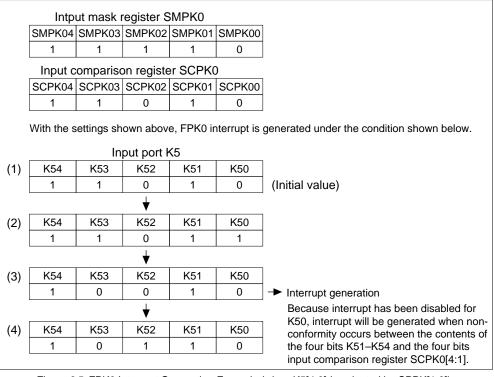

Input interrupt 10 types (programmable)

DMA controller interrupt 5 types

16-bit programmable timer interrupt 12 types

8-bit programmable timer interrupt 4 types

Serial interface interrupt 6 types

A/D converter interrupt 1 type

Clock timer interrupt 1 type

General-purpose input Shared with the I/O pins for internal peripheral circuits

and output ports: Input port 13 bits

I/O port 29 bits

#### External bus interface

BCU (bus control unit) built-in

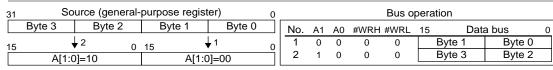

- 24-bit address bus (internal 28-bit processing)

- · 16-bit data bus

Data size is selectable from 8 bits and 16 bits in each area.

- Little-endian memory access; big-endian may be set in each area.

- Memory mapped I/O

- Chip enable and wait control circuits built-in

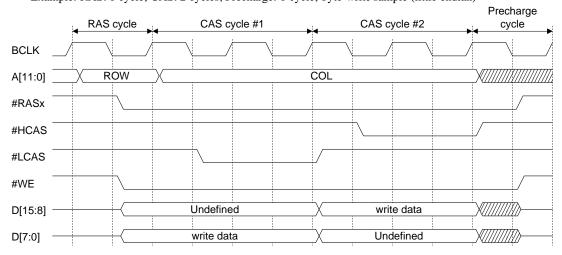

- · DRAM direct interface function built-in

Supports fast page mode and EDO page mode.

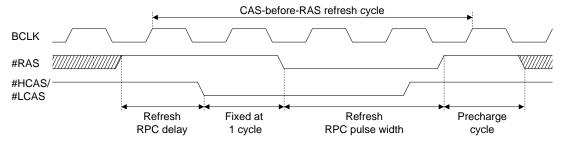

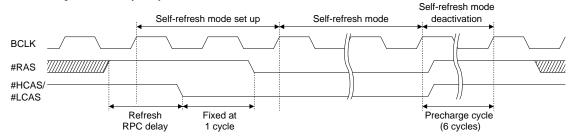

Supports self-refresh and CAS-before RAS refresh.

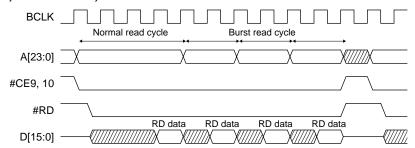

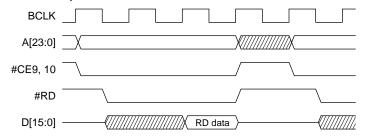

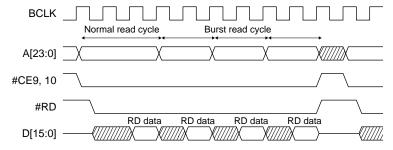

• Supports burst ROM.

#### Operating conditions and power consumption

Operating voltage: Core (VDD) 1.8 V to 3.6 V I/O (VDDE) 1.8 V to 5.5 V

Operating clock frequency: Max. 60 MHz (when core voltage = I/O voltage =  $3.3 \text{ V} \pm 0.3 \text{ V}$ )

Operating temperature: -40 to 85°C

Power consumption: During SLEEP 4 µW typ.

During HALT 100 mW typ.(3.3 V, 50 MHz) During execution 215 mW typ.(3.3 V, 50 MHz)

Note: The values of power consumption during execution were measured when a test

program that consisted of 55% load instructions, 23% arithmetic operation instructions, 1% mac instruction, 12% branch instructions and 9% ext instruction

was being continuously executed.

#### Supply form

QFP5-128pin or QFP15-128pin plastic package, or chip (Note that a chip is available only for the E0C33208.)

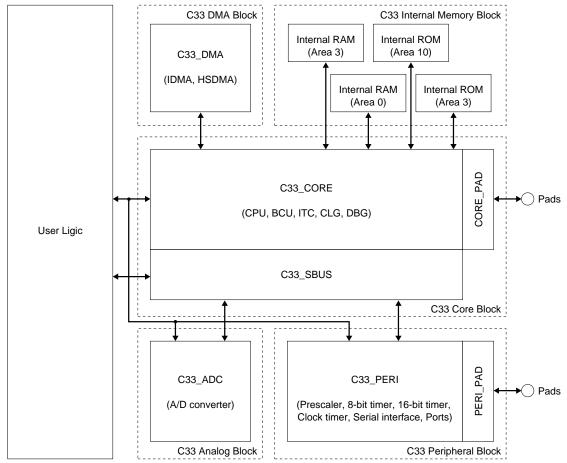

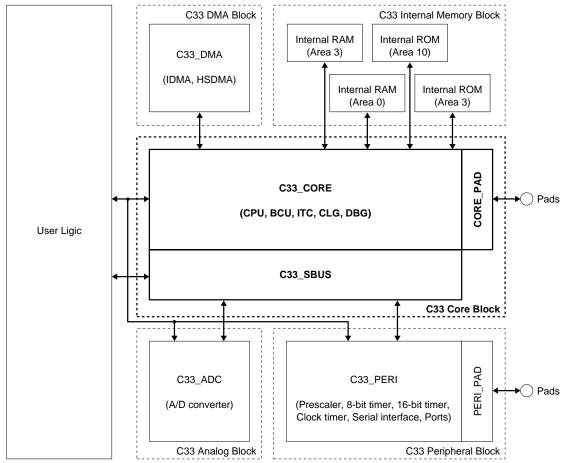

### 1.2 Block Diagram

Figure 1.2.1 E0C33208/204/202 Block Diagram

### 1.3 Pin Description

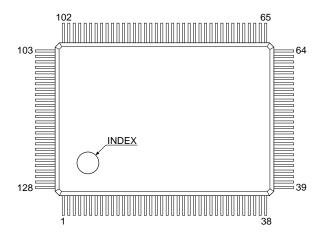

### 1.3.1 Pin Layout Diagram (plastic package)

### QFP5-128pin

| No. | Pin name           | No. | Pin name               |    | Pin name           | No. | Pin name             |

|-----|--------------------|-----|------------------------|----|--------------------|-----|----------------------|

| _ 1 | P24/TM2            | 33  | K65/AD5                | 65 | #RESET             | 97  | A16                  |

| 2   | Vss                | 34  | K50/#DMAREQ0           | 66 | #NMI               | 98  | ICEMD                |

| 3   | P25/TM3            | 35  | K64/AD4                | 67 | A0/#BSL            | 99  | A17                  |

| 4   | P26/TM4            | 36  | K63/AD3                | 68 | A1                 | 100 | A18                  |

| 5   | P15/EXCL4/#DMAEND0 | 37  | K62/AD2                | 69 | P34/#BUSREQ/#CE6   | 101 | A19                  |

| 6   | P27/TM5            | 38  | AVDDE                  | 70 | Vss                | 102 | P04/SIN1/#DMAACK2    |

| 7   | BCLK               | 39  | K61/AD1                | 71 | A2                 | 103 | P05/SOUT1/#DMAEND2   |

| 8   | P00/SIN0           | 40  | K60/AD0                | 72 | A3                 | 104 | P06/#SCLK1/DMAACK3   |

| 9   | P01/SOUT0          | 41  | D6                     | 73 | A4                 | 105 | Vss                  |

| 10  | D15                | 42  | Vss                    | 74 | A5                 | 106 | PLLC                 |

| 11  | VDD                | 43  | D5                     | 75 | A6                 | 107 | Vss                  |

| 12  | P03/#SRDY0         | 44  | D4                     | 76 | #CE10IN            | 108 | PLLS1                |

| 13  | D14                | 45  | D3                     | 77 | VDD                | 109 | PLLS0                |

| 14  | P31/#BUSGET/#GARD  | 46  | D2                     | 78 | #EMEMRD            | 110 | P07/#SRDY1/#DMAEND3  |

| 15  | D13                | 47  | D1                     | 79 | A7                 | 111 | #X2SPD               |

| 16  | P32/#DMAACK0       | 48  | D0                     | 80 | #HCAS              | 112 | EA10MD0              |

| 17  | D12                | 49  | P35/#BUSACK            | 81 | A8                 | 113 | EA10MD1              |

| 18  | P33/#DMAACK1       | 50  | VDDE                   | 82 | #LCAS              | 114 | VDD                  |

| 19  | D11                | 51  | #CE9/#CE17/#CE17&18    | 83 | A9                 | 115 | EA3MD                |

| 20  | K54/#DMAREQ3       | 52  | OSC2                   | 84 | P16/EXCL5/#DMAEND1 | 116 | OSC4                 |

| 21  | D10                | 53  | #CE7/#RAS0/#CE13/#RAS2 | 85 | A10                | 117 | P20/#DRD             |

| 22  | K53/#DMAREQ2       | 54  | OSC1                   | 86 | A20                | 118 | OSC3                 |

| 23  | D9                 | 55  | #CE6/#CE7&8            | 87 | A11                | 119 | P21/#DWE/#GAAS       |

| 24  | K52/#ADTRG         | 56  | #RD                    | 88 | A21                | 120 | #CE3                 |

| 25  | Vss                | 57  | Vss                    | 89 | A12                | 121 | P22/TM0              |

| 26  | K51/#DMAREQ1       | 58  | #WRL/#WR/#WE           | 90 | A22                | 122 | P23/TM1              |

| 27  | P02/#SCLK0         | 59  | #WRH/#BSH              | 91 | A13                | 123 | DSIO                 |

| 28  | D8                 | 60  | #CE10EX/#CE9&10EX      | 92 | A23                | 124 | P10/EXCL0/T8UF0/DST0 |

| 29  | D7                 | 61  | #CE8/#RAS1/#CE14/#RAS3 | 93 | Vss                | 125 | P11/EXCL1/T8UF1/DST1 |

| 30  | VDDE               | 62  | #CE5/#CE15/#CE15&16    | 94 | A14                | 126 | P12/EXCL2/T8UF2/DST2 |

| 31  | K67/AD7            | 63  | #CE4/#CE11/#CE11&12    | 95 | A15                | 127 | P13/EXCL3/T8UF3/DPCO |

| 32  | K66/AD6            | 64  | P30/#WAIT/#CE4&5       | 96 | VDDE               | 128 | P14/FOSC1/DCLK       |

Figure 1.3.1 Pin Layout Diagram (QFP5-128pin)

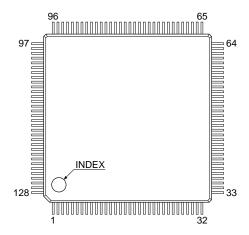

### QFP15-128pin

| No. | Pin name           | No. | Pin name               | No. | Pin name           | No. | Pin name             |

|-----|--------------------|-----|------------------------|-----|--------------------|-----|----------------------|

| 1   | P26/TM4            | 33  | K63/AD3                | 65  | A1                 | 97  | A18                  |

| 2   | P15/EXCL4/#DMAEND0 | 34  | K62/AD2                | 66  | P34/#BUSREQ/#CE6   | 98  | A19                  |

| 3   | P27/TM5            | 35  | AVDDE                  | 67  | Vss                | 99  | P04/SIN1/#DMAACK2    |

| 4   | BCLK               | 36  | K61/AD1                | 68  | A2                 | 100 | P05/SOUT1/#DMAEND2   |

| 5   | P00/SIN0           | 37  | K60/AD0                | 69  | A3                 | 101 | P06/#SCLK1/DMAACK3   |

| 6   | P01/SOUT0          | 38  | D6                     | 70  | A4                 | 102 | Vss                  |

| 7   | D15                | 39  | Vss                    | 71  | A5                 | 103 | PLLC                 |

| 8   | Vdd                | 40  | D5                     | 72  | A6                 | 104 | Vss                  |

| 9   | P03/#SRDY0         | 41  | D4                     | 73  | #CE10IN            | 105 | PLLS1                |

| 10  | D14                | 42  | D3                     | 74  | VDD                | 106 | PLLS0                |

| 11  | P31/#BUSGET/#GARD  | 43  | D2                     | 75  | #EMEMRD            | 107 | P07/#SRDY1/#DMAEND3  |

| 12  | D13                | 44  | D1                     | 76  | A7                 | 108 | #X2SPD               |

| 13  | P32/#DMAACK0       | 45  | D0                     | 77  | #HCAS              | 109 | EA10MD0              |

| 14  | D12                | 46  | P35/#BUSACK            | 78  | A8                 | 110 | EA10MD1              |

| 15  | P33/#DMAACK1       | 47  | VDDE                   | 79  | #LCAS              | 111 | VDD                  |

| 16  | D11                | 48  | #CE9/#CE17/#CE17&18    | 80  | A9                 | 112 | EA3MD                |

| 17  | K54/#DMAREQ3       | 49  | OSC2                   | 81  | P16/EXCL5/#DMAEND1 | 113 | OSC4                 |

| 18  | D10                | 50  | #CE7/#RAS0/#CE13/#RAS2 | 82  | A10                | 114 | P20/#DRD             |

| 19  | K53/#DMAREQ2       | 51  | OSC1                   | 83  | A20                | 115 | OSC3                 |

| 20  | D9                 | 52  | #CE6/#CE7&8            | 84  | A11                | 116 | P21/#DWE/#GAAS       |

| 21  | K52/#ADTRG         | 53  | #RD                    | 85  | A21                | 117 | #CE3                 |

| 22  | Vss                | 54  | Vss                    | 86  | A12                | 118 | P22/TM0              |

| 23  | K51/#DMAREQ1       | 55  | #WRL/#WR/#WE           | 87  | A22                | 119 | P23/TM1              |

| 24  | P02/#SCLK0         | 56  | #WRH/#BSH              | 88  | A13                | 120 | DSIO                 |

| 25  | D8                 | 57  | #CE10EX/#CE9&10EX      | 89  | A23                | 121 | P10/EXCL0/T8UF0/DST0 |

| 26  | D7                 | 58  | #CE8/#RAS1/#CE14/#RAS3 | 90  | Vss                | 122 | P11/EXCL1/T8UF1/DST1 |

| 27  | VDDE               | 59  | #CE5/#CE15/#CE15&16    | 91  | A14                | 123 | P12/EXCL2/T8UF2/DST2 |

| 28  | K67/AD7            | 60  | #CE4/#CE11/#CE11&12    | 92  | A15                | 124 | P13/EXCL3/T8UF3/DPCO |

| 29  | K66/AD6            | 61  | P30/#WAIT/#CE4&5       | 93  | VDDE               | 125 | P14/FOSC1/DCLK       |

| 30  | K65/AD5            | 62  | #RESET                 | 94  | A16                | 126 | P24/TM2              |

| 31  | K50/#DMAREQ0       | 63  | #NMI                   | 95  | ICEMD              | 127 | Vss                  |

| 32  | K64/AD4            | 64  | A0/#BSL                | 96  | A17                | 128 | P25/TM3              |

Figure 1.3.2 Pin Layout Diagram (QFP15-128pin)

### 1.3.2 Pin Functions

Table 1.3.1 List of Pins for Power Supply System

| take the same and the same apply a joiner. |             |            |     |         |                                              |  |  |  |

|--------------------------------------------|-------------|------------|-----|---------|----------------------------------------------|--|--|--|

| Pin name                                   | Pin         | No.        | 1/0 | Pull-up | Function                                     |  |  |  |

| Till liame                                 | QFP5-128    | QFP15-128  |     | i un-up | i dilettori                                  |  |  |  |

| VDD                                        | 11,77,114   | 8,74,111   | -   | -       | Power supply (+) for the internal logic      |  |  |  |

| Vss                                        | 2,25,42,57, | 127,22,39, | _   | -       | Power supply (-); GND                        |  |  |  |

|                                            | 70,93,105,  | 54,67,90,  |     |         |                                              |  |  |  |

|                                            | 107         | 102,104    |     |         |                                              |  |  |  |

| VDDE                                       | 30,50,96    | 27,47,93   | _   | -       | Power supply (+) for the I/O block           |  |  |  |

| AVDDE                                      | 38          | 35         | _   | _       | Analog system power supply (+); AVDDE = VDDE |  |  |  |

Table 1.3.2 List of Pins for External Bus Interface Signals

|                                 | Pin No.                                                  |                                                        |     |         | S 101 External Bus interface Signals                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------------------------|----------------------------------------------------------|--------------------------------------------------------|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin name                        | QFP5-128                                                 | <b>No.</b><br>QFP15-128                                | I/O | Pull-up | Function                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

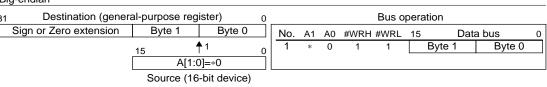

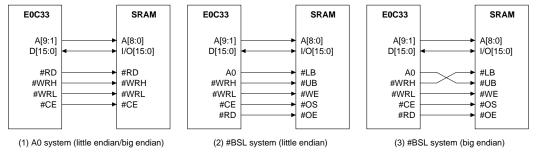

| A0<br>#BSL                      | 67                                                       | 64                                                     | 0   | -       | A0: Address bus (A0) when SBUSST(D3/0x4812E) = "0" (default) #BSL: Bus strobe (low byte) signal when SBUSST(D3/0x4812E) = "1"                                                                                                                                                                                                                                                                                                       |  |  |

| A[23:1]                         | 68,71–75,<br>79,81,83,<br>85–92,94,<br>95, 97,<br>99–101 | 65,68–72,<br>76,78,80,<br>82–89,91,<br>92,94,<br>96–98 | 0   | Т       | Address bus (A1 to A23)                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| D[15:0]                         | 10,13,15,17,<br>19,21,23,28,<br>29,41,43–48              | ' ' ' '                                                | I/O | -       | Data bus (D0 to D15)                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| #CE10EX                         | 60                                                       | 57                                                     | 0   | _       | Area 10 chip enable for external memory  * When CEFUNC[1:0] = "1x", this pin outputs #CE9+#CE10EX signal.                                                                                                                                                                                                                                                                                                                           |  |  |

| #CE10IN                         | 76                                                       | 73                                                     | 0   | -       | Area 10 chip enable for internal ROM emulation memory                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| #CE9<br>#CE17                   | 51                                                       | 48                                                     | 0   | I       | #CE9: Area 9 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)  #CE17: Area 17 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"  * When CEFUNC[1:0] = "1x", this pin outputs #CE17+#CE18 signal.                                                                                                                                                                                                                   |  |  |

| #CE8<br>#RAS1<br>#CE14<br>#RAS3 | 61                                                       | 58                                                     | 0   | -       | #CE8: Area 8 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A8DRA(D8/0x48128) = "0" (default)  #RAS1: Area 8 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A8DRA(D8/0x48128) = "1"  #CE14: Area 14 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A14DRA(D8/0x48122) = "0"  #RAS3: Area 14 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A14DRA(D8/0x48122) = "1" |  |  |

| #CE7<br>#RAS0<br>#CE13<br>#RAS2 | 53                                                       | 50                                                     | 0   | -       | #CE7: Area 7 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A7DRA(D7/0x48128) = "0" (default)  #RAS0: Area 7 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "00" and A7DRA(D7/0x48128) = "1"  #CE13: Area 13 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A13DRA(D7/0x48122) = "0"  #RAS2: Area 13 DRAM row strobe when CEFUNC[1:0](D[A:9])/0x48130) = "01" or "1x" and A13DRA(D7/0x48122) = "1" |  |  |

| #CE6                            | 55                                                       | 52                                                     | 0   | -       | Area 6 chip enable  * When CEFUNC[1:0] = "1x", this pin outputs #CE7+#CE8 signal.                                                                                                                                                                                                                                                                                                                                                   |  |  |

| #CE5<br>#CE15                   | 62                                                       | 59                                                     | 0   | _       | #CE5: Area 5 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)  #CE15: Area 15 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"                                                                                                                                                                                                                                                                                    |  |  |

| #CE4<br>#CE11                   | 63                                                       | 60                                                     | 0   | -       | #CE4: Area 4 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "00" (default)  #CE11: Area 11 chip enable when CEFUNC[1:0](D[A:9])/0x48130) = "01"   * When CEFUNC[1:0] = "1x", this pin outputs #CE11+#CE12 signal.                                                                                                                                                                                                                  |  |  |

| #CE3                            | 120                                                      | 117                                                    | 0   | -       | Area 3 chip enable                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

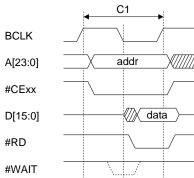

| #RD                             | 56                                                       | 53                                                     | 0   | -       | Read signal                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| #EMEMRD                         | 78                                                       | 75                                                     | 0   | -       | Read signal for internal ROM emulation memory                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| Pin name | Pin      | No.       | 1/0 | Pull-up | Function       |                                                                                                 |  |

|----------|----------|-----------|-----|---------|----------------|-------------------------------------------------------------------------------------------------|--|

| Pin name | QFP5-128 | QFP15-128 | 20  | Pull-up | Function       |                                                                                                 |  |

| #WRL     | 58       | 55        | 0   | -       | #WRL:          | Write (low byte) signal when SBUSST(D3/0x4812E) = "0"                                           |  |

| #WR      |          |           |     |         |                | (default)                                                                                       |  |

| #WE      |          |           |     |         |                | Write signal when SBUSST(D3/0x4812E) = "1"                                                      |  |

|          |          |           |     |         | #WE:           | DRAM write signal (default)                                                                     |  |

| #WRH     | 59       | 56        | 0   | -       | #WRH:          | Write (high byte) signal when SBUSST(D3/0x4812E) = "0"                                          |  |

| #BSH     |          |           |     |         |                | (default)                                                                                       |  |

|          |          |           |     |         |                | Bus strobe (high byte) signal when SBUSST(D3/0x4812E)="1"                                       |  |

| #HCAS    | 80       | 77        | 0   | -       |                | DRAM column address strobe (high byte) signal                                                   |  |

| #LCAS    | 82       | 79        | 0   | -       |                | DRAM column address strobe (low byte) signal                                                    |  |

| BCLK     | 7        | 4         | 0   | _       | Bus clock or   |                                                                                                 |  |

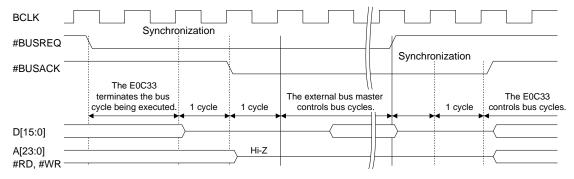

| P34      | 69       | 66        | I/O | -       |                | I/O port when CFP34(D4/0x402DC) = "0" (default)                                                 |  |

| #BUSREQ  |          |           |     |         |                | Bus release request input when CFP34(D4/0x402DC) = "1"                                          |  |

| #CE6     |          |           |     |         | #CE6:          | Area 6 chip enable when CFP34(D4/0x402DC) = "1"                                                 |  |

| Dos      |          |           |     |         |                | and IOC34(D4/0x402DE) = "1"                                                                     |  |

| P35      | 49       | 46        | I/O | -       |                | I/O port when CFP35(D5/0x402DC) = "0" (default)                                                 |  |

| #BUSACK  |          |           |     |         |                | Bus acknowledge output when CFP35(D5/0x402DC) = "1"                                             |  |

| P30      | 64       | 61        | I/O | _       | P30:           | I/O port when CFP30(D0/0x402DC) = "0" (default)                                                 |  |

| #WAIT    |          |           |     |         |                | Wait cycle request input when CFP30(D0/0x402DC) = "1"                                           |  |

| #CE4&5   |          |           |     |         |                | Areas 4&5 chip enable when CFP30(D0/0x402DC) = "1"                                              |  |

| P20      | 117      | 114       | I/O |         |                | and IOC30(D0/0x402DE) = "1"                                                                     |  |

| #DRD     | 117      | 114       | 1/0 | _       | #DRD:          | I/O port when CFP20(D0/0x402D8) = "0" (default) DRAM read signal output for successive RAS mode |  |

| #DIXD    |          |           |     |         |                | when CFP20(D0/0x402D8) = "1"                                                                    |  |

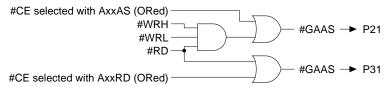

| P21      | 119      | 116       | I/O |         |                | I/O port when CFP21(D1/0x402D8) = "0"                                                           |  |

| #DWE     | 113      | 110       | 1/0 |         |                | and CFEX2(D2/0x402DF) = "0" (default)                                                           |  |

| #GAAS    |          |           |     |         |                | DRAM write signal output for successive RAS mode                                                |  |

|          |          |           |     |         |                | when CFP21(D1/0x402D8) = "1"                                                                    |  |

|          |          |           |     |         |                | and CFEX2(D2/0x402DF) = "0"                                                                     |  |

|          |          |           |     |         | #GAAS:         | Area address strobeoutput for GA when CFEX2(D2/0x402DF)                                         |  |

|          |          |           |     |         |                | = "1"                                                                                           |  |

| P31      | 14       | 11        | I/O |         | P31:           | I/O port when CFP31(D1/0x402DC) = "0"                                                           |  |

| #BUSGET  |          |           |     |         |                | and CFEX3(D3/0x402DF) = "0" (default)                                                           |  |

| #GARD    |          |           |     |         | #BUSGET:       | Bus status monitor signal output for bus request                                                |  |

|          |          |           |     |         |                | when CFP31(D1/0x402DC) = "1"                                                                    |  |

|          |          |           |     |         |                | and CFEX3(D3/0x402DF) = "0"                                                                     |  |

| E440MB4  |          |           |     |         |                | Area read signal output for GA when CFEX3(D3/0x402DF)="1"                                       |  |

| EA10MD1  | 113      | 110       | I   | With    |                | ot mode selection                                                                               |  |

|          |          |           |     | pull-up | EA10MD1        | EA10MD0 Mode                                                                                    |  |

| EA40MD0  | 440      | 400       |     |         | 1              | 1 External ROM mode                                                                             |  |

| EA10MD0  | 112      | 109       | I   | _       | 1 0            | 0 Internal ROM mode 1 OTP mode                                                                  |  |

|          |          |           |     |         | 0              | 0 Internal ROM emulation                                                                        |  |

| EA3MD    | 115      | 112       | _   | With    | Area 3 mod     |                                                                                                 |  |

| LASIVID  | 110      | 112       | l ' | pull-up |                | OM mode, 0: Emulation mode                                                                      |  |

|          | l        | l         |     | Pull-up | i. internality | OW Mode, o. Emulation mode                                                                      |  |

Table 1.3.3 List of Pins for HSDMA Control Signals

| Table 1.0.0 Elst of |          |           |             |         |           |                                                        |

|---------------------|----------|-----------|-------------|---------|-----------|--------------------------------------------------------|

| Pin name            | Pin No.  |           | I/O Pull-up |         |           | Function                                               |

| · iii iidiiio       | QFP5-128 | QFP15-128 |             | i un up |           | 1 dilonois                                             |

| K50                 | 34       | 31        | _           | With    | K50:      | Input port when CFK50(D0/0x402C0) = "0" (default)      |

| #DMAREQ0            |          |           |             | pull-up | #DMAREQ0: | HSDMA Ch. 0 request input when CFK50(D0/0x402C0) = "1" |

| K51                 | 26       | 23        | -1          | With    | K51:      | Input port when CFK51(D1/0x402C0) = "0" (default)      |

| #DMAREQ1            |          |           |             | pull-up | #DMAREQ1: | HSDMA Ch. 1 request input when CFK51(D1/0x402C0) = "1" |

| K53                 | 22       | 19        | -1          | With    | K53:      | Input port when CFK53(D3/0x402C0) = "0" (default)      |

| #DMAREQ2            |          |           |             | pull-up | #DMAREQ2: | HSDMA Ch. 2 requestinput when CFK53(D3/0x402C0) = "1"  |

| K54                 | 20       | 17        | -1          | With    | K54:      | Input port when CFK54(D4/0x402C0) = "0" (default)      |

| #DMAREQ3            |          |           |             | pull-up | #DMAREQ3: | HSDMA Ch. 3 request input when CFK54(D4/0x402C0) = "1" |

| P32                 | 16       | 13        | I/O         | -       | P32:      | I/O port when CFP32(D2/0x402DC) = "0" (default)        |

| #DMAACK0            |          |           |             |         | #DMAACK0: | HSDMA Ch. 0 acknowledge output                         |

|                     |          |           |             |         |           | when CFP32(D2/0x402DC) = "1"                           |

8

| Pin name                  | Pin      | No.       | 1/0 | Pull-up | Function                     |                                                                                                                                                                                                                                                  |  |

|---------------------------|----------|-----------|-----|---------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin name                  | QFP5-128 | QFP15-128 | 1/0 | Pull-up |                              |                                                                                                                                                                                                                                                  |  |

| P33<br>#DMAACK1           | 18       | 15        | I/O | -       | P33:<br>#DMAACK1:            | I/O port when CFP33(D3/0x402DC) = "0" (default) HSDMA Ch. 1 acknowledge output when CFP33(D3/0x402DC) = "1"                                                                                                                                      |  |

| P04<br>SIN1<br>#DMAACK2   | 102      | 99        | I/O | -       | P04:<br>SIN1:<br>#DMAACK2:   | I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0" (default) Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and CFEX4(D4/0x402DF) = "0" HSDMA Ch. 2 acknowledge output when CFEX4(D4/0x402DF) = "1"                     |  |

| P06<br>#SCLK1<br>#DMAACK3 | 104      | 101       | I/O | -       | P06:<br>#SCLK1:<br>#DMAACK3: | I/O port when CFP06(D6/0x402D0) = "0" and CFEX6(D6/0x402DF) = "0" (default) Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1" and CFEX6(D6/0x402DF) = "0" HSDMA Ch. 3 acknowledge output when CFEX6(D6/0x402DF) = "1"             |  |

| P15<br>EXCL4<br>#DMAEND0  | 5        | 2         | 1/0 | ı       | P15:<br>EXCL4:<br>#DMAEND0:  | I/O port when CFP15(D5/0x402D4) = "0" (default) 16-bit timer 4 event counter input when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "0" HSDMA Ch. 0 end-of-transfer signal output when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "1"   |  |

| P16<br>EXCL5<br>#DMAEND1  | 84       | 81        | I/O | -       | P16:<br>EXCL5:<br>#DMAEND1:  | I/O port when CFP16(D6/0x402D4) = "0" (default) 16-bit timer 5 event counter input when CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "0" HSDMA Ch. 1 end-of-transfer signal output when CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "1"   |  |

| P05<br>SOUT1<br>#DMAEND2  | 103      | 100       | I/O | -       | P05:<br>SOUT1:<br>#DMAEND2:  | I/O port when CFP05(D5/0x402D0) = "0" and CFEX5(D5/0x402DF) = "0" (default) Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0" HSDMA Ch. 2 end-of-transfer signal output when CFEX5(D5/0x402DF) = "1"         |  |

| P07<br>#SRDY1<br>#DMAEND3 | 110      | 107       | I/O | -       | P07:<br>#SRDY1:<br>#DMAEND3: | I/O port when CFP07(D7/0x402D0) = "0" and CFEX7(D7/0x402DF) = "0" (default) Serial I/F Ch. 1 ready signal output when CFP07(D7/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0" HSDMA Ch. 3 end-of-transfer signal output when CFEX7(D7/0x402DF) = "1" |  |

Table 1.3.4 List of Pins for Internal Peripheral Circuits

| Pin name     | Pin      | No.       | 1/0 | Pull-up |         | Function                                                 |

|--------------|----------|-----------|-----|---------|---------|----------------------------------------------------------|

| Fill lialite | QFP5-128 | QFP15-128 |     | ruii-up |         | Function                                                 |

| K52          | 24       | 21        | 1   | With    | K52:    | Input port when CFK52(D2/0x402C0) = "0" (default)        |

| #ADTRG       |          |           |     | pull-up | #ADTRG: | A/D converter trigger input when CFK52(D2/0x402C0) = "1" |

| K60          | 40       | 37        | 1   | _       | K60:    | Input port when CFK60(D0/0x402C3) = "0" (default)        |

| AD0          |          |           |     |         | AD0:    | A/D converter Ch. 0 input when CFK60(D0/0x402C3) = "1"   |

| K61          | 39       | 36        | 1   | -       | K61:    | Input port when CFK61(D1/0x402C3) = "0" (default)        |

| AD1          |          |           |     |         | AD1:    | A/D converter Ch. 1 input when CFK61(D1/0x402C3) = "1"   |

| K62          | 37       | 34        | 1   | -       | K62:    | Input port when CFK62(D2/0x402C3) = "0" (default)        |

| AD2          |          |           |     |         | AD2:    | A/D converter Ch. 2 input when CFK62(D2/0x402C3) = "1"   |

| K63          | 36       | 33        | 1   | -       | K63:    | Input port when CFK63(D3/0x402C3) = "0" (default)        |

| AD3          |          |           |     |         | AD3:    | A/D converter Ch. 3 input when CFK63(D3/0x402C3) = "1"   |

| K64          | 35       | 32        | 1   | -       | K64:    | Input port when CFK64(D4/0x402C3) = "0" (default)        |

| AD4          |          |           |     |         | AD4:    | A/D converter Ch. 4 input when CFK64(D4/0x402C3) = "1"   |

| K65          | 33       | 30        | ı   | -       | K65:    | Input port when CFK65(D5/0x402C3) = "0" (default)        |

| AD5          |          |           |     |         | AD5:    | A/D converter Ch. 5 input when CFK65(D5/0x402C3) = "1"   |

| K66          | 32       | 29        | ı   | -       | K66:    | Input port when CFK66(D6/0x402C3) = "0" (default)        |

| AD6          |          |           |     |         | AD6:    | A/D converter Ch. 6 input when CFK60(D6/0x402C3) = "1"   |

| K67          | 31       | 28        | ı   | _       | K67:    | Input port when CFK67(D7/0x402C3) = "0" (default)        |

| AD7          |          |           |     |         | AD7:    | A/D converter Ch. 7 input when CFK67(D7/0x402C3) = "1"   |

| Pin name                | Pin      | No.       | 1/0 | Pull-up |                            | Function                                                                                                                                                                                        |

|-------------------------|----------|-----------|-----|---------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rin name                | QFP5-128 | QFP15-128 | 1/0 | r un-up |                            | Function                                                                                                                                                                                        |

| P00<br>SIN0             | 8        | 5         | I/O | _       | P00:<br>SIN0:              | I/O port when CFP00(D0/0x402D0) = "0" (default) Serial I/F Ch. 0 data input when CFP00(D0/0x402D0) = "1"                                                                                        |

| P01<br>SOUT0            | 9        | 6         | I/O | -       | P01:<br>SOUT0:             | I/O port when CFP01(D1/0x402D0) = "0" (default) Serial I/F Ch. 0 data output when CFP01(D1/0x402D0) = "1"                                                                                       |

| P02<br>#SCLK0           | 27       | 24        | I/O | _       | P02:<br>#SCLK0:            | I/O port when CFP02(D2/0x402D0) = "0" (default) Serial I/F Ch. 0 clock input/output when CFP02(D2/0x402D0) = "1"                                                                                |

| P03<br>#SRDY0           | 12       | 9         | I/O | _       | P03:<br>#SRDY0:            | I/O port when CFP03(D3/0x402D0) = "0" (default) Serial I/F Ch. 0 ready signal output when CFP03(D3/0x402D0) = "1"                                                                               |

| P04<br>SIN1<br>#DMAACK2 | 102      | 99        | I/O | I       | P04:<br>SIN1:<br>#DMAACK2: | I/O port when CFP04(D4/0x402D0) = "0" and CFEX4(D4/0x402DF) = "0" (default) Serial I/F Ch. 1 data input when CFP04(D4/0x402D0) = "1" and CFEX4(D4/0x402DF) = "0" HSDMA Ch. 2 acknowledge output |

| P05                     | 103      | 100       | I/O | _       | P05:                       | when CFEX4(D4/0x402DF) = "1"  I/O port when CFP05(D5/0x402D0) = "0"                                                                                                                             |

| SOUT1<br>#DMAEND2       |          |           |     |         | SOUT1:                     | and CFEX5(D5/0x402DF) = "0" (default) Serial I/F Ch. 1 data output when CFP05(D5/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"                                                                     |

|                         |          |           |     |         | #DMAEND2:                  | HSDMA Ch. 2 end-of-transfer signal output when CFEX5(D5/0x402DF) = "1"                                                                                                                          |

| P06<br>#SCLK1           | 104      | 101       | I/O | -       | P06:                       | I/O port when CFP06(D6/0x402D0) = "0"<br>and CFEX6(D6/0x402DF) = "0" (default)                                                                                                                  |

| #DMAACK3                |          |           |     |         | #SCLK1:<br>#DMAACK3:       | Serial I/F Ch. 1 clock input/output when CFP06(D6/0x402D0) = "1" and CFEX6(D6/0x402DF) = "0" HSDMA Ch. 3 acknowledge output                                                                     |

|                         |          |           |     |         |                            | when CFEX6(D6/0x402DF) = "1"                                                                                                                                                                    |

| P07<br>#SRDY1           | 110      | 107       | I/O | _       | P07:                       | I/O port when CFP07(D7/0x402D0) = "0"<br>and CFEX7(D7/0x402DF) = "0" (default)                                                                                                                  |

| #DMAEND3                |          |           |     |         | #SRDY1:                    | Serial I/F Ch. 1 ready signal output when  CFP07(D7/0x402D0) = "1" and CFEX5(D5/0x402DF) = "0"  HSDMA Ch. 3 end-of-transfer signal output                                                       |

|                         |          |           |     |         | #DIVIALINDS.               | when CFEX7(D7/0x402DF) = "1"                                                                                                                                                                    |

| P10<br>EXCL0            | 124      | 121       | I/O | -       | P10:                       | I/O port when CFP10(D0/0x402D4) = "0"<br>and CFEX1(D1/0x402DF) = "0"                                                                                                                            |

| T8UF0<br>DST0           |          |           |     |         | EXCL0:                     | 16-bit timer 0 event counter input when CFP10(D0/0x402D4) = "1", IOC10(D0/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"                                                                            |

|                         |          |           |     |         | T8UF0:                     | 8-bit timer 0 output when CFP10(D0/0x402D4) = "1",<br>IOC10(D0/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0"                                                                                       |

|                         |          |           |     |         | DST0:                      | DST0 signal output when CFEX1(D1/0x402DF)="1" (default)                                                                                                                                         |

| P11<br>EXCL1            | 125      | 122       | I/O | -       | P11:                       | I/O port when CFP11(D1/0x402D4) = "0"<br>and CFEX1(D1/0x402DF) = "0"                                                                                                                            |

| T8UF1<br>DST1           |          |           |     |         | EXCL1:                     | 16-bit timer 1 event counter input when CFP11(D1/0x402D4) = "1", IOC11(D1/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"                                                                            |

|                         |          |           |     |         | T8UF1:                     | 8-bit timer 1 output when CFP11(D1/0x402D4) = "1", IOC11(D1/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0" DST1 signal output when CFEX1(D1/0x402DF) = "1" (default)                                |

| P12<br>EXCL2            | 126      | 123       | I/O | _       | DST1:<br>P12:              | I/O port when CFP12(D2/0x402D4) = "0" and CFEX0(D0/0x402DF) = "0"                                                                                                                               |

| T8UF2<br>DST2           |          |           |     |         | EXCL2:                     | 16-bit timer 2 event counter input when CFP12(D2/0x402D4) = "1", IOC12(D2/0x402D6) = "0" and CFEX0(D0/0x402DF) = "0"                                                                            |

|                         |          |           |     |         | T8UF2:                     | 8-bit timer 2 output when CFP12(D2/0x402D4) = "1",<br>IOC12(D2/0x402D6) = "1" and CFEX0(D0/0x402DF) = "0"                                                                                       |

|                         |          |           |     |         | DST2:                      | DST2 signal output when CFEX0(D0/0x402DF)="1" (default)                                                                                                                                         |

| Pin name                      | Pin      | No.       | I/O | Pull-up |                             | Function                                                                                                                                                                                                                                       |

|-------------------------------|----------|-----------|-----|---------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin name                      | QFP5-128 | QFP15-128 | 1/0 | Pull-up |                             | runction                                                                                                                                                                                                                                       |

| P13<br>EXCL3<br>T8UF3<br>DPCO | 127      | 124       | I/O | -       | P13:<br>EXCL3:              | I/O port when CFP13(D3/0x402D4) = "0" and CFEX1(D1/0x402DF) = "0" 16-bit timer 3 event counter input when CFP13(D3/0x402D4) = "1", IOC13(D3/0x402D6) = "0" and CFEX1(D1/0x402DF) = "0"                                                         |

|                               |          |           |     |         | T8UF3:<br>DPCO:             | 8-bit timer 3 output when CFP13(D3/0x402D4) = "1", IOC13(D3/0x402D6) = "1" and CFEX1(D1/0x402DF) = "0" DPCO signal output when CFEX1(D1/0x402DF) = "1" (default)                                                                               |

| P14<br>FOSC1<br>DCLK          | 128      | 125       | I/O | -       | P14:<br>FOSC1:<br>DCLK:     | I/O port when CFP14(D4/0x402D4) = "0" and CFEX0(D0/0x402DF) = "0" OSC1 clock output when CFP14(D4/0x402D4) = "1" and CFEX0(D0/0x402DF) = "0" DCLK signal output when CFEX0(D0/0x402DF) = "1" (default)                                         |

| P15<br>EXCL4<br>#DMAEND0      | 5        | 2         | I/O | -       | P15:<br>EXCL4:<br>#DMAEND0: | I/O port when CFP15(D5/0x402D4) = "0" (default) 16-bit timer 4 event counter input when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "0" HSDMA Ch. 0 end-of-transfer signal output when CFP15(D5/0x402D4) = "1" and IOC15(D5/0x402D6) = "1" |

| P16<br>EXCL5<br>#DMAEND1      | 84       | 81        | I/O | -       | P16:<br>EXCL5:<br>#DMAEND1: | I/O port when CFP16(D6/0x402D4) = "0" (default) 16-bit timer 5 event counter input when CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "0" HSDMA Ch. 1 end-of-transfer signal output when CFP16(D6/0x402D4) = "1" and IOC16(D6/0x402D6) = "1" |

| P22<br>TM0                    | 121      | 118       | I/O | -       | P22:<br>TM0:                | I/O port when CFP22(D2/0x402D8) = "0" (default) 16-bit timer 0 output when CFP22(D2/0x402D8) = "1"                                                                                                                                             |

| P23<br>TM1                    | 122      | 119       | I/O | -       | P23:<br>TM1:                | I/O port when CFP23(D3/0x402D8) = "0" (default) 16-bit timer 1 output when CFP23(D3/0x402D8) = "1"                                                                                                                                             |

| P24<br>TM2                    | 1        | 126       | I/O | -       | P24:<br>TM2:                | I/O port when CFP24(D4/0x402D8) = "0" (default) 16-bit timer 2 output when CFP24(D4/0x402D8) = "1"                                                                                                                                             |

| P25<br>TM3                    | 3        | 128       | I/O | -       | P25:<br>TM3:                | I/O port when CFP25(D5/0x402D8) = "0" (default) 16-bit timer 3 output when CFP25(D5/0x402D8) = "1"                                                                                                                                             |

| P26<br>TM4                    | 4        | 1         | I/O | -       | P26:<br>TM4:                | I/O port when CFP26(D6/0x402D8) = "0" (default) 16-bit timer 4 output when CFP26(D6/0x402D8) = "1"                                                                                                                                             |

| P27<br>TM5                    | 6        | 3         | I/O | _       | P27:<br>TM5:                | I/O port when CFP27(D7/0x402D8) = "0" (default) 16-bit timer 5 output when CFP27(D7/0x402D8) = "1"                                                                                                                                             |

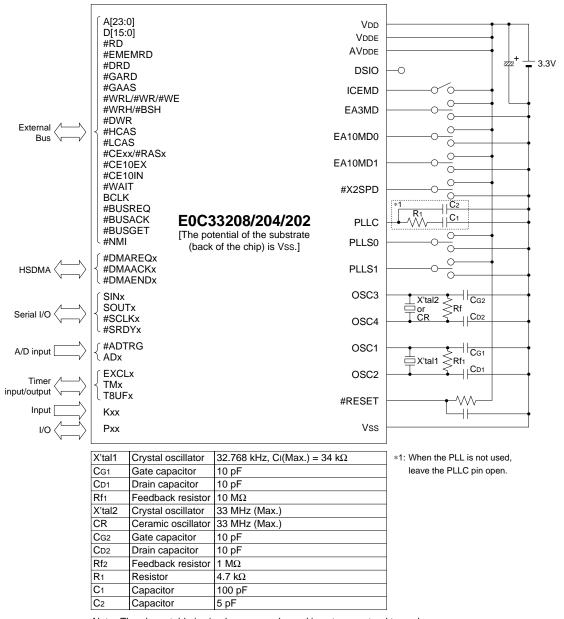

Table 1.3.5 List of Pins for Clock Generator

|            |          |           |     |         | OFFIRS OF Clock Generalor                                                   |  |  |  |  |  |  |  |

|------------|----------|-----------|-----|---------|-----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Pin name   | Pin      | No.       | 1/0 | Pull-up | Function                                                                    |  |  |  |  |  |  |  |

| T III Hame | QFP5-128 | QFP15-128 | 2   | i un up | T unotion                                                                   |  |  |  |  |  |  |  |

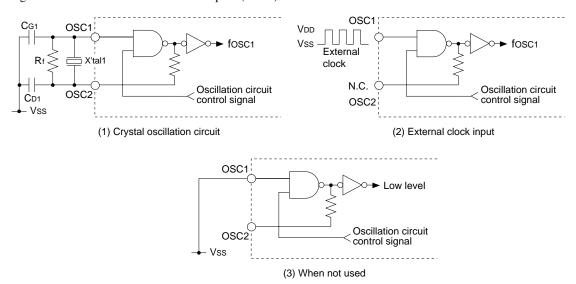

| OSC1       | 54       | 51        | -   | _       | Low-speed (OSC1) oscillation input (32 kHz crystal oscillator or external   |  |  |  |  |  |  |  |

|            |          |           |     |         | clock input)                                                                |  |  |  |  |  |  |  |

| OSC2       | 52       | 49        | 0   | _       | Low-speed (OSC1) oscillation output                                         |  |  |  |  |  |  |  |

| OSC3       | 118      | 115       | 1   | _       | High-speed (OSC3) oscillation input (crystal/ceramic oscillator or external |  |  |  |  |  |  |  |

|            |          |           |     |         | clock input)                                                                |  |  |  |  |  |  |  |

| OSC4       | 116      | 113       | 0   | -       | High-speed (OSC3) oscillation output                                        |  |  |  |  |  |  |  |

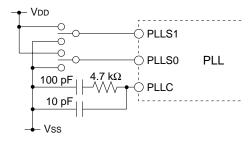

| PLLS[1:0]  | 108,109  | 105,106   | -   | _       | PLL set-up pins                                                             |  |  |  |  |  |  |  |

|            |          |           |     |         | PLLS1 PLLS0 fin (fosc3) fout (fpscin)                                       |  |  |  |  |  |  |  |

|            |          |           |     |         | 1 1 10-30MHz 20-60MHz *1                                                    |  |  |  |  |  |  |  |

|            |          |           |     |         | 10-25MHz 20-50MHz *2                                                        |  |  |  |  |  |  |  |

|            |          |           |     |         | 0 1 10–15MHz 40–60MHz *1                                                    |  |  |  |  |  |  |  |

|            |          |           |     |         | 10–12.5MHz 40–50MHz *2                                                      |  |  |  |  |  |  |  |

|            |          |           |     |         | 0 0 PLL is not used L                                                       |  |  |  |  |  |  |  |

|            |          |           |     |         | *1: ROM-less model with 3.3 V ± 0.3 V operating voltage                     |  |  |  |  |  |  |  |

|            |          |           |     |         | *2: ROM built-in model, or 3.0 V $\pm$ 0.3 V operating voltage              |  |  |  |  |  |  |  |

| PLLC       | 106      | 103       | _   | _       | Capacitor connecting pin for PLL                                            |  |  |  |  |  |  |  |

Table 1.3.6 List of Other Pins

| Pin name   | Pin      | No.       | 1/0 | Pull-down | Function                                                                        |

|------------|----------|-----------|-----|-----------|---------------------------------------------------------------------------------|

| 1 III Hame | QFP5-128 | QFP15-128 | 2   | Pull-up   | Tundon                                                                          |

| ICEMD      | 98       | 95        | 1   | With      | High-impedance control input pin                                                |

|            |          |           |     | pull-down | When this pin is set to High, all the output pins go into high-impedance state. |

|            |          |           |     |           | This makes it possible to disable the E0C33 chip on the board.                  |

| DSIO       | 123      | 120       | I/O | With      | Serial I/O pin for debugging                                                    |

|            |          |           |     | Pull-up   | This pin is used to communicate with the debugging tool ICD33.                  |

| #X2SPD     | 111      | 108       | 1   | _         | Clock doubling mode set-up pin                                                  |

|            |          |           |     |           | 1: CPU clock = bus clock x 1, 0: CPU clock = bus clock x 2                      |

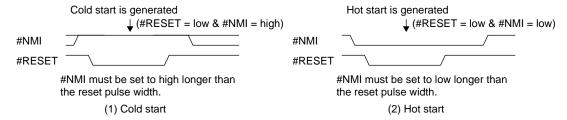

| #NMI       | 66       | 63        | 1   | With      | NMI request input pin                                                           |

|            |          |           |     | Pull-up   |                                                                                 |

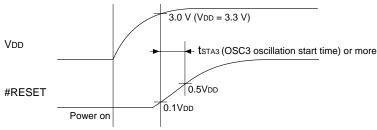

| #RESET     | 65       | 62        | 1   | With      | Initial reset input pin                                                         |

|            |          |           |     | Pull-up   |                                                                                 |

**Note:** "#" in the pin names indicates that the signal is low active.

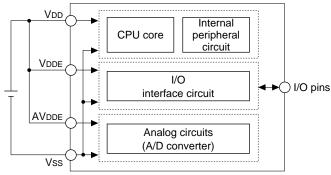

# 2 Power Supply

This chapter explains the operating voltage of the E0C33208/204/202.

### 2.1 Power Supply Pins

The E0C33208/204/202 has the power supply pins shown in Table 2.1.1.

Table 2.1.1 Power Supply Pins

| Pin name   | Pin                      | No.                        | Function                                     |

|------------|--------------------------|----------------------------|----------------------------------------------|

| Till liame | QFP5-128pin              | QFP15-128pin               | i uncuon                                     |

| VDD        | 11,77,114                | 8,74,111                   | Power supply (+) for the internal logic      |

| Vss        | 2,25,42,57,70,93,105,107 | 22,39,54,67,90,102,104,127 | Power supply (-); GND                        |

| VDDE       | 30,50,96                 | 27,47,93                   | Power supply (+) for the I/O block           |

| AVDDE      | 38                       | 35                         | Analog system power supply (+); AVDDE = VDDE |

Figure 2.1.1 Power Supply System

### 2.2 Operating Voltage (VDD)

The core CPU and internal peripheral circuits operate with a voltage supplied between the VDD and Vss pins. The following operating voltage can be used:

$V_{DD} = 1.8 \text{ V to } 3.6 \text{ V (Vss} = GND)$

**Note:** The E0C33208/204/202 has three VDD pins and eight Vss pins. Be sure to supply the operating voltage to all the pins. Do not open any of them.

The operating clock frequency range (OSC3) is 5 MHz to 50 MHz with this voltage.

### 2.3 Power Supply for I/O Interface (VDDE)

The VDDE voltage is used for interfacing with external I/O signals. For the I/O interface of the E0C33208/204/202, the VDDE voltage is used as high level and the VSS voltage as low level.

Normally, supply the same voltage level as VDD. It can be supplied separately from VDD for 5 V interface. The Vss pin is used for the ground common with VDD.

The following voltage is enabled for VDDE:

$V_{DDE} = 1.8 \text{ V to } 5.5 \text{ V (Vss} = GND)$

- **Notes:•** The E0C33208/204/202 has three VDDE pins. Be sure to supply a voltage to all the pins. Do not open any of them.

- When an external clock is input to the OSC1 or OSC3 pin, the clock signal level must be VDD.

- The interface voltage level of the DSIO, P10, P11, P12, P13 and P14 pins is VDD.

### 2.4 Power Supply for Analog Circuits (AVDDE)

The analog power supply pin (AVDDE) is provided separately from the VDD pin in order that the digital circuits do not affect the analog circuit (A/D converter). The AVDDE pin is used to supply an analog power voltage and the Vss pin is used as the analog ground.

Supply the same voltage level as the VDDE to the AVDDE pin.

AVDDE = VDDE (VSS = GND)

**Note:** Be sure to supply VDDE to the AVDDE pin even if the analog circuit is not used.

Noise on the analog power lines decrease the A/D converting precision, so use a stabilized power supply and make the board pattern with consideration given to that.

# 3 Internal Memory

This chapter explains the internal memory configuration.

### **3.1 RAM**

The E0C33208/204/202 has a built-in RAM. Table 3.1.1 shows the size and mapping address.

Table 3.1.1 Built-in RAM

| Model    | Size     | Address    |

|----------|----------|------------|

| E0C33208 | 8K bytes | 0x0-0x1FFF |

| E0C33204 | 4K bytes | 0x0-0x0FFF |

| E0C33202 | 2K bytes | 0x0-0x07FF |

The internal RAM is a 32-bit sized device and data can be read/written in 1 cycle regardless of data size (byte, half-word or word).

Figure 3.1.1 shows the basic internal memory map.

| Area   | Address                | E0C33208                  | E0C33202                 | Bus cycle                | Device size       |           |

|--------|------------------------|---------------------------|--------------------------|--------------------------|-------------------|-----------|

| Area 3 | 0x00FFFFF              |                           |                          |                          |                   |           |

|        |                        | (Reserved)                | (Reserved)               | (Reserved)               |                   |           |

|        |                        | , , , ,                   | , , ,                    | , i                      |                   |           |

|        |                        | For middleware use        | For middleware use       | For middleware use       |                   |           |

|        | 0x0080000              |                           |                          |                          |                   |           |

| Area 2 | 0x007FFFF              |                           |                          |                          | Fixed at 3 cycles | 16 bits   |

|        |                        | (Reserved)                | (Reserved)               | (Reserved)               |                   |           |

|        |                        | For CPU core              | For CPU core             | For CPU core             |                   |           |

|        |                        | or debug mode             | or debug mode            | or debug mode            |                   |           |

|        | 0x0060000              | _                         |                          | _                        |                   |           |

| Area 1 | 0x005FFFF              | (14)                      | (1)                      | (1.1)                    | Fixed at 2 cycles | 8,16 bits |

|        | 0 0050000              | (Mirror of internal I/O)  | (Mirror of internal I/O) | (Mirror of internal I/O) |                   |           |

|        | 0x0050000<br>0x004FFFF |                           |                          |                          |                   |           |

|        | TTTTFOOAU              | Internal I/O              | Internal I/O             | Internal I/O             |                   |           |

|        | 0x0040000              |                           |                          |                          |                   |           |

|        | $0 \times 003 FFFF$    | (Mirror of internal I/O)  | (Mirror of internal I/O) | (Mirror of internal I/O) |                   |           |

|        | 0x0030000              | (Will of a litterial 1/0) | (Will of the first tro)  | (Will of all cornar a c) |                   |           |

| Area 0 | 0x0002FFF              | (Mirror of internal RAM)  |                          |                          | Fixed at 1 cycle  | 32 bits   |

|        | 0x0002000              | ,                         | (Mirror of internal RAM) |                          |                   |           |

|        | 0x0001FFF              |                           |                          | (Mirror of internal RAM) |                   |           |

|        | 0x0001000              |                           |                          |                          |                   |           |

|        | 0x0000FFF              | Internal RAM (8KB)        |                          |                          |                   |           |

|        | 0x0000800<br>0x00007FF |                           | Internal RAM (4KB)       |                          |                   |           |

|        | 0x00007FF              |                           |                          | Internal RAM (2KB)       |                   |           |

|        | 0.00000000             |                           |                          |                          |                   |           |

Figure 3.1.1 Basic Internal Memory Map

Area 2 is used in debug mode only and it cannot be accessed in user mode (normal program execution status).

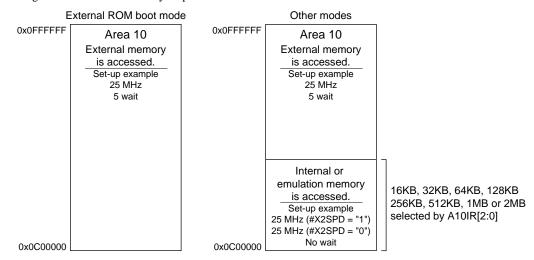

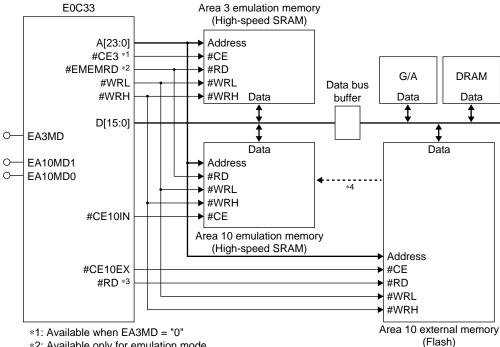

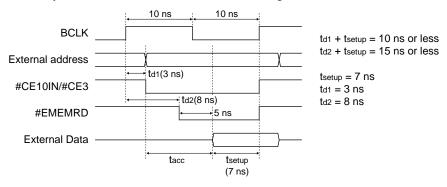

### 3.2 ROM and Boot Address

The E0C33208/204/202 has no built-in ROM. Since the boot address is fixed at 0x0C00000 in the E0C33208/204/202, an external ROM/Flash must be placed from the top of Area 10.

For setting up Area 10, refer to the "BCU (Bus Controller Unit)" section in the "E0C33 Family ASIC Macro Manual".

# 4 Peripheral Circuits

This chapter lists the built-in peripheral circuits and the I/O memory map. For details of the circuits, refer to the "E0C33 Family ASIC Macro Manual".

### 4.1 List of Peripheral Circuits

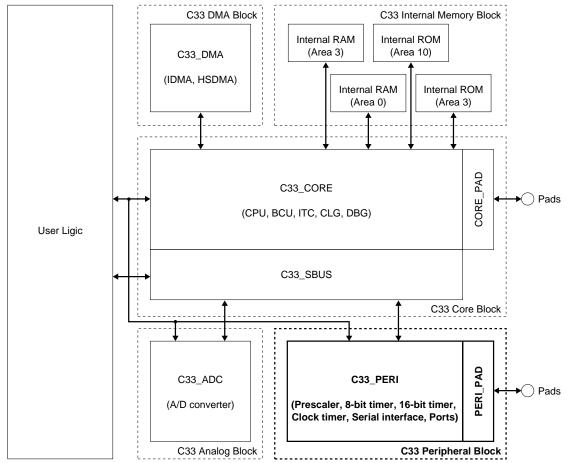

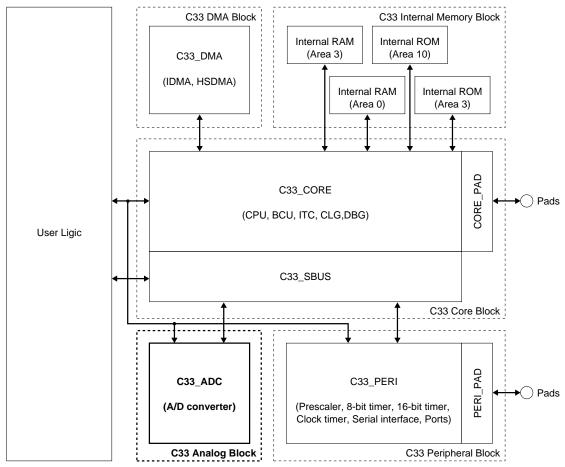

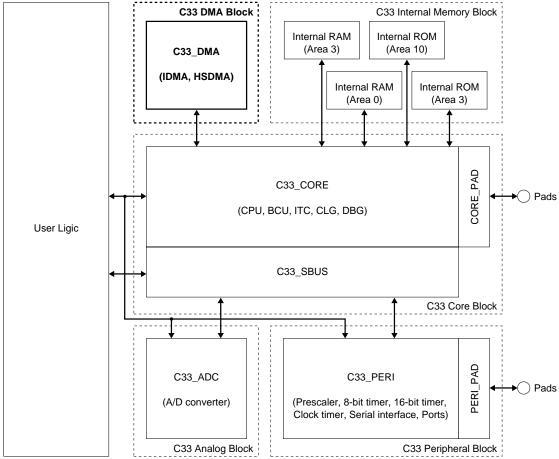

The E0C33208/204/202 consists of the C33 ASIC Macro Blocks: C33 Core Block, C33 Peripheral Block, C33 DMA Block and C33 Analog Block.

#### C33 Core Block

CPU E0C33000 32-bit RISC type CPU

BCU (Bus Control Unit) 24-bit external address bus and 16-bit data bus

All the BCU functions can be used.

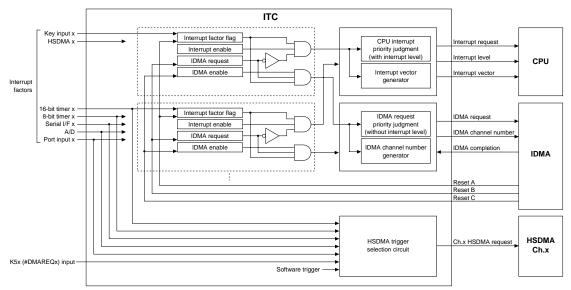

ITC (Interrupt Controller) 39 types of interrupts are available.

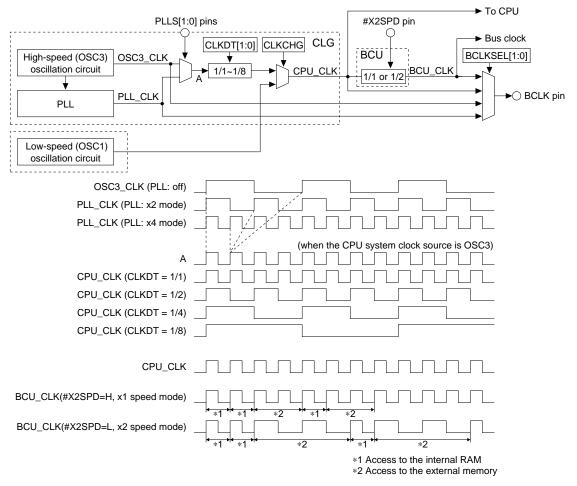

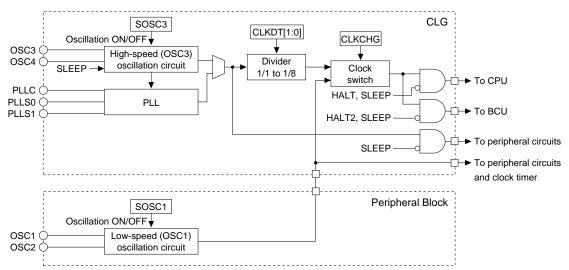

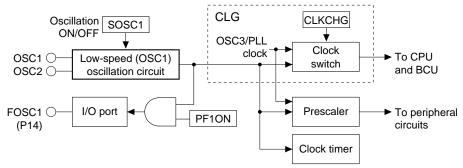

CLG (Clock Generator) OSC3 oscillation circuit (33 MHz Max.), PLL and OSC1 oscillation circuit

(32.768 kHz Typ.) built-in

DBG (Debug Unit) Functional block for debugging with the ICD33 (In-Circuit Debugger for E0C33

Family)

#### C33 Peripheral Block

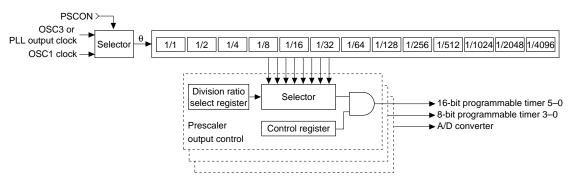

Prescaler Programmable clock generator for peripheral circuits

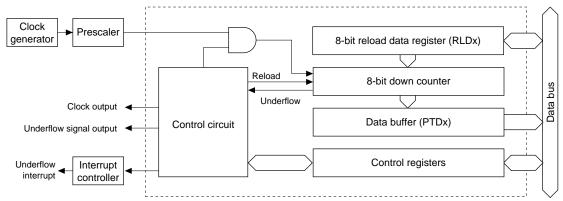

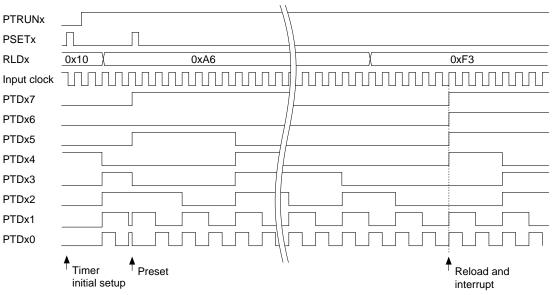

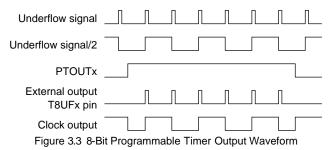

8-bit programmable timer 4 channels with clock output function

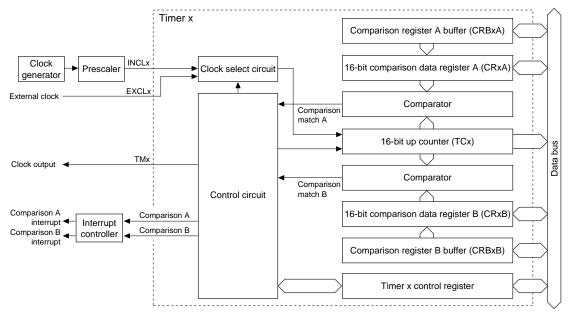

16-bit programmable timer 6 channels with event counter, clock output and watchdog timer functions

Serial interface 2 channels (asynchronous mode, clock synchronous mode and IrDA are

selectable.)

Input and I/O ports 13 bits of input ports and 29 bits of I/O ports (used for peripheral I/O)

Clock timer 1 channel with alarm function

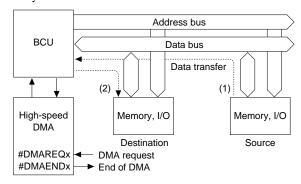

#### C33 DMA Block

HSDMA (High-Speed DMA) 4 channels IDMA (Intelligent DMA) 128 channels

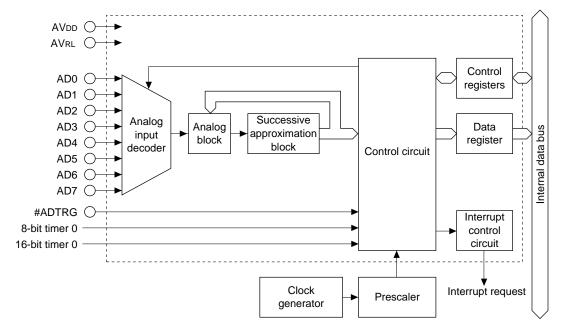

#### C33 Analog Block

A/D converter 10-bit A/D converter with 8 input channels

### 4.2 I/O Memory Map

Table 4.2.1 I/O Memory Map

| Register name  | Address | Bit  | Name    | Function                              | Setting                    | Init. | R/W   | Remarks                |

|----------------|---------|------|---------|---------------------------------------|----------------------------|-------|-------|------------------------|

| 8-bit timer    | 0040146 | D7-4 | _       | reserved                              | _                          | _     | _     | 0 when being read.     |

| clock select   | (B)     | D7-4 | P8TPCK3 | 8-bit timer 3 clock selection         | 1 0 Divided clk.           | 0     | R/W   | θ: selected by         |

| register       | (5)     | D2   | P8TPCK2 | 8-bit timer 2 clock selection         | 1 θ/1 0 Divided clk.       | 0     | R/W   | Prescaler clock selec  |

| . og.oto.      |         | D1   | P8TPCK1 | 8-bit timer 1 clock selection         | 1 θ/1 0 Divided clk.       | 0     | R/W   | register (0x40181)     |

|                |         | D0   | P8TPCK0 | 8-bit timer 0 clock selection         | 1 θ/1 0 Divided clk.       | 0     | R/W   | regioner (ex 10 10 1)  |

| 16-bit timer 0 | 0040147 | D7-4 | _       | reserved                              |                            | _     | _     | 0 when being read.     |

| clock control  | (B)     | D7-4 | P16TON0 | 16-bit timer 0 clock control          | 1 On 0 Off                 | 0     | R/W   | o when being read.     |

| register       | (5)     | D2   | P16TS02 | 16-bit timer 0                        | P16TS0[2:0] Division ratio | 0     | R/W   | θ: selected by         |

| . og.oto.      |         | D1   | P16TS01 | clock division ratio selection        | 1 1 1 0/4096               | 0     |       | Prescaler clock select |

|                |         | D0   | P16TS00 |                                       | 1 1 0 θ/1024               | 0     |       | register (0x40181)     |

|                |         |      |         |                                       | 1 0 1 θ/256                |       |       |                        |

|                |         |      |         |                                       | 1 0 0 θ/64                 |       |       | 16-bit timer 0 can be  |

|                |         |      |         |                                       | 0 1 1 θ/16                 |       |       | used as a watchdog     |

|                |         |      |         |                                       | 0 1 0 θ/4                  |       |       | timer.                 |

|                |         |      |         |                                       | 0 0 1 θ/2                  |       |       |                        |

|                |         |      |         |                                       | 0 0 0 θ/1                  |       |       |                        |

| 16-bit timer 1 | 0040148 | D7-4 | -       | reserved                              | -                          | -     | _     | 0 when being read.     |

| clock control  | (B)     | D3   | P16TON1 | 16-bit timer 1 clock control          | 1 On 0 Off                 | 0     | R/W   |                        |

| register       |         | D2   | P16TS12 | 16-bit timer 1                        | P16TS1[2:0] Division ratio | 0     | R/W   | θ: selected by         |

|                |         | D1   | P16TS11 | clock division ratio selection        | 1 1 1 θ/4096               | 0     |       | Prescaler clock select |

|                |         | D0   | P16TS10 |                                       | 1 1 0 θ/1024               | 0     |       | register (0x40181)     |

|                |         |      |         |                                       | 1 0 1 0/256                |       |       |                        |