# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER **E0C33A104 TECHNICAL MANUAL**

# E0C33A104 Technical Hardware

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

### CONTENTS

| 1 Outline                                                            | 1  |

|----------------------------------------------------------------------|----|

| 1.1 Features                                                         | 1  |

| 1.2 Block Diagram                                                    |    |

| 1.3 Pin Description                                                  |    |

|                                                                      |    |

| 1.3.2 Pin Functions                                                  | 6  |

| 2 Power Supply and I/O Level                                         | 8  |

| 2.1 Power Supply                                                     | 8  |

| 2.1.1 Power Supply Pins                                              |    |

| 2.1.2 Operating Voltage (VDD)                                        |    |

| 2.1.3 Power Supply for Clock (VDD1)                                  |    |

| 2.1.4 Power Supply for Analog Circuits (AVDD, AVSS)<br>2.2 I/O Level |    |

|                                                                      |    |

| 3 Initial Reset                                                      |    |

| 3.1 Pins for Initial Reset                                           | 10 |

| 3.2 Cold Start and Hot Start                                         | 10 |

| 3.3 Power-on Reset                                                   |    |

| 3.4 Reset Pulse                                                      | 11 |

| 3.5 Boot Address                                                     | 12 |

| 3.6 Notes Related to Initial Reset                                   | 12 |

| 4 CPU and Operating Modes                                            | 14 |

| 4.1 CPU                                                              | 14 |

| 4.2 Standby Mode                                                     | 15 |

| 4.2.1 HALT Mode                                                      | 15 |

| 4.2.2 SLEEP Mode                                                     |    |

| 4.2.3 Notes on Standby Mode                                          |    |

| 4.3 Test Mode                                                        |    |

| 4.4 High-impedance Mode                                              | 17 |

| 4.5 Debug Mode                                                       | 17 |

| 5 Address Space                                                      | 18 |

| 5.1 Memory Map                                                       | 18 |

| 5.2 I/O Map for Internal Peripheral Circuits                         | 19 |

| 6 Internal Memory                                                    | 44 |

| 6.1 RAM                                                              | 44 |

| 6.2 ARAM                                                             | 45 |

| 6.2.1 Expanded RAM Mode                                              | 45 |

| 7 External System Interface                                          | 46 |

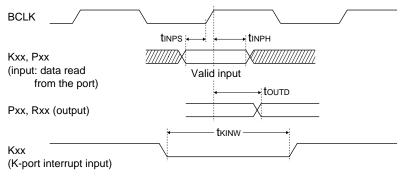

| 7.1 Pin Assignment for External System Interface                     |    |

| 7.1.1 I/O Pin List                                                   |    |

| 7.1.2 Combination of System Bus Control Signals                      |    |

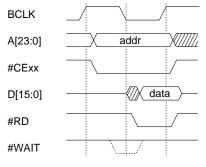

| 7.2 External Memory Map and Chip Enable Switchover                   |    |

| 7.3 Setting External Bus Conditions                                  |    |

| 7.3.1 Setting Device Type and Size                                   |    |

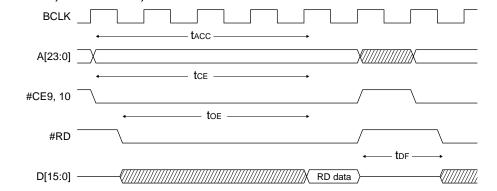

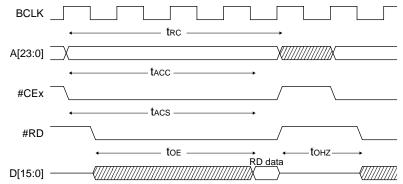

| 7.3.2 Setting SRAM Timing Conditions                                 |    |

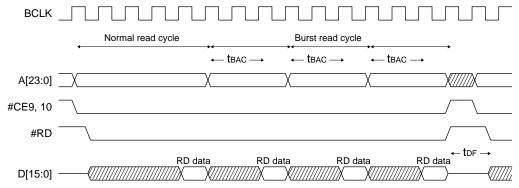

|      | 7.3.3 Setting Timing Conditions of Burst ROM              | 51  |

|------|-----------------------------------------------------------|-----|

|      | 7.4 Bus Operation                                         |     |

|      | 7.4.1 Data Arrangement in Memory                          |     |

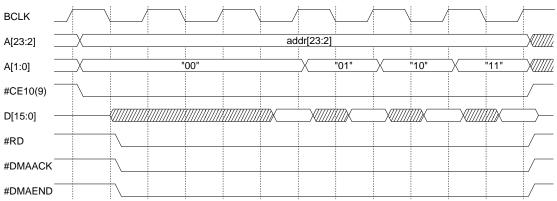

|      | 7.4.2 Bus Operation of External Memory                    | 52  |

|      | 7.4.3 Bus Clock                                           | 54  |

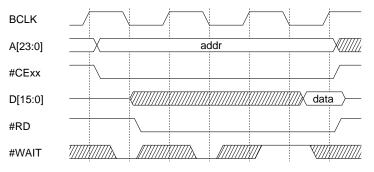

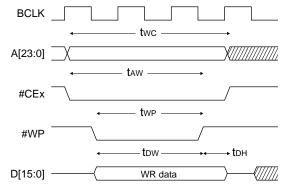

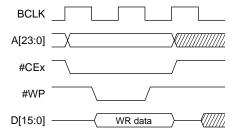

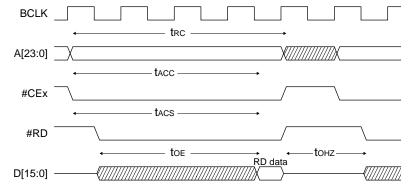

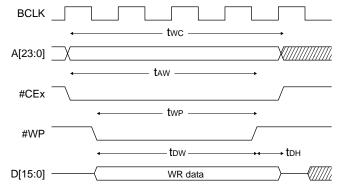

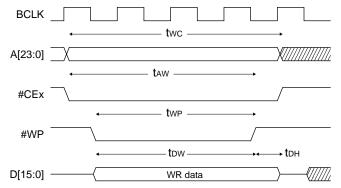

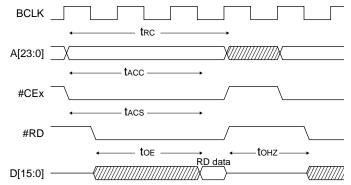

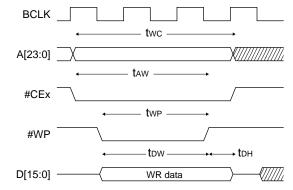

|      | 7.5 Bus Cycles in External System Interface               | 55  |

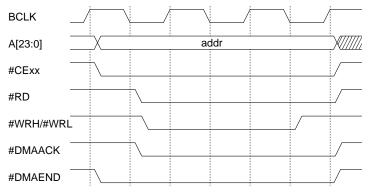

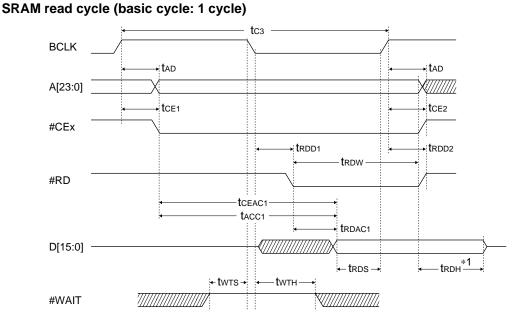

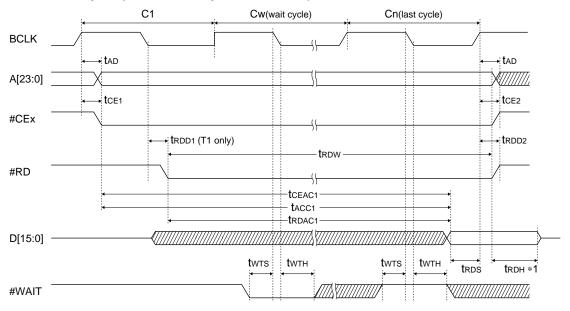

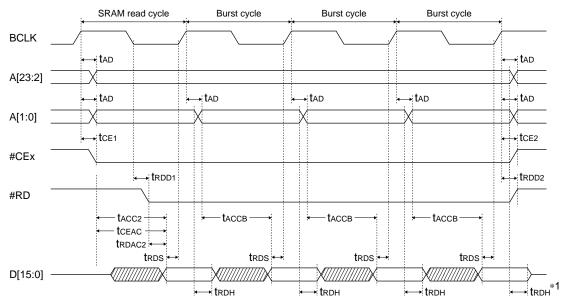

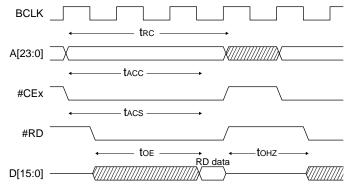

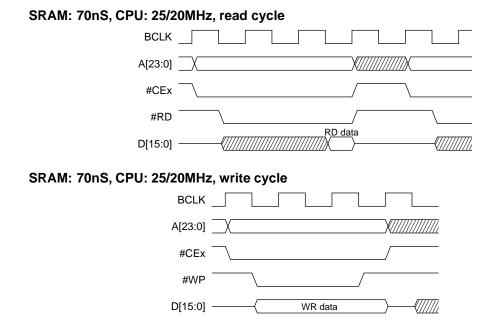

|      | 7.5.1 SRAM Read Cycles                                    |     |

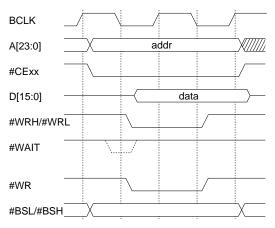

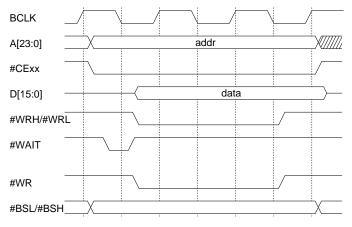

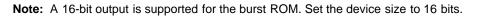

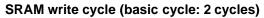

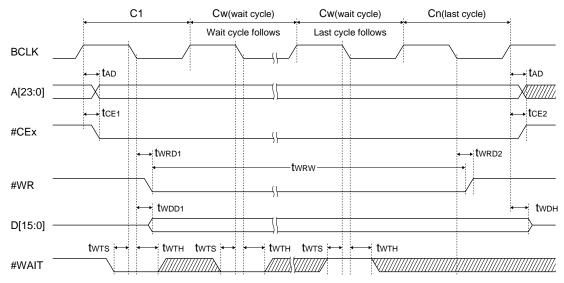

|      | 7.5.2 SRAM Write Cycles                                   | 56  |

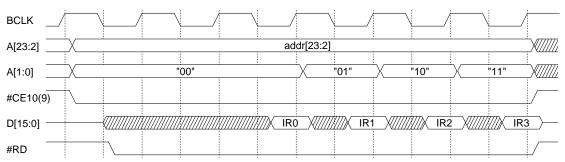

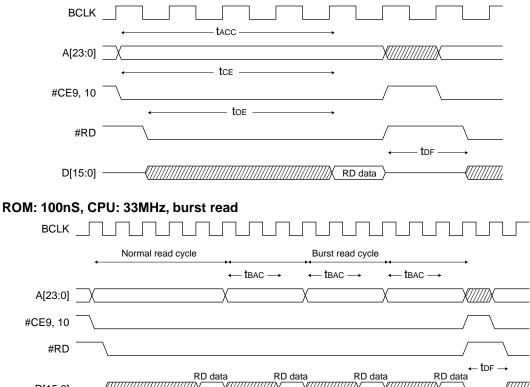

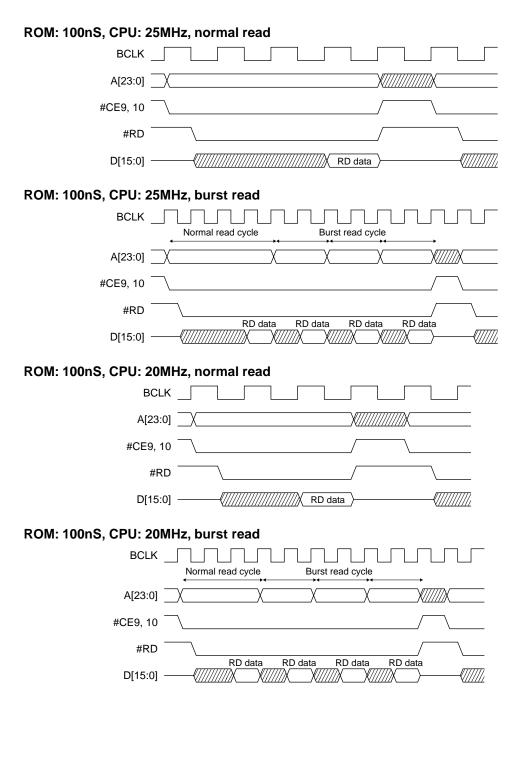

|      | 7.5.3 Burst ROM Read Cycles                               | 57  |

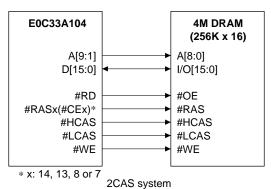

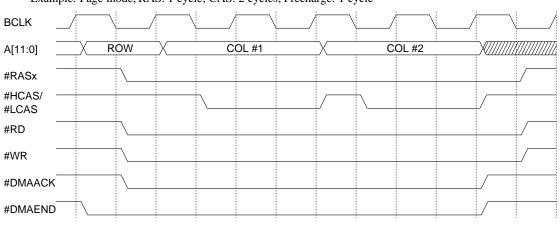

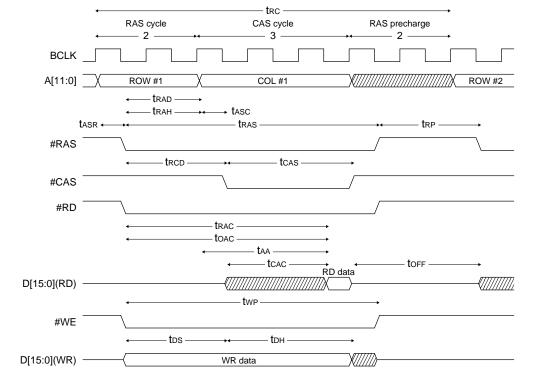

|      | 7.6 DRAM Direct Interface                                 |     |

|      | 7.6.1 Outline of DRAM Interface                           |     |

|      | 7.6.2 DRAM Setting Conditions                             | 59  |

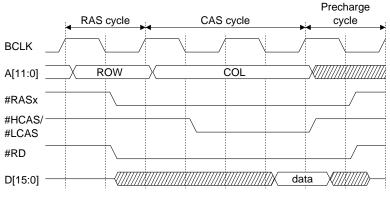

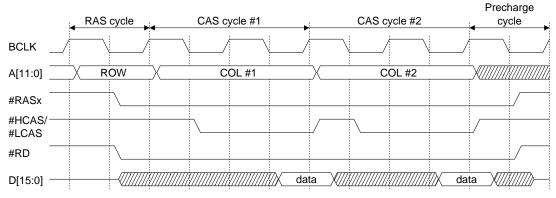

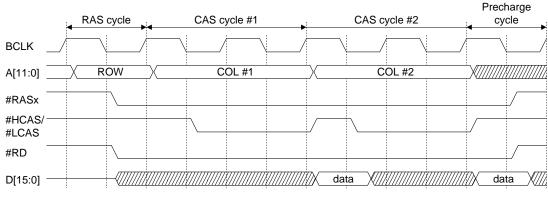

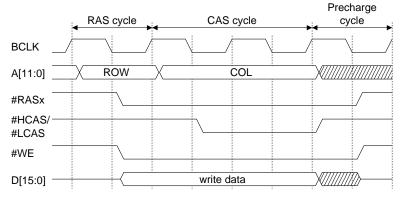

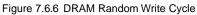

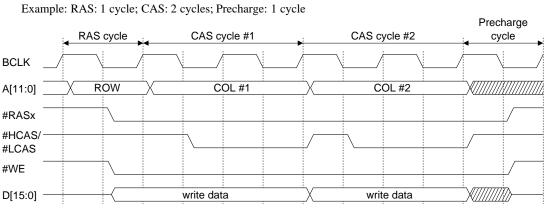

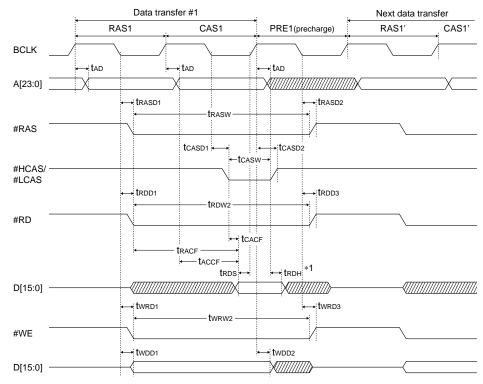

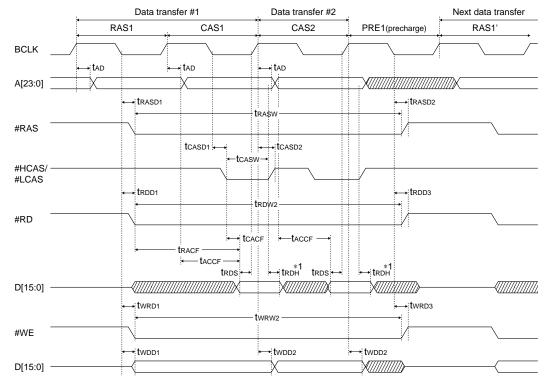

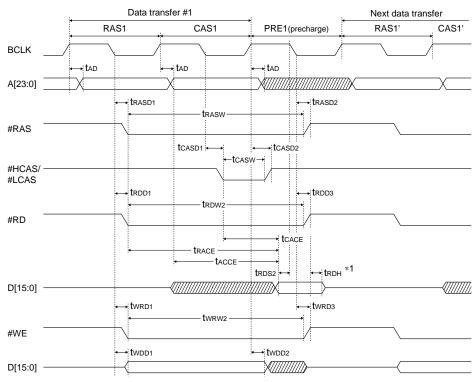

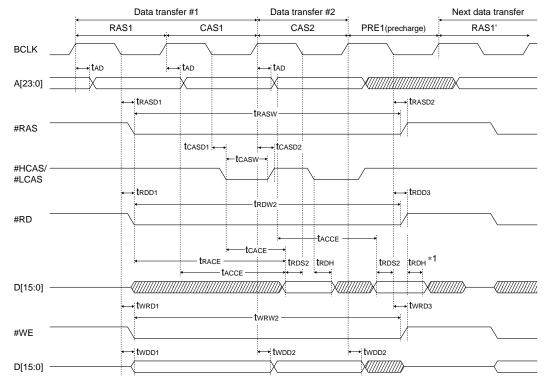

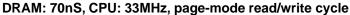

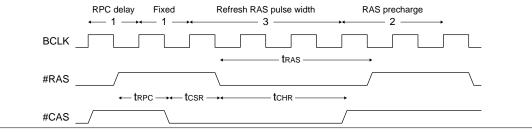

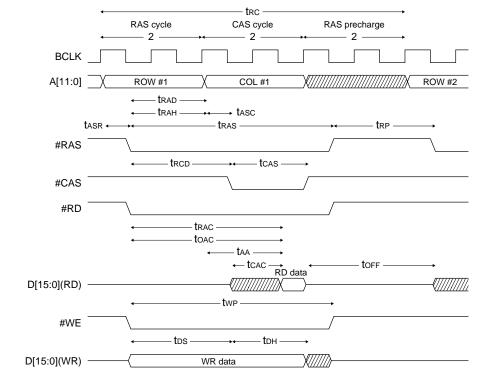

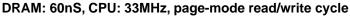

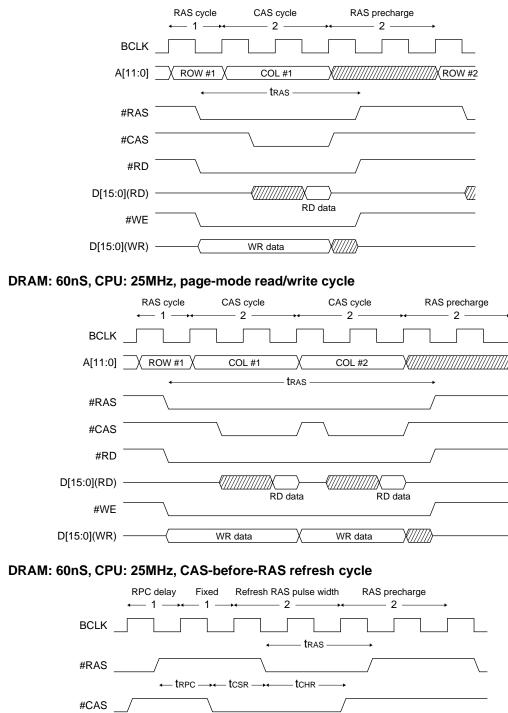

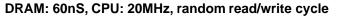

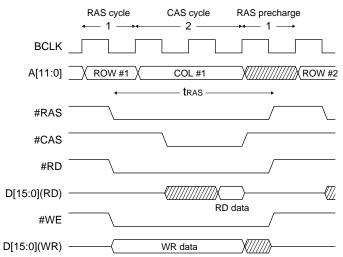

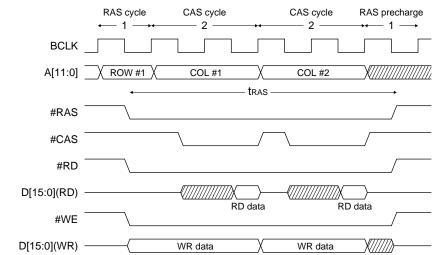

|      | 7.6.3 DRAM Read/Write Cycles                              | 62  |

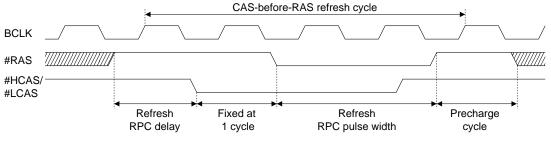

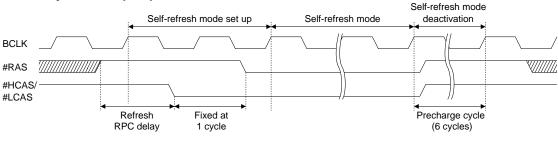

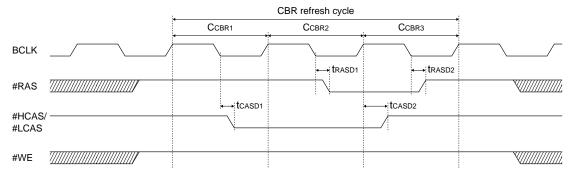

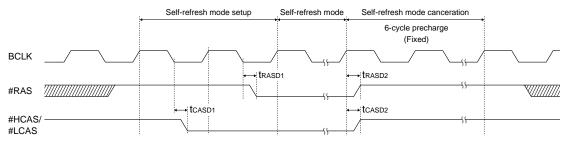

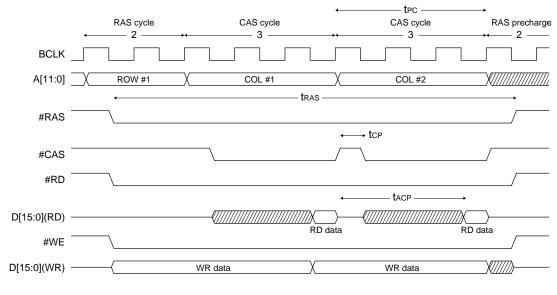

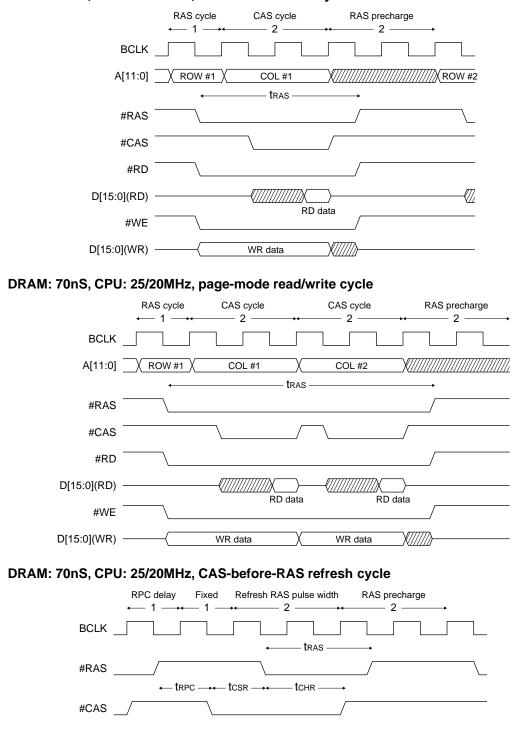

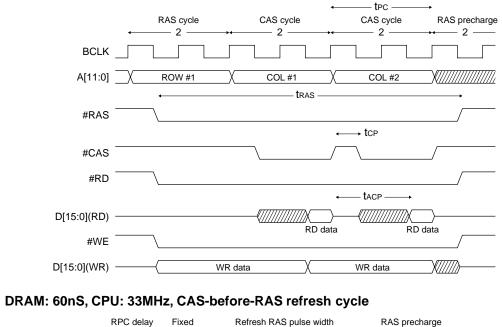

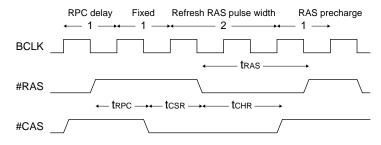

|      | 7.6.4 DRAM Refresh Cycles                                 | 65  |

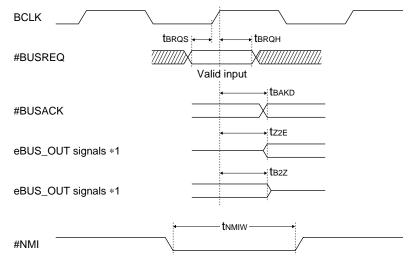

|      | 7.7 Releasing External Bus                                | 66  |

|      | 7.8 Power-down Control by External Device                 |     |

|      | 7.9 I/O Memory of External System Interface               |     |

|      |                                                           |     |

|      | 7.10 Programming Note                                     |     |

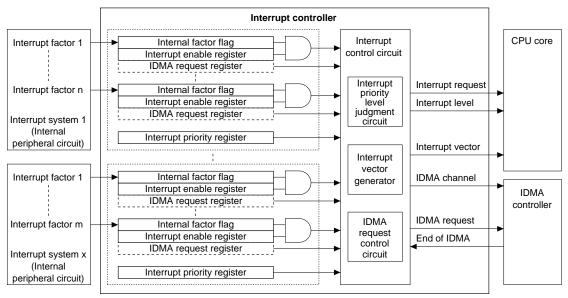

| 8 Ir | nterrupt                                                  | 78  |

|      | 8.1 Outline of Interrupt Functions                        |     |

|      | 8.1.1 Maskable Interrupts                                 |     |

|      | 8.1.2 Interrupt Factors and Intelligent DMA               |     |

|      | 8.1.3 Nonmaskable Interrupt (NMI)                         |     |

|      | 8.1.4 Interrupt Processing by the CPU                     |     |

|      | 8.1.5 Clearing Standby Mode by Interrupts                 | 80  |

|      | 8.2 Trap Table                                            | 81  |

|      | 8.3 Control of Maskable Interrupts                        |     |

|      | 8.3.1 Structure of the Interrupt Controller               |     |

|      | 8.3.2 Processor Status Register (PSR)                     |     |

|      | 8.3.3 Interrupt Factor Flag and Interrupt Enable Register |     |

|      | 8.3.4 Interrupt Priority Register and Interrupt Levels    |     |

|      | 8.4 IDMA Request Register and IDMA Invocation             |     |

|      | 8.5 I/O Memory of Interrupt Controller                    |     |

|      | 8.6 Programming Notes                                     |     |

|      | 8.6 Programming Notes                                     |     |

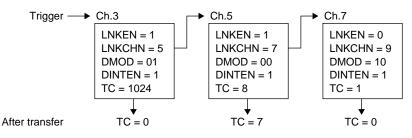

| 9 D  | MA Controller                                             | 94  |

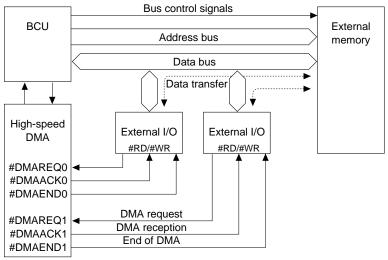

|      | 9.1 High-Speed DMA                                        | 94  |

|      | 9.1.1 Functional Outline of High-Speed DMA                |     |

|      | 9.1.2 I/O Pins of High-Speed DMA                          | 95  |

|      | 9.1.3 Setting High-Speed DMA                              | 96  |

|      | 9.1.4 Operation of High-Speed DMA                         | 98  |

|      | 9.1.5 Interrupt Function of High-Speed DMA                | 100 |

|      | 9.1.6 I/O Memory of High-Speed DMA                        |     |

|      | 9.1.7 Programming Notes                                   | 108 |

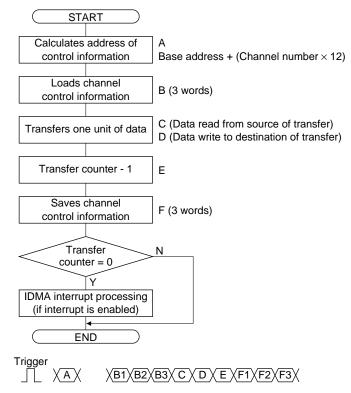

|      | 9.2 Intelligent DMA                                       | 109 |

|      | 9.2.1 Functional Outline of Intelligent DMA               | 109 |

|      | 9.2.2 Programming Control Information                     |     |

|      | 9.2.3 IDMA Invocation                                     | 112 |

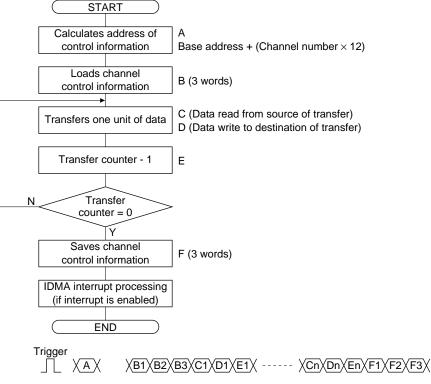

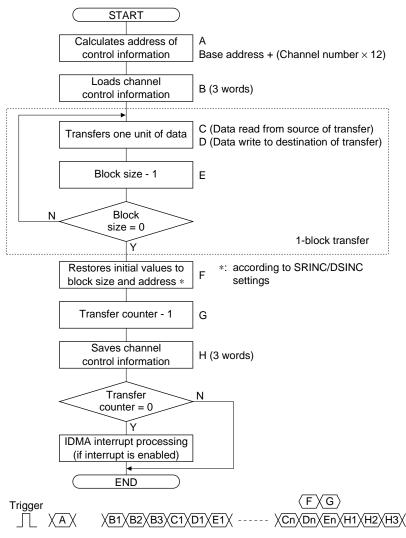

|      | 9.2.4 Operation of IDMA                                   |     |

|      | 9.2.5 Linking                                             |     |

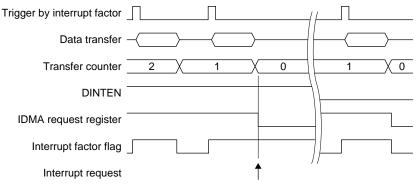

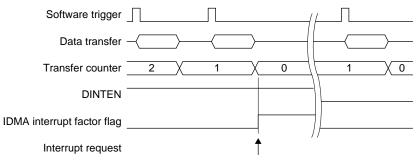

|      | 9.2.6 Interrupt Function of Intelligent DMA               | 120 |

#### CONTENTS

| 9.2.7 I/O Memory of Intelligent DMA                              |  |

|------------------------------------------------------------------|--|

| 9.2.8 Programming Notes                                          |  |

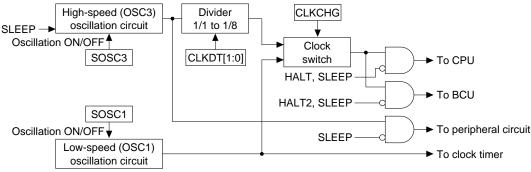

| 10 Oscillation Circuits and Clock Control                        |  |

| 10.1 Oscillation Circuits                                        |  |

| 10.1.1 Configuration of Oscillation Circuits                     |  |

| 10.1.2 I/O Pins of Oscillation Circuits                          |  |

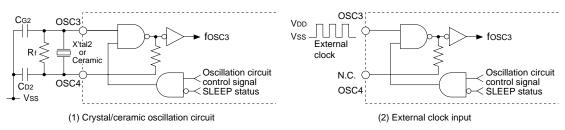

| 10.1.3 High-Speed (OSC3) Oscillation Circuit                     |  |

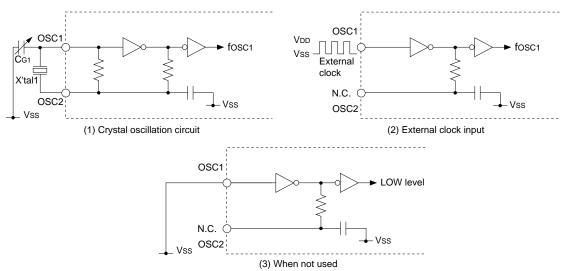

| 10.1.4 Low-Speed (OSC1) Oscillation Circuit                      |  |

| 10.1.5 Controlling Oscillation                                   |  |

| 10.1.6 Setting and Switching Over the CPU Operating Clock        |  |

| 10.1.7 Power-Control Register Protection Flag                    |  |

| 10.1.8 Operation in Standby Mode                                 |  |

| 10.1.9 OSC1 Clock Output to External Devices                     |  |

| 10.1.10 I/O Memory of Oscillation Circuits                       |  |

| 10.1.11 Programming Notes                                        |  |

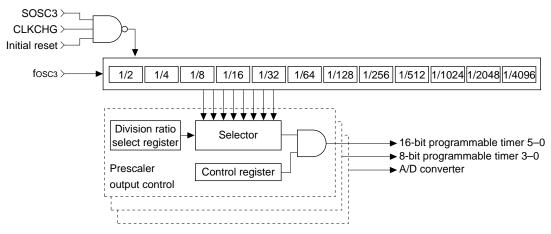

| 10.2 Prescaler and Operating Clock for Peripheral Circuits       |  |

| 10.2 Prescaler and Operating Clock for Peripheral Circuits       |  |

| 10.2.2 Source Clock                                              |  |

| 10.2.3 Selecting Division Ratio and Output Control for Prescaler |  |

| 10.2.4 I/O Memory of Prescaler                                   |  |

| 10.2.5 Programming Notes                                         |  |

|                                                                  |  |

| 11 Timers                                                        |  |

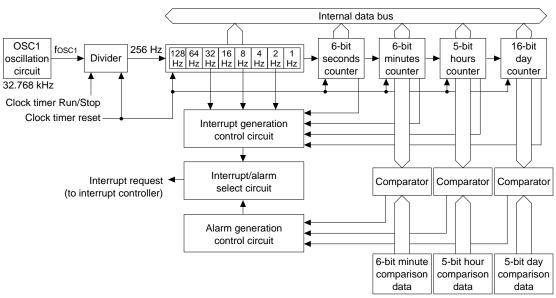

| 11.1 Clock Timer                                                 |  |

| 11.1.1 Configuration of Clock Timer                              |  |

| 11.1.2 Control and Operation of the Clock Timer                  |  |

| 11.1.3 Interrupt Function                                        |  |

| 11.1.4 OSC1 Auto-Off Function                                    |  |

| 11.1.5 Retention of System (CPU) Power-Supply On/Off Data        |  |

| 11.1.6 Examples of Use of Clock Timer                            |  |

| 11.1.7 I/O Memory of Clock Timer                                 |  |

| 11.1.8 Programming Notes                                         |  |

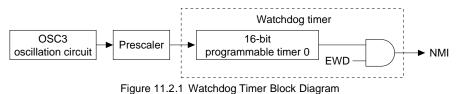

| 11.2 Watchdog Timer                                              |  |

| 11.2.1 Configuration of Watchdog Timer                           |  |

| 11.2.2 Control of Watchdog Timer                                 |  |

| 11.2.3 Operation in Standby Modes                                |  |

| 11.2.4 I/O Memory of Watchdog Timer                              |  |

| 11.2.5 Programming Notes                                         |  |

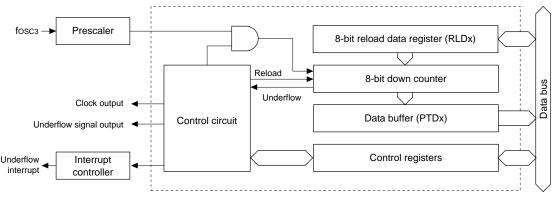

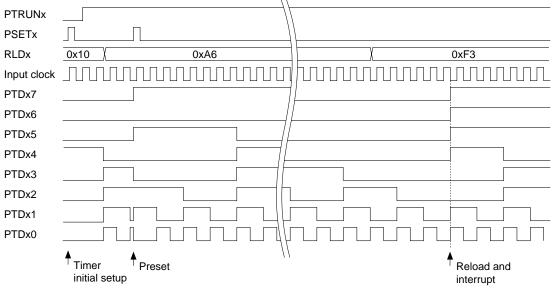

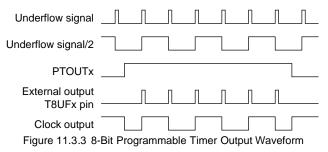

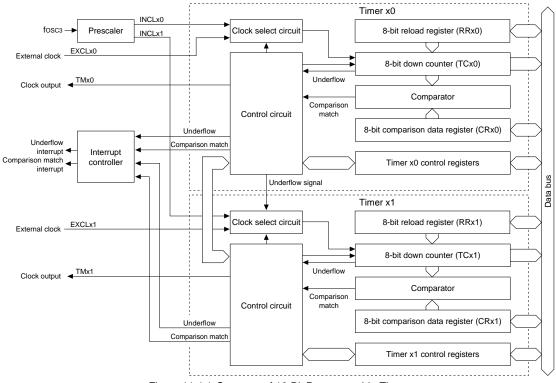

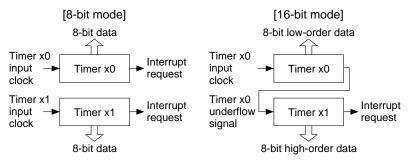

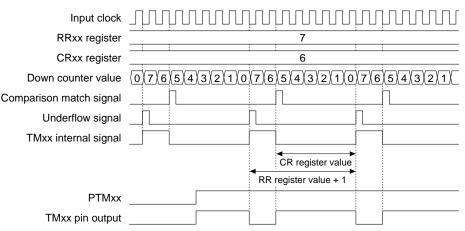

| 11.3 8-Bit Programmable Timers                                   |  |

| 11.3.1 Configuration of 8-Bit Programmable Timer                 |  |

| 11.3.2 Output Pins of 8-Bit Programmable Timers                  |  |

| 11.3.3 Uses of 8-Bit Programmable Timers                         |  |

| 11.3.4 Control and Operation of 8-Bit Programmable Timer         |  |

| 11.3.5 Control of Clock Output                                   |  |

| 11.3.6 8-Bit Programmable Timer Interrupts and DMA               |  |

| 11.3.7 I/O Memory of 8-Bit Programmable Timers                   |  |

| 11.3.8 Programming Notes                                         |  |

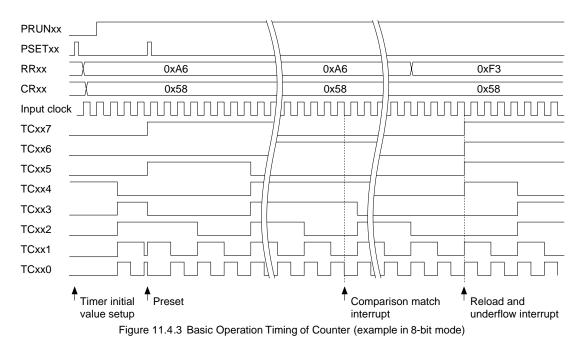

| 11.4 16-Bit Programmable Timers                                  |  |

| 11.4.1 Configuration of 16-Bit Programmable Timer                |  |

| 11.4.2 I/O Pins of 16-Bit Programmable Timers                    |  |

| 11.4.3 Uses of 16-Bit Programmable Timers                        |  |

| 11.4.4 Operation Modes of 16-Bit Programmable Timers             |  |

| 11.4.5 Control and Operation of 16-Bit Programmable Timer        |  |

| 11.4.7 16-Bit Programmable Timer Interrupts and DMA                                                                 |            |

|---------------------------------------------------------------------------------------------------------------------|------------|

| 11.4.8 I/O Memory of 16-Bit Programmable Timers                                                                     |            |

| 11.4.9 Programming Notes                                                                                            |            |

|                                                                                                                     |            |

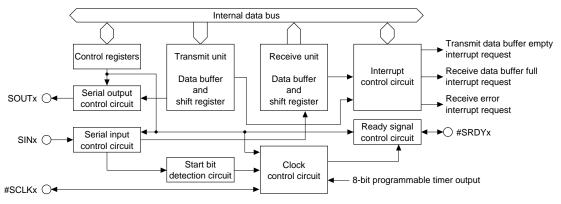

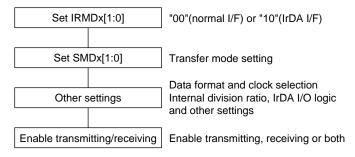

| 12 Serial Interface                                                                                                 |            |

| 12.1 Configuration of Serial Interfaces                                                                             |            |

| 12.1.1 Features of Serial Interfaces                                                                                |            |

| 12.1.2 I/O Pins of Serial Interface                                                                                 |            |

| 12.1.3 Setting Transfer Mode                                                                                        |            |

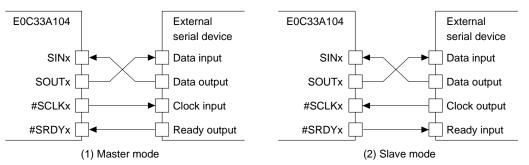

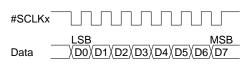

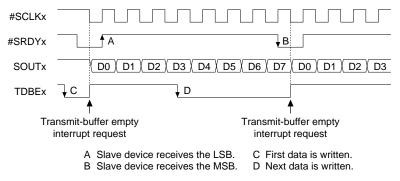

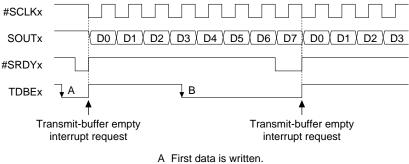

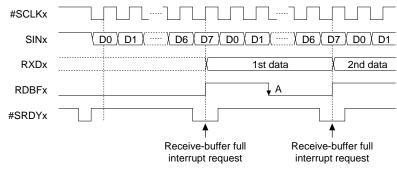

| 12.2 Clock-Synchronized Interface                                                                                   | 205        |

| 12.2.1 Outline of Clock-Synchronized Interface                                                                      |            |

| 12.2.2 Setting Clock-Synchronized Interface                                                                         |            |

| 12.2.3 Control and Operation of Clock-Synchronized Transfer                                                         |            |

|                                                                                                                     |            |

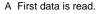

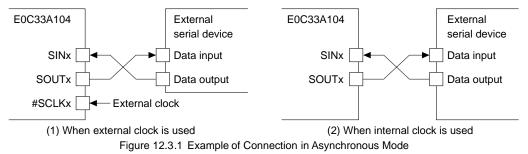

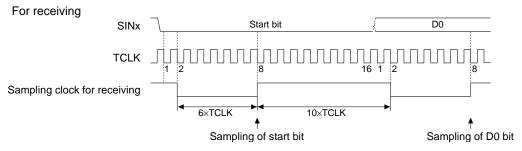

| 12.3 Asynchronous Interface                                                                                         |            |

| 12.3.1 Outline of Asynchronous Interface                                                                            |            |

| 12.3.2 Setting Asynchronous Interface                                                                               |            |

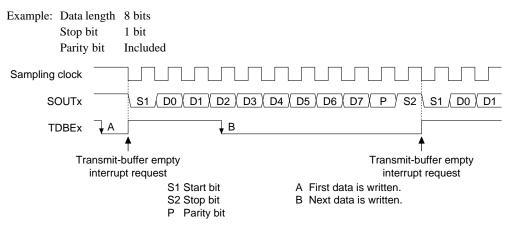

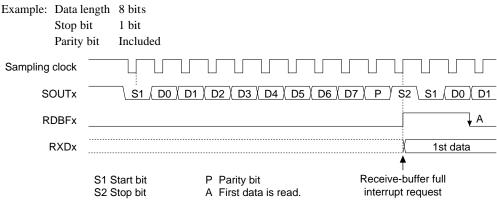

| 12.3.3 Control and Operation of Asynchronous Transfer                                                               |            |

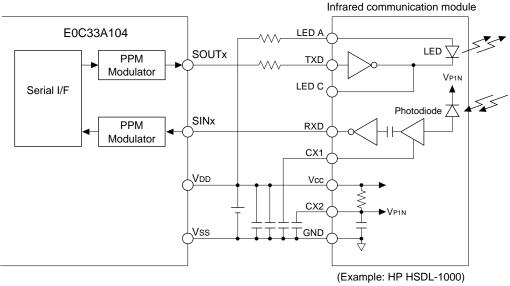

| 12.4 IrDA Interface                                                                                                 |            |

| 12.4.1 Outline of IrDA Interface                                                                                    |            |

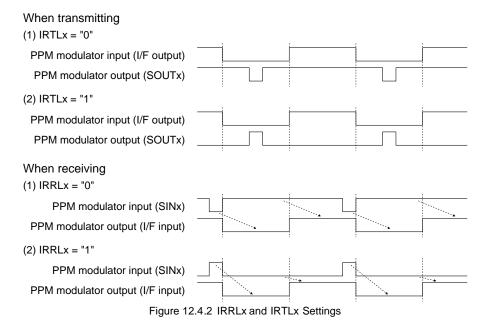

| 12.4.2 Setting IrDA Interface                                                                                       |            |

| 12.4.3 Control and Operation of IrDA Interface                                                                      |            |

| 12.5 Serial Interface Interrupts and DMA                                                                            |            |

| 12.6 I/O Memory of Serial Interface                                                                                 |            |

| -                                                                                                                   |            |

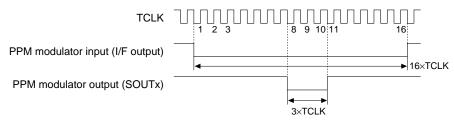

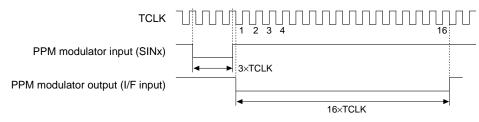

| 12.7 Programming Notes                                                                                              | 234        |

| 13 A/D and D/A Converters                                                                                           |            |

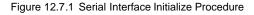

| 13.1 A/D Converter                                                                                                  |            |

| 13.1.1 Features and Structure of A/D Converter                                                                      |            |

| 13.1.2 I/O Pins of A/D Converter                                                                                    |            |

| 13.1.3 Setting A/D Converter                                                                                        |            |

| 13.1.4 Control and Operation of A/D Conversion                                                                      |            |

| 13.1.4 Control and Operation of A/D Conversion                                                                      |            |

| 12.1.5 $\Lambda/D$ Converter Interrupt and DMA                                                                      | 242        |

| 13.1.5 A/D Converter Interrupt and DMA                                                                              |            |

| 13.1.6 I/O Memory of A/D Converter                                                                                  |            |

| 13.1.6 I/O Memory of A/D Converter<br>13.1.7 Programming Notes                                                      | 244<br>250 |

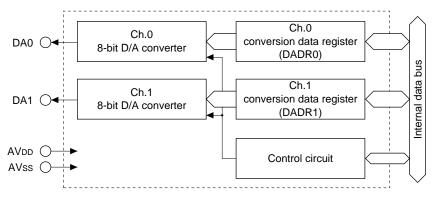

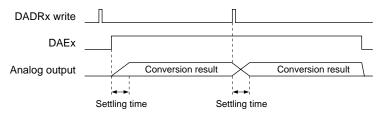

| 13.1.6 I/O Memory of A/D Converter<br>13.1.7 Programming Notes<br>13.2 D/A Converter                                |            |

| 13.1.6 I/O Memory of A/D Converter<br>13.1.7 Programming Notes                                                      |            |

| 13.1.6 I/O Memory of A/D Converter<br>13.1.7 Programming Notes<br>13.2 D/A Converter                                |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li> <li>13.1.7 Programming Notes</li> <li>13.2 D/A Converter</li></ul> |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li> <li>13.1.7 Programming Notes</li> <li>13.2 D/A Converter</li></ul> |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               |            |

| <ul> <li>13.1.6 I/O Memory of A/D Converter</li></ul>                                                               | 244<br>    |

#### CONTENTS

| 14.2.3 I/O Memory of Output Ports                                    |     |

|----------------------------------------------------------------------|-----|

| 14.2.4 Programming Note                                              | 270 |

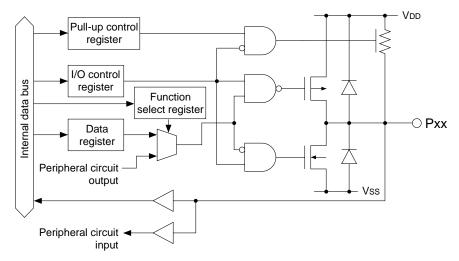

| 14.3 I/O Ports (P Ports)                                             |     |

| 14.3.1 Structure of I/O Port                                         | 271 |

| 14.3.2 I/O Port Pins                                                 |     |

| 14.3.3 I/O Control Register and I/O Modes                            |     |

| 14.3.4 Pull-Up Resistors                                             |     |

| 14.3.5 I/O Memory of I/O Ports                                       |     |

| 14.3.6 Programming Notes                                             |     |

| 15 Power-Down Control                                                |     |

| 16 Basic External Wiring Diagram                                     |     |

| 17 Precautions on Mounting                                           |     |

| 18 Electrical Characteristics                                        |     |

| 18.1 Absolute Maximum Rating                                         |     |

| 18.2 Recommended Operating Conditions                                |     |

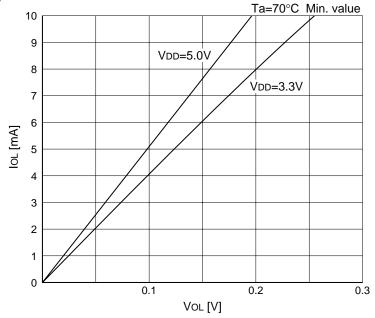

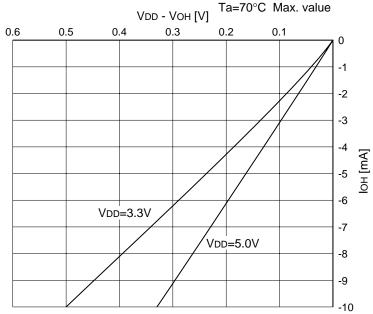

| 18.3 DC Characteristics                                              |     |

| 18.4 Current Consumption                                             |     |

| 18.5 A/D Converter Characteristics                                   |     |

| 18.6 D/A Converter Characteristics                                   |     |

| 18.7 AC Characteristics                                              |     |

| 18.7.1 Symbol Description                                            |     |

| 18.7.2 AC Characteristics Measurement Condition                      |     |

| 18.7.3 AC Characteristic Tables                                      |     |

| 18.7.4 AC Characteristic Timing Charts                               |     |

| 18.8 Oscillation Characteristics                                     |     |

| 18.9 Characteristic Curves                                           |     |

| 19 Package                                                           |     |

| 19.1 Plastic Package                                                 |     |

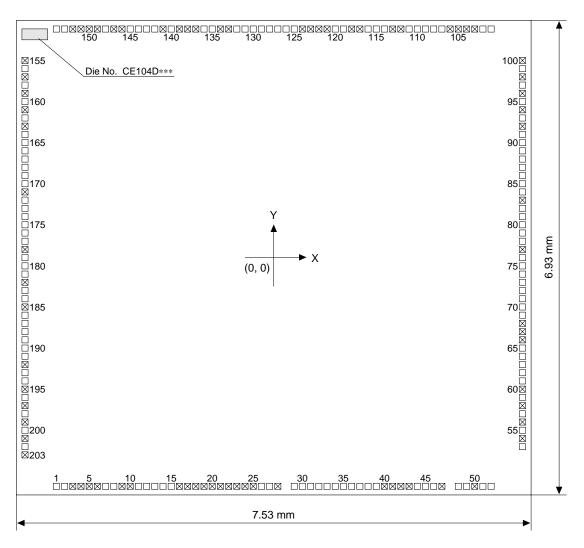

| 20 Pad Layout                                                        |     |

| 20.1 Pad Layout Diagram                                              |     |

| 20.2 Pad Coordinate                                                  |     |

| Appendix A <reference> External Device Interface Timings</reference> |     |

| A.1 Interface Timing Examples for 5V Operation                       |     |

| A.1.1 DRAM (70nS)                                                    |     |

| A.1.2 DRAM (60nS)                                                    |     |

| A.1.3 ROM and Burst ROM                                              |     |

| A.1.4 SRAM (55nS)                                                    |     |

| A.1.5 SRAM (70nS)                                                    |     |

| A.1.6 8255A                                                          |     |

| A.2 Interface Timing Examples for 3.3V Operation                     |     |

| A.2.1 ROM and Burst ROM                                              |     |

| A.2.2 SRAM (150nS)<br>A.2.3 SRAM (100nS)                             |     |

|                                                                      |     |

| Appendix B Summary of Notes                                          | ວ24 |

# 1 Outline

The E0C33A104 is a Seiko Epson original 32-bit microcomputer that features low power and low-voltage operation. It is designed for portable equipment that needs advanced data processing.

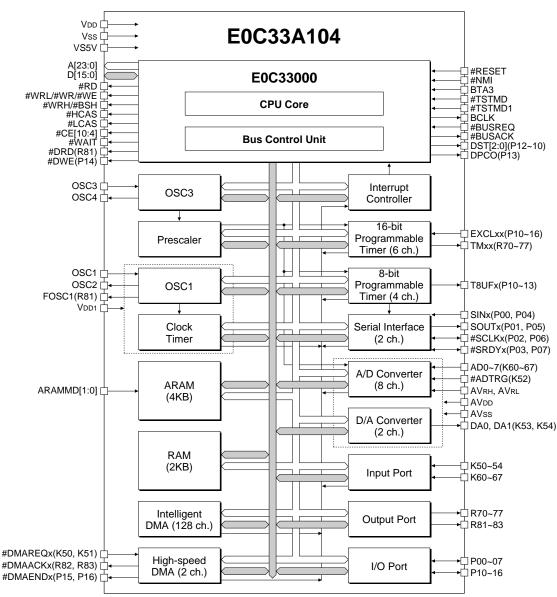

The E0C33A104 consists of the E0C33000 32-bit RISC type CPU as the core, a bus control unit, a DMA controller, an interrupt controller, timers, serial interface circuits, A/D converter, D/A converter, and RAM. It also includes two oscillation circuits that generate high-speed and low-speed operating clocks allowing high-speed operation and low-power operation and a clock timer that provides excellent clock functions.

The E0C33A104 also provides a DSP function, by using the internal MAC (multiplication and accumulation) operation function with the A/D converter, it makes it possible to design simply speech recognition and voice synthesis systems.

# 1.1 Features

### Core CPU

Seiko Epson original 32-bit RISC CPU E0C33000 built-in

- Basic instruction set: 105 instructions (16-bit fixed size)

- Sixteen 32-bit general-purpose register

- 32-bit ALU and 8-bit shifter

- Multiplication/division instructions and MAC (multiplication and accumulation) instruction are available

- 30 ns of minimum instruction execution time at 33 MHz operation

#### Internal memory

RAM: 2K bytes ARAM: 4K bytes (used as internal RAM)

#### Internal peripheral circuits

| Oscillation circuit:  | High-speed (OSC3) oscillation circuit 33 MHz max.    |                                  |  |  |  |  |  |  |

|-----------------------|------------------------------------------------------|----------------------------------|--|--|--|--|--|--|

|                       | Crystal/ceramic oscillator or external clock input   |                                  |  |  |  |  |  |  |

|                       | Low-speed (OSC1) oscillation circuit 32.768 kHz typ. |                                  |  |  |  |  |  |  |

|                       | Crystal oscillator or externa                        | al clock input                   |  |  |  |  |  |  |

| Timers:               | 8-bit timer 4 channels                               |                                  |  |  |  |  |  |  |

|                       | 16-bit timer 6 channels                              |                                  |  |  |  |  |  |  |

|                       | Watchdog timer                                       |                                  |  |  |  |  |  |  |

|                       | Clock timer 1 channel (with ala                      | arm function)                    |  |  |  |  |  |  |

| Serial interface:     | 2 channels (clock-synchronous syste                  | em, asynchronous system and IrDA |  |  |  |  |  |  |

|                       | interface are selectable)                            |                                  |  |  |  |  |  |  |

| A/D converter:        | 10 bits $\times$ 8 channels                          |                                  |  |  |  |  |  |  |

| D/A converter:        | 8 bits $\times$ 2 channels                           |                                  |  |  |  |  |  |  |

| DMA controller:       | High-speed DMA 2 channels                            |                                  |  |  |  |  |  |  |

|                       | Intelligent DMA 128 channels                         |                                  |  |  |  |  |  |  |

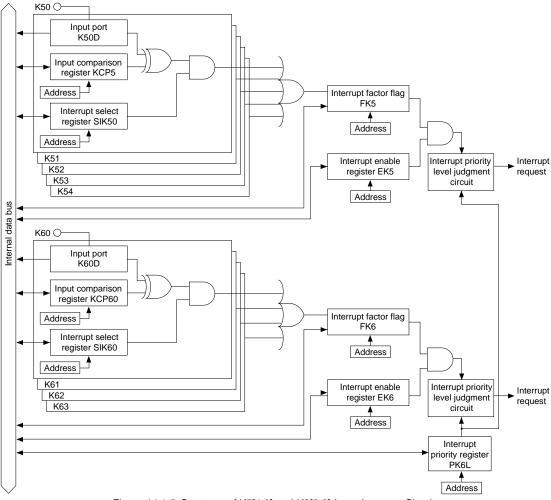

| Interrupt controller: | Possible to invoke intelligent DMA                   |                                  |  |  |  |  |  |  |

|                       | Input interrupt                                      | 6 types                          |  |  |  |  |  |  |

|                       | DMA controller interrupt                             | 3 types                          |  |  |  |  |  |  |

|                       | 16-bit programmable timer interrupt                  | 16 types                         |  |  |  |  |  |  |

|                       | 8-bit programmable timer interrupt                   | 4 types                          |  |  |  |  |  |  |

|                       | Serial interface interrupt                           | 6 types                          |  |  |  |  |  |  |

|                       | A/D converter interrupt                              | 1 type                           |  |  |  |  |  |  |

|                       | Clock timer interrupt 1 type                         |                                  |  |  |  |  |  |  |

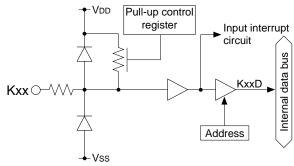

| General-purpose input | Shared with the I/O pins for internal                | peripheral circuits              |  |  |  |  |  |  |

| and output ports:     | Input port 13 bits (built-in pull-up                 | resistors are available)         |  |  |  |  |  |  |

|                       | Output port 11 bits                                  |                                  |  |  |  |  |  |  |

|                       | I/O port 15 bits (built-in pull-up                   | resistors are available)         |  |  |  |  |  |  |

|                       |                                                      |                                  |  |  |  |  |  |  |

### External bus interface

- BCU (bus control unit) built-in

- 24-bit address bus (internal 28-bit processing)

- 16-bit data bus Data size is selectable from 8 bits and 16 bits in each area.

- Little-endian memory access

- Memory mapped I/O

- Chip enable and wait control circuits built-in

- DRAM direct interface function built-in Supports fast page mode and EDO page mode. Supports self-refresh and CAS-before RAS refresh.

- Supports burst ROM.

#### Operating conditions and power consumption

| Operating voltage:        | 5 V ±10% or 3.3 V ±  | ±0.3 V     |                  |

|---------------------------|----------------------|------------|------------------|

| Operating clock frequency | : Max. 33 MHz at 5 V | operation  |                  |

|                           | Max. 20 MHz at 3 V   | operation  |                  |

| Operating temperature:    | -20 to 70°C          |            |                  |

| Power consumption:        | During SLEEP         | 5 μW typ.  | (5 V)            |

| (Typ.)                    |                      | 4 μW typ.  | (3.3 V)          |

|                           | During HALT          | 200 mW typ | .(5 V, 33 MHz)   |

|                           |                      | 40 mW typ. | (3.3 V, 20 MHz)  |

|                           | During execution     | 400 mW typ | .(5 V, 33 MHz)   |

|                           |                      | 100 mW typ | .(3.3 V, 20 MHz) |

|                           |                      |            |                  |

Note: The values of power consumption during execution were measured when a test program that consisted of 55% load instructions, 23% arithmetic operation instructions, 1% mac instruction, 12% branch instructions and 9% ext instruction was being continuously executed.

### Supply form

QFP5-128pin, QFP15-128pin plastic package or die form

Figure 1.2.1 E0C33A104 Block Diagram

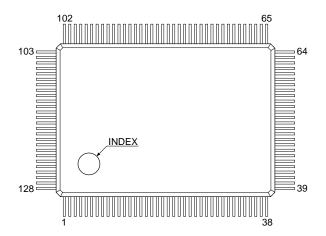

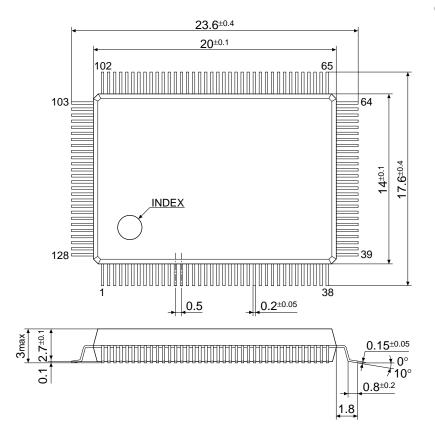

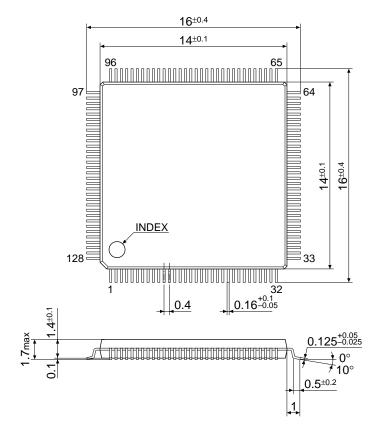

# 1.3.1 Pin Layout Diagram (plastic package)

### QFP5-128pin

| No. | Pin name               | No. | Pin name                | No. | Pin name   | No. | Pin name     |

|-----|------------------------|-----|-------------------------|-----|------------|-----|--------------|

| 1   | #CE5/#CE15             | 33  | OSC1                    | 65  | P03/#SRDY0 | 97  | D1           |

| 2   | #CE6                   | 34  | VDD1                    | 66  | P04/SIN1   | 98  | D0           |

| 3   | #CE7/#RAS0/#CE13/#RAS2 | 35  | K52/#ADTRG              | 67  | P05/SOUT1  | 99  | #WAIT        |

| 4   | #CE8/#RAS1/#CE14/#RAS3 | 36  | R70/TM00                | 68  | P06/#SCLK1 | 100 | ARAMMD1      |

| 5   | #CE9/#CE17             | 37  | R71/TM01                | 69  | P07/#SRDY1 | 101 | ARAMMD0      |

| 6   | #CE10                  | 38  | R72/TM10                | 70  | A7         | 102 | #BUSACK      |

| 7   | VS5V                   | 39  | R73/TM11                | 71  | A6         | 103 | #BUSREQ      |

| 8   | #NMI                   | 40  | R74/TM21                | 72  | A5         | 104 | BCLK         |

| 9   | Vss                    | 41  | R75/TM31                | 73  | A4         | 105 | #HCAS        |

| 10  | #TSTMD                 | 42  | R76/TM41                | 74  | A3         | 106 | #LCAS        |

| 11  | #RESET                 | 43  | R77/TM51                | 75  | A2         | 107 | #WRH/#BSH    |

| 12  | Vdd                    | 44  | Vss                     | 76  | A1         | 108 | #WRL/#WR/#WE |

| 13  | Vss                    | 45  | Vdd                     | 77  | A0/#BSL    | 109 | #RD          |

| 14  | OSC4                   | 46  | P10/EXCL00/T8UF0/DST0   | 78  | D15        | 110 | Vdd          |

| 15  | OSC3                   | 47  | P11/EXCL01/T8UF1/DST1   | 79  | Vss        | 111 | A8           |

| 16  | AVrh                   | 48  | P12/EXCL10/T8UF2/DST2   | 80  | D14        | 112 | A9           |

| 17  | AVRL                   | 49  | P13/EXCL20/T8UF3/DPCO   | 81  | D13        | 113 | A10          |

| 18  | AVss                   | 50  | P14/EXCL30/#BUSGET/#DWE | 82  | D12        | 114 | A11          |

| 19  | K67/AD7                | 51  | P15/EXCL40/#DMAEND0     | 83  | D11        | 115 | A12          |

| 20  | K66/AD6                | 52  | P16/EXCL50/#DMAEND1     | 84  | D10        | 116 | A13          |

| 21  | K65/AD5                | 53  | ВТАЗ                    | 85  | D9         | 117 | A14          |

| 22  | K64/AD4                | 54  | K51/#DMAREQ1            | 86  | D8         | 118 | A15          |

| 23  | K63/AD3                | 55  | R83/#DMAACK1            | 87  | D7         | 119 | A16          |

| 24  | K62/AD2                | 56  | #TSTMD1                 | 88  | Vdd        | 120 | A17          |

| 25  | K61/AD1                | 57  | R81/FOSC1/#DRD          | 89  | Vss        | 121 | A18          |

| 26  | K60/AD0                | 58  | K50/#DMAREQ0            | 90  | D6         | 122 | A19          |

| 27  | K53/DA0                | 59  | R82/#DMAACK0            | 91  | Vdd        | 123 | A20          |

| 28  | K54/DA1                | 60  | P00/SIN0                |     | Vss        | 124 | A21          |

| 29  | AVdd                   | 61  | Vdd                     | 93  | D5         | 125 | A22          |

| 30  | N.C.                   | 62  | Vss                     | 94  | D4         | 126 | A23          |

| 31  | Vss                    | 63  | P01/SOUT0               | 95  | D3         | 127 | Vss          |

| 32  | 0SC2                   | 64  | P02/#SCLK0              | 96  | D2         | 128 | #CE4/#CE11   |

Figure 1.3.1 Pin Layout Diagram (QFP5-128pin)

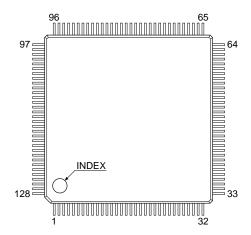

| No. | Pin name               | No. | Pin name                | No. | Pin name   | No. | Pin name               |

|-----|------------------------|-----|-------------------------|-----|------------|-----|------------------------|

| 1   | #CE8/#RAS1/#CE14/#RAS3 | 33  | R70/TM00                | 65  | P06/#SCLK1 | 97  | ARAMMD1                |

| 2   | #CE9/#CE17             | 34  | R71/TM01                | 66  | P07/#SRDY1 | 98  | ARAMMD0                |

| 3   | #CE10                  | 35  | R72/TM10                | 67  | A7         | 99  | #BUSACK                |

| 4   | VS5V                   | 36  | R73/TM11                | 68  | A6         | 100 | #BUSREQ                |

| 5   | #NMI                   | 37  | R74/TM21                | 69  | A5         | 101 | BCLK                   |

| 6   | Vss                    | 38  | R75/TM31                | 70  | A4         | 102 | #HCAS                  |

| 7   | #TSTMD                 | 39  | R76/TM41                | 71  | A3         | 103 | #LCAS                  |

| 8   | #RESET                 | 40  | R77/TM51                | 72  | A2         | 104 | #WRH/#BSH              |

| 9   | Vdd                    | 41  | Vss                     | 73  | A1         | 105 | #WRL/#WR/#WE           |

| 10  | Vss                    | 42  | Vdd                     | 74  | A0/#BSL    | 106 | #RD                    |

| 11  | OSC4                   | 43  | P10/EXCL00/T8UF0/DST0   | 75  | D15        | 107 | Vdd                    |

| 12  | OSC3                   | 44  | P11/EXCL01/T8UF1/DST1   | 76  | Vss        | 108 | A8                     |

| 13  | AVrh                   | 45  | P12/EXCL10/T8UF2/DST2   | 77  | D14        | 109 | A9                     |

| 14  | AVrl                   | 46  | P13/EXCL20/T8UF3/DPCO   | 78  | D13        | 110 | A10                    |

| 15  | AVss                   | 47  | P14/EXCL30/#BUSGET/#DWE | 79  | D12        | 111 | A11                    |

| 16  | K67/AD7                | 48  | P15/EXCL40/#DMAEND0     |     | D11        | 112 | A12                    |

| 17  | K66/AD6                | 49  | P16/EXCL50/#DMAEND1     |     | D10        | 113 | A13                    |

| 18  | K65/AD5                | 50  | ВТАЗ                    |     | D9         | 114 | A14                    |

| 19  | K64/AD4                | 51  | K51/#DMAREQ1            | 83  | D8         | 115 | A15                    |

| 20  | K63/AD3                | 52  | R83/#DMAACK1            |     | D7         | 116 | A16                    |

| 21  | K62/AD2                | 53  | #TSTMD1                 | 85  | Vdd        | 117 | A17                    |

| 22  | K61/AD1                | 54  | R81/FOSC1/#DRD          | 86  | Vss        | 118 | A18                    |

| 23  | K60/AD0                | 55  | K50/#DMAREQ0            | 87  | D6         | 119 | A19                    |

| 24  | K53/DA0                | 56  | R82/#DMAACK0            | 88  | Vdd        | 120 | A20                    |

| 25  | K54/DA1                | 57  | P00/SIN0                | 89  | Vss        | 121 | A21                    |

| 26  | AVdd                   | 58  | Vdd                     | 90  | D5         | 122 | A22                    |

| 27  | Vss                    | 59  | Vss                     | 91  | D4         | 123 | A23                    |

| 28  | 0SC2                   | 60  | P01/SOUT0               |     | D3         | 124 | Vss                    |

| 29  | 0SC1                   | 61  | P02/#SCLK0              |     | D2         | 125 | #CE4/#CE11             |

| 30  | N.C.                   | 62  | P03/#SRDY0              | 94  | D1         | 126 | #CE5/#CE15             |

| 31  | Vdd1                   | 63  | P04/SIN1                | 95  | D0         | 127 | #CE6                   |

| 32  | K52/#ADTRG             | 64  | P05/SOUT1               | 96  | #WAIT      | 128 | #CE7/#RAS0/#CE13/#RAS2 |

Figure 1.3.2 Pin Layout Diagram (QFP15-128pin)

### 1.3.2 Pin Functions

Table 1.3.1 List of Pins for Power Supply System

| Pin name | Pin No.   |           | Pin No. |         | Pin No.                                       |  | Pin No. |  | Function |

|----------|-----------|-----------|---------|---------|-----------------------------------------------|--|---------|--|----------|

| Pin name | QFP5-128  | QFP15-128 | 1/0     | Pull-up | Function                                      |  |         |  |          |

| Vdd      | 12,45,61, | 9,42,58,  | -       | -       | Power supply (+)                              |  |         |  |          |

|          | 88,91,110 | 85,88,107 |         |         |                                               |  |         |  |          |

| Vss      | 9,13,31,  | 6,10,27,  | -       | -       | Power supply (-)                              |  |         |  |          |

|          | 44,62,79, | 41,59,76, |         |         |                                               |  |         |  |          |

|          | 89,92,127 | 86,89,124 |         |         |                                               |  |         |  |          |

| VDD1     | 34        | 31        | -       | -       | Low-speed oscillation system power supply (+) |  |         |  |          |

| AVdd     | 29        | 26        | -       | -       | Analog system power supply (+)                |  |         |  |          |

| AVss     | 18        | 15        | -       | -       | Analog system power supply (-)                |  |         |  |          |

| AVRH     | 16        | 13        | -       | _       | Analog system reference voltage (+)           |  |         |  |          |

| AVRL     | 17        | 14        | -       | -       | Analog system reference voltage (-)           |  |         |  |          |

#### Table 1.3.2 List of Pins for External Interface Signals

| Pin name     | Pin No.   |           | 1/0 | Pull-up  | Function                                   |

|--------------|-----------|-----------|-----|----------|--------------------------------------------|

| Pin name     | QFP5-128  | QFP15-128 | 10  | r ull-up | Function                                   |

| A[0]/#BSL    | 77        | 74        | 0   | -        | Address bus (A0) / Bus strobe (low byte)   |

| A[23:1]      | 70–76,    | 67~73,    | 0   | -        | Address bus (A1 to A23)                    |

|              | 111–126   | 108~123   |     |          |                                            |

| D[15:0]      | 78,80–87, | 75,77~84, | I/O | -        | Data bus (D0 to D15)                       |

|              | 90,93–98  | 87,90~95  |     |          |                                            |

| #CE10        | 6         | 3         | 0   | -        | Area 10 chip enable                        |

| #CE9/#CE17   | 5         | 2         | 0   | -        | Area 9/17 chip enable                      |

| #CE8/#RAS1/  | 4         | 1         | 0   | -        | Area 8/14 chip enable / DRAM row strobe    |

| #CE14/#RAS3  |           |           |     |          |                                            |

| #CE7/#RAS0/  | 3         | 128       | 0   | -        | Area 7/13 chip enable / DRAM row strobe    |

| #CE13/#RAS2  |           |           |     |          |                                            |

| #CE6         | 2         | 127       | 0   | -        | Area 6 chip enable                         |

| #CE5/#CE15   | 1         | 126       | 0   | -        | Area 5/15 chip enable                      |

| #CE4/#CE11   | 128       | 125       | 0   | -        | Area 4/11 chip enable                      |

| #RD          | 109       | 106       | 0   | -        | Read signal                                |

| #WRL/#WR/#WE | 108       | 105       | 0   | -        | Write (low byte) / Write / DRAM write      |

| #WRH/#BSH    | 107       | 104       | 0   | -        | Write (high byte) / Bus strobe (high byte) |

| #HCAS        | 105       | 102       | 0   | -        | DRAM column address strobe (high byte)     |

| #LCAS        | 106       | 103       | 0   | -        | DRAM column address strobe (low byte)      |

| BCLK         | 104       | 101       | 0   | -        | Bus clock output                           |

| #BUSREQ      | 103       | 100       | Ι   | -        | Bus release request                        |

| #BUSACK      | 102       | 99        | 0   | -        | Bus acknowledge                            |

| #WAIT        | 99        | 96        | Ι   | -        | Wait cycle request                         |

#### Table 1.3.3 List of I/O Pins for Input/Output Ports and Internal Peripheral Circuits

| Pin name     | Pin No.  |           | Pin No. |          | 10                                      | I/O Pull-up | Function |

|--------------|----------|-----------|---------|----------|-----------------------------------------|-------------|----------|

| Fin hame     | QFP5-128 | QFP15-128 | 1/0     | Full-up  | Function                                |             |          |

| K50/#DMAREQ0 | 58       | 55        | Ι       | built-in | Input port / High-speed DMA request 0   |             |          |

| K51/#DMAREQ1 | 54       | 51        | 1       | built-in | Input port / High-speed DMA request 1   |             |          |

| K52/#ADTRG   | 35       | 32        | Т       | built-in | Input port / AD converter trigger input |             |          |

| K53/DA0      | 27       | 24        | I(O)    | built-in | Input port / DA converter output 0      |             |          |

| K54/DA1      | 28       | 25        | I(O)    | built-in | Input port / DA converter output 1      |             |          |

| K60/AD0      | 26       | 23        | Т       | built-in | Input port / AD converter input 0       |             |          |

| K61/AD1      | 25       | 22        | 1       | built-in | Input port / AD converter input 1       |             |          |

| K62/AD2      | 24       | 21        | I       | built-in | Input port / AD converter input 2       |             |          |

| K63/AD3      | 23       | 20        | Т       | built-in | Input port / AD converter input 3       |             |          |

| K64/AD4      | 22       | 19        | 1       | built-in | Input port / AD converter input 4       |             |          |

| K65/AD5      | 21       | 18        | 1       | built-in | Input port / AD converter input 5       |             |          |

| K66/AD6      | 20       | 17        | 1       | built-in | Input port / AD converter input 6       |             |          |

| K67/AD7      | 19       | 16        | I       | built-in | Input port / AD converter input 7       |             |          |

|              | Pin      | No.       |     |          |                                                                               |

|--------------|----------|-----------|-----|----------|-------------------------------------------------------------------------------|

| Pin name     | QFP5-128 | QFP15-128 | I/O | Pull-up  | Function                                                                      |

| R70/TM00     | 36       | 33        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 00) output             |

| R71/TM01     | 37       | 34        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 01) output             |

| R72/TM10     | 38       | 35        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 10) output             |

| R73/TM11     | 39       | 36        | 0   | 1        | Output port (initial value = "0") /16-bit timer (timer 11) output             |

| R74/TM21     | 40       | 37        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 21) output             |

| R75/TM31     | 41       | 38        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 31) output             |

| R76/TM41     | 42       | 39        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 41) output             |

| R77/TM51     | 43       | 40        | 0   | -        | Output port (initial value = "0") /16-bit timer (timer 51) output             |

| R81/FOSC1/   | 57       | 54        | 0   | -        | Output port (initial value = "1")/ Low-speed (OSC1) oscillation clock output/ |

| #DRD         |          |           |     |          | DRAM read                                                                     |

| R82/#DMAACK0 | 59       | 56        | 0   | -        | Output port (initial value = "1") / High-speed DMA acknowledge 0              |

| R83/#DMAACK1 | 55       | 52        | 0   | -        | Output port (initial value = "1") / High-speed DMA acknowledge 1              |

| P00/SIN0     | 60       | 57        | I/O | built-in | I/O port / Serial IF Ch.0 data input                                          |

| P01/SOUT0    | 63       | 60        | I/O | built-in | I/O port / Serial IF Ch.0 data output                                         |

| P02/#SCLK0   | 64       | 61        | I/O | built-in | I/O port / Serial IF Ch.0 clock input/output                                  |

| P03/#SRDY0   | 65       | 62        | I/O | built-in | I/O port / Serial IF Ch.0 ready signal output                                 |

| P04/SIN1     | 66       | 63        | I/O | built-in | I/O port / Serial IF Ch.1 data input                                          |

| P05/SOUT1    | 67       | 64        | I/O | built-in | I/O port / Serial IF Ch.1 data output                                         |

| P06/#SCLK1   | 68       | 65        | I/O | built-in | I/O port / Serial IF Ch.1 clock input/output                                  |

| P07/#SRDY1   | 69       | 66        | I/O | built-in | I/O port / Serial IF Ch.1 ready signal output                                 |

| P10/EXCL00/  | 46       | 43        | I/O | built-in | I/O port / Timer 00 event counter input / 8-bit timer 0 output / DST0 output  |

| T8UF0/DST0   |          |           |     |          |                                                                               |

| P11/EXCL01/  | 47       | 44        | I/O | built-in | I/O port / Timer 01 event counter input / 8-bit timer 1 output / DST1 output  |

| T8UF1/DST1   |          |           |     |          |                                                                               |

| P12/EXCL10/  | 48       | 45        | I/O | built-in | I/O port / Timer 10 event counter input / 8-bit timer 2 output / DST2 output  |

| T8UF2/DST2   |          |           |     |          |                                                                               |

| P13/EXCL20/  | 49       | 46        | I/O | built-in | I/O port / Timer 20 event counter input / 8-bit timer 3 output / DPCO output  |

| T8UF3/DPCO   |          |           |     |          |                                                                               |

| P14/EXCL30/  | 50       | 47        | I/O | built-in | I/O port/Timer 30 event counterinput/#BUSGET signal output/DRAM write         |

| #BUSGET/#DWE |          |           |     |          |                                                                               |

| P15/EXCL40/  | 51       | 48        | I/O | built-in | I/O port / Timer 40 event counter input / End of high-speed DMA (Ch.0)        |

| DMAEND0      |          |           |     |          |                                                                               |

| P16/EXCL50/  | 52       | 49        | I/O | built-in | I/O port / Timer 50 event counter input / End of high-speed DMA (Ch.1)        |

| DMAEND1      |          |           |     |          |                                                                               |

Note 1 Follow the notes below for pins with a pull-up resistor (Kxx, Pxx).

- 1) The pull-up resistors can be turned on and off individually using the control registers.

- 2) All the pull-up resistors turn off at cold start. At hot start, they retain the previous status (on or off) before an initial reset.

**Note 2** The output port pins (Rxx) output the initial value "0" ("1" for R81 to R83) at cold start. At hot start, they retain the previous status before an initial reset.

| Pin name    | Pin      | No.       | 1/0 | Pull-up  | Function                                                                                    |

|-------------|----------|-----------|-----|----------|---------------------------------------------------------------------------------------------|

| Pin name    | QFP5-128 | QFP15-128 | 1/0 | Pull-up  | Function                                                                                    |

| OSC1        | 33       | 29        | I   | -        | Low-speed (OSC1) oscillation input (32 kHz crystal oscillator or external clock input)      |

| OSC2        | 32       | 28        | 0   | -        | Low-speed (OSC1) oscillation output                                                         |

| OSC3        | 15       | 12        | I   | -        | High-speed (OSC3) oscillation input (crystal/ceramic oscillator or external<br>clock input) |

| OSC4        | 14       | 11        | 0   | -        | High-speed (OSC3) oscillation output                                                        |

| #NMI        | 8        | 5         | I   | -        | NMI request                                                                                 |

| BTA3        | 53       | 50        | I   | -        | Boot address setup (Low: Area 10)                                                           |

| VS5V        | 7        | 4         | I   | -        | Input threshold voltage setup (High: TTL, Low: CMOS)                                        |

| ARAMMD[1:0] | 100,101  | 97,98     | I   | -        | ARAM mode setup                                                                             |

| #TSTMD      | 10       | 7         | I.  | -        | Test input (Fixed at high during operation.)                                                |

| #TSTMD1     | 56       | 53        | I   | _        | Test input (Fixed at high during operation.)                                                |

| #RESET      | 11       | 8         | I   | built-in | Initial reset input                                                                         |

Table 1.3.4 List of Other Pins

# 2 Power Supply and I/O Level

This chapter explains the operating voltage and I/O levels of the E0C33A104.

# 2.1 Power Supply

### 2.1.1 Power Supply Pins

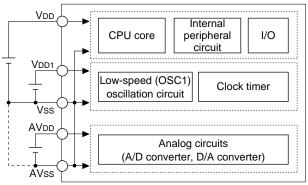

The E0C33A104 has the power supply pins shown in Table 2.1.1.

Table 2.1.1 Power Supply Pins

| Pin name | Pin                | No.               | Function                                                                          |  |

|----------|--------------------|-------------------|-----------------------------------------------------------------------------------|--|

| Fin name | QFP5-128           | QFP15-128         | Function                                                                          |  |

| Vdd      | 12,45,61,88,91,110 | 9,42,58,85,88,107 | Power supply (+) for the internal logic circuits and I/O                          |  |

| Vss      | 9,13,31,44,62,79,  | 6,10,27,41,59,76, | Power supply (GND) for the internal logic circuits and I/O                        |  |

|          | 89,92,127          | 86,89,124         |                                                                                   |  |

| VDD1     | 34                 | 31                | Power supply (+) for the low-speed (OSC1) oscillation circuit and the clock timer |  |

| AVdd     | 29                 | 26                | Power supply (+) for the internal analog circuits                                 |  |

| AVss     | 18                 | 15                | Power supply (GND) for the internal analog circuits                               |  |

Figure 2.1.1 Power Supply System

### 2.1.2 Operating Voltage (VDD)

The core CPU and internal peripheral circuit (excluding analog circuits, low-speed oscillation circuit and clock timer) operate with a voltage supplied between the VDD and VSS pins. The following two operating voltages can be used:

5 V system:  $VDD = 5.0 V \pm 10\%$  (Vss = GND) 3 V system:  $VDD = 3.3 V \pm 0.3 V$  (Vss = GND)

**Note:** The E0C33A104 has six VDD pins and nine Vss pins. Be sure to supply the operating voltage to all the pins. Do not open any of them.

The operating clock frequency range is limited as shown in Table 2.1.2 according to the operating voltage to be supplied.

| Supply voltage (VDD)              | Minimum operating clock<br>frequency (OSC3) | Maximum operating clock<br>frequency (OSC3) |

|-----------------------------------|---------------------------------------------|---------------------------------------------|

| 5.0 V ± 10%                       | 5 MHz                                       | 33 MHz                                      |

| $3.3~\textrm{V}\pm0.3~\textrm{V}$ | 5 MHz                                       | 20 MHz                                      |

Table 2.1.2 Range of Operating Clock Frequency

### 2.1.3 Power Supply for Clock (VDD1)

The VDD1 voltage is used for driving the low-speed (OSC1) oscillation circuit and the clock timer. VDD1 can be supplied separately from VDD, it makes it possible to drive the clock timer system when the core CPU and other internal peripheral circuits are turned off. The same power supply can also be used for both VDD and VDD1. The VSS pin is used for the ground common with VDD.

The following two voltage levels are enabled for VDD1 the same as VDD:

5 V system:  $VDD = 5.0 V \pm 10\%$  (Vss = GND)

3 V system:  $VDD = 3.3 V \pm 0.3 V$  (Vss = GND)

However, satisfy the condition of VDD1  $\leq$  VDD. When VDD is 3.3 V, 5 V cannot be used for VDD1.

### 2.1.4 Power Supply for Analog Circuits (AVDD, AVss)

The analog power supply pins (AVDD and AVSS) are provided separately from the VDD and VSS pins in order that the digital circuits do not affect the analog circuits (A/D converter and D/A converter). The AVDD pin is used to supply an analog power voltage and the AVSS pin is used as the analog ground. Supply the same voltage level as the VDD to the AVDD pin.

AVDD = VDD, AVSS = VSS (GND)

**Note:** These pins should be set as AVDD = VDD, AVss = Vss (GND) even if the analog circuits are not used.

The AVss pin is electrically connected with the Vss pin on the chip substrate.

The reference voltage pins (AVRH, AVRL) are also provided for A/D conversion. Refer to Section 13.1, "A/D Converter", for the analog reference voltage.

Noise on the analog power lines decrease the A/D and D/A converting precision, so use a stabilized power supply and make the board pattern with consideration given to that. Refer to Chapter 17 for precautions in making a pattern.

### 2.2 I/O Level

For the output interface of the E0C33A104, the VDD voltage is used as high level and the VSS voltage as low level. For the input interface, the input threshold level can be set using the VS5V pin.

| Pin name | Pin      | No.       | Dull un | I/O | Function                                                          |

|----------|----------|-----------|---------|-----|-------------------------------------------------------------------|

| Pin name | QFP5-128 | QFP15-128 | Pull-up | Ņ   | Function                                                          |

| VS5V     | 7        | 4         | -       |     | Input interface level setup<br>High: TTL level<br>Low: CMOS level |

Table 2.2.1 Input Interface Level Setup Pin

**Note:** The VS5V pin does not have a pull-up resistor, therefore it must be connected to VDD or Vss. Furthermore, when using a 3.3 V of operating voltage, do not set the VS5V pin to high.

# 3 Initial Reset

This chapter explains the initial reset for the E0C33A104.

### 3.1 Pins for Initial Reset

Table 3.1.1 shows the pins used for initial reset.

| Pin name | Pin      | No.       | Pull-up  | I/O | Function                                            |  |

|----------|----------|-----------|----------|-----|-----------------------------------------------------|--|

| Fininame | QFP5-128 | QFP15-128 | r ull-up | 1/0 | Function                                            |  |

| #RESET   | 11       | 8         | Built-in | Ι   | Initial reset input pin                             |  |

|          |          |           |          |     | Low: Resets the CPU.                                |  |

| #NMI     | 8        | 5         | -        | 1   | NMI request pin                                     |  |

|          |          |           |          |     | This pin is also used for selecting a reset method. |  |

|          |          |           |          |     | High: Cold start                                    |  |

|          |          |           |          |     | Low: Hot start                                      |  |

| BTA3     | 53       | 50        | -        | 1   | Boot address setup pin                              |  |

|          |          |           |          |     | Low: Area 10                                        |  |

Table 3.1.1 Pins for Initial Reset

The E0C33A104 is reset when the #RESET pin goes low and starts operating at the rising edge of the reset signal. The core CPU and internal peripheral circuits are initialized while the #RESET pin is low.

# 3.2 Cold Start and Hot Start

The E0C33A104 supports two initial reset methods: cold start and hot start. The #NMI pin is used with the #RESET pin to set this condition.

The differences between cold start and hot start are shown in Table 3.2.1.

| Setup contents                        | Cold start                                        | Hot start                  |  |

|---------------------------------------|---------------------------------------------------|----------------------------|--|

| Reset condition                       | #RESET = low & #NMI = high                        | #RESET = low & #NMI = low  |  |

| CPU: PC                               | The vector at the boot ad                         | dress is loaded to the PC. |  |

| CPU: PSR                              | All the PSR bit                                   | s are reset to 0.          |  |

| CPU: Other registers                  | Undefined                                         |                            |  |

| CPU: Operating clock                  | The CPU operates with the OSC3 clock.             |                            |  |

| External bus status (0x40120–0x4013F) | Initialized                                       | Status is retained.        |  |

| Oscillation circuit                   | Both the OSC1 and OSC3 circuit start oscillating. |                            |  |

| I/O pin status (0x402C0–0x402DF)      | Initialized                                       | Status is retained.        |  |

| Other peripheral circuit              | Initialized or undefined                          |                            |  |

Table 3.2.1 Differences between Cold Start and Hot Start

Since cold start initializes all the internal peripheral circuits as well as the CPU, it is useful as a power-on reset. Hot start initializes the CPU and peripheral circuits, but does not reset the bus control unit and the input, output and I/O port status. It is useful as a reset that maintains the external memory, external I/O and the port status.

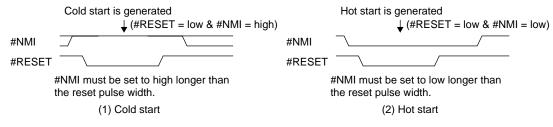

The #NMI pin that specifies the reset method should be set following the timing chart shown in Figure 3.2.1.

### 3.3 Power-on Reset

Be sure to reset (cold start) the E0C33A104 after turning on the power to start operating.

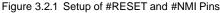

Since the #RESET pin has a built-in pull-up resister (approx. 160 k $\Omega$ ), a power-on reset circuit is simply configured by connecting a capacitor as shown in Figure 3.3.1.

Figure 3.3.1 Power-on Reset Circuit

An initial reset (#RESET = low) turns the high-speed (OSC3) oscillation circuit on. The CPU starts operating with the OSC3 clock at the rising edge of the reset signal. The high-speed (OSC3) oscillation circuit takes time (10 ms max. under the standard condition in 3.3 V) for the oscillation to stabilize, therefore initial reset must be released after an appropriate oscillation-stabilization time has passed in order to start up the CPU without fault. The external capacitance should be decided so that the time constant of the capacitor and built-in pull-up resistor exceeds the oscillation-stabilization time.

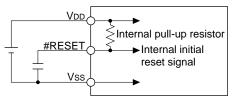

Figure 3.3.2 shows a power-on reset timing chart.

Figure 3.3.2 Power-on Reset Timing

Maintain the #RESET pin at 0.1•VDD or less (low level) after turning the power on until the supply voltage rises at least to the oscillation start voltage (3.0 V or 4.5 V). Furthermore, maintain the #RESET pin at 0.5•VDD or less until the high-speed (OSC3) oscillation circuit stabilizes oscillating.

**Note:** The OSC3 oscillation start time varies due to the elements used, board pattern and operating environment, therefore allow enough margin for the reset-release time. Refer to Section 18.8, "Oscillation Characteristics", in which an example of oscillation start time is provided.

# 3.4 Reset Pulse

A low pulse can be input to the #RESET pin for resetting the E0C33A104 being operated.

The minimum reset pulse width is provided in Section 18.7, "AC Characteristics". Be sure to input a pulse that has a pulse width longer than the minimum value.

To reset the E0C33A104 when the high-speed (OSC3) oscillation circuit is in off status, the pulse width must be extended until the oscillation stabilizes similarly to the power-on reset. Be aware that a short reset pulse may cause an operation error of the IC.

# 3.5 Boot Address

When the core CPU is initially reset, it reads the reset vector (program start address) from the boot address and loads the address to the PC (program counter). Then the CPU starts executing the program from the address when the #RESET pin goes high.

The boot address is decided according to the BTA3-pin setting.

| 1 | Pin name | Pin      | No.       | Pull-up | I/O Setup level |             | Boot address        |  |

|---|----------|----------|-----------|---------|-----------------|-------------|---------------------|--|

|   | Pin name | QFP5-128 | QFP15-128 | Pull-up | 1/0             | Setup level | Boot address        |  |

|   | BTA3     | 53       | 50        | -       | Ι               | Low         | 0x0C00000 (area 10) |  |

| Table 3.5.1 | BTA3 Pin and | Boot Address |

|-------------|--------------|--------------|

Note: The BTA3 pin must be fixed at Low level.

The trap table in which trap vectors for interrupts and other trap factors are written also begins from the boot address by the default setting. (Refer to the "E0C33000 Core CPU Manual" for details of the trap table.) The trap table base address can also be changed to a 1KB boundary address using the TTBR register (0x48134 to 0x48137).

# 3.6 Notes Related to Initial Reset

### Core CPU

Since the all registers except for the PC and PSR are indeterminate at initial reset, they should be initialized by a program. In particular, the SP (stack pointer) must be initialized before accessing the stack area. NMI requests are disabled until any value is written to the SP. The initialization is necessary when the CPU is hot-started.

### Internal RAM

The contents of the internal RAM are indeterminate at initial reset. Initialize the area to be used if necessary.

### High-speed (OSC3) oscillation circuit

An initial reset activates the high-speed (OSC3) oscillation circuit and the CPU starts operating with the OSC3 clock after the initial reset is released. In order to prevent a malfunction of the CPU due to an unstabilized clock, the #RESET pin must be maintained at low until the OSC3 oscillation stabilizes when performing a power-on reset or resetting while the high-speed (OSC3) oscillation circuit is stopped. (Refer to Sections 3.3.)

### Low-speed (OSC1) oscillation circuit

A power-on reset or an initial reset when the low-speed (OSC1) oscillation circuit is off starts the OSC1 oscillation. The low-speed (OSC1) oscillation circuit takes a longer stabilization time (3 sec max. under the standard condition) than the high-speed (OSC3) oscillation circuit. In order to prevent a malfunction due to an unstabilized clock, do not use the OSC1 clock until the stabilization time has passed.

### BCU (external system interface)

Cold-start initializes the control registers for the BCU (bus control unit). Therefore, it is necessary to set up all the bus conditions.

Hot-start retains the previous bus conditions before an initial reset.

#### Input/output ports and input/output pins

Cold start initializes the control and data registers for the input, output and I/O ports.

The pull-up resistors in the input ports are disconnected.

The R70–R77 output ports output "0" (low level) and the R81–R83 ports output "1" (high level).

The I/O ports are set in input mode. The pull-up resistors in the I/O ports are disconnected.

Hot start retains the contents of the control registers and input/output pin status before an initial reset. However, when the pins are used for the internal peripheral circuits, it is necessary to set up the control registers of the peripheral circuit because they are initialized by an initial reset.

#### Other internal peripheral circuits

The control and data registers of peripheral circuits other than those listed above are initialized with the predefined values or become indeterminate regardless of the reset method (cold start or hot start). Therefore, it is necessary to set up the peripheral circuit conditions.

Refer to the I/O maps or explanation of each peripheral circuit section for initial settings of the peripheral circuits.

# 4 CPU and Operating Modes

This chapter explains the core CPU and the operating modes.

# 4.1 CPU

The E0C33A104 employs the E0C33000 32-bit RISC type CPU as the core CPU.

Since the E0C33A104 has a built-in multiplier, all instructions (105 instructions) in the E0C33000 instruction set including the MAC (multiplication and accumulation) instruction and the multiplication/division instructions are available.

All the internal registers of the E0C33000 can be used. The internal register can handle 28-bit addresses. However, the E0C33A104 has a 24-bit external address bus (A[0:23]), so the low-order 24 bits of address data can only be delivered to the external address bus.

Refer to the "E0C33000 Core CPU Manual" for details of the E0C33000.

#### Note: MAC execution error

<Descriptions of the problem>

The result of the MAC instructions may be incorrect when the following instructions appear right before the MAC instruction. The following instructions modify the %ALR and %AHR registers and this causes incorrect MAC results.

"Id.w %ALR, %Rs" "div\*" "Id.w %ALR, %Rs" "mlt\*"

<How to avoid this problem>

Do not place the above instructions right before the MAC instructions.

#### Load and data-size conversion instruction instruction error

<Descriptions of the problem>

**CASE 1**: When executing instructions in area 3 or area 0 (internal RAM), the following combination of instruction execution may result in incorrect register values to the destination register of the first instruction.

Id.ub

%r12, [%r9]

or

Id.ub

%r12, [%r9]

or

Id.h

%r12, [%r5]

or

Id.w

%r12, [%r6]

Id.h

%r10, %r12

or

Id.h

%r12, [%r5]

or

Id.w

%r12, [%r6]

The %r12 may be incorrect.

Notice that the source register of the second instruction is the destination register of the first instruction and the second instruction is a data-size conversion instruction, load/store instruction or branch instruction.

**CASE 2**: When turning on the CBR refresh cycles for the external DRAM access, the above instruction combination may result in incorrect register values even if the instructions are fetched from an external memory.

**CASE 3**: When the source register and destination register of the data-size conversion instruction is the same, the result may be incorrect.

**CASE 4**: When executing a data-size conversion instruction, the results become invalid and a debug environment like ICE will not work properly.

<How to avoid this problem>

There is a "FILTER" program in the CC33 software development package. Carefully go through the readme file in the CC33\utility\filter directory before using.

### 4.2 Standby Mode

The E0C33A104 supports three standby modes: two HALT modes and a SLEEP mode. By setting the E0C33A104 in the standby mode, power consumption can greatly be reduced.

### 4.2.1 HALT Mode

When the CPU executes the halt instruction, it suspends the program execution and enters the HALT mode. The E0C33A104 supports two types of HALT modes (basic HALT mode and HALT2 mode) and either can be selected using the HLT2OP (D3) / Clock option register (0x40150).

The CPU stops operating in basic HALT mode, so the amount of current consumption can be reduced. The internal peripheral circuits including the oscillation circuit keep operating in basic HALT mode.

HALT2 mode stops the external bus control functions including DMA and the bus clock as well as the CPU similar to basic HALT mode. Consequently, HALT2 mode realizes more power saving than the basic HALT mode. The HALT mode is canceled by an initial reset or an interrupt including NMI. This mode is useful for saving power when waiting for an external input or completion of the peripheral circuit operations that do not need to execute the

CPU.

The CPU transits to program execution status through trap processing when the HALT mode is canceled by an interrupt and executes the interrupt processing routine. The trap processing of the CPU saves the address of the instruction that follows the executed halt instruction into the stack. Therefore, when the interrupt processing routine is terminated by the reti instruction, the program flow returns to the instruction that follows the halt instruction. Note that the HALT mode cannot be canceled with an interrupt factor except for reset and NMI if the PSR is set into interrupt disabled status.

### 4.2.2 SLEEP Mode

When the CPU executes the slp instruction, it suspends the program execution and enters SLEEP mode. In SLEEP mode, the CPU and the internal peripheral circuits including the high-speed (OSC3) oscillation circuit stop operating. Thus SLEEP mode can greatly reduce current consumption in comparison to HALT mode. Moreover, the low-speed (OSC1) oscillation circuit and clock timer do not stop operating. The clock function keeps operating in SLEEP mode.

SLEEP mode is canceled by an initial reset or an interrupt (NMI, clock timer interrupt, external interrupt such as a key entry). Note that other interrupts by the internal peripheral circuits that use the OSC3 clock cannot be used for canceling SLEEP mode.

The CPU transits to program execution status through trap processing when the SLEEP mode is canceled by an interrupt and executes the interrupt processing routine. The trap processing of the CPU saves the address of the instruction that follows the executed slp instruction into the stack. Therefore, when the interrupt processing routine is terminated by the reti instruction, the program flow returns to the instruction that follows the slp instruction. Note that SLEEP mode cannot be canceled with an interrupt factor except for reset and NMI if the PSR is set into interrupt disabled status.

### 4.2.3 Notes on Standby Mode

#### Interrupts

The standby mode can be canceled by an interrupt. Therefore, it is necessary to enable the interrupt to be used for canceling the standby mode before setting the CPU in the standby mode. It is also necessary to set the IE (interrupt enable) and IL (interrupt level) bits in the PSR to a condition that can accept the interrupt. Otherwise, the standby mode cannot be canceled even when an interrupt occurs. Refer to Chapter 8, "Interrupt", for interrupt settings.

#### **Oscillation circuit**

The high-speed (OSC3) oscillation circuit stops in SLEEP mode and restarts oscillating when SLEEP mode is canceled. If the CPU had operated with the OSC3 clock before entering SLEEP mode, the CPU restarts operating with the OSC3 clock immediately after canceling SLEEP mode. However, the OSC3 oscillation needs appropriate stabilization time (10 ms max. under the standard condition in 3.3 V). To restart the CPU after the oscillation stabilizes, a programmable interval can be inserted between cancellation of SLEEP mode and starting the CPU operation. Refer to Section 10.1, "Oscillation Circuits", for details.

The oscillation start time of the high-speed (OSC3) oscillation circuit varies according to the components to be used, board pattern and operating environment. The interval must be set to allow enough margin. Refer to Section 18.8, "Oscillation Characteristics", for examples of oscillation start time.

#### **BCU** (external bus)

When the CPU enters the standby mode, the BCU (bus control unit) stops after the current bus cycle has completed. All the chip enable signals are negated.

In basic HALT mode, the BCLK (bus clock) signal is output and DRAM refresh cycles are generated. DMA also operates.

In HALT2 or SLEEP mode, the BCLK signal stops, therefore DRAM refresh cycles cannot be generated and DMA stops.

#### Additional

The contents of the CPU registers and input/output port status are retained in the standby mode. Almost all control and data registers of the internal peripheral circuits are also retained, note, however, some registers may be changed at the transition to SLEEP mode. Refer to the section of each peripheral circuit for other precautions.