## CMOS 4-BIT SINGLE CHIP MICROCOMPUTER **E0C6001 TECHNICAL MANUAL**

E0C6001 Technical Hardware E0C6001 Technical Software

#### **PREFACE**

This manual is individualy described about the hardware and the software of the E0C6001.

#### I. E0C6001 Technical Hardware

This part explains the function of the E0C6001, the circuit configurations, and details the controlling method.

#### II. E0C6001 Technical Software

This part explains the programming method of the E0C6001.

# E0C6001 Technical Hardware

#### **CONTENTS**

| CHAPTER 1 | INTRODUCTION I-1                   |

|-----------|------------------------------------|

|           | 1.1 Configuration I-1              |

|           | 1.2 Features                       |

|           | 1.3 Block Diagram I-3              |

|           | 1.4 Pin Layout Diagram I-4         |

|           | 1.5 Pin Description I-5            |

| CHAPTER 2 | POWER SUPPLY AND INITIAL RESET I-6 |

|           | 2.1 Power Supply I-6               |

|           | 2.2 Initial Reset                  |

| CHAPTER 3 | CPU, ROM, RAM I-1                  |

|           | 3.1 CPU                            |

|           | 3.2 ROM I-1                        |

|           | 3.3 RAM I-1                        |

| CHAPTER 4 | PERIPHERAL CIRCUITS AND OPERATION I |                                             |      |  |  |  |  |  |

|-----------|-------------------------------------|---------------------------------------------|------|--|--|--|--|--|

|           | 4.1                                 | Memory Map                                  | I-13 |  |  |  |  |  |

|           | 4.2                                 | Oscillation Circuit                         | I-18 |  |  |  |  |  |

|           |                                     | Crystal oscillation circuit                 | I-18 |  |  |  |  |  |

|           |                                     | CR oscillation circuit                      | I-19 |  |  |  |  |  |

|           | 4.3                                 | Input Port (K00–K03)                        | I-20 |  |  |  |  |  |

|           |                                     | Configuration of input port                 | I-20 |  |  |  |  |  |

|           |                                     | Interrupt function                          | I-20 |  |  |  |  |  |

|           |                                     | Mask option                                 | I-22 |  |  |  |  |  |

|           |                                     | Control of input port                       | I-23 |  |  |  |  |  |

|           | 4.4                                 | Output Port (R00, R01)                      | I-25 |  |  |  |  |  |

|           |                                     | Configuration of output port                | I-25 |  |  |  |  |  |

|           |                                     | Mask option                                 | I-26 |  |  |  |  |  |

|           |                                     | Control of output port                      | I-28 |  |  |  |  |  |

|           | 4.5                                 | I/O Port (P00–P03)                          | I-31 |  |  |  |  |  |

|           |                                     | Configuration of I/O port                   | I-31 |  |  |  |  |  |

|           |                                     | I/O control register and I/O mode           | I-32 |  |  |  |  |  |

|           |                                     | Mask option                                 | I-32 |  |  |  |  |  |

|           |                                     | Control of I/O port                         | I-33 |  |  |  |  |  |

|           | 4.6                                 | LCD Driver (COM0-COM3, SEG0-SEG19)          | I-35 |  |  |  |  |  |

|           |                                     | Configuration of LCD driver                 | I-35 |  |  |  |  |  |

|           |                                     | Cadence adjustment of oscillation frequency | I-41 |  |  |  |  |  |

|           |                                     | Mask option (segment allocation)            | I-42 |  |  |  |  |  |

|           |                                     | Control of LCD driver                       | I-44 |  |  |  |  |  |

|           | 4.7                                 | Clock Timer                                 | I-45 |  |  |  |  |  |

|           |                                     | Configuration of clock timer                | I-45 |  |  |  |  |  |

|           |                                     | Interrupt function                          | I-46 |  |  |  |  |  |

|           |                                     | Control of clock timer                      | I-47 |  |  |  |  |  |

|           | 4.8                                 | Heavy Load Protection Function              | I-49 |  |  |  |  |  |

|           |                                     | Operation of heavy load protection function |      |  |  |  |  |  |

|           |                                     | Control of heavy load protection function   | I-50 |  |  |  |  |  |

|           | 4.9 Interrupt and HALT I-5                                           | 51  |

|-----------|----------------------------------------------------------------------|-----|

|           | Interrupt factors I-5                                                |     |

|           | Specific masks and factor flags for interrupt I-5                    |     |

|           | Interrupt vectors I-5                                                |     |

|           | Control of interrupt I-5                                             | 55  |

| CHAPTER 5 | BASIC EXTERNAL WIRING DIAGRAM1-5                                     | 6   |

| CHAPTER 6 | ELECTRICAL CHARACTERISTICS I-5                                       | 58  |

|           | 6.1 Absolute Maximum Rating I-5                                      | 58  |

|           | 6.2 Recommended Operating Conditions I-5                             | 59  |

|           | 6.3 DC Characteristics I-6                                           | 3C  |

|           | 6.4 Analog Circuit Characteristics and Power Current Consumption I-6 | 32  |

|           | 6.5 Oscillation Characteristics I-6                                  | 36  |

| CHAPTER 7 | PACKAGE I-6                                                          | 38  |

|           | 7.1 Plastic Package I-6                                              | 38  |

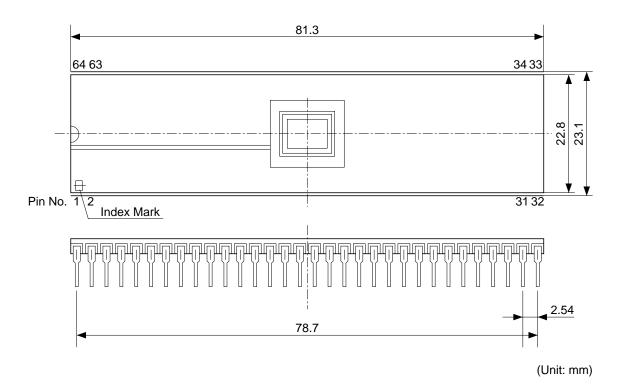

|           | 7.2 Ceramic Package for Test Samples I-6                             | 39  |

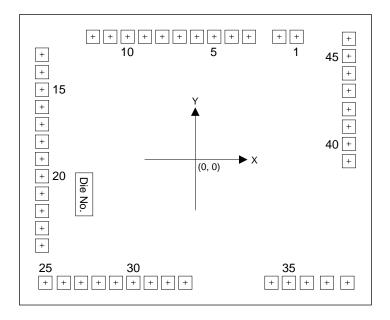

| CHAPTER 8 | PAD LAYOUT I-7                                                       | 7C  |

|           | 8.1 Diagram of Pad Layout I-7                                        | 70  |

|           | 8.2 Pad Coordinates I-7                                              | 7 1 |

#### CHAPTER 1 INTRODUCTION

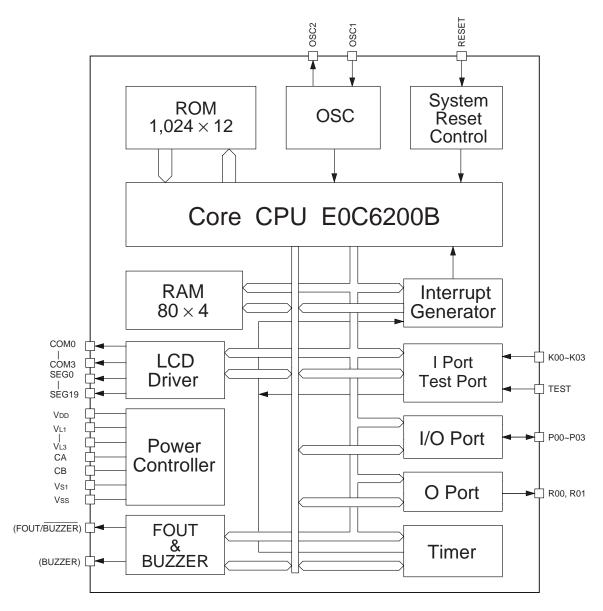

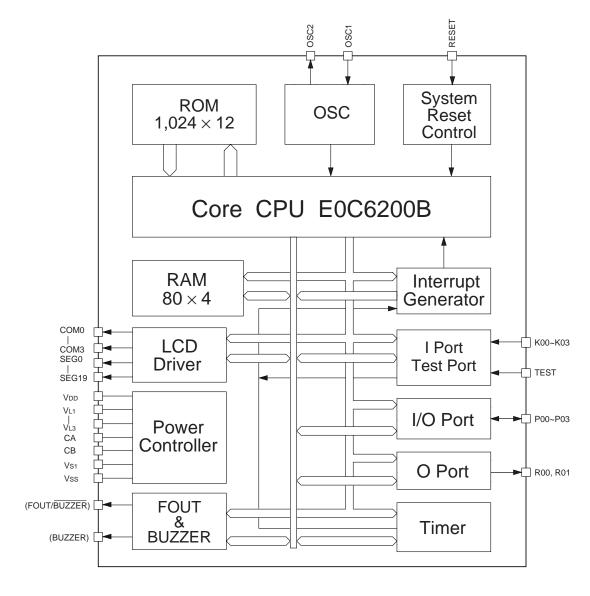

Each member of the E0C6001 Series of single chip microcomputers feature a 4-bit E0C6200B core CPU, 1,024 words of ROM (12 bits per word), 80 words of RAM (4 bits per word), an LCD driver, 4 bits for input ports (K00–K03), 2 bits for output ports (R00, R01), one 4-bit I/O port (P00–P03) and one timer (clock timer).

Because of their low voltage operation and low power consumption, the E0C6001 Series are ideal for a wide range of applications.

#### 1.1 Configuration

The E0C6001 Series are configured as follows, depending on the supply voltage.

Table 1.1.1

Configuration of the E0C6001 Series

| Model    | Supply Voltage | Supply Voltage Range | Oscillation Circuits |

|----------|----------------|----------------------|----------------------|

| E0C6001  | 3.0 V          | 1.8–3.6 V            | Crystal or CR        |

| E0C60L01 | 1.5 V          | 1.2-2.0 V            | Crystal or CR        |

#### 1.2 Features

Built-in oscillation circuit Crystal or CR oscillation circuit, 32.768 kHz (typ.)

Instruction set 100 instructions

ROM capacity  $1,024 \text{ words} \times 12 \text{ bits}$

RAM capacity (data RAM)  $80 \text{ words} \times 4 \text{ bits}$

Input port 4 bits (Supplementary pull-down resistors may be used )

Output port 2 bits (Piezo buzzer and programmable frequency output

can be driven directry by mask option)

Input/output port 4 bits

LCD driver 20 segments  $\times$  4, 3 or 2 common duty

Timer 1 system: clock timer

Interrupts:

External interrupt Input port interrupt 1 system

Internal interrupt Timer interrupt 1 system

Supply voltage 1.5 V (1.2–2.0 V) E0C60L01

3.0 V (1.8-3.6 V) E0C6001

Current consumption (typ.)  $1.0 \mu A$  (Crystal oscillation CLK = 32.768 kHz, when halted)

2.5 µA (Crystal oscillation CLK = 32.768 kHz, when executing)

Supply form QFP12-48pin (plastic) or chip

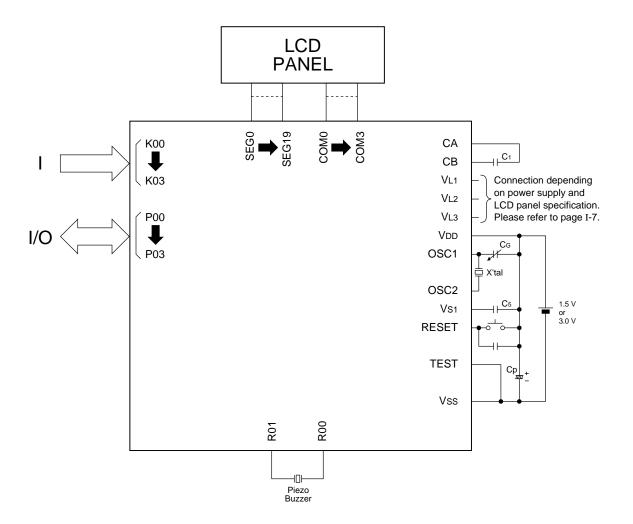

#### 1.3 Block Diagram

Fig. 1.3.1 Block diagram

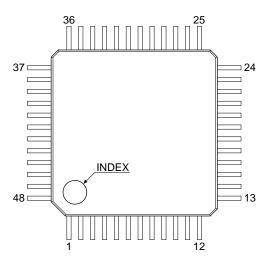

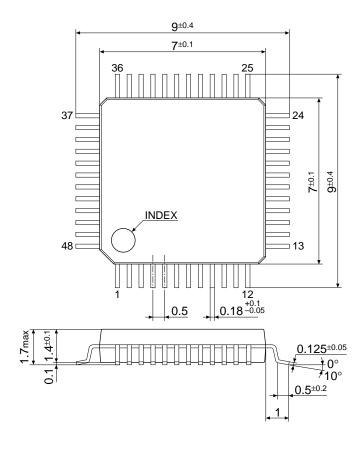

#### 1.4 Pin Layout Diagram

#### QFP12-48pin

| Pin No | Pin Name        |

|--------|----------|--------|----------|--------|----------|--------|-----------------|

| 1      | OSC2     | 13     | R01      | 25     | TEST     | 37     | COM0            |

| 2      | Vs1      | 14     | R00      | 26     | RESET    | 38     | COM1            |

| 3      | N.C.     | 15     | SEG19    | 27     | SEG9     | 39     | COM2            |

| 4      | P00      | 16     | SEG18    | 28     | SEG8     | 40     | COM3            |

| 5      | P01      | 17     | SEG17    | 29     | SEG7     | 41     | VL3             |

| 6      | P02      | 18     | SEG16    | 30     | SEG6     | 42     | VL2             |

| 7      | P03      | 19     | SEG15    | 31     | SEG5     | 43     | V <sub>L1</sub> |

| 8      | K00      | 20     | SEG14    | 32     | SEG4     | 44     | CA              |

| 9      | K01      | 21     | SEG13    | 33     | SEG3     | 45     | СВ              |

| 10     | K02      | 22     | SEG12    | 34     | SEG2     | 46     | Vss             |

| 11     | K03      | 23     | SEG11    | 35     | SEG1     | 47     | Vdd             |

| 12     | N.C.     | 24     | SEG10    | 36     | SEG0     | 48     | OSC1            |

Fig. 1.4.1 Pin assignment

N.C. = No Connection

#### 1.5 Pin Description

Table 1.5.1 Pin description

| Terminal Name | Pin No. | Input/Output | Function                                           |

|---------------|---------|--------------|----------------------------------------------------|

| Vdd           | 47      | (I)          | Power source (+) terminal                          |

| Vss           | 46      | (I)          | Power source (-) terminal                          |

| Vs1           | 2       | 0            | Oscillation and internal logic system regulated    |

|               |         |              | voltage output terminal                            |

| VL1           | 43      | 0            | LCD system reducer output terminal (VL2 × 1/2)     |

|               |         |              | / LCD system reducer output terminal (VL3 × 1/3)   |

| VL2           | 42      | 0            | LCD system booster output terminal (VL1 × 2)       |

|               |         |              | / LCD system reducer output terminal (VL3 × 2/3)   |

| VL3           | 41      | 0            | LCD system booster output terminal (VL1 × 3)       |

|               |         |              | / LCD system booster output terminal (VL2 × 3/2)   |

| CA, CB        | 44, 45  | _            | Booster capacitor connecting terminal              |

| OSC1          | 48      | I            | Crystal or CR oscillation input terminal           |

| OSC2          | 1       | 0            | Crystal or CR oscillation output terminal          |

| K00-K03       | 8-11    | I            | Input terminal                                     |

| P00-P03       | 4–7     | I/O          | I/O terminal                                       |

| R00, R01      | 14, 13  | 0            | Output terminal                                    |

| SEG0-19       | 36–27   | 0            | LCD segment output terminal                        |

|               | 24–15   |              | (convertible to DC output terminal by mask option) |

| COM0-3        | 37–40   | 0            | LCD common output terminal                         |

| RESET         | 26      | I            | Initial setting input terminal                     |

| TEST          | 25      | I            | Test input terminal                                |

#### CHAPTER 2 POWER SUPPLY AND INITIAL RESET

#### 2.1 Power Supply

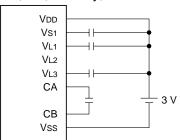

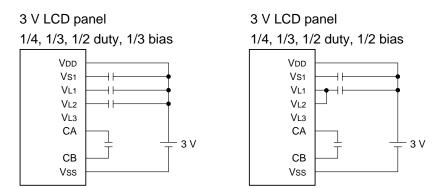

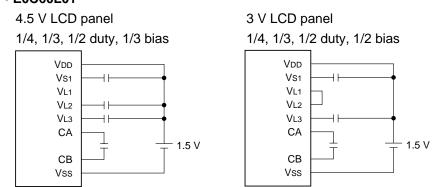

With a single external power supply (\*1) supplied to VDD through Vss, the E0C6001 Series generate the necessary internal voltages with the regulated voltage circuit (<VS1> for oscillators and internal circuit) and the voltage booster/ reducer (<VL2, VL3 or VL1, VL3> for LCDs). When the E0C6001 LCD power is selected for 4.5 V LCD panel by mask option, the E0C6001 short-circuits between <VL2> and <VSS> in internally, and the voltage booster/ reducer generates <VL1> and <VL3>. When 3.0 V LCD panel is selected, the E0C6001 short-circuits between <VL3> and <VSS>, and the voltage reducer generates <VL1> and <VL2>. The E0C60L01 short-circuits between <VL1> and <VSS>, and the voltage booster generates <VL2> and <VL3>. The voltage <VS1> for the internal circuit that is generated by the regulated voltage circuit is -1.2 V (VDD standard). Figure 2.1.1 shows the power supply configuration of the E0C6001 Series in each condition.

\*1 Supply voltage: E0C6001 ..... 3.0 V E0C60L01 .... 1.5 V

- Note External loads cannot be driven by the output voltage of the regulated voltage circuit and the voltage booster/reducer.

- See Chapter 6, "ELECTRICAL CHARACTERISTICS", for voltage values.

#### • E0C6001

4.5 V LCD panel

1/4, 1/3, 1/2 duty, 1/3 bias

Note: VL2 is shorted to VSS inside the IC.

Note: VL3 is shorted to VSS inside the IC.

#### • E0C60L01

Note: VL1 is shorted to VSS inside the IC.

Fig. 2.1.1 External element configuration of power system

#### 2.2 Initial Reset

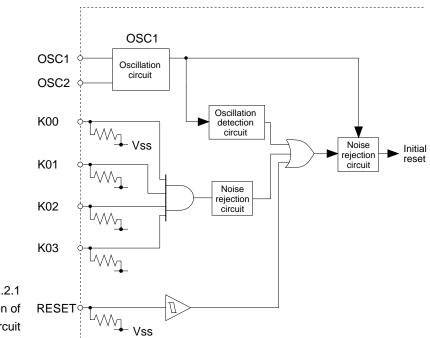

To initialize the E0C6001 Series circuits, an initial reset must be executed. There are three ways of doing this.

- (1) Initial reset by the oscillation detection circuit (Note)

- (2) External initial reset via the RESET pin

- (3) External initial reset by simultaneous high input to pins K00-K03 (depending on mask option)

Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1

Configuration of initial reset circuit

Note Be sure to use reset function (2) or (3) at power-on because the initial reset function by the oscillation detection circuit (1) may not operate normally depending on the power-on procedure.

### Oscillation detection circuit

The oscillation detection circuit outputs the initial reset signal at power-on until the crystal oscillation circuit starts oscillating, or when the crystal oscillation circuit stops oscillating for some reason.

However, use the following reset functions at power-on because the initial reset function by the oscillation detection circuit may not operate normally depending on the power-on procedure.

#### Reset pin (RESET)

An initial reset can be invoked externally by making the reset pin high. This high level must be maintained for at least 5 ms (when oscillating frequency, fosc = 32 kHz), because the initial reset circuit contains a noise rejection circuit. When the reset pin goes low the CPU begins to operate.

## Simultaneous high input to input ports (K00–K03)

Another way of invoking an initial reset externally is to input a high signal simultaneously to the input ports (K00–K03) selected with the mask option. The specified input port pins must be kept high for at least 4 sec (when oscillating frequency fosc = 32 kHz), because of the noise rejection circuit. Table 2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.1 Input port combinations

| Α | Not used        |

|---|-----------------|

| В | K00*K01         |

| С | K00*K01*K02     |

| D | K00*K01*K02*K03 |

When, for instance, mask option D (K00\*K01\*K02\*K03) is selected, an initial reset is executed when the signals input to the four ports K00–K03 are all high at the same time.

If you use this function, make sure that the specified ports do not go high at the same time during normal operation.

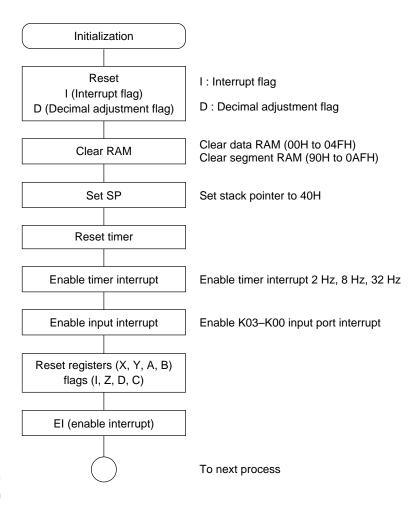

## Internal register following initialization

An initial reset initializes the CPU as shown in the table below.

Table 2.2.2 Initial values

| CPU Core             |        |                |               |  |  |  |  |  |  |

|----------------------|--------|----------------|---------------|--|--|--|--|--|--|

| Name                 | Signal | Number of Bits | Setting Value |  |  |  |  |  |  |

| Program counter step | PCS    | 8              | 00H           |  |  |  |  |  |  |

| Program counter page | PCP    | 4              | 1H            |  |  |  |  |  |  |

| New page pointer     | NPP    | 4              | 1H            |  |  |  |  |  |  |

| Stack pointer        | SP     | 8              | Undefined     |  |  |  |  |  |  |

| Index register X     | X      | 8              | Undefined     |  |  |  |  |  |  |

| Index register Y     | Y      | 8              | Undefined     |  |  |  |  |  |  |

| Register pointer     | RP     | 4              | Undefined     |  |  |  |  |  |  |

| General register A   | A      | 4              | Undefined     |  |  |  |  |  |  |

| General register B   | В      | 4              | Undefined     |  |  |  |  |  |  |

| Interrupt flag       | I      | 1              | 0             |  |  |  |  |  |  |

| Decimal flag         | D      | 1              | 0             |  |  |  |  |  |  |

| Zero flag            | Z      | 1              | Undefined     |  |  |  |  |  |  |

| Carry flag           | C      | 1              | Undefined     |  |  |  |  |  |  |

| Peripheral Circuits      |                |               |  |  |  |  |  |  |

|--------------------------|----------------|---------------|--|--|--|--|--|--|

| Name                     | Number of Bits | Setting Value |  |  |  |  |  |  |

| RAM                      | 80×4           | Undefined     |  |  |  |  |  |  |

| Display memory           | $20 \times 4$  | Undefined     |  |  |  |  |  |  |

| Other peripheral circuit | _              | *1            |  |  |  |  |  |  |

<sup>\*1:</sup> See section 4.1, "Memory Map"

#### 2.3 Test Pin (TEST)

This pin is used when IC is inspected for shipment. During normal operation connect it to Vss.

#### CHAPTER 3 CPU, ROM, RAM

#### 3.1 CPU

The E0C6001 Series employs the E0C6200B core CPU, so that register configuration, instructions, and so forth are virtually identical to those in other processors in the family using the E0C6200B. Refer to the "E0C6200/6200A Core CPU Manual" for details of the E0C6200B.

Note the following points with regard to the E0C6001 Series:

- (1) The SLEEP operation is not provided, so the SLP instruction cannot be used.

- (2) Because the ROM capacity is 1,024 words, 12 bits per word, bank bits are unnecessary, and PCB and NBP are not used.

- (3) The RAM page is set to 0 only, so the page part (XP, YP) of the index register that specifies addresses is invalid.

| PUSH | XP   | PUSH | ΥP   |

|------|------|------|------|

| POP  | XP   | POP  | ΥP   |

| LD   | XP,r | LD   | YP,r |

| LD   | r.XP | LD   | r.YP |

#### 3.2 **ROM**

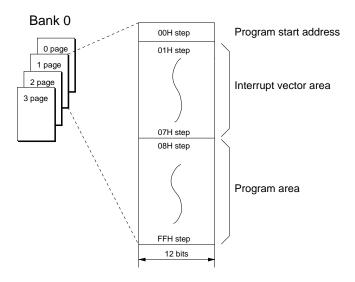

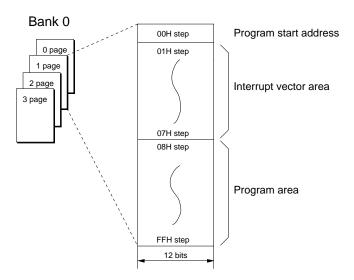

The built-in ROM, a mask ROM for the program, has a capacity of  $1,024 \times 12$ -bit steps. The program area is 4 pages (0–3), each consisting of 256 steps (00H–FFH). After an initial reset, the program start address is page 1, step 00H. The interrupt vector is allocated to page l, steps 01H–07H.

Fig. 3.2.1 ROM configuration

#### 3.3 **RAM**

The RAM, a data memory for storing a variety of data, has a capacity of 80 words, 4-bit words. When programming, keep the following points in mind:

- (1) Part of the data memory is used as stack area when saving subroutine return addresses and registers, so be careful not to overlap the data area and stack area.

- (2) Subroutine calls and interrupts take up three words on the stack.

- (3) Data memory 000H–00FH is the memory area pointed by the register pointer (RP).

## CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

Peripheral circuits (timer, I/O, and so on) of the E0C6001 Series are memory mapped. Thus, all the peripheral circuits can be controlled by using memory operations to access the I/O memory. The following sections describe how the peripheral circuits operate.

#### 4.1 Memory Map

The data memory of the E0C6001 Series has an address space of 113 words, of which 32 words are allocated to display memory and 13 words, to I/O memory. Figure 4.1.1 show the overall memory map for the E0C6001 Series, and Tables 4.1.1(a)–(d), the memory maps for the peripheral circuits (I/O space).

| Address | Low  |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|---------|------|----|---------------------------------|----|----|-------|------|-------|-------|--------|---------|--------|-------|----|----|----|----|

|         |      | 0  | 1                               | 2  | 3  | 4     | 5    | 6     | 7     | 8      | 9       | Α      | В     | С  | D  | E  | F  |

| Page    | High |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 0    | M0 | M1                              | M2 | МЗ | M4    | M5   | M6    | M7    | M8     | M9      | MA     | MB    | МС | MD | ME | MF |

|         | 1    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 2    |    | RAM area (000H-04FH)            |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 3    |    |                                 |    |    |       | 80   | ) wor | ds x  | 4 bits | (R/V    | V)     |       |    |    |    |    |

|         | 4    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 5    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 6    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

| 0       | 7    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

| 0       | 8    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | 9    |    | Display memory area (090H-0AFH) |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | Α    |    |                                 |    |    |       | 32 w | ords  | x 4 b | its (V | Vrite ( | only)  |       |    |    |    |    |

|         | В    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | С    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | D    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | Е    |    |                                 |    |    |       |      |       |       |        |         |        |       |    |    |    |    |

|         | F    |    |                                 |    |    | I/O r | nemo | ry ar | ea    | Table  | s 4.′   | 1.1(a) | )–(d) |    |    |    |    |

Fig. 4.1.1 Memory map

Note Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these areas.

Unused area

Table 4.1.1(a) I/O memory map

| Address |       | Regi  | ister |       |       |       |        |      | Comment                                     |

|---------|-------|-------|-------|-------|-------|-------|--------|------|---------------------------------------------|

| Address | D3    | D2    | D1    | D0    | Name  | SR *1 | 1      | 0    | Comment                                     |

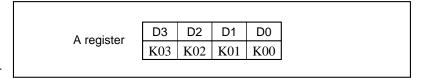

|         | K03   | K02   | K01   | K00   | K03   | - *2  | High   | Low  |                                             |

| 05011   |       | ı     | ₹     |       | K02   | - *2  | High   | Low  | V (V00 V00)                                 |

| 0E0H    |       |       |       |       | K01   | - *2  | High   | Low  | Input port (K00–K03)                        |

|         |       |       |       |       | K00   | - *2  | High   | Low  |                                             |

|         | TM3   | TM2   | TM1   | TM0   | TM3   | -     | High   | Low  | Timer data (clock timer 2 Hz)               |

| 0E4H    |       | F     | ?     |       | TM2   | -     | High   | Low  | Timer data (clock timer 4 Hz)               |

| 00411   |       |       |       |       | TM1   | -     | High   | Low  | Timer data (clock timer 8 Hz)               |

|         |       |       |       |       | TM0   | -     | High   | Low  | Timer data (clock timer 16 Hz)              |

|         | EIK03 | EIK02 | EIK01 | EIK00 | EIK03 | 0     | Enable | Mask | Interrupt mask register (K03)               |

| 0E8H    |       | R     | W     |       | EIK02 | 0     | Enable | Mask | Interrupt mask register (K02)               |

| 02011   |       |       |       |       | EIK01 | 0     | Enable | Mask | Interrupt mask register (K01)               |

|         |       |       |       |       | EIK00 | 0     | Enable | Mask | Interrupt mask register (K00)               |

|         | 0     | EIT2  | EIT8  | EIT32 | 0 *5  |       |        |      |                                             |

| 0EBH    | R     |       | R/W   |       | EIT2  | 0     | Enable | Mask | Interrupt mask register (clock timer 2 Hz)  |

| VEDIT   |       |       |       |       | EIT8  | 0     | Enable | Mask | Interrupt mask register (clock timer 8 Hz)  |

|         |       |       |       |       | EIT32 | 0     | Enable | Mask | Interrupt mask register (clock timer 32 Hz) |

- \* 1 Initial value following initial reset

- \* 2 Not set in the circuit

- \* 3 Undefined

- \* 4 Reset (0) immediately after being read

- \* 5 Constantly 0 when being read

- \* 6 Refer to main manual

Table 4.1.1(b) I/O memory map

| Address | Register                   |     |             |                    |             |       |      | Comment                                   |                                          |

|---------|----------------------------|-----|-------------|--------------------|-------------|-------|------|-------------------------------------------|------------------------------------------|

| Address | D3                         | D2  | D1          | D0                 | Name        | SR *1 | 1    | 0                                         | Comment                                  |

|         | 0                          | 0   | 0           | IK0                | 0 *5        |       |      |                                           |                                          |

| 0EDH    | R                          |     |             | 0 *5               |             |       |      |                                           |                                          |

| DEDH    |                            |     |             |                    | 0 *5        |       |      |                                           |                                          |

|         |                            |     |             |                    | IK0 *4      | 0     | Yes  | No                                        | Interrupt factor flag (K00–K03)          |

|         | 0                          | IT2 | IT8         | IT32               | 0 *5        |       |      |                                           |                                          |

| 0EFH    | R                          |     |             |                    | IT2 *4      | 0     | Yes  | No                                        | Interrupt factor flag (clock timer 2 Hz) |

| UEFH    |                            |     |             |                    | IT8 *4      | 0     | Yes  | No                                        | Interrupt factor flag (clock timer 8 Hz) |

|         |                            |     |             | IT32 <sup>*4</sup> | 0           | Yes   | No   | Interrupt factor flag (clock timer 32 Hz) |                                          |

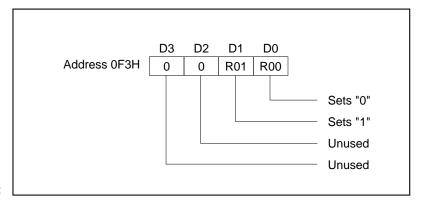

|         | 0 0 R01 R00<br>BUZZER FOUT |     | R00<br>FOUT | 0 *5               |             |       |      |                                           |                                          |

| 0F3H    | F                          | 3   | R           | W                  | 0 *5<br>R01 | 0     | High | Low                                       | R01 output port data                     |

| UFSH    |                            |     | •           |                    | BUZZER      | 0     | ON   | OFF                                       | Buzzer ON/OFF control register           |

|         |                            |     |             |                    | R00         | 0     | High | Low                                       | R00 output port data                     |

|         |                            |     |             |                    | FOUT        | 0     | ON   | OFF                                       | Frequency output ON/OFF control register |

|         | P03                        | P02 | P01         | P00                | P03         | - *2  | High | Low                                       |                                          |

| 0F6H    | R/W                        |     |             | P02                | - *2        | High  | Low  | I/O port (P00–P03)                        |                                          |

| 0.011   |                            |     |             |                    | P01         | - *2  | High | Low                                       | 10 poit (1 00-1 03)                      |

|         |                            |     |             |                    | P00         | - *2  | High | Low                                       |                                          |

- \* 1 Initial value following initial reset

- \* 2 Not set in the circuit

- \* 3 Undefined

- \* 4 Reset (0) immediately after being read

- \* 5 Constantly 0 when being read

- \* 6 Refer to main manual

Table 4.1.1(c) I/O memory map

| Address | Register |       |    |     |       |       | Comment       |                |                                     |

|---------|----------|-------|----|-----|-------|-------|---------------|----------------|-------------------------------------|

| Address | D3       | D2    | D1 | D0  | Name  | SR *1 | 1             | 0              | Comment                             |

| 0F9H    | 0        | TMRST | 0  | 0   | 0 *5  |       |               |                |                                     |

|         | R        | W     | I  | ₹   | TMRST | Reset | Reset         | -              | Clock timer reset                   |

| 0.011   |          |       |    |     | 0 *5  |       |               |                |                                     |

|         |          |       |    |     | 0 *5  |       |               |                |                                     |

|         | HLMOD    | 0     | 0  | 0   | HLMOD | 0     | Heavy<br>load | Normal<br>load | Heavy load protection mode register |

| 0FAH    | R/W      |       | R  |     | 0 *5  |       |               |                |                                     |

| 017111  |          |       |    |     | 0 *5  |       |               |                |                                     |

|         |          |       |    |     | 0 *5  |       |               |                |                                     |

|         | CSDC     | 0     | 0  | 0   | CSDC  | 0     | Static        | Dynamic        | LCD drive switch                    |

| 0FBH    | R/W      |       | R  |     | 0 *5  |       |               |                |                                     |

| 0. 2    |          |       |    |     | 0 *5  |       |               |                |                                     |

|         |          |       |    |     | 0 *5  |       |               |                |                                     |

|         | 0        | 0     | 0  | IOC | 0 *5  |       |               |                |                                     |

| 0FCH    |          | R     |    | R/W | 0 *5  |       |               |                |                                     |

| 0,0,1   |          |       |    |     | 0 *5  |       |               |                |                                     |

|         |          |       |    |     | IOC   | 0     | Output        | Input          | I/O port P00-P03 Input/Output       |

- \* 1 Initial value following initial reset

- \* 2 Not set in the circuit

- \* 3 Undefined

- \* 4 Reset (0) immediately after being read

- \* 5 Constantly 0 when being read

- \* 6 Refer to main manual

Table 4.1.1(d) I/O memory map

| Address |      | Reg | ister  |        |        |       |       |       | Comment                                                                                |

|---------|------|-----|--------|--------|--------|-------|-------|-------|----------------------------------------------------------------------------------------|

| Address | D3   | D2  | D1     | D0     | Name   | SR *1 | 1     | 0     | Comment                                                                                |

|         | XBZR | 0   | XFOUT1 | XFOUT0 | XBZR   | 0     | 2 kHz | 4 kHz | Buzzer frequency control                                                               |

| 0FDH    | R/W  | R   | R      | W      | 0 *5   |       |       |       |                                                                                        |

| OI DIT  |      |     |        |        | XFOUT1 | 0     | High  | Low   | FOUT frequency control:<br>XFOUT1(0), XFOUT0(0) -> F1                                  |

|         |      |     |        |        | XFOUT0 | 0     | High  | Low   | XFOUT1(0), XFOUT0(1) -> F2<br>XFOUT1(1), XFOUT0(0) -> F3<br>XFOUT1(1), XFOUT0(1) -> F4 |

- \* 1 Initial value following initial reset

- \* 2 Not set in the circuit

- \* 3 Undefined

- \* 4 Reset (0) immediately after being read

- \* 5 Constantly 0 when being read

- \* 6 Refer to main manual

#### 4.2 Oscillation Circuit

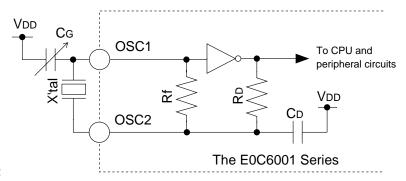

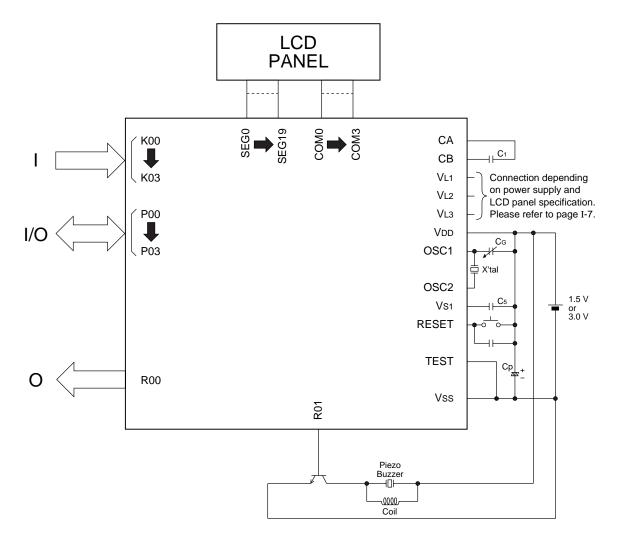

### Crystal oscillation circuit

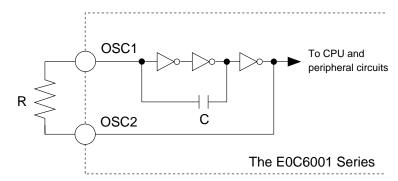

The E0C6001 Series have a built-in crystal oscillation circuit. This circuit generates the operating clock for the CPU and peripheral circuit on connection to an external crystal oscillator (typ. 32.768 kHz) and trimmer capacitor (5–25 pF).

Figure 4.2.1 is the block diagram of the crystal oscillation circuit.

Fig. 4.2.1 Crystal oscillation circuit

As Figure 4.2.1 indicates, the crystal oscillation circuit can be configured simply by connecting the crystal oscillator (X'tal) between the OSC1 and OSC2 pins and the trimmer capacitor (CG) between the OSC1 and VDD pins.

Note The OSC1 and OSC2 terminals on the board should be shielded with the VDD (+ side).

#### **CR** oscillation circuit

For the E0C6001 Series, CR oscillation circuit (typ. 65 kHz) may also be selected by a mask option. Figure 4.2.2 is the block diagram of the CR oscillation circuit.

Fig. 4.2.2 CR oscillation circuit

As Figure 4.2.2 indicates, the CR oscillation circuit can be configured simply by connecting the register (R) between pins OSC1 and OSC2 since capacity (C) is built-in. See Chapter 6, "ELECTRICAL CHARACTERISTICS" for R value.

#### 4.3 Input Port (K00-K03)

## Configuration of input port

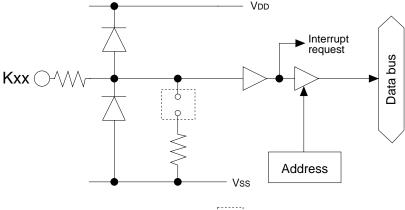

The E0C6001 Series have a 4-bit general-purpose input port. Each of the input port pins (K00–K03) has an internal pull-down resistance. The pull-down resistance can be selected for each bit with the mask option.

Figure 4.3.1 shows the configuration of input port.

Fig. 4.3.1 Configuration of input port

Mask option

Selecting "pull-down resistance enabled" with the mask option allows input from a push button, key matrix, and so forth. When "pull-down resistance disabled" is selected, the port can be used for slide switch input and interfacing with other LSIs.

#### Interrupt function

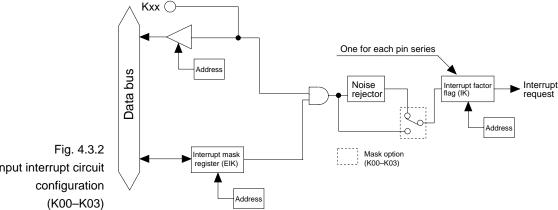

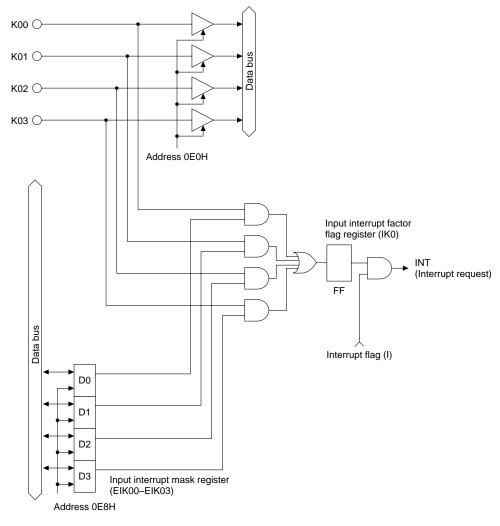

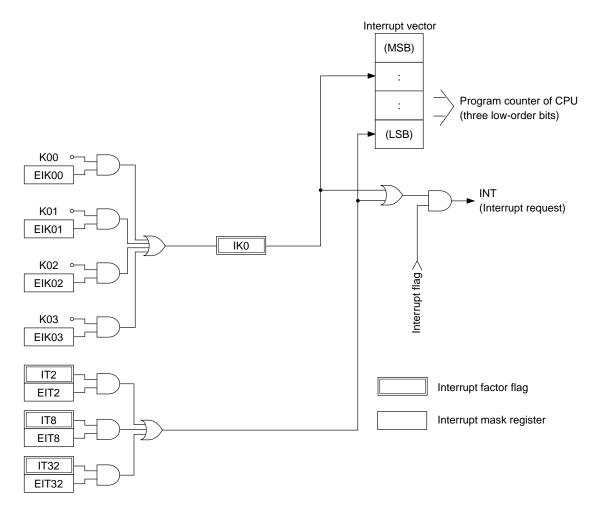

All four input port bits (K00–K03) provide the interrupt function. The conditions for issuing an interrupt can be set by the software for the four bits. Also, whether to mask the interrupt function can be selected individually for all four bits by the software. Figure 4.3.2 shows the configuration of K00–K03.

Input interrupt circuit

The interrupt mask registers (EIK00-EIK03) enable the interrupt mask to be selected individually for K00-K03. An interrupt occurs when the input value which are not masked change and the interrupt factor flag (IKO) is set to 1.

#### Input interrupt programing related precautions

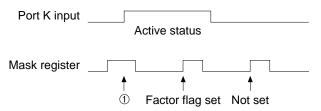

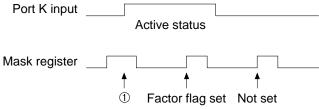

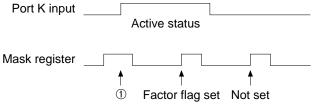

Fig. 4.3.3 Input interrupt timing

When the content of the mask register is rewritten, while the port K input is in the active status. The input interrupt factor flag is set at 1.

When using an input interrupt, if you rewrite the content of the mask register, when the value of the input terminal which becomes the interrupt input is in the active status (input terminal = high status), the factor flag for input interrupt may be set.

For example, a factor flag is set with the timing of ① shown in Figure 4.3.3. However, when clearing the content of the mask register with the input terminal kept in the high status and then setting it, the factor flag of the input interrupt is again set at the timing that has been set.

Consequently, when the input terminal is in the active status (high status), do not rewrite the mask register (clearing, then setting the mask register), so that a factor flag will only set at the rising edge in this case. When clearing, then setting the mask register, set the mask register, when the input terminal is not in the active status (low status).

#### Mask option

The contents that can be selected with the input port mask option are as follows:

- (1) An internal pull-down resistance can be selected for each of the four bits of the input ports (K00–K03). Having selected "pull-down resistance disabled", take care that the input does not float. Select "pull-down resistance enabled" for input ports that are not being used.

- (2) The input interrupt circuit contains a noise rejection circuit to prevent interrupts form occurring through noise. The mask option enables selection of the noise rejection circuit for each separate pin series. When "use" is selected, a maximum delay of 0.5 ms (fosc = 32 kHz) occurs from the time an interrupt condition is established until the interrupt factor flag (IK) is set to 1.

#### Control of input port

Table 4.3.1 list the input port control bits and their addresses.

Table 4.3.1 Input port control bits

| Address | Register |       |       | Comment |       |        |        |                               |                                 |

|---------|----------|-------|-------|---------|-------|--------|--------|-------------------------------|---------------------------------|

| Address | D3       | D2    | D1    | D0      | Name  | SR     | 1      | 0                             | Comment                         |

|         | K03      | K02   | K01   | K00     | K03   | -      | High   | Low                           |                                 |

| 0E0H    | R        |       |       |         | K02   | -      | High   | Low                           | V (VOO VOO)                     |

| UEUH    |          |       |       |         | K01   | -      | High   | Low                           | Input port (K00–K03)            |

|         |          |       |       |         | K00   | -      | High   | Low                           |                                 |

|         | EIK03    | EIK02 | EIK01 | EIK00   | EIK03 | 0      | Enable | Mask                          | Interrupt mask register (K03)   |

| 0E8H    | R/W      |       |       |         | EIK02 | 0      | Enable | Mask                          | Interrupt mask register (K02)   |

| OLOIT   |          |       |       | EIK01   | 0     | Enable | Mask   | Interrupt mask register (K01) |                                 |

|         |          |       |       |         | EIK00 | 0      | Enable | Mask                          | Interrupt mask register (K00)   |

|         | 0        | 0     | 0     | IK0     | 0     |        |        |                               |                                 |

| 0EDH    | R        |       |       | 0       |       |        |        |                               |                                 |

| OLDIT   |          |       |       | 0       |       |        |        |                               |                                 |

|         |          |       |       |         | IK0   | 0      | Yes    | No                            | Interrupt factor flag (K00–K03) |

#### K00-K03 Input port data (0E0H)

The input data of the input port pins can be read with these registers.

When 1 is read: High level When 0 is read: Low level Writing: Invalid

The value read is 1 when the pin voltage of the four bits of the input port (K00–K03) goes high (VDD), and 0 when the voltage goes low (VSS). These bits are reading, so writing cannot be done.

#### EIK00-EIK03 Interrupt mask registers (0E8H)

Masking the interrupt of the input port pins can be done with these registers.

When 1 is written: Enable When 0 is written: Mask Reading: Valid

With these registers, masking of the input port bits can be done for each of the four bits. After an initial reset, these registers are all set to 0.

#### IKO Interrupt factor flag (0EDH)

This flag indicates the occurrence of an input interrupt.

When 1 is read: Interrupt has occurred

When 0 is read: Interrupt has not occurred

Writing: Invalid

The interrupt factor flag IKO is associated with KOO–KO3. From the status of this flag, the software can decide whether an input interrupt has occurred.

This flag is reset when the software has read it.

Reading of interrupt factor flag is available at EI, but be careful in the following cases.

If the interrupt mask register value corresponding to the interrupt factor flag to be read is set to 1, an interrupt request will be generated by the interrupt factor flag set timing, or an interrupt request will not be generated. After an initial reset, this flag is set to 0.

#### 4.4 Output Port (R00, R01)

## Configuration of output port

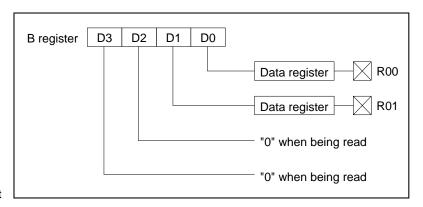

The E0C6001 Series have a 2-bit general output port (R00, R01).

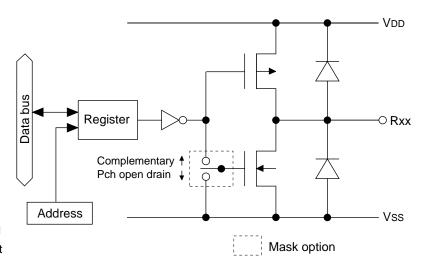

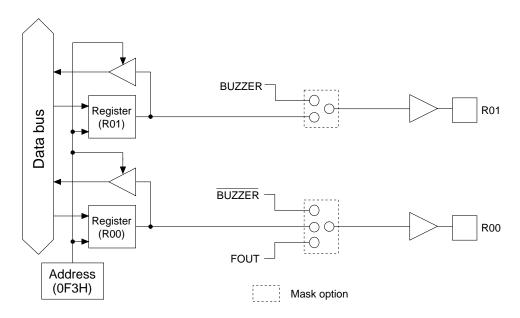

Output specification of the output port can be selected in a bit unit with the mask option. Two kinds of output specifications are available: complementary output and Pch open drain output. Also, the mask option enables the output ports R00 and R01 to be used as special output ports. Figure 4.4.1 shows the configuration of the output port.

Fig. 4.4.1 Configuration of output port

#### Mask option

The mask option enables the following output port selection.

#### (1) Output specification of output port

The output specifications for the output port (R00, R01) may be either complementary output or Pch open drain output for each of the two bits. However, even when Pch open drain output is selected, a voltage exceeding the source voltage must not be applied to the output port.

#### (2) Special output

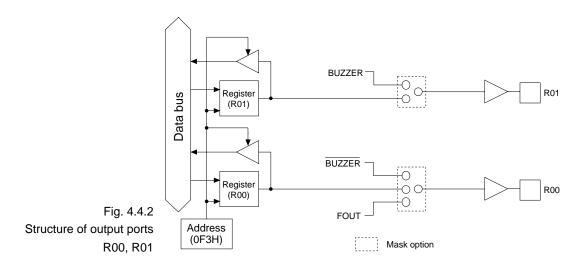

In addition to the regular DC output, special output can be selected for output ports R00 and R01, as shown in Table 4.4.1. Figure 4.4.2 shows the structure of output ports R00 and R01.

Table 4.4.1 Special output

| Pin Name | When Special Output is Selected |  |  |  |  |  |  |

|----------|---------------------------------|--|--|--|--|--|--|

| R00      | FOUT or BUZZER                  |  |  |  |  |  |  |

| R01      | BUZZER                          |  |  |  |  |  |  |

FOUT (R00) When output port R00 is set for FOUT output, this port will generate fosc (CPU operating clock frequency) or clock frequency divided into fosc. Clock frequency may be selected individually for F1-F4, from among 5 types by mask option; one among F1-F4 is selected by software and used. The types of frequency which may be selected are shown in Table 4.4.2.

Table 4.4.2 FOUT clock frequency

| Mask   | Clock Frequency (Hz) fosc = 32.768 kHz |               |               |               |  |  |  |  |  |

|--------|----------------------------------------|---------------|---------------|---------------|--|--|--|--|--|

| Option | F1                                     | F2            | F3            | F4            |  |  |  |  |  |

| Sets   | (D1,D0)=(0,0)                          | (D1,D0)=(0,1) | (D1,D0)=(1,0) | (D1,D0)=(1,1) |  |  |  |  |  |

| Set 1  | 256                                    | 512           | 1,024         | 2,048         |  |  |  |  |  |

|        | (fosc/128)                             | (fosc/64)     | (fosc/32)     | (fosc/16)     |  |  |  |  |  |

| Set 2  | 512                                    | 1,024         | 2,048         | 4,096         |  |  |  |  |  |

|        | (fosc/64)                              | (fosc/32)     | (fosc/16)     | (fosc/8)      |  |  |  |  |  |

| Set 3  | 1,024                                  | 2,048         | 4,096         | 8,192         |  |  |  |  |  |

|        | (fosc/32)                              | (fosc/16)     | (fosc/8)      | (fosc/4)      |  |  |  |  |  |

| Set 4  | 2,048                                  | 4,096         | 8,192         | 16,384        |  |  |  |  |  |

|        | (fosc/16)                              | (fosc/8)      | (fosc/4)      | (fosc/2)      |  |  |  |  |  |

| Set 5  | 4,096                                  | 8,192         | 16,384        | 32,768        |  |  |  |  |  |

|        | (fosc/8)                               | (fosc/4)      | (fosc/2)      | (fosc/1)      |  |  |  |  |  |

(D1, D0) = (XFOUT1, XFOUT0)

Note A hazard may occur when the FOUT signal is turned on or off.

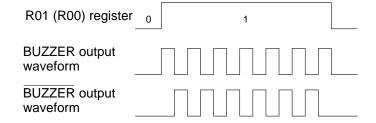

BUZZER, BUZZER Output ports R01 and R00 may be set to BUZZER output (R01, R00) and  $\overline{BUZZER}$  output (BUZZER reverse output), respectively, allowing for direct driving of the piezo-electric buzzer. BUZZER output (R00) may only be set if R01 is set to BUZZER output. In such case, whether ON/OFF of the BUZZER output is done through R00 register or is controlled through R01 simultaneously with BUZZER output is also selected by mask option.

> The frequency of buzzer output may be selected by software to be either 2 kHz or 4 kHz.

### Control of output port

Table 4.4.3 lists the output port control bits and their addresses.

Table 4.4.3 Control bits of output port

| Address |       | Reg | ister         |             |        |     |                      |                                          | Comment                                                                                |

|---------|-------|-----|---------------|-------------|--------|-----|----------------------|------------------------------------------|----------------------------------------------------------------------------------------|

| Address | D3    | D2  | D1            | D0          | Name   | SR  | 1                    | 0                                        | Comment                                                                                |

|         | 0     | 0   | R01<br>BUZZER | R00<br>FOUT | 0      |     |                      |                                          |                                                                                        |

| 0F3H    | R R/W |     | 0<br>R01      | 0           | High   | Low | R01 output port data |                                          |                                                                                        |

| 01 311  |       |     |               |             | BUZZER | 0   | ON                   | OFF                                      | Buzzer ON/OFF control register                                                         |

|         |       |     |               |             | R00    | 0   | High                 | Low                                      | R00 output port data                                                                   |

|         |       |     |               | FOUT        | 0      | ON  | OFF                  | Frequency output ON/OFF control register |                                                                                        |

|         | XBZR  | 0   | XFOUT1 XFOUT0 |             | XBZR   | 0   | 2 kHz                | 4 kHz                                    | Buzzer frequency control                                                               |

| 0FDH    | R/W   | R   | R/W           |             | 0      |     |                      |                                          |                                                                                        |

| 01 511  |       |     |               |             | XFOUT1 | 0   | High                 | Low                                      | FOUT frequency control:<br>XFOUT1(0), XFOUT0(0) -> F1                                  |

|         |       |     |               |             | XFOUT0 | 0   | High                 | Low                                      | XFOUT1(0), XFOUT0(1) -> F2<br>XFOUT1(1), XFOUT0(0) -> F3<br>XFOUT1(1), XFOUT0(1) -> F4 |

R00, R01 Output port data (0F3H D0, 0F3H D1)

Sets the output data for the output ports.

When 1 is written: High output

When 0 is written: Low output

Reading: Valid

The output port pins output the data written to the corresponding registers (R00, R01) without changing it. When 1 is written to the register, the output port pin goes high (VDD), and when 0 is written, the output port pin goes low (VSS). After an initial reset, all the registers are set to 0.

R00 (when FOUT is Special output port data (0F3H D0)

selected) Controls the FOUT (clock) output.

When 1 is written: Clock output

When 0 is written: Low level (DC) output

Reading: Valid

FOUT output can be controlled by writing data to R00. After an initial reset, this register is set to 0.

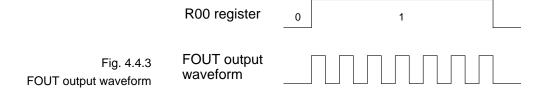

Figure 4.4.3 shows the output waveform for FOUT output.

XFOUT0, XFOUT1 FOUT frequency control (0FDH D0, 0FDH D1)

Selects the output frequency when R00 port is set for FOUT output.

Table 4.4.4 FOUT frequency selection

| XFOUT1 | XFOUT0 | Frequency Selection |

|--------|--------|---------------------|

| 0      | 0      | F1                  |

| 0      | 1      | F2                  |

| 1      | 0      | F3                  |

| 1      | 1      | F4                  |

After an initial reset, these registers are set to 0.

R00, R01 (when BUZZER Special output port data (0F3H D0, 0F3H D1) and BUZZER is Controls the buzzer output.

selected)

When 1 is written: Buzzer output

When 0 is written: Low level (DC) output

Reading: Valid

BUZZER and BUZZER output can be controlled by writing data to R00 and R01.

When BUZZER output by R01 register control is selected by mask option, BUZZER output and BUZZER output can be controlled simultaneously by writing data to R01 register. After an initial reset, these registers are set to 0.

Figure 4.4.4 shows the output waveform for buzzer output.

Fig. 4.4.4 Buzzer output waveform

XBZR Buzzer frequency control (0FDH D3)

Selects the frequency of the buzzer signal.

When 1 is written: 2 kHz When 0 is written: 4 kHz Reading: Valid

When R00 and R01 port is set to buzzer output, the frequency of the buzzer signal can be selected by this register. When 1 is written to this register, the frequency is set in 2 kHz, and in 4 kHz when 0 is written.

After an initial reset, this register is set to 0.

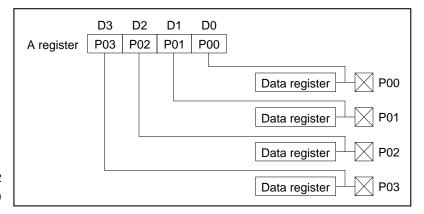

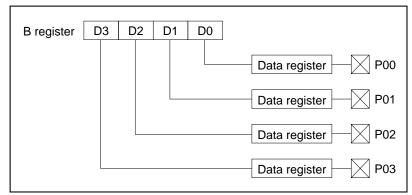

# 4.5 I/O Port (P00-P03)

# Configuration of I/O port

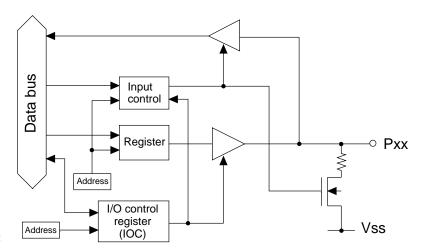

The E0C6001 Series have a 4-bit general-purpose I/O port. Figure 4.5.1 shows the configuration of the I/O port. The four bits of the I/O port P00–P03 can be set to either input mode or output mode. The mode can be set by writing data to the I/O control register (IOC).

Fig. 4.5.1 Configuration of I/O port

# I/O control register and I/O mode

Input or output mode can be set for the four bits of I/O port P00–P03 by writing data into I/O control register IOC. To set the input mode, 0 is written to the I/O control register. When an I/O port is set to input mode, its impedance becomes high and it works as an input port. However, the input line is pulled down when input data is read.

The output mode is set when 1 is written to the I/O control register (IOC). When an I/O port set to output mode works as an output port, it outputs a high signal (VDD) when the port output data is 1, and a low signal (VSS) when the port output data is 0.

After an initial reset, the I/O control register is set to 0, and the I/O port enters the input mode.

# Mask option

The output specification during output mode (IOC = 1) of the I/O port can be set with the mask option for either complementary output or Pch open drain output. This setting can be performed for each bit of the I/O port. However, when Pch open drain output has been selected, voltage in excess of the supply voltage must not be applied to the port.

## Control of I/O port

Table 4.5.1 lists the I/O port control bits and their addresses.

Table 4.5.1 I/O port control bits

| Address |     | Reg | ister |     |      |    |        |       | . Comment                     |  |  |

|---------|-----|-----|-------|-----|------|----|--------|-------|-------------------------------|--|--|

| Addiess | D3  | D2  | D1    | D0  | Name | SR | 1      | 0     | Comment                       |  |  |

|         | P03 | P02 | P01   | P00 | P03  | -  | High   | Low   |                               |  |  |

| 0F6H    |     | R/  | /W    |     | P02  | -  | High   | Low   | 1/0 (P00 P02)                 |  |  |

| UFOR    |     |     |       |     | P01  | -  | High   | Low   | I/O port (P00–P03)            |  |  |

|         |     |     |       |     | P00  | -  | High   | Low   |                               |  |  |

|         | 0   | 0   | 0     | IOC | 0    |    |        |       |                               |  |  |

| 0FCH    |     | R   |       | R/W | 0    |    |        |       |                               |  |  |

| UFCH    |     |     |       |     | 0    |    |        |       |                               |  |  |

|         |     |     |       |     | IOC  | 0  | Output | Input | I/O port P00–P03 Input/Output |  |  |

#### P00-P03 I/O port data (0F6H)

I/O port data can be read and output data can be written through the port.

· When writing data

When 1 is written: High level When 0 is written: Low level

When an I/O port is set to the output mode, the written data is output from the I/O port pin unchanged. When 1 is written as the port data, the port pin goes high (VDD), and when 0 is written, the level goes low (VSS). Port data can also be written in the input mode.

· When reading data

When 1 is read: High level When 0 is read: Low level

The pin voltage level of the I/O port is read. When the I/O port is in the input mode the voltage level being input to the port pin can be read; in the output mode the output voltage level can be read. When the pin voltage is high (VDD) the port data read is 1, and when the pin voltage is low (VSS) the data is 0. Also, the built-in pull-down resistance functions during reading, so the I/O port pin is pulled down.

- Note When the I/O port is set to the output mode and a low-impedance load is connected to the port pin, the data written to the register may differ from the data read.

- When the I/O port is set to the input mode and a low-level voltage (Vss) is input by the built-in pull-down resistance, an erroneous input results if the time constant of the capacitive load of the input line and the built- in pull-down resistance load is greater than the read-out time. When the input data is being read, the time that the input line is pulled down is equivalent to 0.5 cycles of the CPU system clock. Hence, the electric potential of the pins must settle within 0.5 cycles. If this condition cannot be met, some measure must be devised, such as arranging a pull-down resistance externally, or performing multiple read-outs.

#### IOC I/O control register (0FCH D0)

The input or output I/O port mode can be set with this register.

When 1 is written: Output mode

When 0 is written: Input mode

Reading: Valid

The input or output mode of the I/O port is set in units of four bits. For instance, IOC sets the mode for P00–P03. Writing 1 to the I/O control register makes the I/O port enter the output mode, and writing 0, the input mode. After an initial reset, the IOC register is set to 0, so the I/O port is in the input mode.

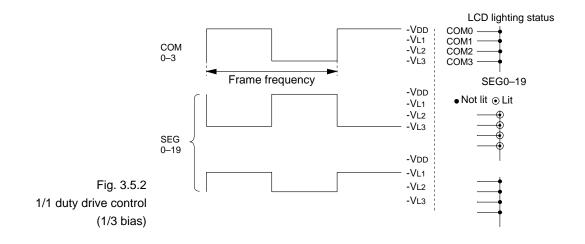

## 4.6 LCD Driver (COM0-COM3, SEG0-SEG19)

# Configuration of LCD driver

The E0C6001 Series have four common pins and 20 (SEG0–SEG19) segment pins, so that an LCD with a maximum of  $80~(20\times4)$  segments can be driven. The power for driving the LCD is generated by the CPU internal circuit, so there is no need to supply power externally.

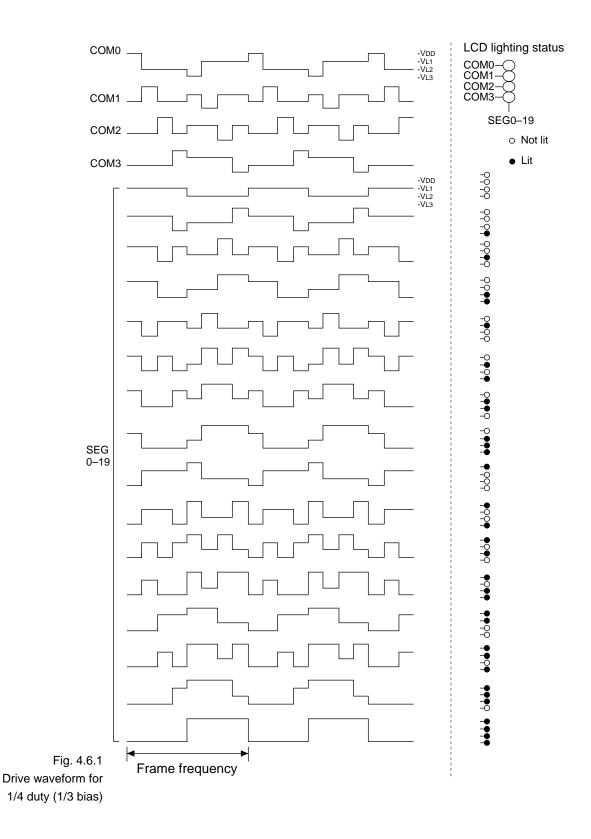

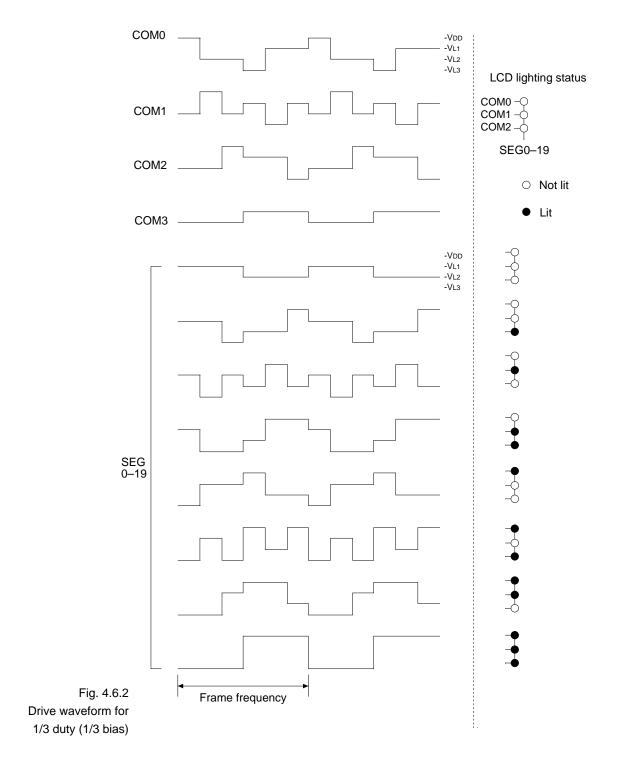

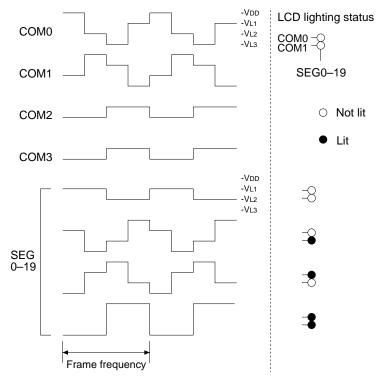

The driving method is 1/4 duty (or 1/3, 1/2 duty by mask option) dynamic drive, adopting the four types of potential (1/3 bias), VDD, VL1, VL2 and VL3. Moreover, the 1/2 bias dynamic drive that uses three types of potential, VDD, VL1 = VL2 and VL3, can be selected by setting the mask option (drive duty can also be selected from 1/4, 1/3 or 1/2). 1/2 bias drive is effective when the LCD system regulated voltage circuit is not used. The VL1 terminal and the VL2 terminal should be connected outside of the IC.

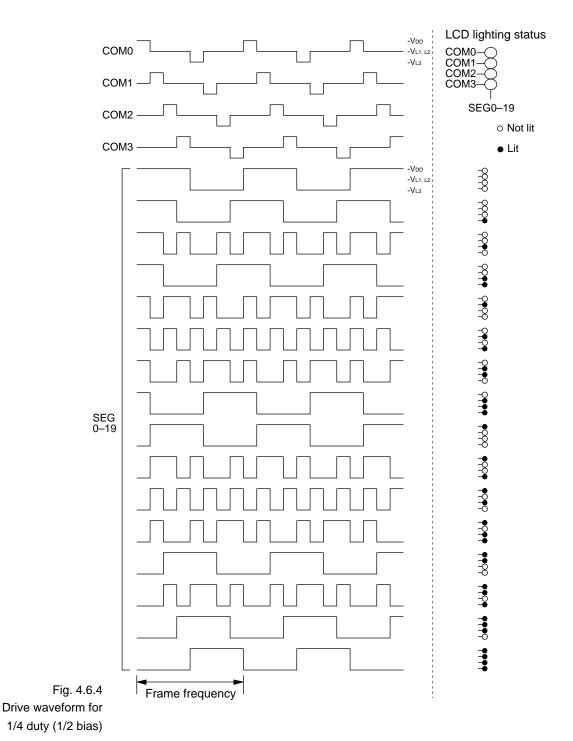

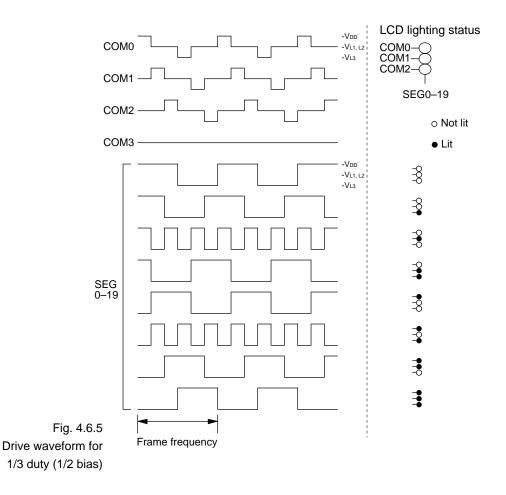

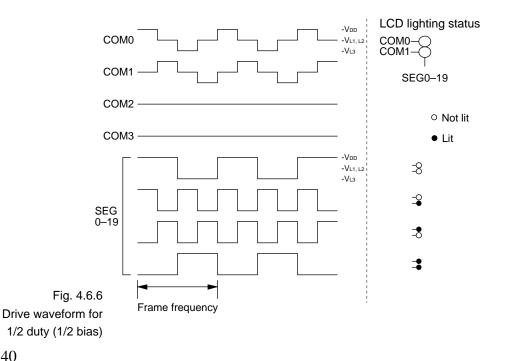

The frame frequency is 32 Hz for 1/4 duty and 1/2 duty, and 42.7 Hz for 1/3 duty (in the case of fosc = 32.768 kHz). Figure 4.6.1 shows the drive waveform for 1/4 duty (1/3 bias), Figure 4.6.2 shows the drive waveform for 1/3 duty (1/3 bias), Figure 4.6.3 shows the drive waveform for 1/2 duty (1/3 bias), Figure 4.6.4 shows the drive waveform for 1/4 duty (1/2 bias), Figure 4.6.5 shows the drive waveform for 1/3 duty (1/2 bias) and Figure 4.6.6 shows the drive waveform for 1/2 duty (1/2 bias).

Note fosc indicates the oscillation frequency of the oscillation circuit.

Fig. 4.6.3 Drive waveform for 1/2 duty (1/3 bias)

# Cadence adjustment of oscillation frequency

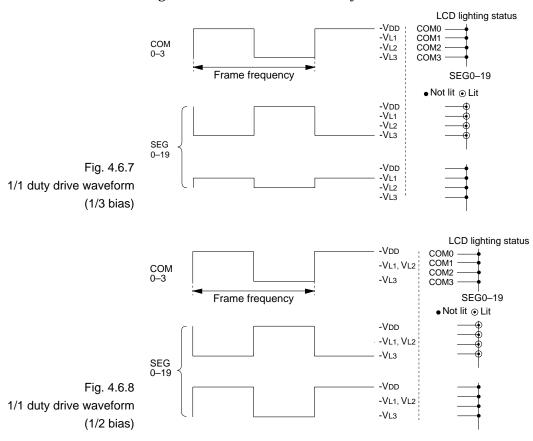

In the E0C6001 Series, the LCD drive duty can be set to 1/1 duty by software. This function enables easy adjustment (cadence adjustment) of the oscillation frequency of the OSC circuit.

The procedure to set to 1/1 duty drive is as follows:

- ① Write 1 to the CSDC register at address 0FBH D3.

- ② Write the same value to all registers corresponding to COMs 0 through 3 of the display memory.

The frame frequency is 32 Hz (fosc1/1,024, when fosc1 = 32.768 kHz).

Note - Even when I/3 or 1/2 duty is selected by the mask option, the display data corresponding to all COM are valid during 1/1 duty driving. Hence, for 1/1 duty drive, set the same value for all

display memory corresponding to COMs 0 through 3.

- For cadence adjustment, set the display data corresponding to COMs 0 through 3, so that all the LCD segments go on.

Figure 4.6.7 shows the 1/1 duty drive waveform (1/3 bias). Figure 4.6.8 shows the 1/1 duty drive waveform (1/2 bias).

# Mask option (segment allocation)

#### (1) Segment allocation

As shown in Figure 4.l.1, the E0C6001 Series display data is decided by the display data written to the display memory (write-only) at address 090H-0AFH.

The address and bits of the display memory can be made to correspond to the segment pins (SEG0–SEG19) in any combination through mask option. This simplifies design by increasing the degree of freedom with which the liquid crystal panel can be designed.

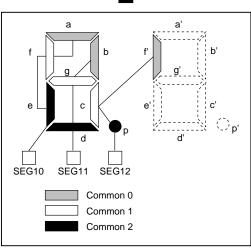

Figure 4.6.9 shows an example of the relationship between the LCD segments (on the panel) and the display memory in the case of 1/3 duty.

| Address | Data |    |    |    |  |  |  |  |

|---------|------|----|----|----|--|--|--|--|

| Address | D3   | D2 | D1 | D0 |  |  |  |  |

| 09AH    | d    | с  | b  | a  |  |  |  |  |

| 09BH    | p    | g  | f  | e  |  |  |  |  |

| 09CH    | d'   | c' | b' | a' |  |  |  |  |

| 09DH    | p'   | g' | f' | e' |  |  |  |  |

Common 0 Common 1 Common 2 SEG10 9B, D1 9B, D0 9A, D0 (a) (f) (e) SEG11 9B, D2 9A, D1 9A, D3 (b) (g) (d) 9A, D2 SEG12 9D, D1 9B, D3 (f') (c) (p)

Display data memory allocation

Pin address allocation

Fig. 4.6.9 Segment allocation

#### (2) Drive duty

According to the mask option, either 1/4, 1/3 or 1/2 duty can be selected as the LCD drive duty.

Table 4.6.1 shows the differences in the number of segments according to the selected duty.

Table 4.6.1

Differences according to selected duty

| Duty | Pins Used in Common | Maximum Number   | Frame Frequency      |

|------|---------------------|------------------|----------------------|

|      | in Common           | of Segments      | (when fosc = 32 kHz) |

| 1/4  | COM0-3              | $80~(20\times4)$ | 32 Hz                |

| 1/3  | COM0-2              | 60 (20 × 3)      | 42.7 Hz              |

| 1/2  | COM0-1              | 40 (20 × 2)      | 32 Hz                |

#### (3) Output specification

- ① The segment pins (SEG0-SEG19) are selected by mask option in pairs for either segment signal output or DC output (VDD and VSS binary output). When DC output is selected, the data corresponding to COM0 of each segment pin is output.

- When DC output is selected, either complementary output or Pch open drain output can be selected for each pin by mask option.

Note

The pin pairs are the combination of SEG (2\*n) and SEG (2\*n + 1) (where n is an integer from 0 to 12).

#### (4) Drive bias

For the drive bias of the E0C6001 or the E0C60L01, either 1/3 bias or 1/2 bias can be selected by the mask option.

# Control of LCD driver

Table 4.6.2 shows the control bits of the LCD driver and their addresses. Figure 4.6.10 shows the display memory map.

Table 4.6.2 Control bits of LCD driver

| Address |      | Reg | ister |    |      |    |        |         | Comment          |

|---------|------|-----|-------|----|------|----|--------|---------|------------------|

| Address | D3   | D2  | D1    | D0 | Name | SR | 1      | 0       | Comment          |

|         | CSDC | 0   | 0     | 0  | CSDC | 0  | Static | Dynamic | LCD drive switch |

| 0FBH    | R/W  |     | R     |    | 0    |    |        |         |                  |

| UFBH    |      |     |       |    | 0    |    |        |         |                  |

|         |      |     |       |    | 0    |    |        |         |                  |

Fig. 4.6.10 Display memory map

| Address | 0 | 1                                                | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | А | В | С | D | E | F |

|---------|---|--------------------------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 090     |   | Display memory (Write only)                      |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

| 0A0     |   | Display memory (Write only)<br>32 words x 4 bits |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

CSDC LCD drive switch (0FBH D3)

The LCD drive format can be selected with this switch.

When 1 is written: Static drive When 0 is written: Dynamic drive

Reading: Valid

After an initial reset, dynamic drive (CSDC = 0) is selected.

Display memory (090H–0AFH)

The LCD segments are turned on or off according to this data.

When 1 is written: On

When 0 is written: Off

Reading: Invalid

By writing data into the display memory allocated to the LCD segment (on the panel), the segment can be turned on or off. After an initial reset, the contents of the display memory are undefined.

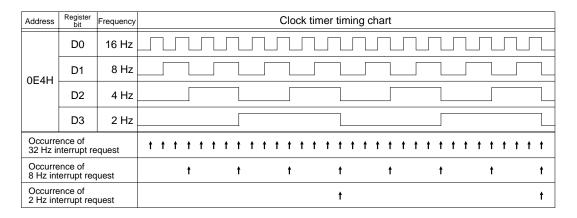

# 4.7 Clock Timer

# Configuration of clock timer

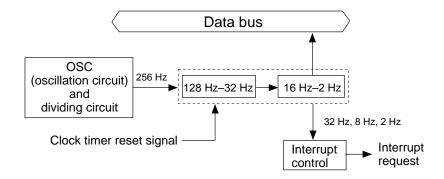

The E0C6001 Series have a built-in clock timer driven by the source oscillator. The clock timer is configured as a seven-bit binary counter that serves as a frequency divider taking a 256 Hz source clock from the dividing circuit. The four high-order bits (16 Hz–2 Hz) can be read by the software.

Figure 4.7.1 is the block diagram of the clock timer.

Fig. 4.7.1 Block diagram of clock timer

Normally, this clock timer is used for all kinds of timing purpose, such as clocks.

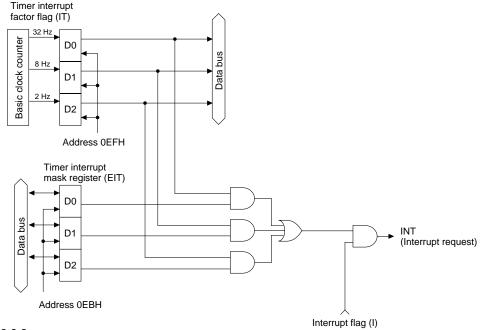

## Interrupt function

The clock timer can interrupt on the falling edge of the 32 Hz, 8 Hz, and 2 Hz signals. The software can mask any of these interrupt signals.

Figure 4.7.2 is the timing chart of the clock timer.

| Address                                 | Register<br>bits          | Frequency | Clock timer timing chart |

|-----------------------------------------|---------------------------|-----------|--------------------------|

|                                         | D0                        | 16 Hz     |                          |

| 0E4H                                    | D1                        | 8 Hz      |                          |

| 00411                                   | D2                        | 4 Hz      |                          |

|                                         | D3                        | 2 Hz      |                          |

|                                         | rrence of<br>interrupt    | request   |                          |

| Occurrence of<br>8 Hz interrupt request |                           | equest    | t t t t t t t            |

|                                         | rrence of<br>interrupt re | equest    | t t                      |

Fig. 4.7.2 Timing chart of the clock timer

As shown in Figure 4.7.2, an interrupt is generated on the falling edge of the 32 Hz, 8 Hz, and 2 Hz frequencies. When this happens, the corresponding interrupt event flag (IT32, IT8, IT2) is set to 1. Masking the separate interrupts can be done with the interrupt mask register (EIT32, EIT8, EIT2). However, regardless of the interrupt mask register setting, the interrupt event flags will be set to 1 on the falling edge of their corresponding signal (e.g. the falling edge of the 2 Hz signal sets the 2 Hz interrupt factor flag to 1).

Note Write to the interrupt mask register (EIT32, EIT8, EIT2) and read the interrupt factor flags (IT32, IT8, IT2) only in the DI status (interrupt flag = 0). Otherwise, it causes malfunction.

# Control of clock timer

Table 4.7.1 shows the clock timer control bits and their addresses.

Table 4.7.1 Control bits of clock timer

| Address |       | Regi  | ister |       |        |      |                                             |      | Comment                                    |

|---------|-------|-------|-------|-------|--------|------|---------------------------------------------|------|--------------------------------------------|

| Address | D3    | D2    | D1    | D0    | Name   | SR   | 1                                           | 0    | Comment                                    |

|         | TM3   | TM2   | TM1   | TM0   | TM3    | -    | High                                        | Low  | Timer data (clock timer 2 Hz)              |

| 0E4H    |       | F     | ₹     |       | TM2    | -    | High                                        | Low  | Timer data (clock timer 4 Hz)              |

| UE4H    |       |       | TM1   | -     | High   | Low  | Timer data (clock timer 8 Hz)               |      |                                            |

|         |       |       |       |       | TM0    | -    | High                                        | Low  | Timer data (clock timer 16 Hz)             |

|         | 0     | EIT2  | EIT8  | EIT32 | 0      |      |                                             |      |                                            |

| 0EBH    | R     |       | R/W   |       | EIT2   | 0    | Enable                                      | Mask | Interrupt mask register (clock timer 2 Hz) |

| OLBIT   |       |       |       |       | EIT8   | 0    | Enable                                      | Mask | Interrupt mask register (clock timer 8 Hz) |

|         |       |       | EIT32 | 0     | Enable | Mask | Interrupt mask register (clock timer 32 Hz) |      |                                            |

|         | 0     | IT2   | IT8   | IT32  | 0      |      |                                             |      |                                            |

| 0EFH    |       | F     | ₹     |       | IT2    | 0    | Yes                                         | No   | Interrupt factor flag (clock timer 2 Hz)   |

| OLITI   |       |       |       |       | IT8    | 0    | Yes                                         | No   | Interrupt factor flag (clock timer 8 Hz)   |

|         |       |       |       |       | IT32   | 0    | Yes                                         | No   | Interrupt factor flag (clock timer 32 Hz)  |

|         | 0     | TMRST | 0     | 0     | 0      |      |                                             |      |                                            |

| 0F9H    | R W R |       | TMRST | Reset | Reset  | -    | Clock timer reset                           |      |                                            |

| 01-911  |       |       |       |       | 0      |      |                                             |      |                                            |

|         |       |       |       |       | 0      |      |                                             |      |                                            |

TM0-TM3 Timer data (0E4H)

The l6 Hz to 2 Hz timer data of the clock timer can be read from this register. These four bits are read-only, and write operations are invalid.

After an initial reset, the timer data is initialized to 0H.

EIT32, EIT8, EIT2 Interrupt mask registers (0EBH D0–D2)

These registers are used to mask the clock timer interrupt.

When 1 is written: Enabled When 0 is written: Masked Reading: Valid

The interrupt mask register bits (EIT32, EIT8, EIT2) mask the corresponding interrupt frequencies (32 Hz, 8 Hz, 2 Hz). After an initial reset, these registers are all set to 0.

IT32, IT8, IT2 Interrupt factor flags (0EFH D0–D2)

These flags indicate the status of the clock timer interrupt.

When 1 is read: Interrupt has occurred When 0 is read: Interrupt has not occurred

Writing: Invalid

The interrupt factor flags (IT32, IT8, IT2) correspond to the clock timer interrupts (32 Hz, 8 Hz, 2 Hz). The software can determine from these flags whether there is a clock timer interrupt. However, even if the interrupt is masked, the flags are set to 1 on the falling edge of the signal. These flags can be reset when the register is read by the software. Reading of interrupt factor flags is available at EI, but be careful in the following cases.

If the interrupt mask register value corresponding to the interrupt factor flags to be read is set to 1, an interrupt request will be generated by the interrupt factor flags set timing, or an interrupt request will not be generated. Be very careful when interrupt factor flags are in the same address.

After an initial reset, these flags are set to 0.

TMRST Clock timer reset (0F9H D2)

This bit resets the clock timer.

When 1 is written: Clock timer reset

When 0 is written: No operation

Reading: Always 0

The clock timer is reset by writing 1 to TMRST. The clock timer starts immediately after this. No operation results when 0 is written to TMRST.

This bit is write-only, and so is always 0 when read.

# 4.8 Heavy Load Protection Function

# Operation of heavy load protection function

The E0C6001 Series have a heavy load protection function for when the battery load becomes heavy and the supply voltage drops, such as when an external buzzer sounds or an external lamp lights. This function works in the heavy load protection mode.

The normal mode changes to the heavy load protection mode in the following case:

When the software changes the mode to the heavy load protection mode (HLMOD = 1)

In the heavy load protection mode, the internally regulated voltage is switched to the high-stability mode from the low current consumption mode. Consequently, more current is consumed in the heavy load protection mode than in the normal mode. Unless necessary, do not select the heavy load protection mode with the software.

# Control of heavy load protection function

Table 4.8.1 shows the control bits and their addresses for the heavy load protection function.

Table 4.8.1 Control bits for heavy load protection function

| Address |       | Reg | ister |    |       |    |               |                | . Comment                           |

|---------|-------|-----|-------|----|-------|----|---------------|----------------|-------------------------------------|

| Address | D3    | D2  | D1    | D0 | Name  | SR | 1             | 0              | Comment                             |

|         | HLMOD | 0   | 0     | 0  | HLMOD | 0  | Heavy<br>load | Normal<br>load | Heavy load protection mode register |

| 0FAH    | R/W   |     | R     |    | 0     |    |               |                |                                     |

| UFAIT   |       |     |       |    | 0     |    |               |                |                                     |

|         |       |     |       |    | 0     |    |               |                |                                     |

HLMOD Heavy load protection mode on/off (0FAH D3)

When 1 is written: Heavy load protection mode on When 0 is written: Heavy load protection mode off

Reading: Valid

When HLMOD is set to 1, the IC enters the heavy load protection mode.

In the heavy load protection mode, the consumed current becomes larger. Unless necessary, do not select the heavy load protection mode with the software.

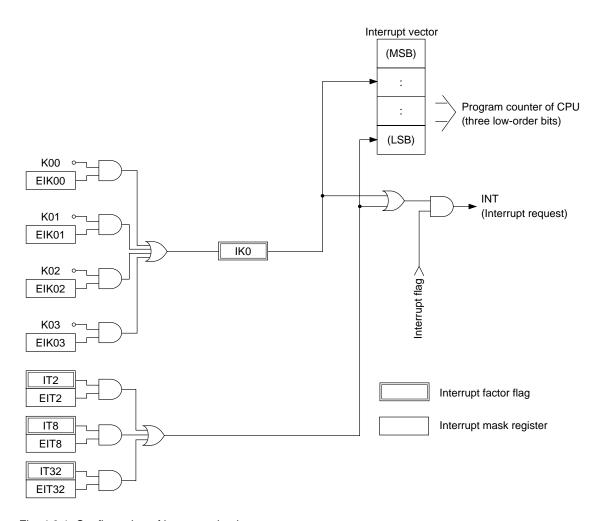

# 4.9 Interrupt and HALT

The E0C6001 Series provide the following interrupt settings, each of which is maskable.

External interrupt: Input interrupt (one)

Internal interrupt: Timer interrupt (one)

To enable interrupts, the interrupt flag must be set to 1 (EI) and the necessary related interrupt mask registers must be set to 1 (enable). When an interrupt occurs, the interrupt flag is automatically reset to 0 (DI) and interrupts after that are inhibited.

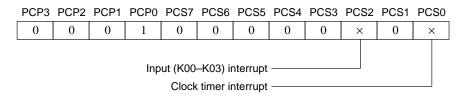

When a HALT instruction is input, the CPU operating clock stops and the CPU enters the halt state. The CPU is reactivated from the halt state when an interrupt request occurs. Figure 4.9.1 shows the configuration of the interrupt circuit.

Fig. 4.9.1 Configuration of interrupt circuit

## Interrupt factors

Table 4.9.1 shows the factors that generate interrupt requests.

The interrupt factor flags are set to 1 depending on the corresponding interrupt factors.

The CPU is interrupted when the following two conditions occur and an interrupt factor flag is set to 1.

- The corresponding mask register is 1 (enabled)

- The interrupt flag is 1 (EI)

The interrupt factor flag is a read-only register, but can be reset to 0 when the register data is read.

After an initial reset, the interrupt factor flags are reset to 0.

Note Reading of interrupt factor flags is available at EI, but be careful in the following cases.

If the interrupt mask register value corresponding to the interrupt factor flags to be read is set to 1, an interrupt request will be generated by the interrupt factor flags set timing, or an interrupt request will not be generated. Be very careful when interrupt factor flags are in the same address.

Table 4.9.1 Interrupt factors

| Interrupt Factor                 | Interrupt Factor Flag |           |  |  |

|----------------------------------|-----------------------|-----------|--|--|

| Colck timer 2 Hz falling edge    | IT2                   | (0EFH D2) |  |  |

| Colck timer 8 Hz falling edge    | IT8                   | (0EFH D1) |  |  |