# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER **E0C62M2 TECHNICAL MANUAL**

**E0C62M2 Technical Hardware**

# **CONTENTS**

| CHAPTER 1 | Ov        | ERVIEW                                               | 1      |

|-----------|-----------|------------------------------------------------------|--------|

|           | 1.1       | Features                                             | 1      |

|           | 1.2       | Block Diagram                                        | 2      |

|           | 1.3       | Pin Layout Diagram                                   |        |

|           | 1.4       | Pin Description                                      |        |

| CHAPTER 2 | Pos       | WER SUPPLY AND INITIAL RESET                         | •      |

| CHAITER 2 |           |                                                      |        |

|           | 2.1       | Power Supply                                         | 7<br>7 |

|           | 2.2       | Initial Reset                                        | 8      |

|           |           | 2.2.1 Reset terminal (RESET)                         | 8      |

|           |           | 2.2.2 Watchdog timer                                 |        |

|           |           | 2.2.3 Internal register at initial resetting         |        |

|           | 2.3       | Test Terminal (TEST)                                 | 9      |

| CHAPTER 3 | <b>CP</b> | U, ROM, RAM                                          | 1      |

|           | 3.1       | <i>CPU</i>                                           | 10     |

|           | 3.2       | ROM                                                  | 10     |

|           | 3.3       | <i>RAM</i>                                           | 10     |

| CHAPTER 4 | PEF       | RIPHERAL CIRCUITS AND OPERATION                      | 1      |

|           | 4.1       | Memory Map                                           |        |

|           | 4.2       | Resetting Watchdog Timer                             |        |

|           |           | 4.2.1 Configuration of watchdog timer                | 16     |

|           |           | 4.2.2 Control of watchdog timer                      |        |

|           |           | 4.2.3 Programming note                               |        |

|           | 4.3       | Oscillation Circuit                                  |        |

|           |           | 4.3.1 Configuration of oscillation circuit           |        |

|           |           | 4.3.3 Clock frequency and instruction execution time |        |

|           | 4.4       | Input Ports (K00–K03, K10–K13)                       |        |

|           |           | 4.4.1 Configuration of input ports                   |        |

|           |           | 4.4.2 Interrupt function                             |        |

|           |           | 4.4.3 Mask option                                    |        |

|           |           | 4.4.4 Control of input ports                         |        |

|           | 4.5       | Output Ports (R00–R03)                               |        |

|           | 4.5       | 4.5.1 Configuration of output ports                  |        |

|           |           | 4.5.2 Mask option                                    |        |

|           |           | 4.5.3 Control of output ports                        |        |

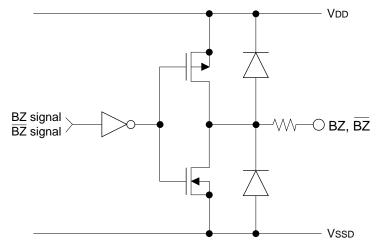

|           | 4.6       | Buzzer Output Ports (BZ, $\overline{BZ}$ )           | 25     |

|           |           | 4.6.1 Configuration of buzzer output ports           |        |

|           |           | 4.6.2 Buzzer output                                  |        |

|           |           | 4.6.3 Control of buzzer output                       | 27     |

| 4.7  | I/O Ports (P00–P03)                                                      | 28        |

|------|--------------------------------------------------------------------------|-----------|

|      | 4.7.1 Configuration of I/O ports                                         |           |

|      | 4.7.2 I/O control registers and input/output mode                        |           |

|      | 4.7.3 Pull down during input mode                                        |           |

|      | 4.7.4 Mask option                                                        |           |

|      | 4.7.5 Control of I/O ports                                               |           |

|      | 4.7.6 Programming note                                                   |           |

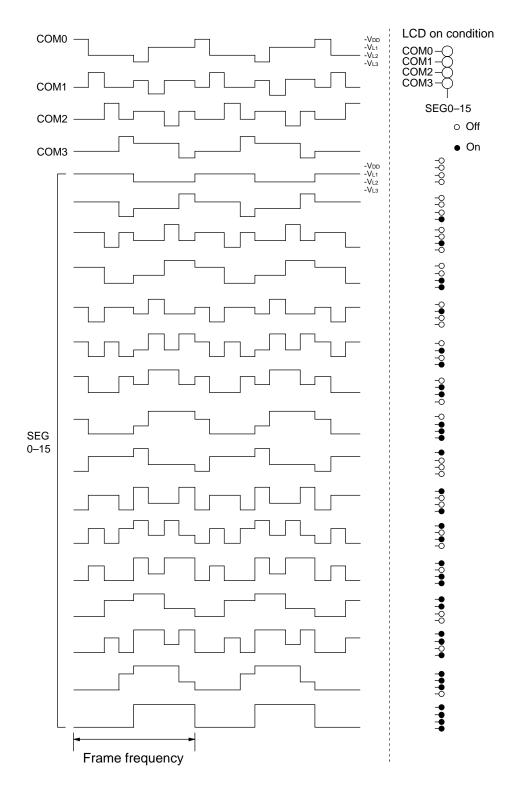

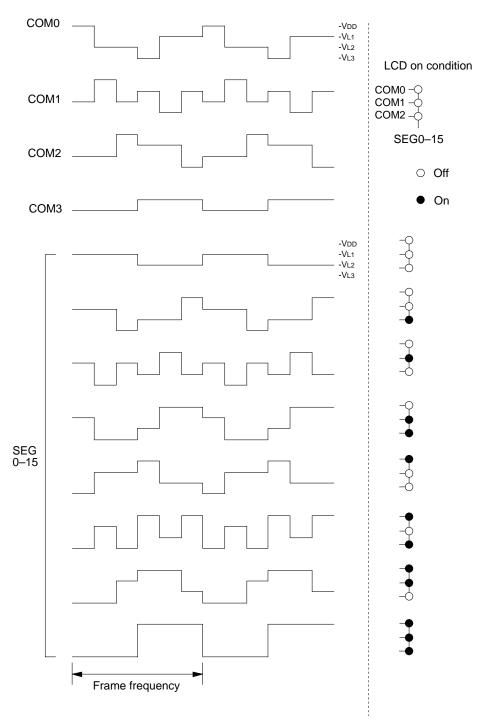

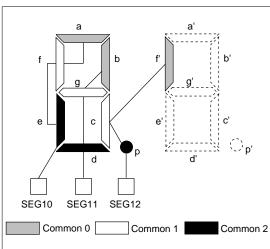

| 4.8  | LCD Driver (COM0–COM3, SEG0–SEG15)                                       | 31        |

|      | 4.8.1 Configuration of LCD driver                                        | -         |

|      | 4.8.2 LCD display control and duty switching                             |           |

|      | 4.8.3 Mask option (segment allocation)                                   |           |

|      | 4.8.4 Control of LCD driver                                              |           |

|      | 4.8.5 Programming notes                                                  |           |

| 4.9  |                                                                          | 20        |

| 4.9  | Clock Timer                                                              | 30        |

|      | 4.9.1 Configuration of clock timer                                       |           |

|      | 4.9.2 Data reading and hold function                                     |           |

|      | 4.9.3 Interrupt function                                                 |           |

|      | 4.9.4 Control of clock timer                                             |           |

|      | 4.9.5 Programming notes                                                  |           |

| 4.10 | J                                                                        | 42        |

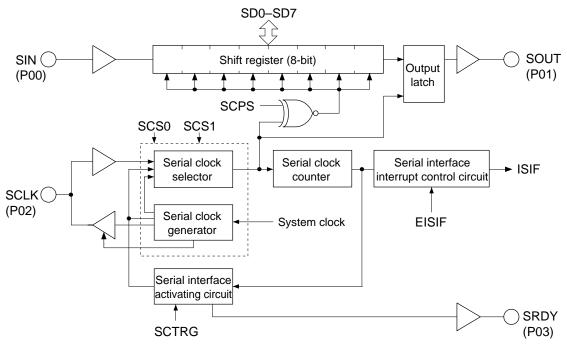

|      | 4.10.1 Configuration of serial interface                                 |           |

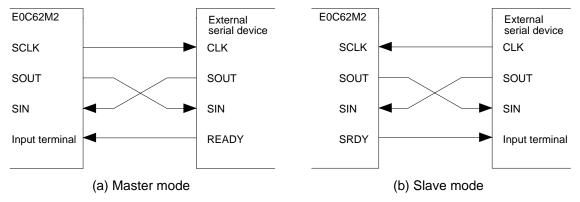

|      | 4.10.2 Master mode and slave mode of serial interface                    |           |

|      | 4.10.3 Data input/output and interrupt function                          |           |

|      | 4.10.4 Mask option                                                       |           |

|      | 4.10.5 Control of serial interface                                       |           |

|      | <i>4.10.6 Programming notes</i>                                          |           |

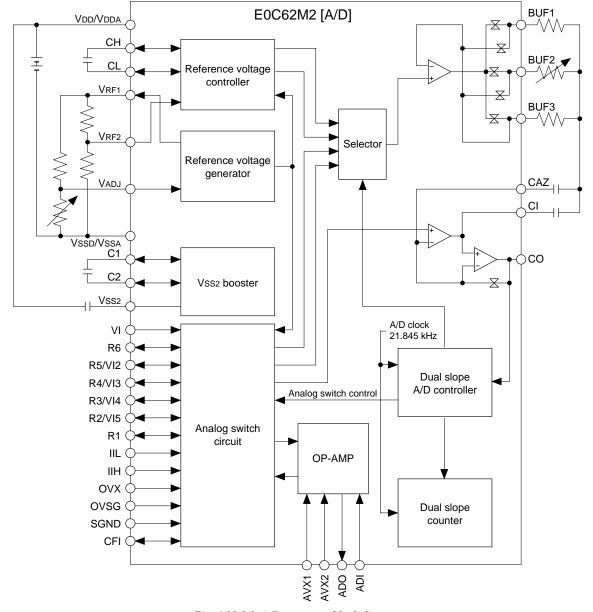

| 4.11 | A/D Converter                                                            | 49        |

|      | 4.11.1 Configuration of A/D converter                                    |           |

|      | 4.11.2 Power supply and reference voltage generator for A/D converter 50 |           |

|      | 4.11.3 Clock for A/D converter                                           |           |

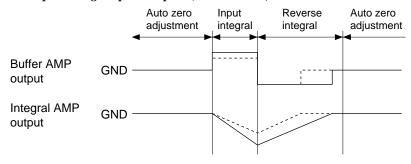

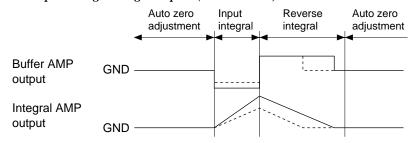

|      | 4.11.4 A/D converter control circuit (Dual slope A/D controller)         |           |

|      | 4.11.5 Operation of dual slope type A/D converter                        |           |

|      | 4.11.6 A/D conversion and interrupt                                      |           |

|      | 4.11.7 Control of A/D converter                                          |           |

|      | 4.11.8 Programming notes                                                 |           |

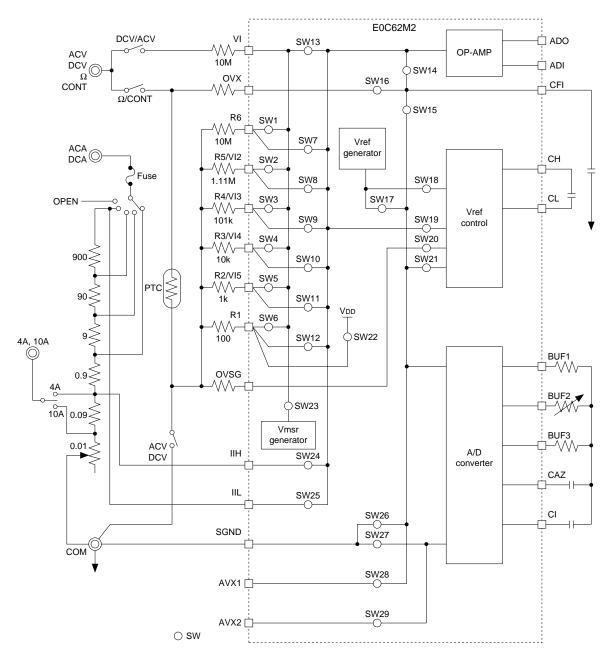

| 4 12 | Measurement Circuit and Measurement Procedure                            | 60        |

| 7.12 | 4.12.1 Sort of measurement                                               | 00        |

|      | 4.12.2 General AMP                                                       |           |

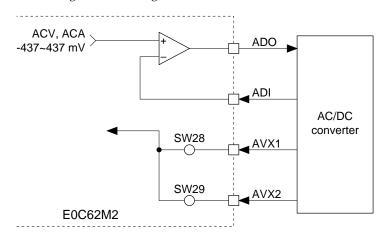

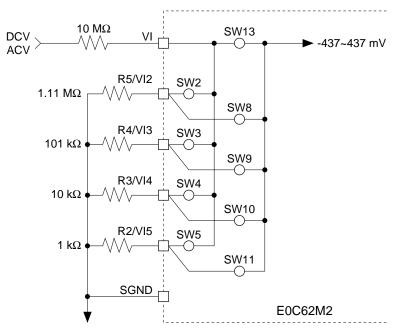

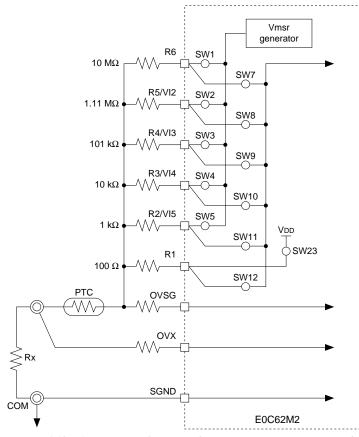

|      | 4.12.3 Voltage measurement 62                                            |           |

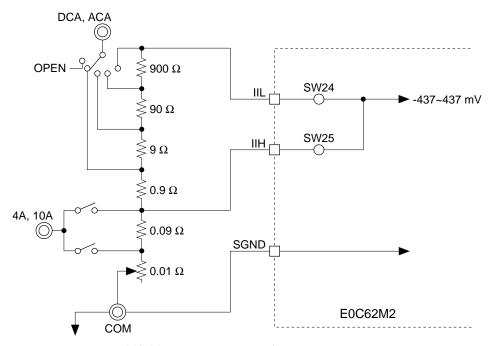

|      | 4.12.4 Current measurement 63                                            |           |

|      | 4.12.5 Resistance measurement 64                                         |           |

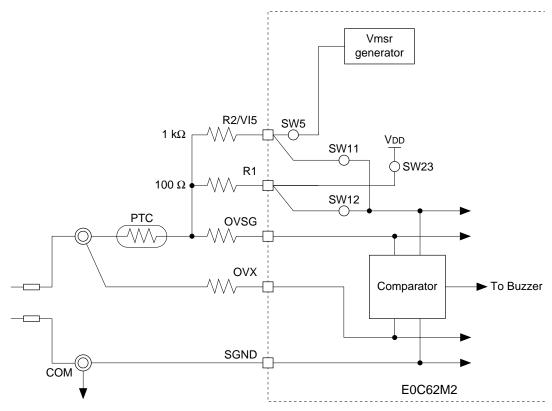

|      | 4.12.6 Continuity check                                                  |           |

|      | 4.12.7 ADPT (adapter)                                                    |           |

|      | 4.12.8 Control method                                                    |           |

|      | 4.12.9 <i>Programming notes</i>                                          |           |

| 4.12 |                                                                          | <b>60</b> |

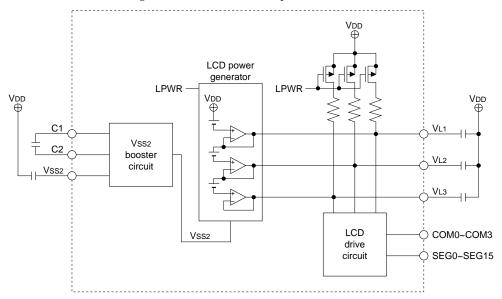

| 4.13 | VSS2 Booster                                                             | 69        |

|      | 4.13.1 Configuration of Vss2 booster                                     |           |

|      | 4.13.2 Control of Vss2 booster                                           |           |

|      | 4.13.3 Programming notes                                                 |           |

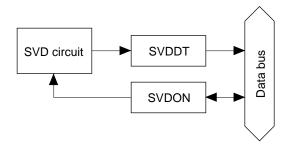

| 4.14 | SVD (Supply Voltage Detection) Circuit                                   | 71        |

|      | 4.14.1 Configuration of SVD circuit                                      |           |

|      | 4.14.2 Operation of SVD circuit                                          |           |

|      | 4.14.3 Control of SVD circuit                                            |           |

|      | 4.14.4 Programming note                                                  |           |

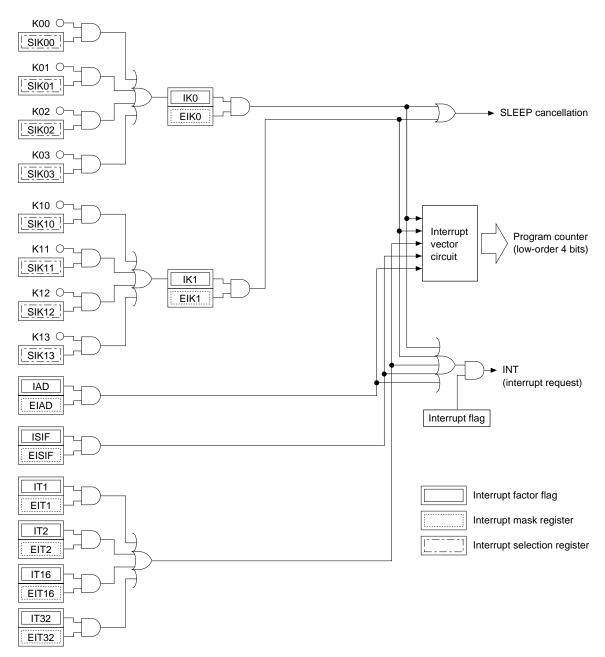

|           | 4.15         | 5 Interrupt and HALT/SLEEP                           | 73  |

|-----------|--------------|------------------------------------------------------|-----|

|           |              | 4.15.1 Interrupt factor                              |     |

|           |              | 4.15.2 Interrupt mask                                | 75  |

|           |              | 4.15.3 Interrupt vector                              |     |

|           |              | 4.15.4 Control of interrupt                          |     |

|           |              | 4.15.5 Programming notes                             | 77  |

| CHAPTER 5 | SUM          | MMARY OF NOTES                                       | 78  |

|           | 5.1          | Notes for Low Current Consumption                    |     |

|           | 5.2          | Summary of Notes by Function                         | 79  |

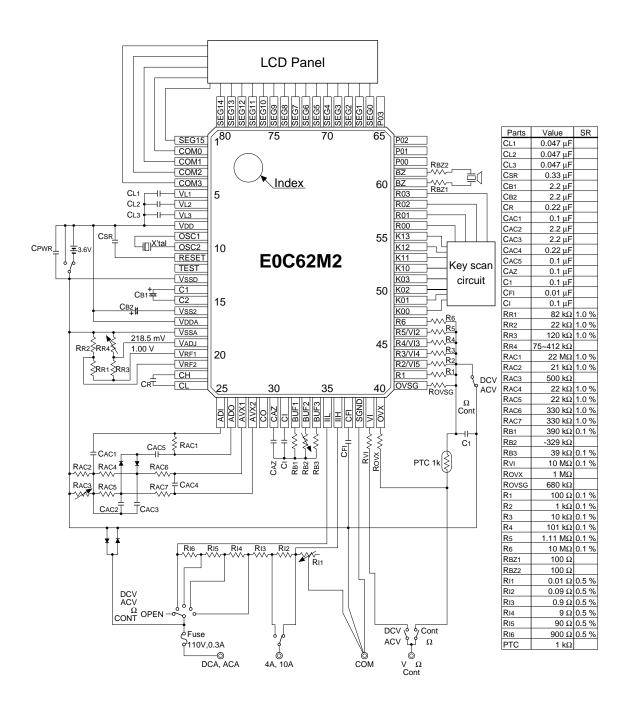

| CHAPTER 6 | DIA          | GRAM OF BASIC EXTERNAL CONNECTIONS                   | 82  |

| CHAPTER 7 | ELI          | ECTRICAL CHARACTERISTICS                             | 83  |

|           | 7.1          | Absolute Maximum Rating                              |     |

|           | 7.2          | Recommended Operating Conditions                     | 83  |

|           | 7.3          | DC Characteristics                                   | 84  |

|           | 7.4          | Analog Characteristics and Current Consumption       | 85  |

|           | 7.5          | Oscillation Characteristics                          | 86  |

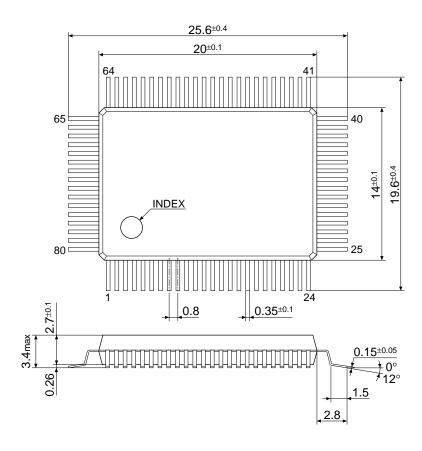

| CHAPTER 8 | PAG          | CKAGE                                                | 87  |

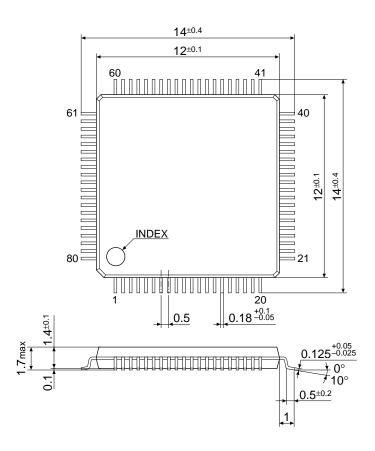

|           | 8.1          | Plastic Package                                      | 87  |

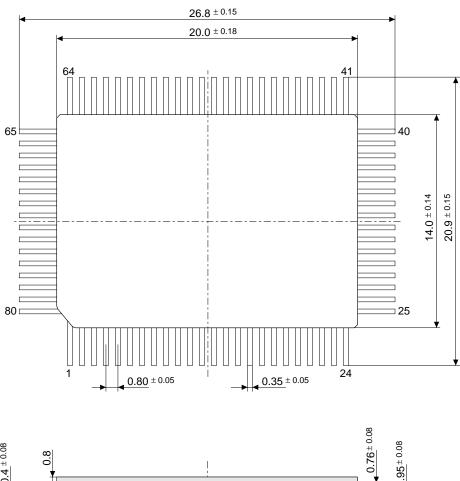

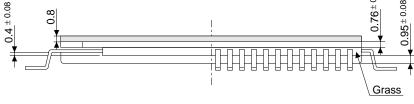

|           | 8.2          | Ceramic Package for Test Samples                     | 89  |

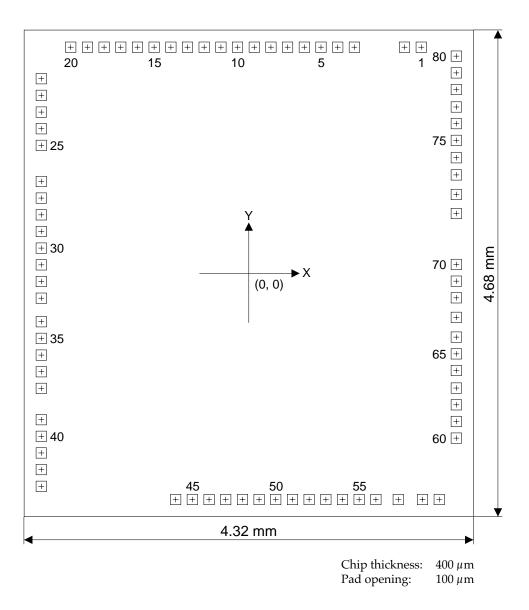

| CHAPTER 9 | PAI          | D LAYOUT                                             | 90  |

|           | 9.1          | Diagram of Pad Layout                                | 90  |

|           | 9.2          | Pad Coordinates                                      | 91  |

| REFERENCE | E <b>D</b> A | TA                                                   | 92  |

|           | 1.           | Electrical Specification                             | 92  |

|           |              | 1.1 DC Voltmeter                                     |     |

|           |              | 1.2 AC Voltmeter                                     |     |

|           |              | 1.3 DC Ammeter                                       |     |

|           |              | 1.4 AC Ammeter                                       |     |

|           |              | 1.5 Resistance                                       |     |

|           | 2            | · · · · · · · · · · · · · · · · · · ·                |     |

|           | 2.           | Notes                                                |     |

|           |              | 2.1 40 $M\Omega$ range during resistance measurement |     |

|           |              | 2.2 Frequency characteristic of AC voltage           |     |

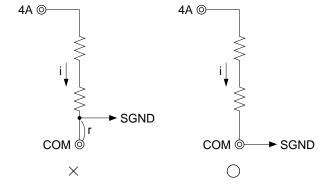

|           |              | 2.4 Connection of SGND                               |     |

|           |              | Co Co Oj DOI 1D                                      | / / |

# CHAPTER 1 OVERVIEW

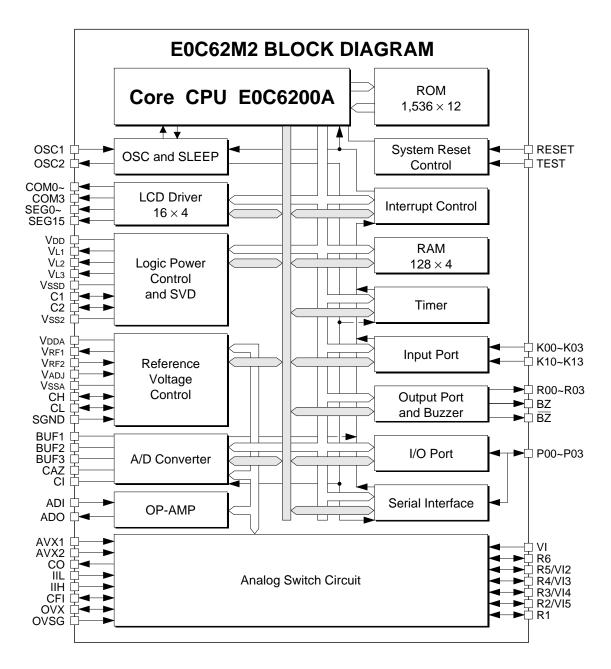

The E0C62M2 is a CMOS 4-bit single-chip microcomputer made up of the 4-bit core CPU E0C6200A, ROM (1,536 words, 12 bits to a word), RAM (128 words, 4 bits to a word), dual slope type A/D converter, attenuator circuit for various measurement modes, LCD driver, serial interface, and other circuits. It is especially suitable for measurement and LCD display systems such as a digital multimeter.

#### 1.1 Features

| erature range: 20°C to 40°C) ernal rectifier circuit an be displayed) |

|-----------------------------------------------------------------------|

| ask option)                                                           |

|                                                                       |

|                                                                       |

|                                                                       |

| itched to general I/O port                                            |

| g software)<br>.2, VL3)                                               |

|                                                                       |

|                                                                       |

|                                                                       |

|                                                                       |

|                                                                       |

|                                                                       |

| surement)                                                             |

| or chip                                                               |

|                                                                       |

# 1.2 Block Diagram

Fig. 1.2.1 Block diagram

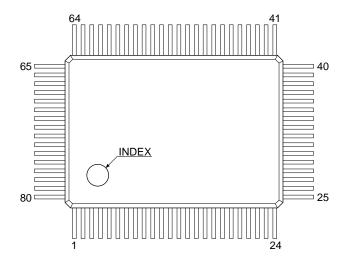

# 1.3 Pin Layout Diagram

QFP5-80pin

| Pin No. | Pin name                 |

|---------|----------|---------|----------|---------|----------|---------|--------------------------|

| 1       | SEG15    | 21      | VrF1     | 41      | OVSG     | 61      | $\overline{\mathrm{BZ}}$ |

| 2       | COM0     | 22      | VRF2     | 42      | R1       | 62      | P00/SIN                  |

| 3       | COM1     | 23      | СН       | 43      | R2/VI5   | 63      | P01/SOUT                 |

| 4       | COM2     | 24      | CL       | 44      | R3/VI4   | 64      | P02/SCLK                 |

| 5       | COM3     | 25      | ADI      | 45      | R4/VI3   | 65      | P03/SRDY                 |

| 6       | VL1      | 26      | ADO      | 46      | R5/VI2   | 66      | SEG0                     |

| 7       | VL2      | 27      | AVX1     | 47      | R6       | 67      | SEG1                     |

| 8       | VL3      | 28      | AVX2     | 48      | K00      | 68      | SEG2                     |

| 9       | Vdd      | 29      | CO       | 49      | K01      | 69      | SEG3                     |

| 10      | OSC1     | 30      | CAZ      | 50      | K02      | 70      | SEG4                     |

| 11      | OSC2     | 31      | CI       | 51      | K03      | 71      | SEG5                     |

| 12      | RESET    | 32      | BUF1     | 52      | K10      | 72      | SEG6                     |

| 13      | TEST     | 33      | BUF2     | 53      | K11      | 73      | SEG7                     |

| 14      | Vssd     | 34      | BUF3     | 54      | K12      | 74      | SEG8                     |

| 15      | C1       | 35      | IIL      | 55      | K13      | 75      | SEG9                     |

| 16      | C2       | 36      | IIH      | 56      | R00      | 76      | SEG10                    |

| 17      | VSS2     | 37      | CFI      | 57      | R01      | 77      | SEG11                    |

| 18      | Vdda     | 38      | SGND     | 58      | R02      | 78      | SEG12                    |

| 19      | Vssa     | 39      | VI       | 59      | R03      | 79      | SEG13                    |

| 20      | VADJ     | 40      | OVX      | 60      | BZ       | 80      | SEG14                    |

Fig. 1.3.1 Pin layout diagram (QFP5-80pin)

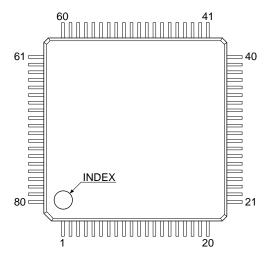

#### QFP14-80pin

| Pin No. | Pin name | Pin No. | Pin name | Pin No. | Pin name                 | Pin No. | Pin name |

|---------|----------|---------|----------|---------|--------------------------|---------|----------|

| 1       | COM2     | 21      | CL       | 41      | R3/VI4                   | 61      | P02/SCLK |

| 2       | COM3     | 22      | ADI      | 42      | R4/VI3                   | 62      | P03/SRDY |

| 3       | VL1      | 23      | ADO      | 43      | R5/VI2                   | 63      | SEG0     |

| 4       | VL2      | 24      | AVX1     | 44      | R6                       | 64      | SEG1     |

| 5       | VL3      | 25      | AVX2     | 45      | K00                      | 65      | SEG2     |

| 6       | Vdd      | 26      | CO       | 46      | K01                      | 66      | SEG3     |

| 7       | OSC1     | 27      | CAZ      | 47      | K02                      | 67      | SEG4     |

| 8       | OSC2     | 28      | CI       | 48      | K03                      | 68      | SEG5     |

| 9       | RESET    | 29      | BUF1     | 49      | K10                      | 69      | SEG6     |

| 10      | TEST     | 30      | BUF2     | 50      | K11                      | 70      | SEG7     |

| 11      | Vssd     | 31      | BUF3     | 51      | K12                      | 71      | SEG8     |

| 12      | C1       | 32      | IIL      | 52      | K13                      | 72      | SEG9     |

| 13      | C2       | 33      | IIH      | 53      | R00                      | 73      | SEG10    |

| 14      | VSS2     | 34      | CFI      | 54      | R01                      | 74      | SEG11    |

| 15      | Vdda     | 35      | SGND     | 55      | R02                      | 75      | SEG12    |

| 16      | Vssa     | 36      | VI       | 56      | R03                      | 76      | SEG13    |

| 17      | VADJ     | 37      | OVX      | 57      | BZ                       | 77      | SEG14    |

| 18      | VrF1     | 38      | OVSG     | 58      | $\overline{\mathrm{BZ}}$ | 78      | SEG15    |

| 19      | VRF2     | 39      | R1       | 59      | P00/SIN                  | 79      | COM0     |

| 20      | СН       | 40      | R2/VI5   | 60      | P01/SOUT                 | 80      | COM1     |

Fig. 1.3.2 Pin layout diagram (QFP14-80pin)

# 1.4 Pin Description

Table 1.4.1 Pin description

| Pin name            | Pin No. (QFP5) | Pin No. (QFP14) | In/Out | Function                                                                |  |  |  |  |

|---------------------|----------------|-----------------|--------|-------------------------------------------------------------------------|--|--|--|--|

| Vdd                 | 9              | 6               | (I)    | Digital system power supply pin (+)                                     |  |  |  |  |

| VDDA                | 18             | 15              | (I)    | Analog system power supply pin (+)                                      |  |  |  |  |

| Vssd                | 14             | 11              | (I)    | Digital system power supply pin (–)                                     |  |  |  |  |

| Vssa                | 19             | 16              | (I)    | Analog system GND pin (same voltage with VSSD)                          |  |  |  |  |

| Vss2                | 17             | 14              | (O)    | Analog system power supply pin (boosted voltage)                        |  |  |  |  |

| C1, C2              | 15, 16         | 12, 13          | О      | Booster capacitor connecting pins for analog system power supply (VSS2) |  |  |  |  |

| OSC1                | 10             | 7               | I      | Crystal oscillation input pin: 32.768 kHz                               |  |  |  |  |

| OSC2                | 11             | 8               | О      | Crystal oscillation output pin                                          |  |  |  |  |

| K00~K13             | 48~55          | 45~52           | I      | Input pins                                                              |  |  |  |  |

| R00~R03             | 56~59          | 53~56           | О      | Output pins                                                             |  |  |  |  |

| BZ, $\overline{BZ}$ | 60, 61         | 57, 58          | О      | Buzzer signal output pins                                               |  |  |  |  |

| P00~P03             | 62~65          | 59~62           | I/O    | I/O pins                                                                |  |  |  |  |

| VL1~VL3             | 6~8            | 3~5             | О      | LCD system voltage output pin                                           |  |  |  |  |

| COM0~3              | 2~5            | 79, 80, 1, 2    | О      | LCD common output pins (1/3, 1/4 duty, programmable)                    |  |  |  |  |

| SEG0~15             | 66~80, 1       | 63~78           | О      | LCD segment output pin (DC output may be selected by mask option)       |  |  |  |  |

| VADJ                | 20             | 17              | -      | Reference voltage adjustment pin                                        |  |  |  |  |

| VRF1                | 21             | 18              | _      | Reference voltage output pin                                            |  |  |  |  |

| VRF2                | 22             | 19              | _      | Reference voltage output pin                                            |  |  |  |  |

| ADI                 | 25             | 22              | I      | OP-AMP inverted input pin for AC-DC conversion                          |  |  |  |  |

| ADO                 | 26             | 23              | О      | OP-AMP output pin for AC-DC conversion                                  |  |  |  |  |

| AVX1                | 27             | 24              | -      | AC-DC converted voltage input pin                                       |  |  |  |  |

| AVX2                | 28             | 25              | -      | AC-DC converted voltage input pin                                       |  |  |  |  |

| IIL, IIH            | 35, 36         | 32, 33          | _      | Input pins for current measurement                                      |  |  |  |  |

| VI                  | 39             | 36              | -      | Input pin for voltage measurement                                       |  |  |  |  |

| R1                  | 42             | 39              | _      | Reference resistor connecting pin (100 $\Omega$ )                       |  |  |  |  |

| R2/VI5              | 43             | 40              | -      | Reference resistor connecting pin (1 k $\Omega$ )                       |  |  |  |  |

| R3/VI4              | 44             | 41              | -      | Reference resistor connecting pin (10 k $\Omega$ )                      |  |  |  |  |

| R4/VI3              | 45             | 42              | -      | Reference resistor connecting pin (101 k $\Omega$ )                     |  |  |  |  |

| R5/VI2              | 46             | 43              | -      | Reference resistor connecting pin (1.11 M $\Omega$ )                    |  |  |  |  |

| R6                  | 47             | 44              | -      | Reference resistor connecting pin (10 M $\Omega$ )                      |  |  |  |  |

| OVX                 | 40             | 37              | ı      | Reference resistor voltage input pin for resistance measurement         |  |  |  |  |

| OVSG                | 41             | 38              | -      | Reference resistor voltage input pin for resistance measurement         |  |  |  |  |

| SGND                | 38             | 35              | ı      | GND for measurement                                                     |  |  |  |  |

| СО                  | 29             | 26              | -      | Dummy pad                                                               |  |  |  |  |

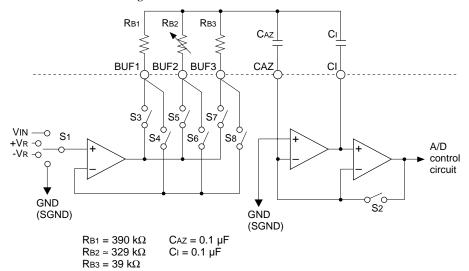

| CAZ                 | 30             | 27              | -      | Capacitor connecting pin for offset voltage zero adjustment             |  |  |  |  |

| CI                  | 31             | 28              | -      | Integral capacitor connecting pin                                       |  |  |  |  |

| BUF1~3              | 32~34          | 29~31           | -      | Buffer AMP output, integral resistor connecting pin                     |  |  |  |  |

| CFI                 | 37             | 34              | -      | Noise rejection filter connecting pin                                   |  |  |  |  |

| СН                  | 23             | 20              | -      | Capacitor connecting pin for reference voltage control                  |  |  |  |  |

| CL                  | 24             | 21              | -      | Capacitor connecting pin for reference voltage control                  |  |  |  |  |

| TEST                | 13             | 10              | I      | Testing input pin                                                       |  |  |  |  |

| RESET               | 12             | 9               | I      | Initial reset input pin                                                 |  |  |  |  |

# CHAPTER 2 POWER SUPPLY AND INITIAL RESET

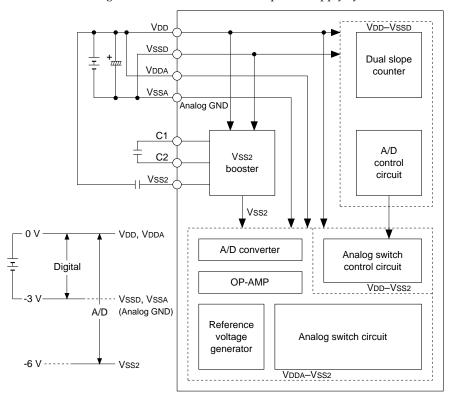

# 2.1 Power Supply

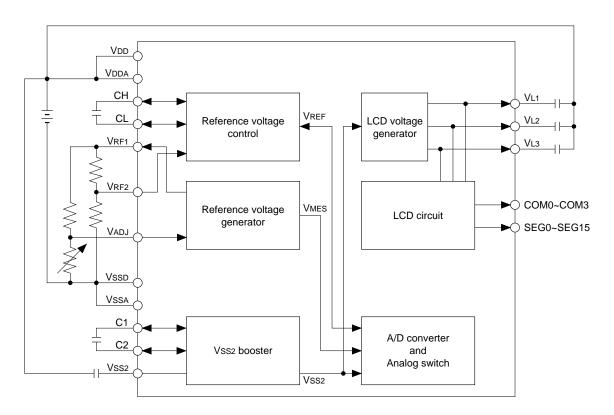

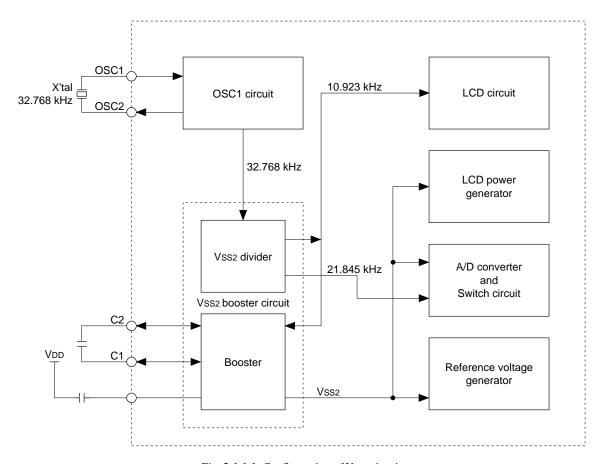

With a single external power supply (3 V \*1) supplied to VDD/VDDA through VSSD/VSSA, the E0C62M2 generates the necessary internal voltage with the regulated voltage circuit (<VL1, VL2, VL3> for LCD driving), the voltage booster (<VSS2> for analog system) and the reference voltage generator (<VRF1> for A/D converter).

Figure 2.1.1 shows the configuration of power supply.

\*1 Supply voltage: 2.15 to 3.5 V

Note: • External loads cannot be driven by the regulated voltage and voltage booster circuit's output voltage.

• See Chapter 7, "ELECTRICAL CHARACTERISTICS" for voltage values.

Fig. 2.1.1 Configuration of power supply

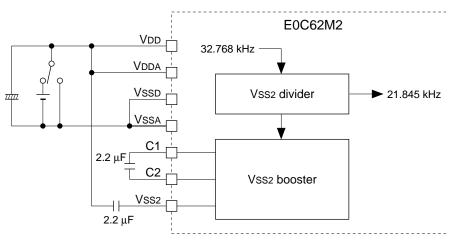

#### 2.1.1 Boosted voltage <VSS2> for analog system

Making VDD the standard (GND), the E0C62M2 voltage booster doubles the supply voltage input from the VDD-VSSD terminals to generate VSS2.

VSS2 is used to operate the analog circuits (A/D converter, analog switch circuit, reference voltage generator and LCD power generator) in the E0C62M2. This voltage can be turned ON and OFF by programming. The VSS2 booster circuit also supplies the clock to the A/D converter and the LCD driver after dividing the clock (32.768 kHz) from the crystal oscillation circuit. Therefore, the VSS2 booster should be turned ON before starting the A/D converter and/or the LCD driver operations. See Section 4.13, "VSS2 Booster" for details.

Figure 2.1.1.1 shows the configuration of the Vss2 circuit.

Fig. 2.1.1.1 Configuration of VSS2 circuit

# 2.1.2 Voltage <VL1, VL2 and VL3> for LCD driving

VL1, VL2 and VL3 are the voltages for LCD driving, and are generated by the internal LCD power generator with VDD as the standard (GND). The LCD power generator operates with the VSS2 voltage as the power supply, and can be turned ON and OFF by programming.

See Chapter 7, "ELECTRICAL CHARACTERISTICS" for the output voltage values.

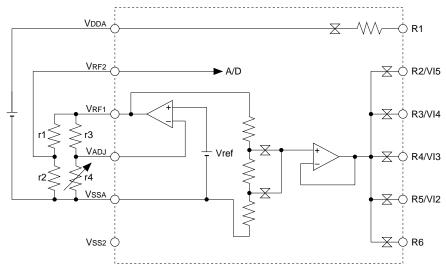

# 2.1.3 Reference voltage <VRF1, VRF2> for A/D converter

VRF1 and VRF2 are reference voltage for the A/D converter. The VRF1 voltage is generated by the reference voltage generator in the E0C62M2, and the VRF2 voltage is generated by dividing using resisters outside of the E0C62M2.

The reference voltage generator automatically starts to operate and outputs VRF1 and VRF2 by turning the A/D converter ON.

See Section 4.11, "A/D Converter" for details of the circuit configuration and the operation.

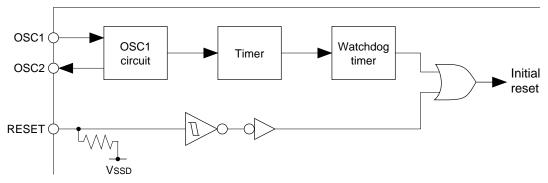

#### 2.2 Initial Reset

To initialize the E0C62M2 circuits, initial reset must be executed. There are two ways of doing this.

- (1) External initial reset using the RESET terminal

- (2) Initial reset by the watchdog timer

Be sure to use reset function (1) when turning the power ON and be sure to initialize securely. In normal operation, the circuits may be initialized by any of the above two types.

Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1 Configuration of initial reset circuit

#### 2.2.1 Reset terminal (RESET)

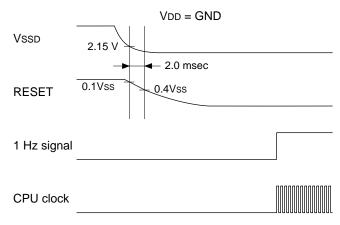

Initial reset can be executed externally by setting the reset terminal to a high level. After that, when the reset terminal goes low, the initial reset is released. However, the clock is not supplied to the CPU until the 1 Hz signal from the timer goes high after an initial reset is released. When the 1 Hz signal goes high, the CPU clock is supplied and the CPU starts to operate.

Maintain the reset terminal at a high level at least 2.0 msec to securely perform the initial reset after turning the power ON.

Figure 2.2.1.1 shows the initial reset timing with the power ON.

Fig. 2.2.1.1 Initial reset at power ON

### 2.2.2 Watchdog timer

If the CPU runs away for some reason, the watchdog timer will detect this situation and output an initial reset signal. See Section 4.2, "Resetting Watchdog Timer" for details.

However, do not perform an initial reset when turning the power ON by this function.

# 2.2.3 Internal register at initial resetting

Initial reset initializes the CPU as shown in the table below.

Table 2.2.3.1 Initial values

|                            | CPU core |                |               |  |  |  |  |  |  |  |  |

|----------------------------|----------|----------------|---------------|--|--|--|--|--|--|--|--|

| Name                       | Symbol   | Number of bits | Setting value |  |  |  |  |  |  |  |  |

| Program counter step       | PCS      | 8              | 00H           |  |  |  |  |  |  |  |  |

| Program counter page       | PCP      | 4              | 1H            |  |  |  |  |  |  |  |  |

| New page pointer           | NPP      | 4              | 1H            |  |  |  |  |  |  |  |  |

| Stack pointer              | SP       | 8              | Undefined     |  |  |  |  |  |  |  |  |

| Index register IX          | IX       | 8              | Undefined     |  |  |  |  |  |  |  |  |

| Index register IY          | IY       | 8              | Undefined     |  |  |  |  |  |  |  |  |

| Register pointer           | RP       | 4              | Undefined     |  |  |  |  |  |  |  |  |

| General-purpose register A | A        | 4              | Undefined     |  |  |  |  |  |  |  |  |

| General-purpose register B | В        | 4              | Undefined     |  |  |  |  |  |  |  |  |

| Interrupt flag             | I        | 1              | 0             |  |  |  |  |  |  |  |  |

| Decimal flag               | D        | 1              | 0             |  |  |  |  |  |  |  |  |

| Zero flag                  | Z        | 1              | Undefined     |  |  |  |  |  |  |  |  |

| Carry flag                 | C        | 1              | Undefined     |  |  |  |  |  |  |  |  |

| Peripheral circuits       |                |               |  |  |  |  |  |  |  |

|---------------------------|----------------|---------------|--|--|--|--|--|--|--|

| Name                      | Number of bits | Setting value |  |  |  |  |  |  |  |

| RAM                       | 4              | Undefined     |  |  |  |  |  |  |  |

| Display memory            | 4              | Undefined     |  |  |  |  |  |  |  |

| Other peripheral circuits | _              | *1            |  |  |  |  |  |  |  |

<sup>\*1</sup> See Section 4.1, "Memory Map".

# 2.3 Test Terminal (TEST)

This is the terminal that is used at the time of the factory inspection of the IC. During normal operation, connect the TEST terminal to VSSD/VSSA.

# CHAPTER 3 CPU, ROM, RAM

#### 3.1 *CPU*

The E0C62M2 employs the 4-bit core CPU E0C6200A for the CPU, so that register configuration, instructions and so forth are virtually identical to those in other family processors using the E0C6200A. Refer to "E0C6200/6200A Core CPU Manual" for details about the E0C6200A. Note the following points with regard to the E0C62M2:

- (1) Because the ROM capacity is 1,536 words, bank bits are unnecessary and PCB and NBP are not used.

- (2) RAM is set up to one page only, so the page portion (XP, YP) of the index register that specifies addresses is invalid. (The four bits of XP and YP are ignored.)

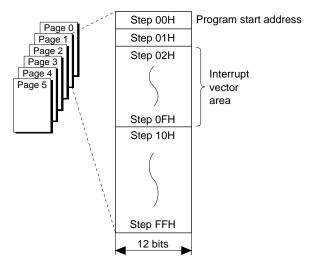

#### 3.2 ROM

The built-in ROM, a mask ROM for storing the program, has a capacity of 1,536 steps, 12 bits each. The program area is 6 pages (0–5), each of 256 steps (00H–FFH). After initial reset, the program beginning address is page 1, step 00H. The interrupt vector is allocated to page 1, steps 02H–0FH.

Fig. 3.2.1 ROM configuration

#### 3.3 RAM

The RAM, a data memory storing a variety of data, has a capacity of 128 words, each of four bits. When programming, keep the following points in mind.

- (1) Part of the data memory can be used as stack area when subroutine calls and saving registers, so be careful not to overlap the data area and stack area.

- (2) Subroutine calls and interrupts take up three words of the stack area.

- (3) The data memory 000H–00FH is for the register pointers (RP), and is the addressable memory register area.

# CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

Peripheral circuits (timer, I/O, and so on) of the E0C62M2 are memory mapped, and interfaced with the CPU. Thus, all the peripheral circuits can be controlled by using the memory operation command to access the I/O memory in the memory map.

The following sections describe how the peripheral circuits operation.

# 4.1 Memory Map

Data memory of the E0C62M2 has an address space of 180 words, of which 16 words are allocated to display memory and 36 words to I/O memory.

Figure 4.1.1 present the overall memory maps of the E0C62M2, and Tables 4.1.1(a)–(e) the peripheral circuits' (I/O space) memory maps.

Table 4.1.2 shows the A/D converter measurement function list and Table 4.1.3 shows the A/D converter measurement range list.

| Address<br>Page | Low<br>High | 0  | 1                                               | 2      | 3    | 4      | 5     | 6       | 7      | 8    | 9     | А     | В      | С | D | E | F |

|-----------------|-------------|----|-------------------------------------------------|--------|------|--------|-------|---------|--------|------|-------|-------|--------|---|---|---|---|

|                 | 0           | M0 | M0 M1 M2 M3 M4 M5 M6 M7 M8 M9 MA MB MC MD ME MF |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | 1           |    |                                                 |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | 2           |    |                                                 |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | 3           |    |                                                 |        |      |        | RΔN   | VI (12  | 28 14/ | orde | v 4 k | nite) |        |   |   |   |   |

|                 | 4           |    |                                                 |        |      |        | 1 1/1 | VI ( 12 | R/     |      | ^ - 1 | Jitaj |        |   |   |   |   |

|                 | 5           |    |                                                 |        |      |        |       |         | Κ/     | ٧V   |       |       |        |   |   |   |   |

|                 | 6           |    | Unused area                                     |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

| 0               | 7           |    |                                                 |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | 8           |    |                                                 |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | 9           |    | Unused area                                     |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | Α           |    |                                                 |        |      | )ispla | ay m  | emo     | y (10  | 6 wo | rds > | < 4 b | its) V | ٧ |   |   |   |

|                 | В           |    |                                                 |        |      |        | 1     |         |        |      |       |       | 1      |   |   |   |   |

|                 | C           |    |                                                 |        |      | 1      |       |         |        |      |       |       |        |   |   |   |   |

|                 | D           |    |                                                 |        |      |        |       |         |        |      |       |       |        | 1 |   |   |   |

|                 | <u> </u>    |    | I/O memory                                      |        |      |        |       |         |        |      |       |       |        |   |   |   |   |

|                 | F           |    | ,                                               | 101110 | '' y |        |       |         |        |      |       |       |        |   |   |   |   |

Unused area

Fig. 4.1.1 Memory map

Note: Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these area.

#### **CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)**

Table 4.1.1(a) I/O memory map (COH–CAH)

| A -1 -1 |           | Regi         | ister        |            |            |              |              |         | 0                                           |

|---------|-----------|--------------|--------------|------------|------------|--------------|--------------|---------|---------------------------------------------|

| Address | D3        | D2           | D1           | D0         | Name       | Init *1      | 1            | 0       | Comment                                     |

|         | SIK03     | SIK02        | SIK01        | SIK00      | SIK03      | 0            | Enable       | Disable | Interrupt selection register (K03)          |

| COH     | SIKUS     | JIKUZ        | SIKUT        | SIKOO      | SIK02      | 0            | Enable       | Disable | Interrupt selection register (K02)          |

| 0011    |           | R/           | W            |            | SIK01      | 0            | Enable       | Disable | Interrupt selection register (K01)          |

|         |           |              |              |            | SIK00      | 0            | Enable       | Disable | Interrupt selection register (K00)          |

|         | K03       | K02          | K01          | K00        | K03        | - *2         | High         | Low     |                                             |

| C1H     | 1100      | 1.02         |              | 1100       | K02        | - *2         | High         | Low     | Input port (K00–K03)                        |

| 0       |           | F            | 3            |            | K01        | - *2         | High         | Low     | input port (1100 1100)                      |

|         |           |              |              |            | K00        | - *2         | High         | Low     |                                             |

|         | SIK13     | SIK12        | SIK11        | SIK10      | SIK13      | 0            | Enable       | Disable | Interrupt selection register (K13)          |

| C2H     |           |              |              |            | SIK12      | 0            | Enable       | Disable | Interrupt selection register (K12)          |

|         |           | R/           | W            |            | SIK11      | 0            | Enable       | Disable | Interrupt selection register (K11)          |

|         |           |              |              |            | SIK10      | 0 "2         | Enable       | Disable | Interrupt selection register (K10)          |

|         | K13       | K12          | K11          | K10        | K13        | - *2         | High         | Low     |                                             |

| СЗН     |           |              |              |            | K12        | - *2<br>- *2 | High         | Low     | Input port (K10–K13)                        |

|         |           | F            | ₹            |            | K11        |              | High         | Low     |                                             |

|         |           |              |              |            | K10        |              | High         | Low     |                                             |

|         | R03       | R02          | R01          | R00        | R03        | 0            | High<br>High | Low     |                                             |

| C4H     |           |              |              |            | R02<br>R01 | 0            | High         | Low     | Output port (R00–R03)                       |

|         |           | R/           | W            |            | R00        | 0            | High         | Low     |                                             |

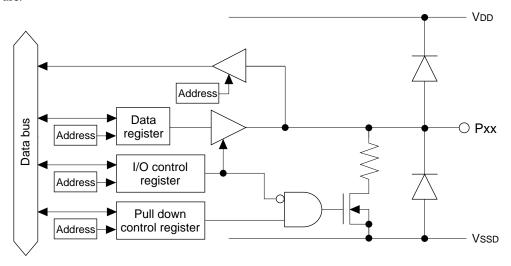

|         |           |              |              |            | IOC03      | 0            | Output       | Input   | 7                                           |

|         | IOC03     | IOC02        | IOC01        | IOC00      | 10C03      | 0            | Output       | Input   |                                             |

|         |           |              |              |            | IOC02      | 0            | Output       | Input   | I/O control register (P00–P03)              |

|         |           | R/           | W            |            | IOC00      | 0            | Output       | Input   | (ESIF = 0)                                  |

| C8H     | When the  | e serial I/F | is used (I   | ESIF = 1): | IOC03      | 0            | Output       | Input   | Master mode: P03 I/O control register       |

| 0011    |           | N (in), P0   |              |            | IOC03      | 0            | 1            | 0       | Slave mode: General-purpose register        |

|         |           | CLK (mast    |              |            | IOC02      | 0            | 1            | 0       |                                             |

|         |           | RDY (slave   |              | ,,         | IOC01      | 0            | 1            | 0       | General-purpose register                    |

|         |           | O port (ma   |              | t)         | IOC00      | 0            | 1            | 0       |                                             |

|         |           |              |              |            | PUL03      | 1            | On           | Off     | 7                                           |

|         | PUL03     | PUL02        | PUL01        | PUL00      | PUL02      | 1            | On           | Off     | P. 11.1                                     |

|         |           | . D/         | W            |            | PUL01      | 1            | On           | Off     | Pull down control register (P00–P03)        |

|         |           | K/           | VV           |            | PUL00      | 1            | On           | Off     | (ESIF = 0)                                  |

| C9H     | When the  | e serial I/F | is used (I   | ESIF = 1): | PUL03      | 1            | On           | Off     | Master mode: P03 pull down control register |

| C9H     | P00 = SI  | N (in), P0   | 1 = SOUT     | (out),     | PUL03      | 1            | 1            | 0       | Slave mode: General-purpose register        |

|         | P02 = S0  | CLK (mast    | er: out, sla | ave: in),  | PUL02      | 1            | 1            | 0       | Master mode: General-purpose register       |

|         | P03 = SI  | RDY (slave   | e: out),     |            | PUL02      | 1            | On           | Off     | Slave mode: SCKL pull down control register |

|         | P03 = I/0 | O port (ma   | ster: in/ou  | t)         | PUL01      | 1            | 1            | 0       | General-purpose register                    |

|         |           |              |              |            | PUL00      | 1            | On           | Off     | SIN pull down control register              |

|         | P03       | P02          | P01          | P00        | P03        | - *2         | High         | Low     |                                             |

|         | . 55      | . 52         |              | . 50       | P02        | - *2         | High         | Low     | I/O port (P00–P03)                          |

|         |           | R/           | W            |            | P01        | - *2         | High         | Low     | (ESIF = 0)                                  |

| 0.11    | L         |              |              |            | P00        | - *2         | High         | Low     |                                             |

| CAH     |           | e serial I/F |              |            | P03        | - *2         | High         | Low     | Master mode: I/O port P03                   |

|         |           | N (in), P0   |              |            | P03        | - *2         | 1            | 0       | Slave mode: General-purpose register        |

|         |           | CLK (mast    |              | ave: in),  | P02        | - *2         | 1            | 0       |                                             |

|         |           | RDY (slave   |              |            | P01        | - *2         | 1            | 0       | General-purpose register                    |

|         | P03 = I/O | O port (ma   | ster: in/ou  | t)         | P00        | - *2         | 1            | 0       |                                             |

<sup>\*1</sup> Initial value at the time of initial reset

12

<sup>\*2</sup> Not set in the circuit

<sup>\*3</sup> Undefined

<sup>\*4</sup> Resets (0) immediately after being read \*5 Constantly "0" when being read

# CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)

Table 4.1.1(b) I/O memory map (CCH–CFH)

| Address |     | Reg  | ister |      |          |         |                |           | Comment                                   |

|---------|-----|------|-------|------|----------|---------|----------------|-----------|-------------------------------------------|

| Address | D3  | D2   | D1    | D0   | Name     | Init *1 | 1              | 0         | Comment                                   |

|         |     |      |       |      | 0 *5     | - *2    |                |           | Unused                                    |

|         | 0   | 0    | SCTRG | ESIF | 0 *5     | - *2    |                |           | Unused                                    |

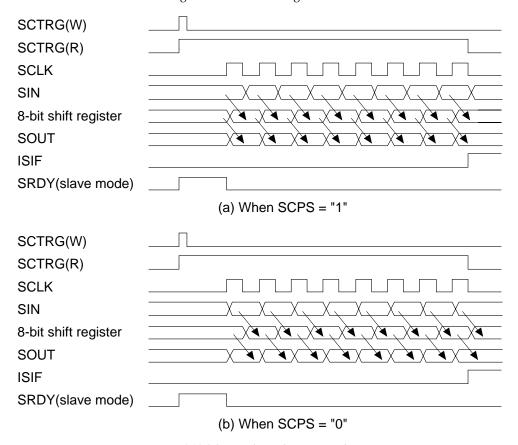

| CCH     |     |      |       |      | SCTRG(W) | - *2    | Trigger        | -         | Serial interface clock trigger (writing)  |

|         |     | R    | R/    | w/W  | SCTRG(R) | 0       | Run            | Stop      | Serial interface clock status (reading)   |

|         |     |      |       |      | ESIF     | 0       | SIF port       | I/O port  | P0 port function selection                |

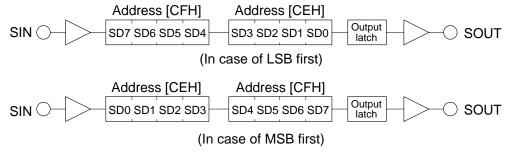

|         | SDP | SCPS | SCS1  | SCS0 | SDP      | 0       | LSB first      | MSB first | Serial data input/output permutation      |

| CDH     | SUF | 3013 | 3031  | 3030 | SCPS     | 0       | _ <del>_</del> | 7         | Serial interface clock phase selection    |

| CDH     |     | D    | /W    |      | SCS1     | 0       |                |           | Serial interface clock mode selection     |

|         |     |      | / VV  |      | SCS0     | 0       |                |           | ☐ 0: Slave, 1: CLK/2, 2: CLK, 3: CLK      |

|         | SD3 | SD2  | SD1   | SD0  | SD3      | - *2    |                |           | MSB                                       |

| CEH     | 303 | 302  | 301   | 350  | SD2      | - *2    |                |           | Serial interface data (low-order 4 bits)  |

| CEH     |     | D    | /W    |      | SD1      | - *2    |                |           | Scriai interface data (10w-order 4 bits)  |

|         |     |      | / VV  |      | SD0      | - *2    |                |           | LSB                                       |

|         | SD7 | SD6  | SD5   | SD4  | SD7      | - *2    |                |           | MSB                                       |

| CFH     | 301 | 300  | 300   | 304  | SD6      | - *2    |                |           | Serial interface data (high-order 4 bits) |

| Crn     |     | D    | w     |      | SD5      | - *2    |                |           | Seriai interface data (ingn-order 4 orts) |

|         |     | N.   | vv    |      | SD4      | - *2    |                |           | _ LSB                                     |

Table 4.1.1(c) I/O memory map (D0H–D6H)

| Address |       | Reg    | ister       |       |         |         |              |                         | Comment                                         |

|---------|-------|--------|-------------|-------|---------|---------|--------------|-------------------------|-------------------------------------------------|

| Address | D3    | D2     | D1          | D0    | Name    | Init *1 | 1            | 0                       | Comment                                         |

|         | 0     | 0      | BZFQ        | R     | 0 *5    | - *2    |              |                         | Unused                                          |

| DOH     | U     | 0      | DZI Q       | I.    | 0 *5    | - *2    |              |                         | Unused                                          |

| DOLL    |       | R      | P.          | w     | BZFQ    | 0       | 2 kHz        | 4 kHz                   | Buzzer signal frequency selection               |

|         |       |        | 10          | •••   | R       | 0       | 1            | 0                       | 1 bit general-purpose register                  |

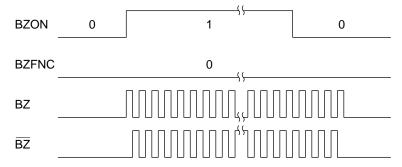

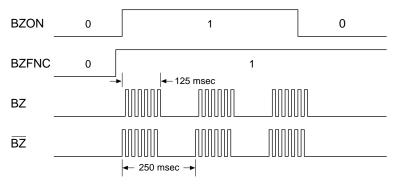

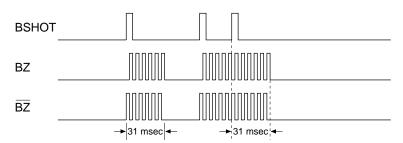

|         | 0     | BSHOT  | BZFNC       | BZON  | 0 *5    | - *2    |              |                         | Unused                                          |

| D1H     | U     | DOTTO  | DZINO       | DZON  | BSHOT*5 | - *2    | One-shot     | -                       | One-shot buzzer signal (31 msec) output trigger |

| וווט    | R     | l w    | P.          | w     | BZFNC   | 0       | Intermittent | Continuous              | Continuous/intermittent output selection        |

|         | IX.   | **     | IX/VV       |       | BZON    | 0       | On           | Off                     | Buzzer signal output control                    |

|         | 0     | 0 WDRS |             | TMRST | 0 *5    | - *2    |              |                         | Unused                                          |

| D4H     | 0     | 0      | WDRST       |       | 0 *5    | - *2    |              |                         | Unused                                          |

| D411    |       | R      | ١,          | V     | WDRST*5 | - *2    | Reset        | -                       | Watchdog timer reset                            |

|         |       |        | ,           |       | TMRST*5 | - *2    | Reset        | -                       | Clock timer and watchdog timer reset            |

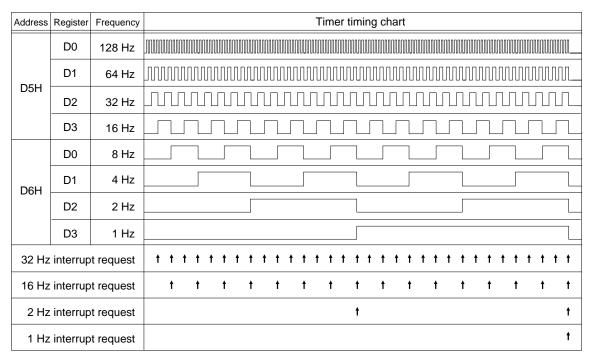

|         | TM3   | TM2    | TM1         | TM0   | TM3     | - *3    |              |                         | Clock timer data (16 Hz)                        |

| D5H     | TIVIS | TIVIZ  | 11011       | TIVIO | TM2     | - *3    |              |                         | Clock timer data (32 Hz)                        |

| DOLL    |       |        | R           |       | TM1     | - *3    |              |                         | Clock timer data (64 Hz)                        |

|         |       |        |             |       | TM0     | - *3    |              |                         | Clock timer data (128 Hz)                       |

|         | TM7   | TM6    | TM5         | TM4   | TM7     | - *3    |              |                         | Clock timer data (1 Hz)                         |

| D6H     | 11017 | 1100   | TIVIO TIVI4 |       | TM6     | - *3    |              |                         | Clock timer data (2 Hz)                         |

| ווטם    |       | R      |             | TM5   | - *3    |         |              | Clock timer data (4 Hz) |                                                 |

|         |       |        |             |       | TM4     | - *3    |              |                         | Clock timer data (8 Hz)                         |

#### **CHAPTER 4: PERIPHERAL CIRCUITS AND OPERATION (Memory Map)**

Table 4.1.1(d) I/O memory map (E0H–EBH)

|              |       | Rea            | ister          |       |                      |                      |                                                                                    |               |                                                                 |

|--------------|-------|----------------|----------------|-------|----------------------|----------------------|------------------------------------------------------------------------------------|---------------|-----------------------------------------------------------------|

| Address      | D3    | D2             | D1             | D0    | Name                 | Init *1              | 1                                                                                  | 0             | Comment                                                         |

| FOLI         | -     | -              | -              | VSS2  | -                    | - *3<br>- *3         |                                                                                    | -             | Unused (Undefined when reading) Unused (Undefined when reading) |

| E0H          |       | R              | •              | R/W   | -<br>VSS2            | - *3<br>0            | On                                                                                 | Off           | Unused (Undefined when reading)<br>VSS2 booster control         |

| <b>-</b> 411 | LOFF  | 0              | LDTY           | LPWR  | LOFF<br>0 *5         | 0<br>- *2            | All off                                                                            | Normal        | LCD display all off / normal switch<br>Unused                   |

| E1H          | R/W   | R              | R R/W          |       | LDTY<br>LPWR         | 0                    | 1/3<br>On                                                                          | 1/4<br>Off    | LCD drive duty selection<br>LCD driver On/Off                   |

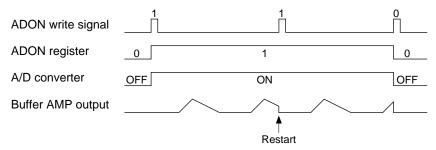

| E2H          | BUFF  | IIN ADSPD ADON |                | ADON  | BUFF<br>IIN          | 0<br>0               | -<br>IIH                                                                           | -<br>IIL      | Fix at 0 Current measurement terminal switching                 |

| СИП          |       | R/W            |                |       | ADSPD<br>ADON        | 0                    | 100 mS<br>On                                                                       | 400 mS<br>Off | A/D conversion speed switching<br>A/D converter On/Off          |

| E3H          | 0     | 0              | SVDDT          | SVDON | 0 *5<br>0 *5         | - *2<br>- *2         |                                                                                    |               | Unused<br>Unused                                                |

| 2011         |       | R              |                | R/W   | SVDDT<br>SVDON       | 0                    | Low<br>On                                                                          | Normal<br>Off | Supply voltage detection data<br>SVD circuit On/Off             |

| E4H          | 0     | FNC2           | FNC1           | FNC0  | 0 *5<br>FNC2         | - *2<br>0            |                                                                                    |               | Unused  Measurement function selection                          |

|              | R     | R/W            |                | T     | FNC1<br>FNC0         | 0                    |                                                                                    |               | (See Table 4.1.2)                                               |

| E5H          | 0     | RNG2 RNG1 RNG0 |                | RNG0  | 0 *5<br>RNG2         | - *2<br>0            |                                                                                    |               | Unused  Measurement range selection                             |

|              | R     | R/W            |                | T     | RNG1<br>RNG0         | 0 0 - *2             |                                                                                    |               | (See Table 4.1.3)                                               |

| E6H          | 0     | 0              | 0              | ADP   | 0 *5<br>0 *5<br>0 *5 | - *2<br>- *2<br>- *2 |                                                                                    |               | Unused<br>Unused<br>Unused                                      |

|              |       |                | R              |       | ADP                  | 1                    | Positive                                                                           | Negative      | A/D converter polarity judgment                                 |

| E7H          | DSC03 | DSC02          | DSC01          | DSC00 | DSC03<br>DSC02       | 0                    | 1                                                                                  | 0             | A/D conversion data (00–03)                                     |

|              |       |                | R              |       | DSC01<br>DSC00       | 0                    | 1                                                                                  | 0             |                                                                 |

| E8H          | DSC13 | DSC12          | DSC11          | DSC10 | DSC13<br>DSC12       | 0                    | 1                                                                                  | 0<br>0        | A/D conversion data (10–13)                                     |

|              |       |                | R              | Ī     | DSC11<br>DSC10       | 0                    | 1                                                                                  | 0             |                                                                 |

| E9H          | DSC23 | DSC22          | DSC21          | DSC20 | DSC23<br>DSC22       | 0                    | 1                                                                                  | 0             | A/D conversion data (20–23)                                     |

|              |       | R              |                | Γ     | DSC21<br>DSC20       | 0                    | 1                                                                                  | 0             |                                                                 |

| EAH          | 0     | DSC32          | DSC31          | DSC30 | 0 *5<br>DSC32        | - *2<br>0            | 1                                                                                  | 0             | Unused                                                          |

| R            |       |                | DSC31<br>DSC30 | 0     | 1                    | 0                    | A/D conversion data (30–32)                                                        |               |                                                                 |

| EBH          | 0     | IDR            | STS1           | STS0  | 0 *5<br>IDR          | - *2<br>0            | Invalid                                                                            | Effective     | Unused<br>Read data status                                      |

|              | R     |                | STS1<br>STS0   | 0     |                      |                      | A/D conversion status 0: auto zero adjustme 1: input integral, 3: reverse integral |               |                                                                 |

*Table 4.1.1(e) I/O memory map (F0H–F6H)*

| Address |          | Reg       | ister        |       |         |         |        |        | Comment                                     |

|---------|----------|-----------|--------------|-------|---------|---------|--------|--------|---------------------------------------------|

| Address | D3       | D2        | D1           | D0    | Name    | Init *1 | 1      | 0      | Comment                                     |

|         | EIK1     | EIK0      | EISIF        | EIAD  | EIK1    | 0       | Enable | Mask   | Interrupt mask register (K10–K13)           |

| FOH     | EINI     | EIKU      | EISIF   EIAU |       | EIK0    | 0       | Enable | Mask   | Interrupt mask register (K00–K03)           |

| ГОП     | R/W      |           |              |       | EISIF   | 0       | Enable | Mask   | Interrupt mask register (Serial interface)  |

|         |          | K         | / VV         |       | EIAD    | 0       | Enable | Mask   | Interrupt mask register (A/D converter)     |

|         | EIT1     | EIT2      | EIT16        | EIT32 | EIT1    | 0       | Enable | Mask   | Interrupt mask register (Clock timer 1 Hz)  |

| F1H     | LIII     | LIIZ      | LITTO        | LIIJZ | EIT2    | 0       | Enable | Mask   | Interrupt mask register (Clock timer 2 Hz)  |

| - 1     |          | D         | /W           |       | EIT16   | 0       | Enable | Mask   | Interrupt mask register (Clock timer 16 Hz) |

|         |          | K         | / VV         |       | EIT32   | 0       | Enable | Mask   | Interrupt mask register (Clock timer 32 Hz) |

|         | 0        | 0         | 0            | IK1   | 0 *5    | - *2    |        |        | Unused                                      |

| F2H     | <u> </u> | 0         |              | IKI   | 0 *5    | - *2    |        |        | Unused                                      |

| ГИП     | R        |           |              |       | 0 *5    | - *2    |        |        | Unused                                      |

|         | K        |           |              |       | IK1 *4  | 0       | Yes    | No     | Interrupt factor flag (K10–K13)             |

|         | 0        | 0         | 0            | IK0   | 0 *5    | - *2    |        |        | Unused                                      |

| F3H     |          | 0         |              | IIKU  | 0 *5    | - *2    |        |        | Unused                                      |

| 1311    |          |           | 2            |       | 0 *5    | - *2    |        |        | Unused                                      |

|         |          |           |              |       | IK0 *4  | 0       | Yes    | No     | Interrupt factor flag (K00–K03)             |

|         | 0        | 0         | 0            | ISIF  | 0 *5    | - *2    |        |        | Unused                                      |

| F4H     |          |           |              | 1511  | 0 *5    | - *2    |        |        | Unused                                      |

| 1411    |          |           | 2            |       | 0 *5    | - *2    |        |        | Unused                                      |

|         |          |           |              |       | ISIF *4 | 0       | Yes    | No     | Interrupt factor flag (Serial interface)    |

|         | IT1      | IT2       | IT16         | IT32  | IT1 *4  | 0       | Yes    | No     | Interrupt factor flag (Clock timer 1 Hz)    |

| F5H     | 1111     | 112       | 1110         | 1132  | IT2 *4  | 0       | Yes    | No     | Interrupt factor flag (Clock timer 2 Hz)    |

| 1311    | R        |           |              |       | IT16 *4 | 0       | Yes    | No     | Interrupt factor flag (Clock timer 16 Hz)   |

|         | K        |           |              |       | IT32 *4 | 0       | Yes    | No     | Interrupt factor flag (Clock timer 32 Hz)   |

|         | 0        | 0 0 0 IAD |              | 0 *5  | - *2    |         |        | Unused |                                             |

| F6H     | <u> </u> |           |              | IAD   | 0 *5    | - *2    |        |        | Unused                                      |

| 1011    | R        |           |              |       | 0 *5    | - *2    |        |        | Unused                                      |

|         |          |           | 1            |       | IAD *4  | 0       | Yes    | No     | Interrupt factor flag (A/D converter)       |

Table 4.1.2 A/D converter measurement function list

| Address | D3 | D2<br>FNC2 | D1<br>FNC1 | D0<br>FNC0 | Measurement function           | Integral resistor<br>normal mode (400 ms) | Integral resistor<br>high speed mode (100 ms) | General<br>amplifier | Com-<br>parator |

|---------|----|------------|------------|------------|--------------------------------|-------------------------------------------|-----------------------------------------------|----------------------|-----------------|

|         | -  | 0          | 0          | 0          | DC voltmeter mode              | BUF1 terminal                             | BUF3 terminal                                 | OFF                  | OFF             |

|         | -  | 0          | 0          | 1          | AC voltmeter mode              |                                           |                                               | ON                   | OFF             |

|         | -  | 0          | 1          | 0          | DC ammeter mode                |                                           |                                               | OFF                  | OFF             |

|         | -  | 0          | 1          | 1          | AC ammeter mode                |                                           |                                               | ON                   | OFF             |

| E4H     | -  | 1          | 0          | 0          | Resistance<br>measurement mode | Input integral: BUF1 t                    | erminal                                       | OFF                  | OFF             |

|         | -  | 1          | 0          | 1          | Continuity check               | Reverse integral: BUF                     | 1 and BUF2 terminals                          | OFF                  | ON              |

|         |    |            |            |            | mode                           | para                                      | llel                                          |                      |                 |

|         | -  | 1          | 1          | 0          | _                              | BUF1 terminal                             | BUF3 terminal                                 | OFF                  | OFF             |

|         | -  | 1          | 1          | 1          | ADPT mode                      |                                           |                                               | OFF                  | OFF             |

<sup>\*</sup> In the resistance measurement mode and continuity check mode, switching between input integral (BUF1 terminal) and reverse integral (BUF1 and BUF2 terminals parallel) is automatically done by the hardware.

Table 4.1.3 A/D converter measurement range list

| Address | D3 | D2   | D1   | D0   | Measurement function |              |                        |                  |               |  |  |

|---------|----|------|------|------|----------------------|--------------|------------------------|------------------|---------------|--|--|

| Address |    | RNG2 | RNG1 | RNG0 | DC voltmeter         | AC voltmeter | Resistance             | Continuity check | Current       |  |  |

|         | -  | 0    | 0    | 0    | 400 mV               | 400 mV       | $400 \Omega$           | 50 Ω judgment    | Switching     |  |  |

|         | -  | 0    | 0    | 1    | 4 V                  | 4 V          | $4~\mathrm{k}\Omega$   | 100 Ω judgment   | outside of IC |  |  |

|         | -  | 0    | 1    | 0    | 40 V                 | 40 V         | 40 kΩ                  | 500 Ω judgment   |               |  |  |

| EELI    | -  | 0    | 1    | 1    | 400 V                | 400 V        | $400~\mathrm{k}\Omega$ | 1 kΩ judgment    |               |  |  |

| E5H     | -  | 1    | 0    | 0    | 1000 V               | 750 V        | $4~\mathrm{M}\Omega$   | 1                |               |  |  |

|         | _  | 1    | 0    | 1    | <b>↑</b>             | <b>↑</b>     | $40~\mathrm{M}\Omega$  | <b>↑</b>         |               |  |  |

|         | -  | 1    | 1    | 0    | 1                    | 1            | <b>↑</b>               | 1                |               |  |  |

|         | -  | 1    | 1    | 1    | <b>↑</b>             | <b>↑</b>     | <b>↑</b>               | <b>↑</b>         |               |  |  |

<sup>\*</sup> In the current measurement mode, the E0C62M2 performs an A/D conversion using a voltage value (within ±437 mV) input from the IIL terminal or IIH terminal. Consequently, it is not necessary to switch the range.

# 4.2 Resetting Watchdog Timer

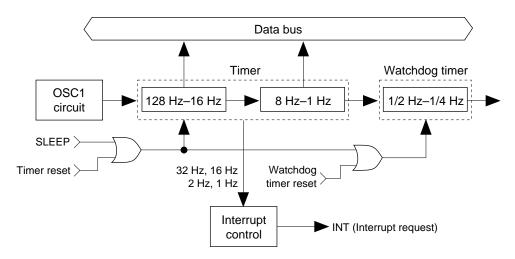

### 4.2.1 Configuration of watchdog timer

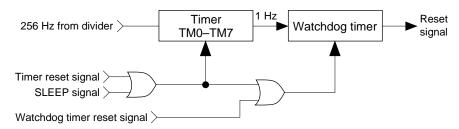

The E0C62M2 incorporates a watchdog timer as the source oscillator for OSC1 (clock timer 1 Hz signal). The watchdog timer must be reset cyclically by the software. If reset is not executed in at least 3 seconds, the initial reset signal is output automatically for the CPU.

Figure 4.2.1.1 is the block diagram of the watchdog timer.

Fig. 4.2.1.1 Watchdog timer block diagram

The watchdog timer, configured of a two-bit binary counter, generates the initial reset signal internally by overflow of the counter.

Watchdog timer reset processing in the program's main routine enables detection of program overrun, such as when the main routine's watchdog timer processing is bypassed. Ordinarily this routine is incorporated where periodic processing takes place, just as for the timer interrupt routine.

The watchdog timer can also be reset by the resetting of the clock timer.

The watchdog timer operates in the HALT mode. If the watchdog timer is not reset within 3 or 4 seconds including the HALT status, the IC reactivates from initial reset status.

When the E0C62M2 enters SLEEP status by the SLP instruction, the watchdog timer and the clock timer are reset. Therefore, when SLEEP status is released, the watchdog timer and the clock timer operate the same as that after releasing an initial reset.

# 4.2.2 Control of watchdog timer

Table 4.2.2.1 lists the watchdog timer's control bits and their address.

Table 4.2.2.1 Control bits of watchdog timer

| Address | Register |          |       |       |         |         |       |   | Comment                              |

|---------|----------|----------|-------|-------|---------|---------|-------|---|--------------------------------------|

| Addiess | D3       | D2       | D1 D0 |       | Name    | Init *1 | 1     | 0 | Comment                              |

|         | 0        | 0        | WDRST | TMRST | 0 *5    | - *2    |       |   | Unused                               |

| Dati    | U        | U        | WDK31 |       | 0 *5    | - *2    |       |   | Unused                               |

| D4H     |          | <u> </u> |       |       | WDRST*5 | - *2    | Reset | - | Watchdog timer reset                 |

|         | ľ        | ?        |       |       | TMRST*5 | - *2    | Reset | ı | Clock timer and watchdog timer reset |

- \*1 Initial value at the time of initial reset

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Resets (0) immediately after being read

- \*5 Constantly "0" when being read

- \*6 Refer to main manual

#### WDRST: Watchdog timer reset (D4H•D1)

This is the bit for resetting the watchdog timer.

When "1" is written: Watchdog timer is reset

When "0" is written: No operation Reading: Always "0"

When "1" is written to WDRST, the watchdog timer is reset, and the operation restarts immediately after this. When "0" is written to WDRST, no operation results.

This bit is dedicated for writing, and is always "0" for reading.

16 EPSON E0C62M2 TECHNICAL MANUAL

#### TMRST: Clock timer reset (D4H•D0)

This is the bit for resetting the clock timer and the watchdog timer.

When "1" is written: Clock timer and watchdog timer are reset

When "0" is written: No operation Reading: Always "0"

When "1" is written to TMRST, the clock timer and the watchdog timer are reset, and the operation restarts immediately after this. When "0" is written to TMRST, no operation results.

This bit is dedicated for writing, and is always "0" for reading.

# 4.2.3 Programming note

The watchdog timer must be reset within 3-second cycles.

# 4.3 Oscillation Circuit

# 4.3.1 Configuration of oscillation circuit

The E0C62M2 has a oscillation circuit (OSC1). OSC1 is a crystal oscillation circuit that supplies the operating clock to the CPU and peripheral circuits.

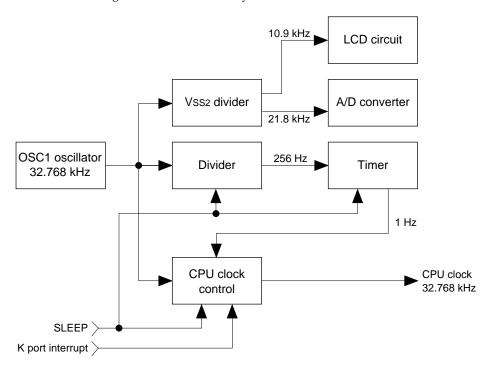

Figure 4.3.1.1 is the block diagram of this oscillation system.

Fig. 4.3.1.1 Oscillation system

#### 4.3.2 Crystal oscillation circuit

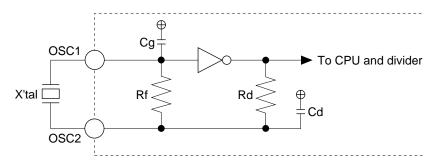

The E0C62M2 has a built-in crystal oscillation circuit. The OSC1 oscillation circuit generates the operating clock for the CPU and peripheral circuitry by connecting the crystal oscillator (Typ. 32.768 kHz) as an external element.

Figure 4.3.2.1 is the block diagram of the OSC1 oscillation circuit.

Fig. 4.3.2.1 OSC1 oscillation circuit

As Figure 4.3.2.1 indicates, the crystal oscillation circuit can be configured simply by connecting the crystal oscillator (X'tal) between terminals OSC1 and OSC2.

The OSC1 oscillation circuit starts to operate immediately after turning the power ON, so programming is not necessary to control the circuit. However, be aware that the system clock is not supplied to the CPU until the 1 Hz signal from the timer goes high after initial resetting.

In the E0C62M2, the OSC1 oscillation circuit does not stop even when the CPU enters SLEEP status. However, SLEEP stops supplying the clock to the peripheral circuits (timer and watchdog timer).

# 4.3.3 Clock frequency and instruction execution time

Table 4.3.3.1 shows the instruction execution time according to the system clock from the OSC1 oscillation circuit.

Table 4.3.3.1 Clock frequency and instruction execution time

| Clock from tonov | Instruction execution time (μsec) |                     |                      |  |  |  |  |  |  |

|------------------|-----------------------------------|---------------------|----------------------|--|--|--|--|--|--|

| Clock frequency  | 5-clock instruction               | 7-clock instruction | 12-clock instruction |  |  |  |  |  |  |

| OSC1: 32.768 kHz | 152.6                             | 213.6               | 366.2                |  |  |  |  |  |  |

# 4.4 Input Ports (K00–K03, K10–K13)

### 4.4.1 Configuration of input ports

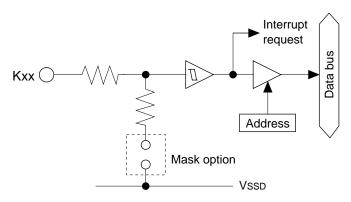

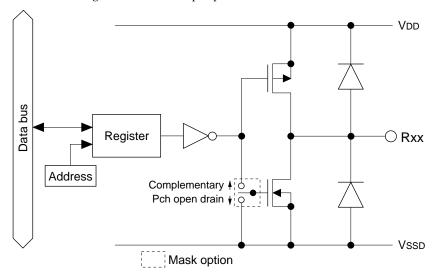

The E0C62M2 has eight bits general-purpose input ports. Each of the input port terminals (K00–K03, K10–K13) provides internal pull down resistor. Pull down resistor can be selected for each bit with the mask option.

Further, a Schmitt buffer is provided on each input line of all input terminals (K00–K03, K10–K13). Figure 4.4.1.1 shows the configuration of input port.

Fig. 4.4.1.1 Configuration of input port

Selection of "With pull down resistor" with the mask option suits input from the push switch, key matrix, and so forth. When "Gate direct" is selected, the port can be used for slide switch input and interfacing with other LSIs.

Further, all the input port terminals (K00-K03, K10-K13) are used as the interrupt port for releasing the SLEEP mode. See Section 4.15, "Interrupt and HALT/SLEEP" for details.

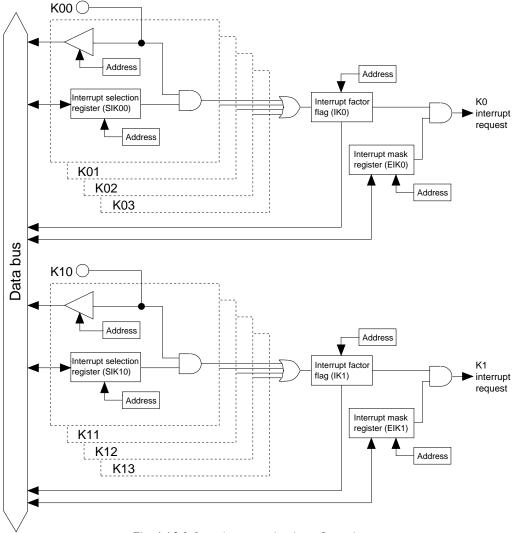

# 4.4.2 Interrupt function

All eight bits of the input ports (K00–K03, K10–K13) provide the interrupt function. The conditions for issuing an interrupt can be set by the software.

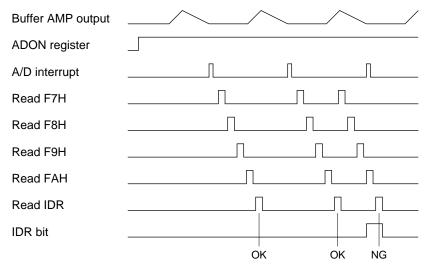

Figure 4.4.2.1 shows the configuration of input interrupt circuit.