MF1195-01

# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

## E0C63P466 Technical Hardware

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

MS-DOS and Windows95/98 are registered trademarks of Microsoft Corporation, U.S.A. PC/AT and IBM are registered trademarks of International Business Machines Corporation, U.S.A. The flash technology in this product is licensed from Silicon Storage Technology Inc. in the U.S.A. All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

### **CONTENTS**

| CHAPTER 1 | <b>O</b> U2 | TLINE                                                                                                                   |        | 1  |

|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------|--------|----|

|           | 1.1         | Features                                                                                                                |        |    |

|           | 1.2         | Block Diagram                                                                                                           |        |    |

|           | 1.3         | Pin Layout Diagram                                                                                                      |        |    |

|           | 1.4         | Pin Description                                                                                                         | 4      |    |

|           | 1.5         | Mask Option                                                                                                             |        |    |

| CHAPTER 2 | Pov         | ver Supply and Initial Reset                                                                                            |        | 6  |

|           | 2.1         | Power Supply<br>2.1.1 Voltage <vd1> for oscillation circuit<br/>2.1.2 Voltage <vc1-vc5> for LCD driving</vc1-vc5></vd1> | 7      |    |

|           | 2.2         | Initial Reset                                                                                                           | 8<br>8 |    |

|           | 2.3         | Test Terminal ( $\overline{TEST}$ )                                                                                     |        |    |

|           | 2.4         | Terminals for Flash EEPROM                                                                                              | 10     |    |

| CHAPTER 3 | CP          | U, ROM, RAM                                                                                                             | i      | 11 |

|           | 3.1         | CPU                                                                                                                     |        |    |

|           | 3.2         | Code ROM                                                                                                                |        |    |

|           | 3.3         | RAM                                                                                                                     |        |    |

|           | 3.4         | Data ROM                                                                                                                |        |    |

| CHAPTER 4 | Рек         | RIPHERAL CIRCUITS AND OPERATION                                                                                         |        | 13 |

|           | 4.1         | Memory Map                                                                                                              |        |    |

|           | 4.2         | Watchdog Timer                                                                                                          |        |    |

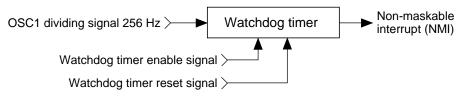

|           |             | 4.2.1 Configuration of watchdog timer                                                                                   |        |    |

|           |             | 4.2.2 Interrupt function                                                                                                |        |    |

|           |             | 4.2.3 I/O memory of watchdog timer                                                                                      |        |    |

|           | 12          | 4.2.4 Programming notes                                                                                                 |        |    |

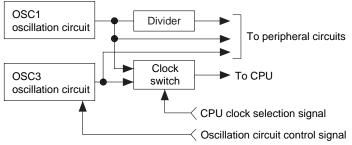

|           | 4.3         | Oscillation Circuit                                                                                                     |        |    |

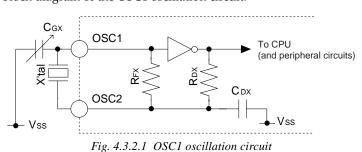

|           |             | 4.3.2 OSC1 oscillation circuit                                                                                          |        |    |

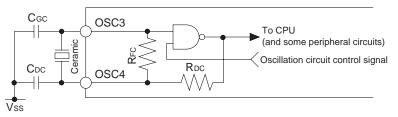

|           |             | 4.3.3 OSC3 oscillation circuit                                                                                          |        |    |

|           |             | 4.3.4 Operating voltage                                                                                                 | 22     |    |

|           |             | 4.3.5 Switching operating clock                                                                                         |        |    |

|           |             | 4.3.6 Clock frequency and instruction execution time                                                                    |        |    |

|           |             | 4.3.7 I/O memory of oscillation circuit<br>4.3.8 Programming notes                                                      |        |    |

|           | 1 1         |                                                                                                                         |        |    |

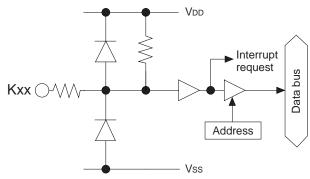

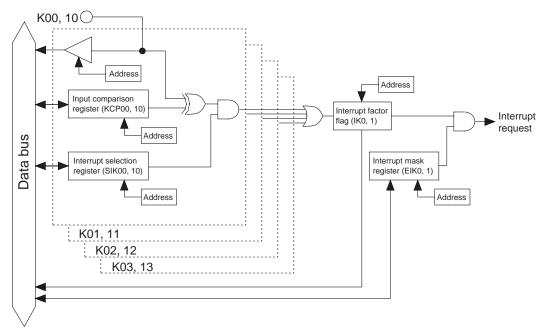

|           | 4.4         | Input Ports (K00–K03 and K10–K13)<br>4.4.1 Configuration of input ports                                                 |        |    |

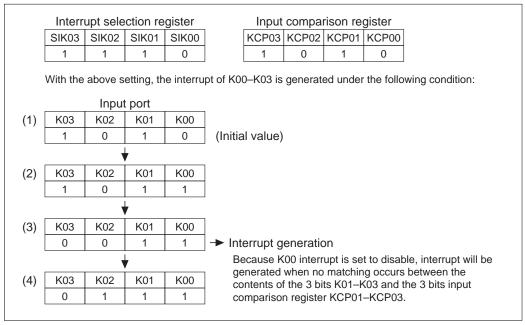

|           |             | 4.4.2 Interrupt function                                                                                                |        |    |

|           |             | 4.4.3 Mask option                                                                                                       |        |    |

|           |             | 4.4.4 I/O memory of input ports                                                                                         | 27     |    |

|           |             | 4.4.5 Programming notes                                                                                                 | 29     |    |

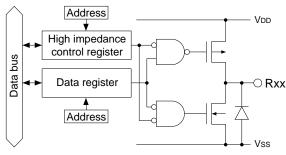

| 4.5  | Output Ports (R00–R03, R10–R13 and R20–R23)              |

|------|----------------------------------------------------------|

|      | 4.5.1 Configuration of output ports                      |

|      | 4.5.2 Mask option                                        |

|      | 4.5.3 High impedance control                             |

|      | 4.5.4 Special output                                     |

|      | 4.5.5 I/O memory of output ports                         |

|      | 4.5.6 Programming notes                                  |

| 4.6  | <i>I/O Ports (P00–P03, P10–P13 and P20–P23)</i>          |

| 4.0  |                                                          |

|      | 4.6.1 Configuration of I/O ports                         |

|      | 4.6.2 Mask option                                        |

|      | 4.6.3 I/O control registers and input/output mode        |

|      | 4.6.4 Pull-up during input mode                          |

|      | 4.6.5 Special outputs (CL, FR)                           |

|      | 4.6.6 I/O memory of I/O ports                            |

|      | 4.6.7 Programming notes                                  |

| 4.7  | LCD Driver (COM0–COM16, SEG0–SEG59)                      |

|      | 4.7.1 Configuration of LCD driver 43                     |

|      | 4.7.2 Power supply for LCD driving                       |

|      | 4.7.3 Mask option                                        |

|      | 4.7.4 LCD display control (ON/OFF) and switching of duty |

|      | 4.7.5 Display memory                                     |

|      | 4.7.6 LCD contrast adjustment 47                         |

|      | 4.7.7 I/O memory of LCD driver                           |

|      | 4.7.8 Programming notes                                  |

| 4.8  | Clock Timer                                              |

|      | 4.8.1 Configuration of clock timer                       |

|      | 4.8.2 Data reading and hold function                     |

|      | 4.8.3 Interrupt function                                 |

|      | 4.8.4 I/O memory of clock timer                          |

|      | 4.8.5 Programming notes                                  |

| 4.9  | Stopwatch Timer                                          |

| 7.7  | 4.9.1 Configuration of stopwatch timer                   |

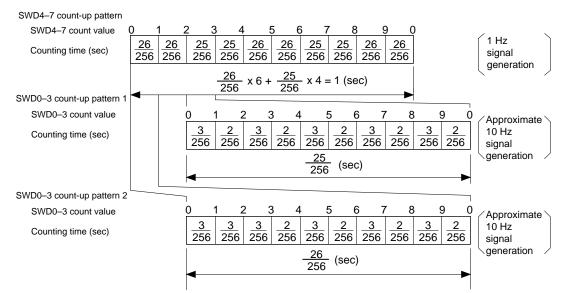

|      | 4.9.2 Count-up pattern                                   |

|      | 4.9.3 Interrupt function                                 |

|      | 4.9.4 I/O memory of stopwatch timer                      |

|      | 4.9.5 Programming notes                                  |

| 4.10 |                                                          |

| 4.10 | Programmable Timer                                       |

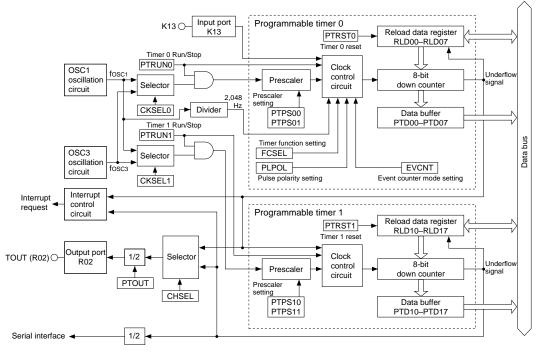

|      | 4.10.1 Configuration of programmable timer               |

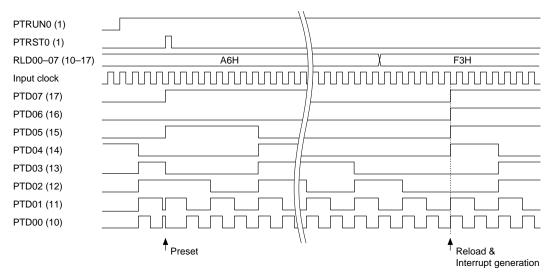

|      | 4.10.2 Setting of initial value and counting down        |

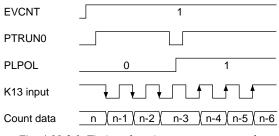

|      | 4.10.3 Counter mode                                      |

|      | 4.10.4 Setting of input clock in timer mode              |

|      | 4.10.5 Interrupt function                                |

|      | 4.10.6 Setting of TOUT output                            |

|      | 4.10.7 Transfer rate setting for serial interface        |

|      | 4.10.8 I/O memory of programmable timer                  |

|      | 4.10.9 Programming notes                                 |

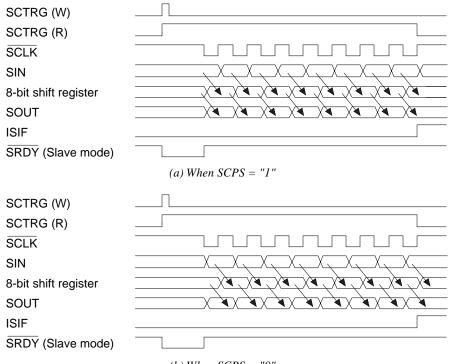

| 4.11 | Serial Interface (SIN, SOUT, SCLK, SRDY)                 |

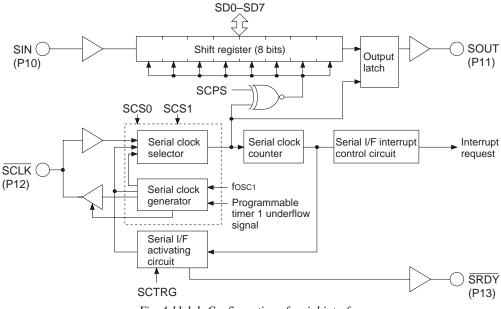

|      | 4.11.1 Configuration of serial interface                 |

|      | 4.11.2 Mask option                                       |

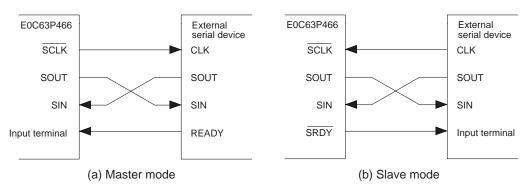

|      | 4.11.3 Master mode and slave mode of serial interface    |

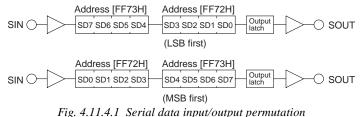

|      | 4.11.4 Data input/output and interrupt function          |

|      | 4.11.5 I/O memory of serial interface                    |

|      | 4.11.6 Programming notes                                 |

#### CONTENTS

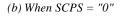

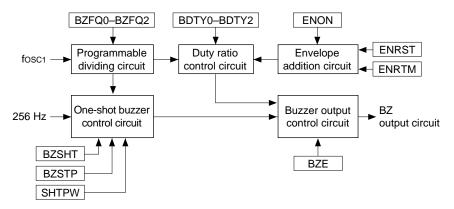

|           | 4.12  | Sound Generator                                                  |     |

|-----------|-------|------------------------------------------------------------------|-----|

|           |       | 4.12.1 Configuration of sound generator                          |     |

|           |       | 4.12.2 Mask option                                               |     |

|           |       | 4.12.3 Control of buzzer output                                  |     |

|           |       | 4.12.4 Setting of buzzer frequency and sound level               |     |

|           |       | 4.12.5 Digital envelope                                          |     |

|           |       | 4.12.6 One-shot output                                           |     |

|           |       | 4.12.7 I/O memory of sound generator<br>4.12.8 Programming notes |     |

|           | 1 1 2 |                                                                  |     |

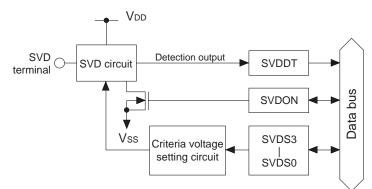

|           | 4.13  | SVD (Supply Voltage Detection) Circuit                           |     |

|           |       | 4.13.1 Configuration of SVD circuit<br>4.13.2 Mask option        |     |

|           |       | 4.13.3 SVD operation                                             |     |

|           |       | 4.13.4 I/O memory of SVD circuit                                 |     |

|           |       | 4.13.5 Programming notes                                         |     |

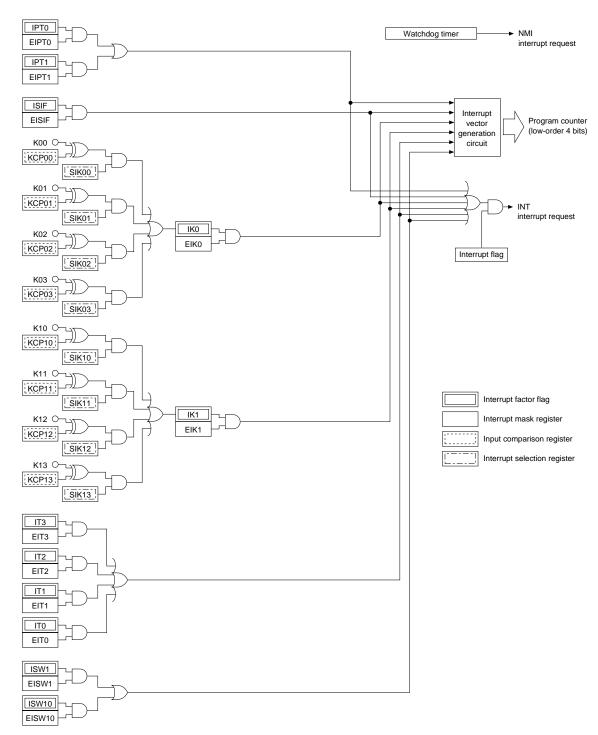

|           | 4.14  | Interrupt and HALT                                               |     |

|           |       | 4.14.1 Interrupt factor                                          |     |

|           |       | 4.14.2 Interrupt mask                                            |     |

|           |       | 4.14.3 Interrupt vector                                          |     |

|           |       | 4.14.4 I/O memory of interrupt                                   |     |

|           |       | 4.14.5 Programming notes                                         |     |

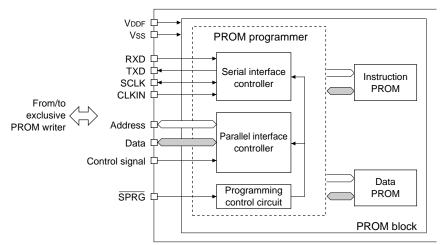

| CHAPTER 5 | PR    | OM PROGRAMMING AND OPERATING MODE                                | 96  |

|           | 5.1   | Configuration of PROM Programmer                                 |     |

|           | 5.2   | Operating Mode                                                   |     |

|           | 0.2   | 5.2.1 Normal operation mode                                      |     |

|           |       | 5.2.2 Serial programming mode                                    |     |

|           |       | 5.2.3 Parallel programming mode                                  |     |

| CHAPTER 6 | Dif   | FERENCES FROM MASK ROM MODELS                                    | 100 |

|           | 6.1   | Mask Option                                                      |     |

|           | 6.2   | Power Supply                                                     |     |

|           | 6.3   | ROM, RAM                                                         |     |

|           | 6.4   | Input/Output Ports and LCD Driver                                |     |

|           | 6.5   | Oscillation Circuit                                              |     |

|           | 6.6   | SVD Circuit                                                      |     |

| CHAPTER 7 | SUN   | amary of Notes                                                   | 104 |

|           | 7.1   | Notes for Low Current Consumption                                |     |

|           | 7.2   | Summary of Notes by Function                                     |     |

|           | 7.3   | Precautions on Mounting                                          |     |

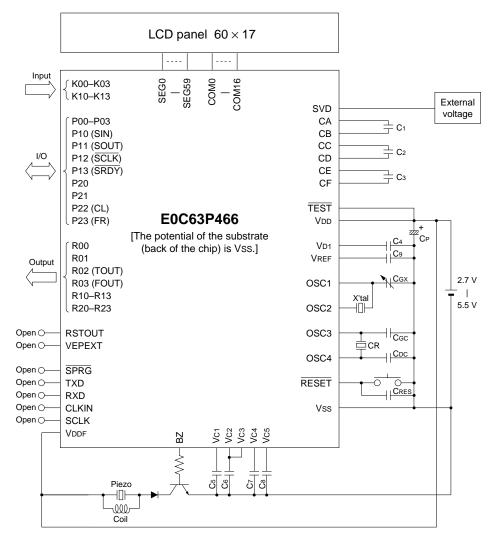

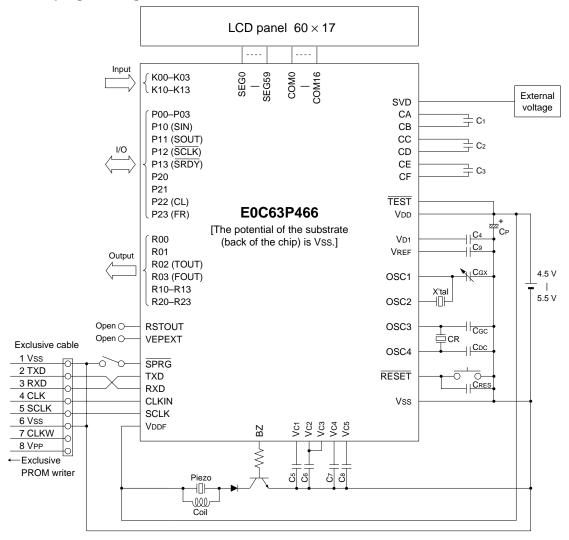

| CHAPTER 8 | BAS   | SIC EXTERNAL WIRING DIAGRAM                                      | 111 |

#### CONTENTS

| CHAPTER 9         | Ele  | ctrical Characteristics                                                                             | 113 |

|-------------------|------|-----------------------------------------------------------------------------------------------------|-----|

|                   | 9.1  | Absolute Maximum Rating                                                                             |     |

|                   | 9.2  | Recommended Operating Conditions                                                                    |     |

|                   | 9.3  | DC Characteristics                                                                                  |     |

|                   | 9.4  | Analog Circuit Characteristics and Power Current Consumption                                        | 115 |

|                   | 9.5  | Oscillation Characteristics                                                                         |     |

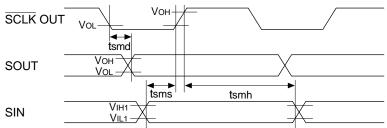

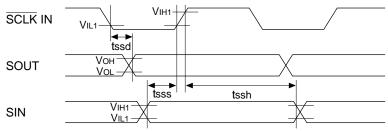

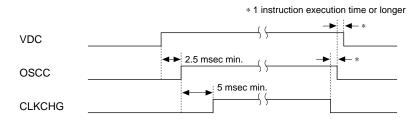

|                   | 9.6  | Serial Interface AC Characteristics                                                                 |     |

|                   | 9.7  | Timing Chart                                                                                        |     |

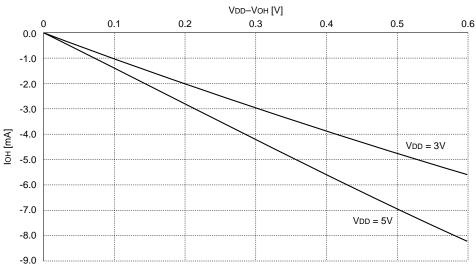

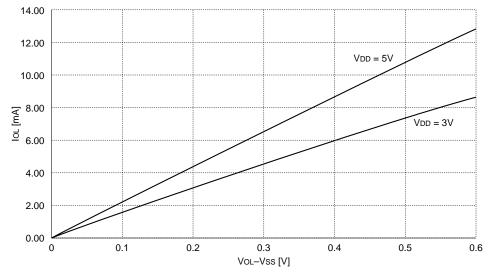

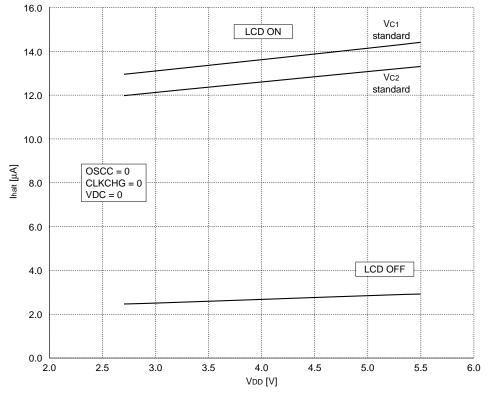

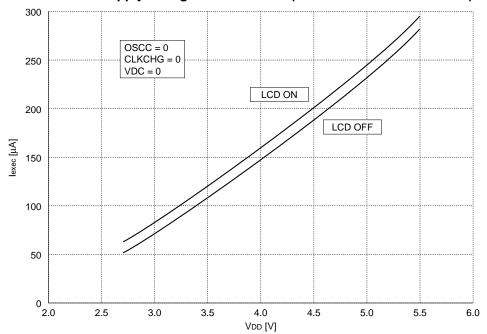

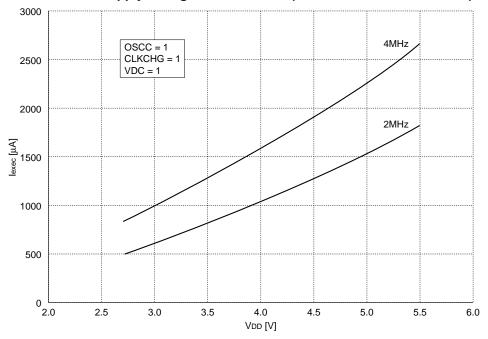

|                   | 9.8  | Characteristics Curves (reference value)                                                            | 120 |

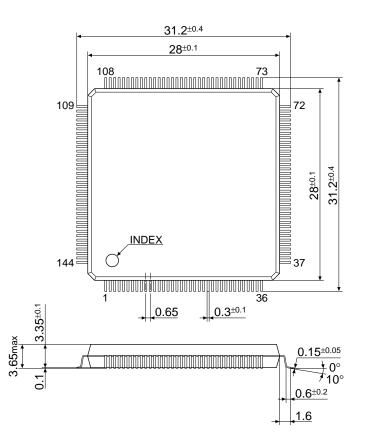

| CHAPTER 10        | PAC  | KAGE                                                                                                | 125 |

|                   |      | Plastic Package                                                                                     |     |

|                   | 10.2 | Ceramic Package for Test Samples                                                                    | 127 |

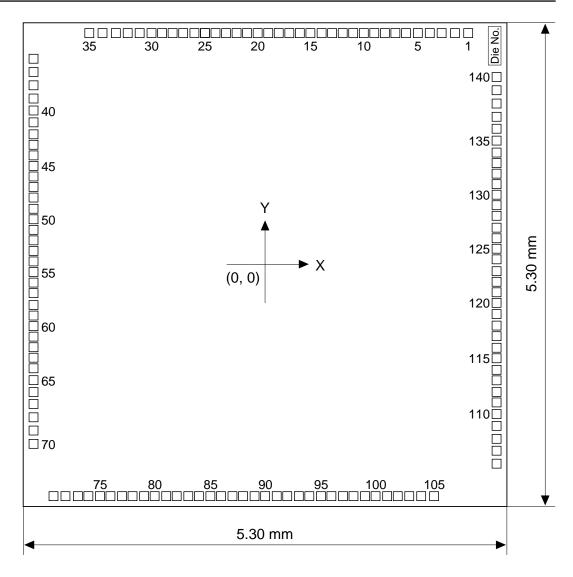

| CHAPTER 11        | PAD  | LAYOUT                                                                                              | 129 |

|                   | 11.1 | Diagram of Pad Layout                                                                               |     |

|                   | 11.2 | Pad Coordinates                                                                                     |     |

| APPENDIX <b>F</b> | PROM | M Programming                                                                                       | 131 |

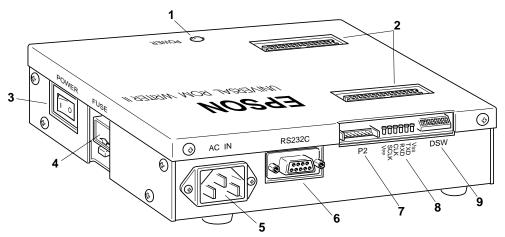

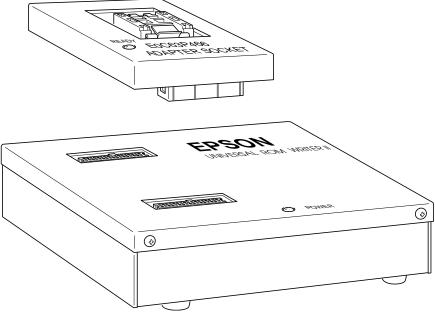

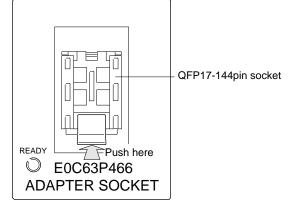

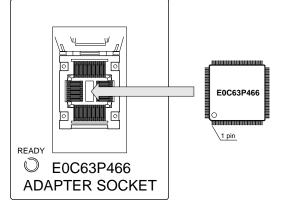

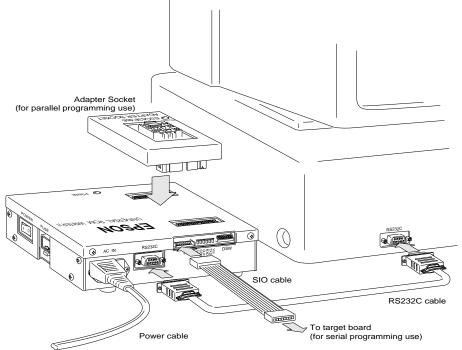

|                   |      | Outline of Writing Tools                                                                            |     |

|                   |      | A.1.1 Universal ROM Writer II                                                                       |     |

|                   |      | A.1.2 Adapter Socket<br>A.1.3 Universal ROM Writer II Control Software                              |     |

|                   | A.2  | System Environment and Connection                                                                   |     |

|                   | 11.2 | A.2.1 System environment                                                                            |     |

|                   |      | A.2.2 RS-232C settings                                                                              |     |

|                   |      | A.2.3 System connection                                                                             |     |

|                   | A.3  | PROM Serial Programming Mode                                                                        |     |

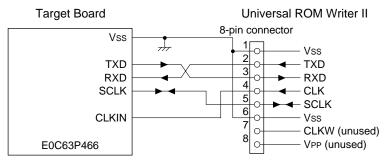

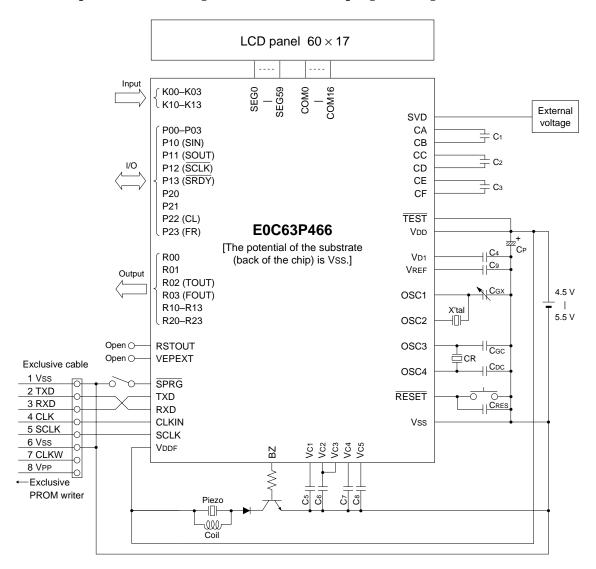

|                   |      | A.3.1 Connecting to target board<br>A.3.2 Sample connection diagram in PROM serial programming mode |     |

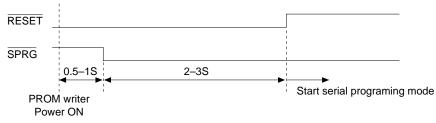

|                   |      | A.3.3 PROM serial programming procedure                                                             |     |

|                   | A.4  | PROM Parallel Programming Mode                                                                      |     |

|                   |      | A.4.1 PROM parallel programming procedure                                                           |     |

|                   | A.5  | Writing Procedure and PROM Writer Command                                                           | 143 |

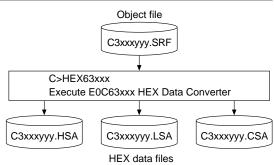

|                   |      | A.5.1 Executing HEX63xxx                                                                            |     |

|                   |      | A.5.2 Writing HEX data (PROM programming)                                                           |     |

|                   |      | A.5.3 PROM writer commands                                                                          |     |

|                   |      | A.5.4 List of commands<br>A.5.5 Error messages                                                      |     |

|                   | A.6  | PROM Programming Notes                                                                              |     |

## CHAPTER 1 OUTLINE

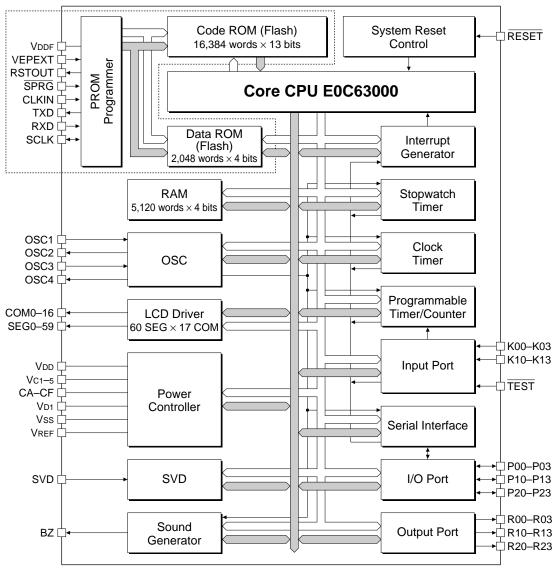

The E0C63P466 is a microcomputer which has a high-performance 4-bit CPU E0C63000 as the core CPU, rewritable ROM (Flash), RAM, dot-matrix LCD driver, serial interface and timers. The E0C63P466 has a built-in large capacity Flash ROM ( $16K \times 13$  bits) and RAM ( $5K \times 4$  bits) that are compatible with the E0C63454, E0C63458 and E0C63466, it can therefore be used as an MTP (Multi-Time Programming) for program development.

## 1.1 Features

| Core CPU                               |                                           |                              | 0                                       |  |  |  |

|----------------------------------------|-------------------------------------------|------------------------------|-----------------------------------------|--|--|--|

| OSC1 oscillation circuit               |                                           |                              |                                         |  |  |  |

|                                        | 4 MHz (Max.) ceramic oscillation circuit  |                              |                                         |  |  |  |

| Instruction set                        |                                           |                              | s with all)                             |  |  |  |

|                                        | Addressing mode: 8 type                   |                              |                                         |  |  |  |

| Instruction execution time             |                                           |                              | 22 µsec 183 µsec                        |  |  |  |

|                                        | During operation at 4 MI                  |                              | 1 μsec 1.5 μsec                         |  |  |  |

| ROM (Flash) capacity                   | Code ROM: 1                               | 16,384 words × 13 b          | its                                     |  |  |  |

|                                        |                                           | 2,048 words $\times$ 4 bits  |                                         |  |  |  |

|                                        | Programming method: 1                     |                              | 0                                       |  |  |  |

|                                        |                                           | (exclusive ROM wr            | iter is used)                           |  |  |  |

|                                        | 0                                         | 100 times (Max.)             |                                         |  |  |  |

| RAM capacity                           | 5                                         | 5,120 words $	imes$ 4 bits   |                                         |  |  |  |

|                                        |                                           | 1,020 bits (240 word         | $ls \times 4$ bits + 60 $\times 1$ bit) |  |  |  |

| Input port                             | 1 1                                       |                              |                                         |  |  |  |

| Output port                            | 1 1                                       | outs are available *1        |                                         |  |  |  |

| I/O port                               |                                           | outs and 4 serial I/C        | ) are available *1)                     |  |  |  |

| Serial interface                       |                                           | nchronous system)            |                                         |  |  |  |

| LCD driver                             |                                           |                              |                                         |  |  |  |

| Time base counter                      | •                                         | *                            |                                         |  |  |  |

| Programmable timer                     | -                                         | , with event counter         | r function                              |  |  |  |

| Watchdog timer                         |                                           |                              |                                         |  |  |  |

| Sound generator                        | -                                         | *                            |                                         |  |  |  |

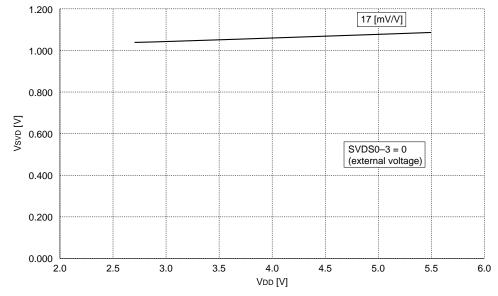

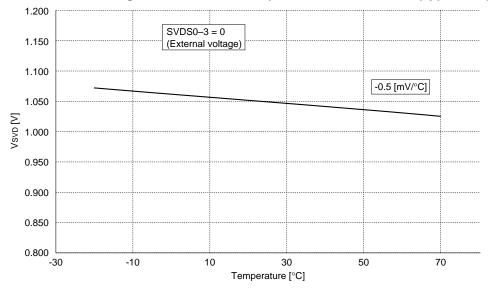

| Supply voltage detection (SVD) circuit | .1 external voltage detecti               | ion level (1.05 V)           |                                         |  |  |  |

|                                        | and 7 internal voltage de                 | tection levels (2.70         | V to 3.30 V)                            |  |  |  |

| External interrupt                     |                                           | 2 systems                    |                                         |  |  |  |

| Internal interrupt                     | -                                         | 4 systems                    |                                         |  |  |  |

|                                        | Stopwatch timer interrup                  |                              |                                         |  |  |  |

|                                        | Programmable timer inte                   |                              |                                         |  |  |  |

|                                        | Serial interface interrupt:               | : 1 system                   |                                         |  |  |  |

| Power supply voltage                   |                                           |                              |                                         |  |  |  |

| Operating temperature range            |                                           |                              |                                         |  |  |  |

| Current consumption (Typ.)             | Single clock (OSC1: Crystal oscillation): |                              |                                         |  |  |  |

|                                        | During HALT (32 kHz                       | (z) $3.0 \text{ V} \pm 10\%$ | 2.5 μA (LCD OFF)                        |  |  |  |

|                                        |                                           | $5.0 \text{ V} \pm 10\%$     | 3.0 µA (LCD OFF)                        |  |  |  |

|                                        | During operation (32                      | kHz) 3.0 V ±10%              | 90 µA                                   |  |  |  |

|                                        |                                           | $5.0 \text{ V} \pm 10\%$     | 300 µA                                  |  |  |  |

|                                        | Twin clock:                               |                              |                                         |  |  |  |

|                                        | During operation (4 N                     |                              | 1 mA                                    |  |  |  |

|                                        |                                           | 5.0 V ±10%                   | 2.3 mA                                  |  |  |  |

| Package                                | . QFP8-144pin (*3), QFP17                 | 7-144pin (plastic *2)        | or chip                                 |  |  |  |

| *1. Can be selected with software *2.  | 129 nin nackaga is not availa             | blo $*2$ , The OED9 1        | 144 nin naakaga daas not                |  |  |  |

\*1: Can be selected with software. \*2: 128-pin package is not available. \*3: The QFP8-144pin package does not support parallel programming using an adapter socket. Only serial programming can be performed.

## 1.2 Block Diagram

Fig. 1.2.1 Block diagram

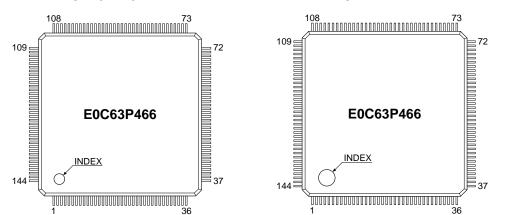

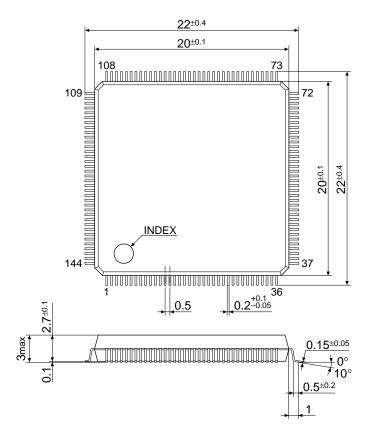

#### QFP8-144pin (Note)

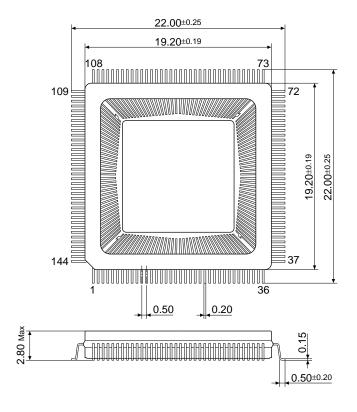

QFP17-144pin

|     |          | Pin name |           |

|-----|----------|----------|-----------|-----|----------|----------|-----------|-----|----------|----------|-----------|-----|----------|----------|-----------|

| No. | E0C63458 | E0C63466 | E0C63P466 |

| 1   | SEG13    | SEG13    | SEG13     | 37  | N.C.     | N.C.     | RXD       | 73  | N.C.     | N.C.     | VDDF      | 109 | N.C.     | N.C.     | RSTOUT    |

| 2   | SEG12    | SEG12    | SEG12     | 38  | N.C.     | N.C.     | TXD       | 74  | SVD      | SVD      | SVD       | 110 | SEG47    | SEG47    | SEG47     |

| 3   | SEG11    | SEG11    | SEG11     | 39  | R23      | R23      | R23       | 75  | VCI      | VCI      | VCI       | 111 | SEG46    | SEG46    | SEG46     |

| 4   | SEG10    | SEG10    | SEG10     | 40  | R22      | R22      | R22       | 76  | Vc2      | VC2      | VC2       | 112 | SEG45    | SEG45    | SEG45     |

| 5   | SEG9     | SEG9     | SEG9      | 41  | R21      | R21      | R21       | 77  | VC3      | VC3      | VC3       | 113 | SEG44    | SEG44    | SEG44     |

| 6   | SEG8     | SEG8     | SEG8      | 42  | R20      | R20      | R20       | 78  | VC4      | VC4      | VC4       | 114 | SEG43    | SEG43    | SEG43     |

| 7   | SEG7     | SEG7     | SEG7      | 43  | R13      | R13      | R13       | 79  | Vc5      | Vc5      | Vc5       | 115 | SEG42    | SEG42    | SEG42     |

| 8   | SEG6     | SEG6     | SEG6      | 44  | R12      | R12      | R12       | 80  | CF       | CF       | CF        | 116 | SEG41    | SEG41    | SEG41     |

| 9   | SEG5     | SEG5     | SEG5      | 45  | R11      | R11      | R11       | 81  | CE       | CE       | CE        | 117 | SEG40    | SEG40    | SEG40     |

| 10  | SEG4     | SEG4     | SEG4      | 46  | R10      | R10      | R10       | 82  | CD       | CD       | CD        | 118 | SEG39    | SEG39    | SEG39     |

| 11  | SEG3     | SEG3     | SEG3      | 47  | R03      | R03      | R03       | 83  | CC       | CC       | CC        | 119 | SEG38    | SEG38    | SEG38     |

| 12  | SEG2     | SEG2     | SEG2      | 48  | R02      | R02      | R02       | 84  | CB       | CB       | CB        | 120 | SEG37    | SEG37    | SEG37     |

| 13  | SEG1     | SEG1     | SEG1      | 49  | R01      | R01      | R01       | 85  | CA       | CA       | CA        | 121 | SEG36    | SEG36    | SEG36     |

| 14  | SEG0     | SEG0     | SEG0      | 50  | R00      | R00      | R00       | 86  | COM8     | COM8     | COM8      | 122 | SEG35    | SEG35    | SEG35     |

| 15  | COM7     | COM7     | COM7      | 51  | P23      | P23      | P23       | 87  | COM9     | COM9     | COM9      | 123 | SEG34    | SEG34    | SEG34     |

| 16  | COM6     | COM6     | COM6      | 52  | P22      | P22      | P22       | 88  | COM10    | COM10    | COM10     | 124 | SEG33    | SEG33    | SEG33     |

| 17  | COM5     | COM5     | COM5      | 53  | P21      | P21      | P21       | 89  | COM11    | COM11    | COM11     | 125 | SEG32    | SEG32    | SEG32     |

| 18  | COM4     | COM4     | COM4      | 54  | P20      | P20      | P20       | 90  | COM12    | COM12    | COM12     | 126 | SEG31    | SEG31    | SEG31     |

| 19  | N.C.     | N.C.     | N.C.      | 55  | P13      | P13      | P13       | 91  | COM13    | COM13    | COM13     | 127 | SEG30    | SEG30    | SEG30     |

| 20  | COM3     | COM3     | COM3      | 56  | P12      | P12      | P12       | 92  | COM14    | COM14    | COM14     | 128 | SEG29    | SEG29    | SEG29     |

| 21  | COM2     | COM2     | COM2      | 57  | P11      | P11      | P11       | 93  | COM15    | COM15    | COM15     | 129 | SEG28    | SEG28    | SEG28     |

| 22  | COM1     | COM1     | COM1      | 58  | P10      | P10      | P10       | 94  | COM16    | COM16    | COM16     | 130 | SEG27    | SEG27    | SEG27     |

| 23  | COM0     | COM0     | COM0      | 59  | P03      | P03      | P03       | 95  | SEG59    | SEG59    | SEG59     | 131 | SEG26    | SEG26    | SEG26     |

| 24  | BZ       | BZ       | BZ        | 60  | P02      | P02      | P02       | 96  | SEG58    | SEG58    | SEG58     | 132 | SEG25    | SEG25    | SEG25     |

| 25  | Vss      | Vss      | Vss       | 61  | P01      | P01      | P01       | 97  | SEG57    | SEG57    | SEG57     | 133 | SEG24    | SEG24    | SEG24     |

| 26  | OSC1     | OSC1     | OSC1      | 62  | P00      | P00      | P00       | 98  | SEG56    | SEG56    | SEG56     | 134 | SEG23    | SEG23    | SEG23     |

| 27  | OSC2     | OSC2     | OSC2      | 63  | K13      | K13      | K13       | 99  | SEG55    | SEG55    | SEG55     | 135 | SEG22    | SEG22    | SEG22     |

| 28  | VD1      | VDI      | VDI       | 64  | K12      | K12      | K12       | 100 | SEG54    | SEG54    | SEG54     | 136 | SEG21    | SEG21    | SEG21     |

| 29  | OSC3     | OSC3     | OSC3      | 65  | K11      | K11      | K11       | 101 | SEG53    | SEG53    | SEG53     | 137 | SEG20    | SEG20    | SEG20     |

| 30  | OSC4     | OSC4     | OSC4      | 66  | K10      | K10      | K10       | 102 | SEG52    | SEG52    | SEG52     | 138 | SEG19    | SEG19    | SEG19     |

| 31  | Vdd      | Vdd      | Vdd       | 67  | K03      | K03      | K03       | 103 | SEG51    | SEG51    | SEG51     | 139 | SEG18    | SEG18    | SEG18     |

| 32  | RESET    | RESET    | RESET     | 68  | K02      | K02      | K02       | 104 | SEG50    | SEG50    | SEG50     | 140 | SEG17    | SEG17    | SEG17     |

| 33  | TEST     | TEST     | TEST      | 69  | K01      | K01      | K01       | 105 | SEG49    | SEG49    | SEG49     | 141 | SEG16    | SEG16    | SEG16     |

| 34  | VREF     | VREF     | VREF      | 70  | K00      | K00      | K00       | 106 | SEG48    | SEG48    | SEG48     | 142 | SEG15    | SEG15    | SEG15     |

| 35  | N.C.     | N.C.     | CLKIN     | 71  | N.C.     | N.C.     | SPRG      | 107 | N.C.     | N.C.     | VEPEXT    | 143 | SEG14    | SEG14    | SEG14     |

| 36  | N.C.     | N.C.     | SCLK      | 72  | N.C.     | N.C.     | N.C.      | 108 | N.C.     | N.C.     | N.C.      | 144 | N.C.     | N.C.     | N.C.      |

Fig. 1.3.1 Pin layout diagram

Notes: • The pin layout diagram of the both package is same.

• The QFP8-144pin package does not support parallel programming using an adapter socket. Only serial programming can be performed.

## 1.4 Pin Description

| Pin name        | Pin No.             | In/Out | Function                                                                |

|-----------------|---------------------|--------|-------------------------------------------------------------------------|

| VDD             | 31                  | _      | Power (+) supply pin                                                    |

| Vss             | 25                  | _      | Power (–) supply pin                                                    |

| V <sub>D1</sub> | 28                  | _      | Oscillation/internal logic system regulated voltage output pin          |

| VC1–VC5         | 75–79               | _      | LCD system power supply pin (1/4 bias generated internally)             |

| Vref            | 34                  | 0      | LCD system power supply testing pin                                     |

| CA–CF           | 85-80               | _      | LCD system boosting/reducing capacitor connecting pin                   |

| OSC1            | 26                  | Ι      | Crystal oscillation input pin                                           |

| OSC2            | 27                  | 0      | Crystal oscillation output pin                                          |

| OSC3            | 29                  | Ι      | Ceramic oscillation input pin                                           |

| OSC4            | 30                  | 0      | Ceramic oscillation output pin                                          |

| K00-K03         | 70–67               | Ι      | Input port                                                              |

| K10, K11        | 66,65               | Ι      | Input port                                                              |

| K12             | 64                  | Ι      | Input port                                                              |

| K13             | 63                  | Ι      | Input port                                                              |

| P00-P03         | 62–59               | I/O    | I/O port                                                                |

| P10-P13         | 58–55               | I/O    | I/O port (switching to serial I/F input/output is possible by software) |

| P20             | 54                  | I/O    | I/O port                                                                |

| P21             | 53                  | I/O    | I/O port                                                                |

| P22             | 52                  | I/O    | I/O port (switching to CL signal output is possible by software)        |

| P23             | 51                  | I/O    | I/O port (switching to FR signal output is possible by software)        |

| R00             | 50                  | 0      | Output port                                                             |

| R01             | 49                  | 0      | Output port                                                             |

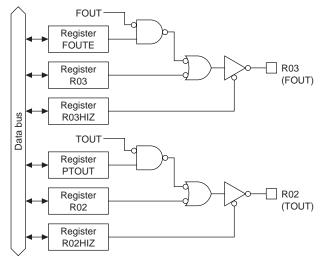

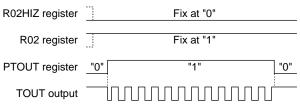

| R02             | 48                  | 0      | Output port(switching to TOUT signal output is possible by software)    |

| R03             | 47                  | 0      | Output port(switching to FOUT signal output is possible by software)    |

| R10-R13         | 46–43               | 0      | Output port                                                             |

| R20-R23         | 42–39               | 0      | Output port                                                             |

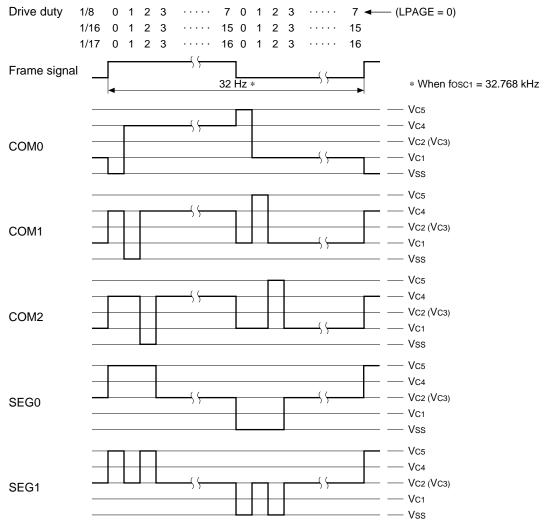

| COM0, COM1      | 23,22               | 0      | LCD common output pin                                                   |

| COM2–COM14      | 21,20,18-15,86-92   |        | (1/8, 1/16, 1/17 duty can be selected by software)                      |

| COM15, COM16    | 93,94               |        |                                                                         |

| SEG0-SEG59      | 14-1,143-110,106-95 | 0      | LCD segment output pin                                                  |

| BZ              | 24                  | 0      | Sound output pin                                                        |

| SVD             | 74                  | Ι      | SVD external voltage input pin                                          |

| RESET           | 32                  | Ι      | Initial reset input pin                                                 |

| TEST            | 33                  | Ι      | Testing input pin                                                       |

| TXD             | 38                  | 0      | Serial data output pin for Flash programming                            |

| RXD             | 37                  | Ι      | Serial data input pin for Flash programming                             |

| SCLK            | 36                  | I/O    | Serial clock input/output pin for Flash programming                     |

| CLKIN           | 35                  | Ι      | Clock input pin for Flash programming                                   |

| SPRG            | 71                  | Ι      | Flash programming control pin                                           |

| RSTOUT          | 109                 | 0      | Flash test pin (N.C. in normal operation)                               |

| VDDF            | 73                  | _      | Flash power (+) supply pin (connect to VDD in normal operation)         |

| VEPEXT          | 107                 | I/O    | Flash test pin (N.C. in normal operation)                               |

Table 1.4.1 Pin description

## 1.5 Mask Option

The mask options provided for the E0C63454/63458/63466 are fixed as follows in the E0C63P466, so they cannot be selected.

| Mask option                          |             | Setting                            |  |

|--------------------------------------|-------------|------------------------------------|--|

| OSC1 oscillation circuit             |             | Crystal oscillation (32.768 kHz)   |  |

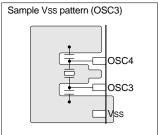

| OSC3 oscillation circuit             |             | Use <ceramic> or Not use</ceramic> |  |

| Multiple key entry reset combinati   | on          | Not use                            |  |

| Multiple key entry reset time author | orization   | Not use                            |  |

| Input port pull-up resistor          | K00         | With pull-up resistor              |  |

|                                      | K01         | With pull-up resistor              |  |

|                                      | K02         | With pull-up resistor              |  |

|                                      | K03         | With pull-up resistor              |  |

|                                      | K10         | With pull-up resistor              |  |

|                                      | K11         | With pull-up resistor              |  |

|                                      | K12         | With pull-up resistor              |  |

|                                      | K13         | With pull-up resistor              |  |

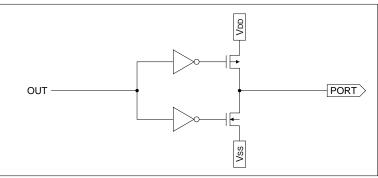

| Output port specification            | R00         | Complementary                      |  |

|                                      | R01         | Complementary                      |  |

|                                      | R02         | Complementary                      |  |

|                                      | R03         | Complementary                      |  |

|                                      | R1x         | Complementary                      |  |

|                                      | R2x         | Complementary                      |  |

| I/O port specification               | P0x         | Complementary                      |  |

|                                      | P1x         | Complementary                      |  |

|                                      | P20         | Complementary                      |  |

|                                      | P21         | Complementary                      |  |

|                                      | P22         | Complementary                      |  |

|                                      | P23         | Complementary                      |  |

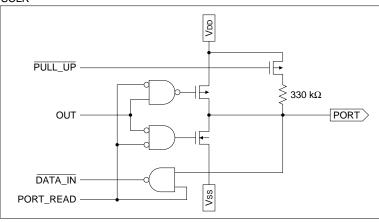

| I/O port pull-up resistor            | P0x         | With pull-up resistor              |  |

|                                      | P1x         | With pull-up resistor              |  |

|                                      | P20         | With pull-up resistor              |  |

|                                      | P21         | With pull-up resistor              |  |

| P                                    |             | With pull-up resistor              |  |

| P23                                  |             | With pull-up resistor              |  |

| LCD drive power                      |             | Internal power supply              |  |

| Serial interface polarity            |             | Negative polarity                  |  |

| SVD circuit external voltage detec   |             | Use                                |  |

| Sound generator buzzer output spe    | ecification | Positive polarity                  |  |

Table 1.5.1 E0C63P466 mask option configuration

## **CHAPTER 2** Power Supply and Initial Reset

## 2.1 Power Supply

The E0C63P466 operating power voltage is as follows:

| Table 2.1.1 Operating power voltage    |             |  |  |  |  |  |

|----------------------------------------|-------------|--|--|--|--|--|

| Operating mode Operating power voltage |             |  |  |  |  |  |

| MCU normal operation mode              | 2.7 V–5.5 V |  |  |  |  |  |

| PROM programming mode                  | 5.0 V ±10%  |  |  |  |  |  |

The E0C63P466 operates by applying a single power supply within the above range between VDD/VDDF and Vss. The E0C63P466 generates the voltage necessary for all the internal circuits by the built-in power supply circuits shown in Table 2.1.2. Supply the same voltage level as VDD to the VDDF terminal from outside the IC.

| Table 2.1.2 | Power suppl | y circuits |

|-------------|-------------|------------|

|-------------|-------------|------------|

| Circuit             | Power supply circuit                 | Output voltage |

|---------------------|--------------------------------------|----------------|

| Oscillation circuit | Oscillation system voltage regulator | VD1            |

| LCD driver          | LCD system voltage circuit           | VC1–VC5        |

Notes: • Do not drive external loads with the output voltage from the internal power supply circuits.

- The internal LCD system voltage circuit (1/4 bias) is always used in the E0C63P466, connect between Vc3 and Vc2 terminals.

- See Chapter 9, "Electrical Characteristics", for voltage values and drive capability.

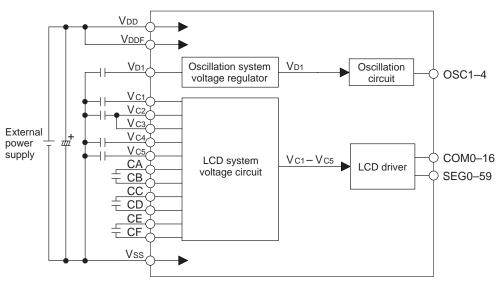

Fig. 2.1.1 Configuration of power supply

## 2.1.1 Voltage <VD1> for oscillation circuit

VD1 is the operating voltage for the oscillation circuit, and is generated by the oscillation system voltage regulator for stabilizing the oscillation.

In the E0C63454/63458/63466, it is necessary to switch the VD1 voltage level according to the oscillation circuit and operating frequency by controlling the voltage regulator. In the E0C63P466, the VD1 voltage level is fixed, so software control for switching the VD1 level does not affect the actual output voltage. Refer to Chapter 6, "Differences from Mask ROM Models", for details.

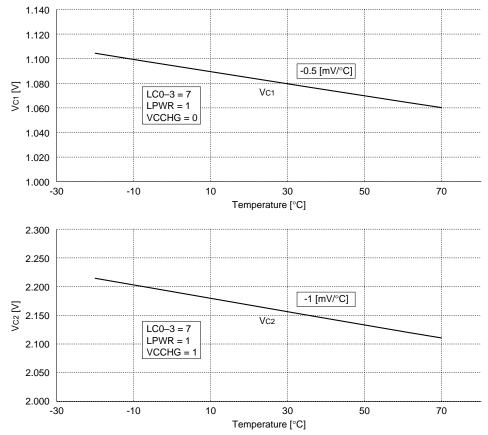

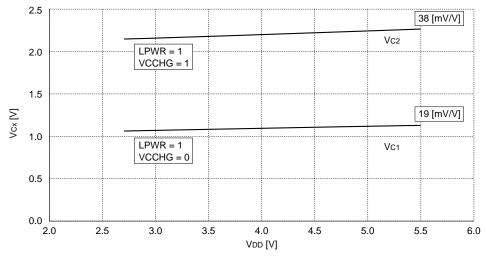

## 2.1.2 Voltage <VC1-VC5> for LCD driving

VC1–VC5 are the LCD drive voltages generated by the LCD system voltage circuit. The built-in LCD system voltage circuit generates four voltages (1/4 bias) VC1, VC2, VC4 and VC5 (excluding VC3). These four output voltages can only be supplied to the externally expanded LCD driver.

The LCD system voltage circuit generates VC1 or VC2 with the voltage regulator built-in, and generates three other voltages by boosting or reducing the voltage of VC1 or VC2. Table 2.1.2.1 shows the VC1, VC2, VC4 and VC5 voltage values and boost/reduce status.

|                   | 0                 |                     |

|-------------------|-------------------|---------------------|

| LCD drive voltage | Vc1 standard      | Vc2 standard        |

| Vc1 (0.975–1.2 V) | VC1 (regulated)   | $1/2 \times V_{C2}$ |

| Vc2 (1.950-2.4 V) | $2 \times V_{C1}$ | VC2 (regulated)     |

| Vc4 (2.925-3.6 V) | 3 × Vc1           | $3/2 \times V_{C2}$ |

| Vc5 (3.900-4.8 V) | $4 \times V_{C1}$ | $2 \times V_{C2}$   |

Table 2.1.2.1 LCD drive voltage when generated internally

Note: The LCD drive voltage can be adjusted by the software (see Section 4.7.6). Values in the above table are typical values.

Either the VC1 or VC2 used for the standard is selected according to the supply voltage by the software. In the E0C63P466, either can be selected regardless of the supply voltage level since the minimum operating voltage is 2.7 V.

The VC2 standard improves the display quality and reduces current consumption, note, however, the VC1 standard must be set in the mask ROM model if the power supply voltage VDD is 2.6 V or less. Refer to Section 4.7, "LCD Driver", for control of the LCD drive voltage.

## 2.2 Initial Reset

To initialize the E0C63P466 circuits, initial reset must be executed. The E0C63P466 supports the initial reset factor below.

External initial reset by the RESET terminal

When the power is turned on, be sure to initialize using the reset function. It is not guaranteed that the circuits are initialized by only turning the power on.

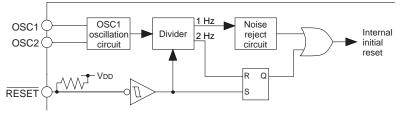

Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1 Configuration of initial reset circuit

## 2.2.1 Reset terminal (RESET)

Initial reset can be executed externally by setting the reset terminal to a low level (VSS). After that the initial reset is released by setting the reset terminal to a high level (VDD) and the CPU starts operation. The reset input signal is maintained by the RS latch and becomes the internal initial reset signal. The RS latch is designed to be released by a 2 Hz signal (high) that is divided by the OSC1 clock. Therefore in normal operation, a maximum of 250 msec (when fOSC1 = 32.768 kHz) is needed until the internal initial reset is released after the reset terminal goes to high level. Be sure to maintain a reset input of 0.1 msec or more.

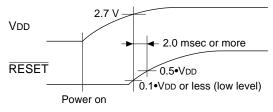

However, when turning the power on, the reset terminal should be set at a low level as in the timing shown in Figure 2.2.1.1.

Fig. 2.2.1.1 Initial reset at power on

The reset terminal should be set to  $0.1 \cdot \text{VDD}$  or less (low level) until the supply voltage becomes 2.7 V or more. After that, a level of  $0.5 \cdot \text{VDD}$  or less should be maintained more than 2.0 msec.

In the E0C63P466, a low level input to the reset terminal initializes some analog circuits as well as the internal logic. At this time, 10  $\mu$ A or more current is consumed as the bias current.

### 2.2.2 Internal register at initial resetting

Initial reset initializes the CPU as shown in Table 2.2.2.1.

The registers and flags which are not initialized by initial reset should be initialized in the program if necessary.

In particular, the stack pointers SP1 and SP2 must be set as a pair because all the interrupts including NMI are masked after initial reset until both the SP1 and SP2 stack pointers are set with software. When data is written to the EXT register, the E flag is set and the following instruction will be executed in the extended addressing mode.

If an instruction which does not permit extended operation is used as the following instruction, the operation is not guaranteed. Therefore, do not write data to the EXT register for initialization only. Refer to the "E0C63000 Core CPU Manual" for extended addressing and usable instructions.

|                            | CPU core   |                |               |  |  |  |  |  |  |

|----------------------------|------------|----------------|---------------|--|--|--|--|--|--|

| Name                       | Symbol     | Number of bits | Setting value |  |  |  |  |  |  |

| Data register A            | А          | 4              | Undefined     |  |  |  |  |  |  |

| Data register B            | В          | 4              | Undefined     |  |  |  |  |  |  |

| Extension register EXT     | EXT        | 8              | Undefined     |  |  |  |  |  |  |

| Index register X           | Х          | 16             | Undefined     |  |  |  |  |  |  |

| Index register Y           | Y          | 16             | Undefined     |  |  |  |  |  |  |

| Program counter            | PC         | 16             | 0110H         |  |  |  |  |  |  |

| Stack pointer SP1          | SP1        | 8              | Undefined     |  |  |  |  |  |  |

| Stack pointer SP2          | SP2        | 8              | Undefined     |  |  |  |  |  |  |

| Zero flag                  | Z          | 1              | Undefined     |  |  |  |  |  |  |

| Carry flag                 | С          | 1              | Undefined     |  |  |  |  |  |  |

| Interrupt flag             | Ι          | 1              | 0             |  |  |  |  |  |  |

| Extension flag             | Е          | 1              | 0             |  |  |  |  |  |  |

| Queue register             | Q          | 16             | Undefined     |  |  |  |  |  |  |

|                            |            |                |               |  |  |  |  |  |  |

|                            | Peripheral | circuits       |               |  |  |  |  |  |  |

| Name                       | Nu         | mber of bits   | Setting value |  |  |  |  |  |  |

| RAM                        |            | 4              | Undefined     |  |  |  |  |  |  |

| Display memory             |            | 4              | Undefined     |  |  |  |  |  |  |

| Other pheripheral circuits |            | _              | *             |  |  |  |  |  |  |

Table 2.2.2.1 Initial values

\* See Section 4.1, "Memory Map".

#### 2.2.3 Terminal settings at initial resetting

The output port (R) terminals and I/O port (P) terminals are shared with special output terminals and input/output terminals of the serial interface. These functions are selected by the software. At initial reset, these terminals are set to the general purpose output port terminals and I/O port terminals. Set them according to the system in the initial routine. In addition, take care of the initial status of output terminals when designing a system.

Table 2.2.3.1 shows the list of the shared terminal settings.

| Terminal | Terminal status           |      | Special | output | Seria | al I/F  |         |

|----------|---------------------------|------|---------|--------|-------|---------|---------|

| name     | at initial reset          | TOUT | FOUT    | CL     | FR    | Master  | Slave   |

| R00      | R00 (High output)         |      |         |        |       |         |         |

| R01      | R01 (High output)         |      |         |        |       |         |         |

| R02      | R02 (High output)         | TOUT |         |        |       |         |         |

| R03      | R03 (High output)         |      | FOUT    |        |       |         |         |

| R10-R13  | R10–R13 (High output)     |      |         |        |       |         |         |

| R20-R23  | R20–R23 (High output)     |      |         |        |       |         |         |

| P00-P03  | P00-P03 (Input & Pull-up) |      |         |        |       |         |         |

| P10      | P10 (Input & Pull-up)     |      |         |        |       | SIN(I)  | SIN(I)  |

| P11      | P11 (Input & Pull-up)     |      |         |        |       | SOUT(O) | SOUT(O) |

| P12      | P12 (Input & Pull-up)     |      |         |        |       | SCLK(O) | SCLK(I) |

| P13      | P13 (Input & Pull-up)     |      |         |        |       |         | SRDY(O) |

| P20      | P20 (Input & Pull-up)     |      |         |        |       |         |         |

| P21      | P21 (Input & Pull-up)     |      |         |        |       |         |         |

| P22      | P22 (Input & Pull-up)     |      |         | CL     |       |         |         |

| P23      | P23 (Input & Pull-up)     |      |         |        | FR    |         |         |

Table 2.2.3.1 List of shared terminal settings

For setting procedure of the functions, see explanations for each of the peripheral circuits.

## 2.3 Test Terminal ( $\overline{TEST}$ )

This is the terminal used for the factory inspection of the IC. During normal operation, connect the  $\overline{\text{TEST}}$  terminal to VDD.

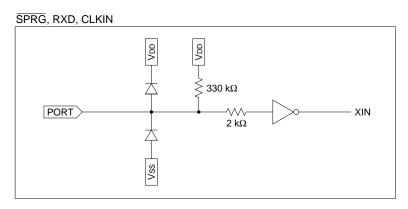

## 2.4 Terminals for Flash EEPROM

The E0C63P466 has the following terminals used for writing data to the Flash EEPROM and for factory testing.

VDDF: Power supply (+) terminal for Flash EEPROM

SPRG: Flash EEPROM programming control terminal

SCLK: Clock input/output terminal for Flash EEPROM serial programming

RXD: Data input terminal for Flash EEPROM serial programming

TXD: Data output terminal for Flash EEPROM serial programming

CLKIN: Flash EEPROM write-control clock input terminal

RSTOUT: Test-signal monitor terminal

VEPEXT: Test-signal monitor terminal

The above terminals should be set up according to the operating mode. Refer to Chapter 5, "PROM Programmer and Operating Mode", for details.

## CHAPTER 3 CPU, ROM, RAM

## 3.1 CPU

The E0C63P466 has a 4-bit core CPU E0C63000 built-in as its CPU part. Refer to the "E0C63000 Core CPU Manual" for the E0C63000.

Note: The SLP instruction cannot be used because the SLEEP operation is not assumed in the E0C63P466.

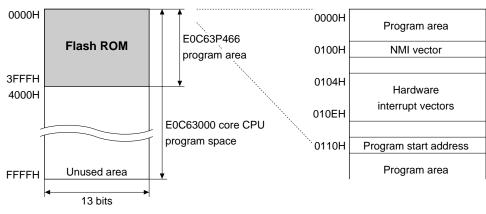

## 3.2 Code ROM

The built-in code ROM is a Flash ROM for loading programs, and has a capacity of 16,384 steps  $\times$  13 bits. The core CPU can linearly access the program space up to step FFFFH from step 0000H, however, the program area of the E0C63P466 is step 0000H to step 3FFFH. The program start address after initial reset is assigned to step 0110H. The non-maskable interrupt (NMI) vector and hardware interrupt vectors are allocated to step 0100H and steps 0104H–010EH, respectively.

Fig. 3.2.1 Configuration of code ROM

## 3.3 RAM

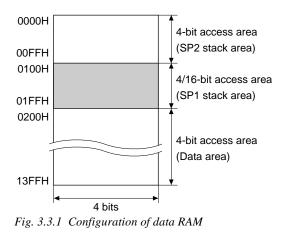

The RAM is a data memory for storing various kinds of data, and has a capacity of  $5,120 \text{ words} \times 4 \text{ bits}$ . The RAM area is assigned to addresses 0000H to 13FFH on the data memory map. Addresses 0100H to 01FFH are 4-bit/16-bit data accessible areas and in other areas it is only possible to access 4-bit data. When programming, keep the following points in mind.

- (1) Part of the RAM area is used as a stack area for subroutine call and register evacuation, so pay attention not to overlap the data area and stack area.

- (2) The E0C63000 core CPU handles the stack using the stack pointer for 4-bit data (SP2) and the stack pointer for 16-bit data (SP1).

16-bit data are accessed in stack handling by SP1, therefore, this stack area should be allocated to the area where 4-bit/16-bit access is possible (0100H to 01FFH). The stack pointers SP1 and SP2 change cyclically within their respective range: the range of SP1 is 0000H to 03FFH and the range of SP2 is 0000H to 00FFH. Therefore, pay attention to the SP1 value because it may be set to 0200H or more exceeding the 4-bit/16-bit accessible range in the E0C63P466 or it may be set to 00FFH or less. Memory accesses except for stack operations by SP1 are 4-bit data access.

After initial reset, all the interrupts including NMI are masked until both the stack pointers SP1 and SP2 are set by software. Further, if either SP1 or SP2 is re-set when both are set already, the interrupts including NMI are masked again until the other is re-set. Therefore, the settings of SP1 and SP2 must be done as a pair.

#### CHAPTER 3: CPU, ROM, RAM

(3) Subroutine calls use 4 words (for PC evacuation) in the stack area for 16-bit data (SP1). Interrupts use 4 words (for PC evacuation) in the stack area for 16-bit data (SP1) and 1 word (for F register evacuation) in the stack area for 4-bit data.

## 3.4 Data ROM

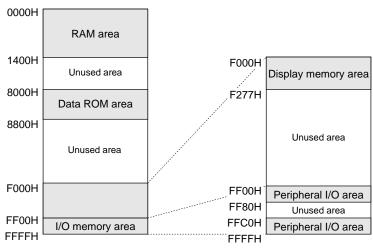

The data ROM is a Flash ROM for loading various static data such as a character generator, and has a capacity of 2,048 words  $\times$  4 bits. The data ROM is assigned to addresses 8000H to 87FFH on the data memory map, and the data can be read using the same data memory access instructions as the RAM.

## CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

The peripheral circuits of E0C63P466 (timer, I/O, etc.) are interfaced with the CPU in the memory mapped I/O method. Thus, all the peripheral circuits can be controlled by accessing the I/O memory on the memory map using the memory operation instructions. The following sections explain the detailed operation of each peripheral circuit.

## 4.1 Memory Map

The E0C63P466 data memory consists of 5,120-word RAM, 2,048-word data ROM, 1,020-bit display memory and 67-word peripheral I/O memory. Figure 4.1.1 shows the overall memory map of the E0C63P466, and Tables 4.1.1(a)–(e) the peripheral circuits' (I/O space) memory maps.

Fig. 4.1.1 Memory map

Note: Memory is not implemented in unused areas within the memory map. Further, some non-implementation areas and unused (access prohibition) areas exist in the display memory area and the peripheral I/O area. If the program that accesses these areas is generated, its operation cannot be guaranteed. Refer to Section 4.7.5, "Display memory", for the display memory, and the I/O memory maps shown in Tables 4.1.1 (a)–(e) for the peripheral I/O area.

|         |        | Rea    | ister  |        |                |         |                  |                    | (p(rr00n-rr51n)                                                                             |  |

|---------|--------|--------|--------|--------|----------------|---------|------------------|--------------------|---------------------------------------------------------------------------------------------|--|

| Address | D3     | D2     | D1     | D0     | Name           | Init *1 | 1                | 0                  | Comment                                                                                     |  |

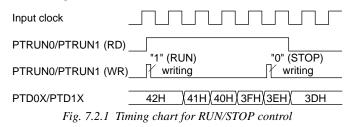

|         | CLKCHG | OSCC   | 0      | VDC    | CLKCHG         | 0       | OSC3             | OSC1               | CPU clock switch                                                                            |  |

| FF00H   | CLKCHG | USCC   | 0      | VDC    | OSCC           | 0       | On               | Off                | OSC3 oscillation On/Off                                                                     |  |

| 110011  | R/     | w      | R      | R/W    | 0 *3           | _ *2    |                  |                    | Unused                                                                                      |  |

|         |        |        | Ň      | 10.00  | VDC            | 0       | 1                | 0                  | CPU operating voltage switch                                                                |  |

|         | SVDS3  | SVDS2  | SVDS1  | SVDS0  | SVDS3          | 0       |                  |                    | SVD criteria voltage setting<br>[SVDS3–0] 0 1 2 3 4 5 6 7                                   |  |

| FF04H   |        |        |        |        | SVDS2<br>SVDS1 | 0<br>0  |                  |                    | Voltage(V) 1.05(Ext)                                                                        |  |

|         |        | R      | /W     |        | SVDS1<br>SVDS0 | 0       |                  |                    | [SVDS3-0] 8 9 10 11 12 13 14 15                                                             |  |

|         |        |        |        |        | 0 *3           | _ *2    |                  |                    | ⊥ Voltage(V) – – 2.80 2.90 3.00 3.10 3.20 3.30<br>Unused                                    |  |

|         | 0      | 0      | SVDDT  | SVDON  | 0 *3           | _ *2    |                  |                    | Unused                                                                                      |  |

| FF05H   |        |        | 1      |        | SVDDT          | 0       | Low              | Normal             | SVD evaluation data                                                                         |  |

|         |        | R      |        | R/W    | SVDON          | 0       | On               | Off                | SVD circuit On/Off                                                                          |  |

|         | FOUTE  | 0      | 50501  | 50500  | FOUTE          | 0       | Enable           | Disable            | FOUT output enable                                                                          |  |

| FF06H   | FOUTE  | 0      | FOFQ1  | FOFQ0  | 0 *3           | _ *2    |                  |                    | Unused                                                                                      |  |

| FFUOR   | R/W    | R      | р      | W      | FOFQ1          | 0       |                  |                    | FOUT [FOFQ1, 0] 0 1 2 3                                                                     |  |

|         | R/W    | ĸ      | R/     | /vv    | FOFQ0          | 0       |                  |                    | selection Frequency fosci/64 fosci/8 fosci fosca                                            |  |

|         | 0      | 0      | WDEN   | WDRST  | 0 *3           | _ *2    |                  |                    | Unused                                                                                      |  |

| FF07H   |        | •      | WDEN   | WDIG1  | 0 *3           | _ *2    |                  | <u>.</u>           | Unused                                                                                      |  |

|         | F      | 2      | R/W    | w      | WDEN           | 1       | Enable           | Disable            | Watchdog timer enable                                                                       |  |

|         |        |        |        |        | WDRST*3        | Reset   | Reset            | Invalid            | Watchdog timer reset (writing)                                                              |  |

|         | SIK03  | SIK02  | SIK01  | SIK00  | SIK03<br>SIK02 | 0<br>0  | Enable<br>Enable | Disable<br>Disable |                                                                                             |  |

| FF20H   |        |        |        |        | SIK02          | 0       | Enable           | Disable            | K00-K03 interrupt selection register                                                        |  |

|         |        | R      | W/W    |        | SIKO           | 0       | Enable           | Disable            |                                                                                             |  |

|         |        |        |        |        | K03            | - *2    | High             | Low                |                                                                                             |  |

|         | K03    | K02    | K01    | K00    | K02            | _ *2    | High             | Low                |                                                                                             |  |

| FF21H   |        |        |        |        | K01            | _ *2    | High             | Low                | K00–K03 input port data                                                                     |  |

|         |        | I      | 2      |        | K00            | - *2    | High             | Low                |                                                                                             |  |

|         | KCP03  | KCD02  | KCD01  | KCP00  | KCP03          | 1       | Ţ                | <u> </u>           |                                                                                             |  |

| FF22H   | KCP03  | KCP02  | KCP01  | KCP00  | KCP02          | 1       |                  | ſ                  | K00–K03 input comparison register                                                           |  |

| 112211  |        | R      | /W     |        | KCP01          | 1       | Ţ                | Ī                  |                                                                                             |  |

|         |        |        |        | 1      | KCP00          | 1       | <u>+</u>         | <u> </u>           |                                                                                             |  |

|         | SIK13  | SIK12  | SIK11  | SIK10  | SIK13<br>SIK12 | 0<br>0  | Enable<br>Enable | Disable<br>Disable |                                                                                             |  |

| FF24H   |        |        |        |        | SIK12          | 0       | Enable           | Disable            | K10-K13 interrupt selection register                                                        |  |

|         |        | R      | W/W    |        | SIK10          | 0       | Enable           | Disable            |                                                                                             |  |

|         |        |        |        |        | K13            | - *2    | High             | Low                |                                                                                             |  |

|         | K13    | K12    | K11    | K10    | K12            | _ *2    | High             | Low                |                                                                                             |  |

| FF25H   |        |        |        | 1      | K11            | _ *2    | High             | Low                | K10–K13 input port data                                                                     |  |

|         |        | ł      | 2      |        | K10            | - *2    | High             | Low                |                                                                                             |  |

|         | KCP13  | KCP12  | KCP11  | KCD10  | KCP13          | 1       | ┍╸┙              | 1                  |                                                                                             |  |

| FF26H   | KCP13  | KUP 12 | KCPTT  | KCP10  | KCP12          | 1       | Ţ                | ſ                  | K10–K13 input comparison register                                                           |  |

| 112011  |        | R      | /W     |        | KCP11          | 1       | Ţ                |                    |                                                                                             |  |

|         |        |        |        |        | KCP10          | 1       | <u> </u>         | _ <u>_</u>         |                                                                                             |  |

|         |        |        |        |        | R03HIZ         | 0       | High-Z           | Output             | R03 output high impedance control (FOUTE=0)                                                 |  |

|         | R03HIZ | R02HIZ | R01HIZ | R00HIZ |                | 0       | Lliah 7          | Output             | FOUT output high impedance control (FOUTE=1)<br>R02 output high impedance control (PTOUT=0) |  |

| FF30H   |        |        |        |        | R02HIZ         | 0       | High-Z           | Output             | TOUT output high impedance control (PTOUT=0)                                                |  |

|         |        | Л      | /W     |        | R01HIZ         | 0       | High-Z           | Output             | R01 output high impedance control                                                           |  |

|         |        | R      | ٧V     |        | R00HIZ         | 0       | High-Z           | Output             | R00 output high impedance control                                                           |  |

|         |        |        |        |        | R03            | 1       | High             | Low                | R03 output port data (FOUTE=0) Fix at "1" when FOUT is used                                 |  |

|         | R03    | R02    | R01    | R00    | R02            | 1       | High             | Low                | R02 output port data (PTOUT=0) Fix at "1" when TOUT is used                                 |  |

| FF31H   |        |        |        | 1      | R01            | 1       | High             | Low                | R01 output port data                                                                        |  |

|         |        | R      | W      |        | R00            | 1       | High             | Low                | R00 output port data                                                                        |  |

| Table 4.1.1  | (a) | I/0 | memorv | тар  | (FF00H- | FF31H) |

|--------------|-----|-----|--------|------|---------|--------|

| 100000 11111 | (0) |     |        | monp | 1       |        |

#### Remarks

\*1 Initial value at initial reset

\*2 Not set in the circuit

\*3 Constantly "0" when being read

|         |        | Reg    | ister |        |              |              |              |              |                                                                                                       |

|---------|--------|--------|-------|--------|--------------|--------------|--------------|--------------|-------------------------------------------------------------------------------------------------------|

| Address | D3     | D2     | D1    | D0     | Name         | Init *1      | 1            | 0            | Comment                                                                                               |

|         | 0      | 0      | 0     | R1HIZ  | 0 *3         | - *2         |              |              | Unused                                                                                                |

| FF32H   |        | Ū      | 0     | KIIIIZ | 0 *3         | _ *2         |              |              | Unused                                                                                                |

|         |        | R      |       | R/W    | 0 *3         | _ *2         | 11.1.7       | <u></u>      | Unused                                                                                                |

|         |        |        |       |        | R1HIZ        | 0            | High-Z       | Output       | R1 output high impedance control                                                                      |

|         | R13    | R12    | R11   | R10    | R13          | 1<br>1       | High         | Low          |                                                                                                       |

| FF33H   |        |        |       |        | R12<br>R11   | 1            | High<br>High | Low<br>Low   | R10-R13 output port data                                                                              |

|         |        | R/     | W     |        | R10          | 1            | High         | Low          |                                                                                                       |

|         |        |        |       |        | 0 *3         | _ *2         | riigii       | LOW          | Unused                                                                                                |

|         | 0      | 0      | 0     | R2HIZ  | 0 *3         | _ *2         |              |              | Unused                                                                                                |

| FF34H   |        |        |       |        | 0 *3         | _ *2         |              |              | Unused                                                                                                |

|         |        | R      |       | R/W    | R2HIZ        | 0            | High-Z       | Output       | R2 output high impedance control                                                                      |

|         | 500    | 500    | Dat   | 5.00   | R23          | 1            | High         | Low          | 7                                                                                                     |

| FEOELL  | R23    | R22    | R21   | R20    | R22          | 1            | High         | Low          | P20 P22 output nort data                                                                              |

| FF35H   |        |        |       |        | R21          | 1            | High         | Low          | R20–R23 output port data                                                                              |

|         |        | R/     | VV    |        | R20          | 1            | High         | Low          |                                                                                                       |

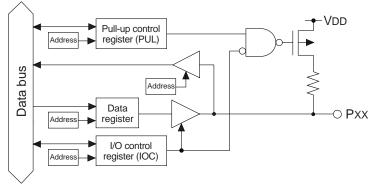

|         | IOC03  | IOC02  | IOC01 | 10C00  | IOC03        | 0            | Output       | Input        | 7                                                                                                     |

| FF40H   | 10003  | 10002  | 10001 | 10000  | IOC02        | 0            | Output       | Input        | P00-P03 I/O control register                                                                          |

| 114011  |        | R/     | w     |        | IOC01        | 0            | Output       | Input        |                                                                                                       |

|         |        |        | **    |        | IOC00        | 0            | Output       | Input        |                                                                                                       |

|         | PUL03  | PUL02  | PUL01 | PUL00  | PUL03        | 1            | On           | Off          |                                                                                                       |

| FF41H   | . 0200 | . 0202 |       | . 0200 | PUL02        | 1            | On           | Off          | P00–P03 pull-up control register                                                                      |

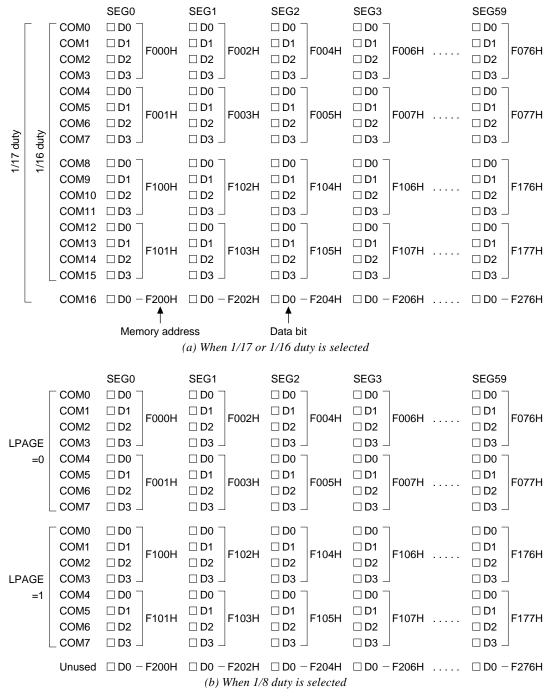

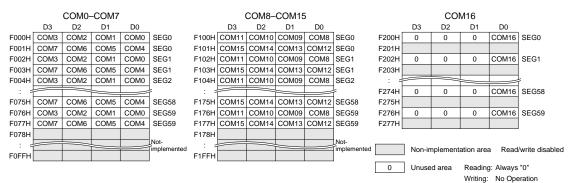

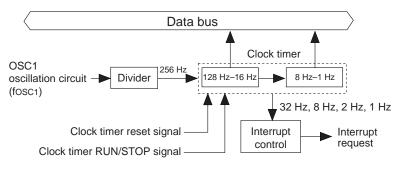

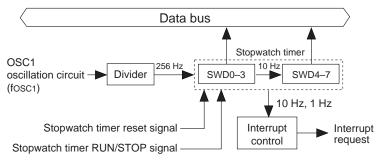

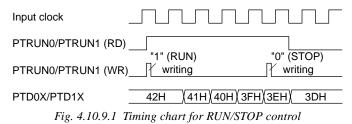

|         |        | R/     | W     |        | PUL01        | 1            | On           | Off          |                                                                                                       |