MF859-04

# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

# E0C6S32 Technical Hardware E0C6S32 Technical Software

**SEIKO EPSON CORPORATION**

### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. Please note that "E0C" is the new name for the old product "SMC". If "SMC" appears in other manuals understand that it now reads "E0C".

### PREFACE

This manual is individually described about the hardware and the software of the E0C6S32.

# I. E0C6S32 Technical Hardware

This part explains the function of the E0C6S32, the circuit configurations, and details the controlling method.

# II. E0C6S32 Technical Software

This part explains the programming method of the E0C6S32.

# E0C6S32 Technical Hardware

# CONTENTS

| CHAPTER 1 | OVI | ERVIEW                                                                                                                                                                                                                | I-1                          |

|-----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

|           | 1.1 | Configuration                                                                                                                                                                                                         | . I-1                        |

|           | 1.2 | Features                                                                                                                                                                                                              | . I-2                        |

|           | 1.3 | Block Diagram                                                                                                                                                                                                         | . I-3                        |

|           | 1.4 | Pin Layout Diagram                                                                                                                                                                                                    | . I-4                        |

|           | 1.5 | Pin Description                                                                                                                                                                                                       | . I-5                        |

| CHAPTER 2 | POV | WER SUPPLY AND INITIAL RESET                                                                                                                                                                                          | I-6                          |

|           | 2.1 | Power Supply                                                                                                                                                                                                          | I-6                          |

|           | 2.2 | Initial Reset<br>Reset pin (RESET)<br>Simultaneous high input to input ports (K00–K03)<br>Watchdog timer (Auxiliary reset)<br>Oscillation detection circuit (Auxiliary reset)<br>Internal register at initial setting | I-11<br>I-11<br>I-11<br>I-12 |

|           | 2.3 | Test Terminal (TEST)                                                                                                                                                                                                  | I-12                         |

| CHAPTER 3 | CPL | J, ROM, RAM                                                                                                                                                                                                           | I-13                         |

|           | 3.1 | CPU                                                                                                                                                                                                                   | I-13                         |

|           | 3.2 | ROM                                                                                                                                                                                                                   | I-14                         |

|           | 3.3 | RAM                                                                                                                                                                                                                   | I-15                         |

| CHAPTER 4 | PER | IPHERAL CIRCUITS AND OPERATION                                                                                                                                                                                        | I-16                         |

|           | 4.1 | Memory Map                                                                                                                                                                                                            | I-16                         |

|           | 4.2 | Resetting Watchdog Timer<br>Configuration of watchdog timer<br>Mask option<br>Control of watchdog timer<br>Programming note                                                                                           | I-24<br>I-24<br>I-25         |

| 4.3 | Oscillation Circuit                           | I-26 |

|-----|-----------------------------------------------|------|

|     | OSC1 oscillation circuit                      | I-26 |

|     | OSC3 oscillation circuit                      | I-26 |

|     | Configuration of oscillation circuit          | I-28 |

|     | Control of oscillation circuit                | I-29 |

|     | Programming notes                             | I-30 |

| 4.4 | Input Ports (K00–K03, K10)                    | I-31 |

|     | Configuration of input ports                  | I-31 |

|     | Differential registers and interrupt function |      |

|     | Mask option                                   |      |

|     | Control of input ports                        |      |

|     | Programming notes                             |      |

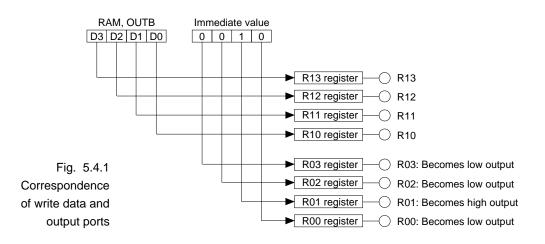

| 4.5 | Output Ports (R00–R03, R10–R13)               | I-40 |

| 1.0 | Configuration of output ports                 |      |

|     | Mask option                                   |      |

|     | Control of output ports                       |      |

|     | Programming note                              |      |

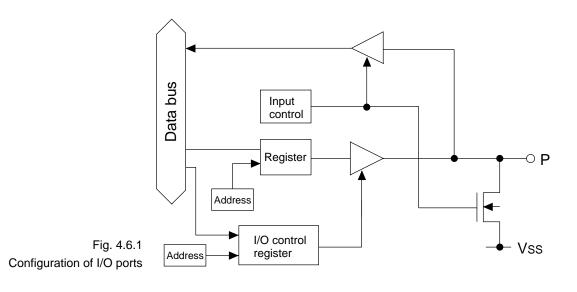

| 4.6 | I/O Ports (P00–P03, P10–P13)                  |      |

| 4.0 | Configuration of I/O ports                    |      |

|     | I/O control register and I/O mode             |      |

|     | Mask option                                   |      |

|     | Control of I/O ports                          |      |

|     | Programming notes                             |      |

|     |                                               |      |

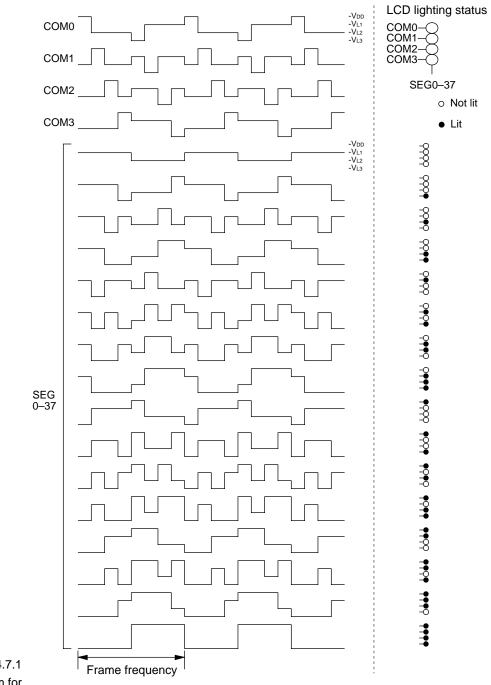

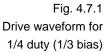

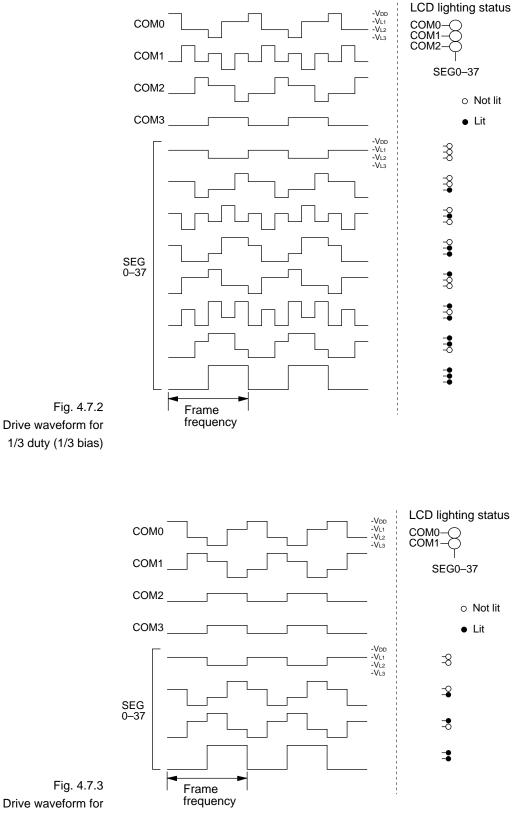

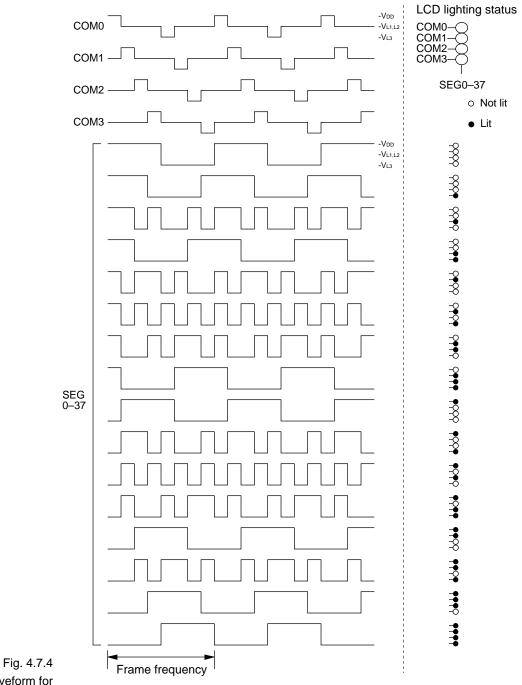

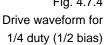

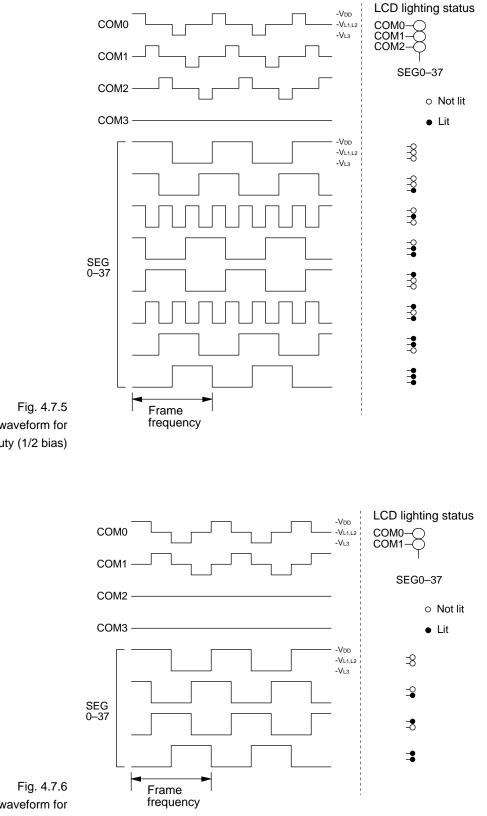

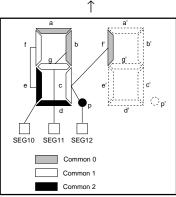

| 4.7 | LCD Driver (COM0–3, SEG0–37)                  | I-51 |

|     | Configuration of LCD driver                   | I-51 |

|     | Switching between dynamic and ALL OFF         | I-56 |

|     | Mask option (segment allocation)              | I-57 |

|     | Control of LCD driver                         | I-59 |

|     | Programming notes                             | I-60 |

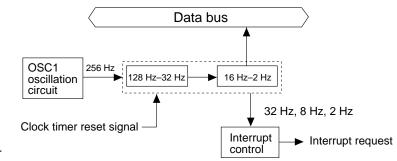

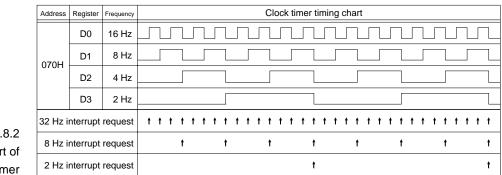

| 4.8 | Clock Timer                                   | I-61 |

|     | Configuration of clock timer                  | I-61 |

|     | Interrupt function                            | I-62 |

|     | Control of clock timer                        | I-63 |

|     | Programming notes                             | I-65 |

|     |                                               |      |

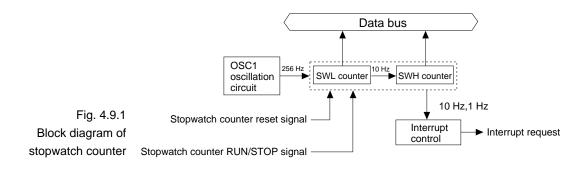

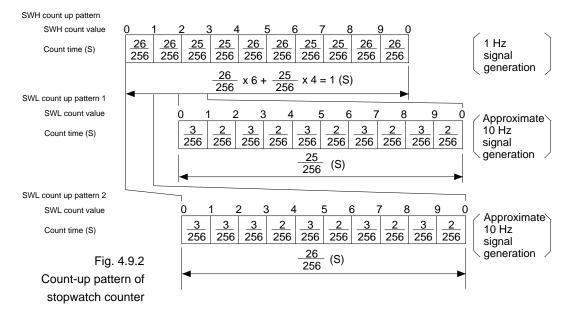

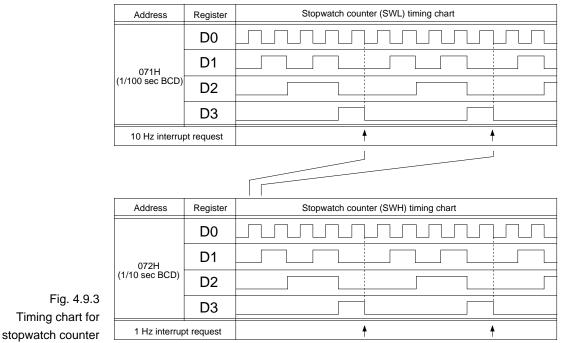

| 4.9  | Stopwatch Counter                             | I-66 |

|------|-----------------------------------------------|------|

|      | Configuration of stopwatch counter            | I-66 |

|      | Count-up pattern                              | I-67 |

|      | Interrupt function                            | I-68 |

|      | Control of stopwatch counter                  | I-69 |

|      | Programming notes                             | I-72 |

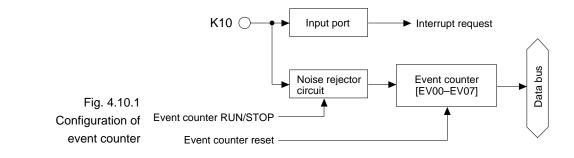

| 4.10 | Event Counter                                 | I-73 |

|      | Configuration of event counter                | I-73 |

|      | Operation of event counter                    | I-73 |

|      | Mask option                                   | I-74 |

|      | Control of event counter                      | I-75 |

|      | Programming note                              | I-76 |

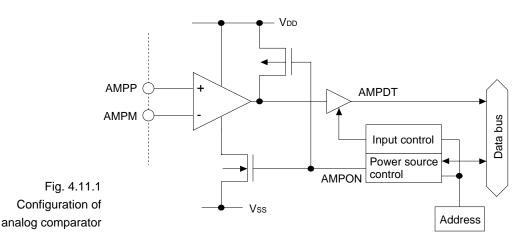

| 4.11 | Analog Comparator                             | I-77 |

|      | Configuration of analog comparator            | I-77 |

|      | Operation of analog comparator                | I-77 |

|      | Control of analog comparator                  | I-78 |

|      | Programming notes                             | I-79 |

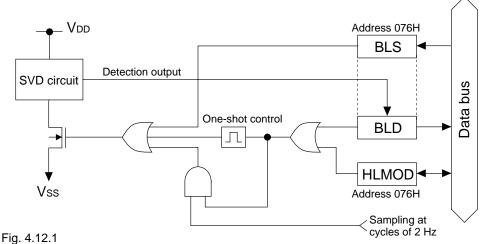

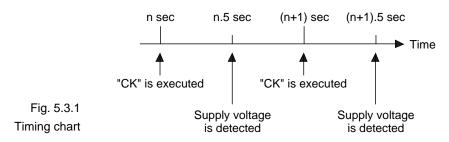

| 4.12 | Supply Voltage Detection (SVD) Circuit        |      |

|      | and Heavy Load Protection Function            | I-80 |

|      | Configuration of SVD circuit                  | I-80 |

|      | Heavy load protection function                | I-81 |

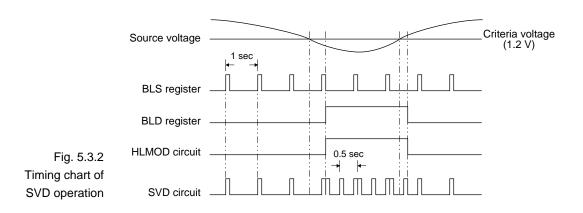

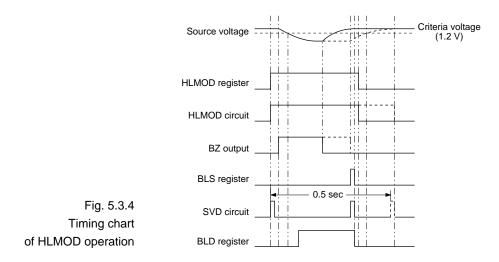

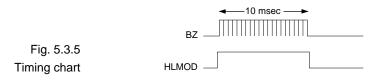

|      | Detection timing of SVD circuit               | I-82 |

|      | Control of SVD circuit                        | I-84 |

|      | Programing notes                              | I-86 |

| 4.13 | Interrupt and HALT                            | I-88 |

|      | Interrupt factors                             | I-90 |

|      | Specific masks and factor flags for interrupt | I-91 |

|      | Interrupt vectors                             | I-92 |

|      | Control of interrupt and HALT                 | I-93 |

|      | Programming notes                             | I-96 |

|      |                                               |      |

| CHAPTER 5 | SUM  | IMARY OF NOTES                                         | I-97  |

|-----------|------|--------------------------------------------------------|-------|

|           | 5.1  | Notes for Low Current Consumption                      | I-97  |

|           | 5.2  | Summary of Notes by Function                           | I-98  |

| CHAPTER 6 |      | GRAM OF BASIC<br>ERNAL CONNECTIONS                     | I-104 |

| CHAPTER 7 | ELEC | CTRICAL CHARACTERISTICS                                | I-107 |

|           | 7.1  | Absolute Maximum Rating                                | I-107 |

|           | 7.2  | Recommended Operating Conditions                       | I-108 |

|           | 7.3  | DC Characteristics                                     | I-109 |

|           | 7.4  | Analog Circuit Characteristics<br>and Consumed Current | I-111 |

|           | 7.5  | Oscillation Characteristics                            | I-119 |

| CHAPTER 8 | PAC  | CKAGE                                                  | I-124 |

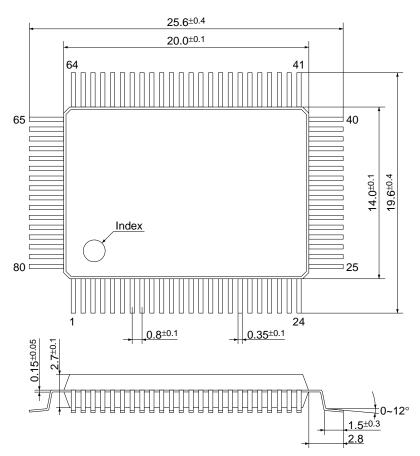

|           | 8.1  | Plastic Package                                        | I-124 |

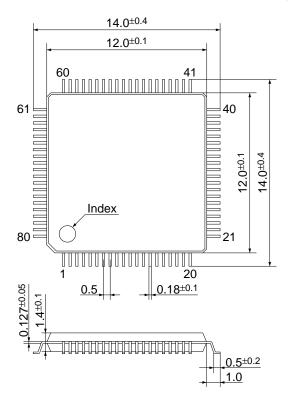

|           | 8.2  | Ceramic Package for Test Samples                       | I-126 |

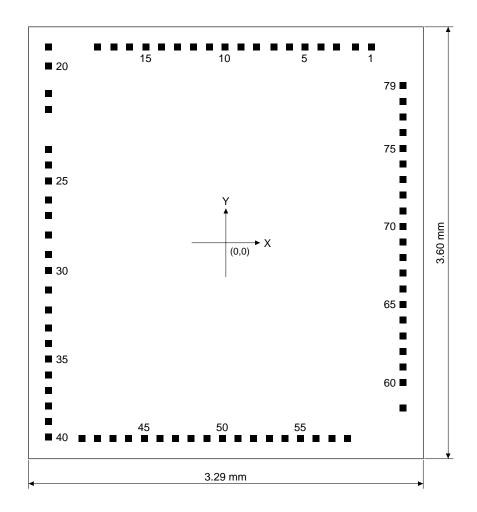

| CHAPTER 9 | PAD  | LAYOUT                                                 | I-127 |

|           | 9.1  | Diagram of Pad Layout                                  | I-127 |

|           | 9.2  | Pad Coordinates                                        | I-128 |

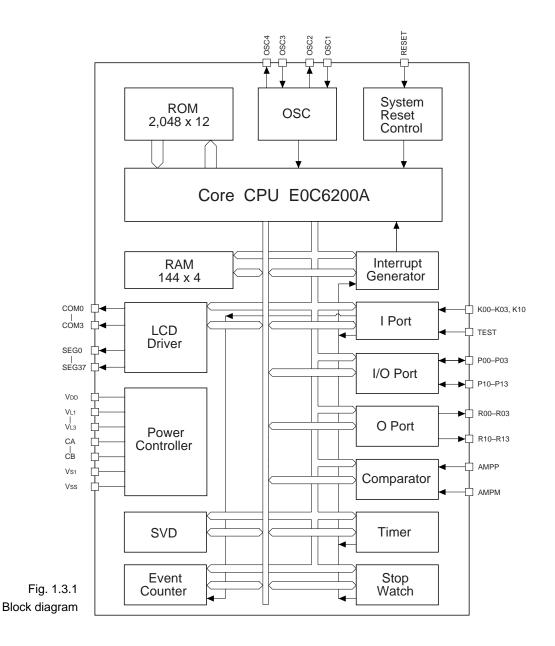

# **CHAPTER 1**

# **OVERVIEW**

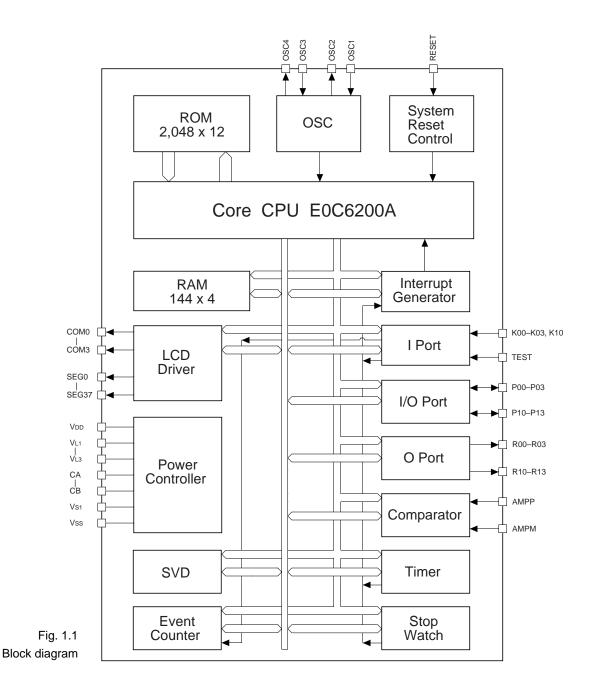

The E0C6S32 Series is a single-chip microcomputer made up of the 4-bit core CPU E0C6200A, ROM (2,048 words, 12 bits to a word), RAM (144 words, 4 bits to a word) LCD driver circuit, analog comparator, event counter, watchdog timer, and two types of time base counter. Because of its low-voltage operation and low power consumption, this series is ideal for a wide range of applications, and is especially suitable for battery-driven systems. Furthermore, the E0C6S32 is a shrunk model of the E0C6232. It can be used as various controller applications such as a clock, game and pager.

# 1.1 Configuration

The E0C6S32 Series is configured as follows, depending on supply voltage and oscillation circuits.

| Model                           | E0C6S32                         | E0C6SL32                        | E0C6SB32         | E0C6SA32                            |

|---------------------------------|---------------------------------|---------------------------------|------------------|-------------------------------------|

| Supply Voltage                  | 1.8*–3.6 V                      | 0.9–1.8 V                       | 0.9–3.6 V        | 1.8*–3.6 V                          |

| External<br>LCD<br>Power Supply | Supports<br>3.0 V<br>LCD panels | Supports<br>3.0 V<br>LCD panels | Not<br>supported | Supports<br>4.5/3.0 V<br>LCD panels |

| Oscillation                     |                                 | OSC1 only                       |                  | OSC1 and OSC3                       |

| Circuits                        |                                 | (Twin Clock)                    |                  |                                     |

\* Applications that display with an LCD panel require at least 2.2 V of supply voltage because a voltage less than 2.2 V lowers the LCD drive voltage.

# 1.2 Features

|                   |                        | E0C6S32                                                                                     | E0C6SL32                 | E0C6SB32            | E0C6SA32                |  |  |

|-------------------|------------------------|---------------------------------------------------------------------------------------------|--------------------------|---------------------|-------------------------|--|--|

| OSC1 oscillation  | n circuit              | Crystal oscillation circ                                                                    | uit 32.768 kHz (Typ.)    |                     |                         |  |  |

| OSC3 oscillation  | n circuit              | No setting                                                                                  | No setting               |                     |                         |  |  |

|                   |                        |                                                                                             |                          |                     |                         |  |  |

|                   |                        |                                                                                             |                          | 1 MHz (Typ.)        |                         |  |  |

| Instruction sets  |                        | 100 types                                                                                   |                          |                     |                         |  |  |

| Instruction exec  | ution time             | 153 µsec, 214 µsec, 36                                                                      | 66 μsec (CLK = 32.768    | kHz)                |                         |  |  |

| (differs dependi  | ng oninstruction)      |                                                                                             |                          |                     | 5 µsec, 7 µsec, 12 µsec |  |  |

| (CLK: CPU ope     | ration frequency)      |                                                                                             |                          |                     | (CLK = 1 MHz)           |  |  |

| ROM capacity      |                        | 2,048 words, 12 bits p                                                                      | er word                  |                     |                         |  |  |

| RAM capacity      |                        | 144 words, 4 bits per v                                                                     | vord                     |                     |                         |  |  |

| Input ports       |                        | 5 bits (pull-down resis                                                                     | tor can be added throug  | gh mask option)     |                         |  |  |

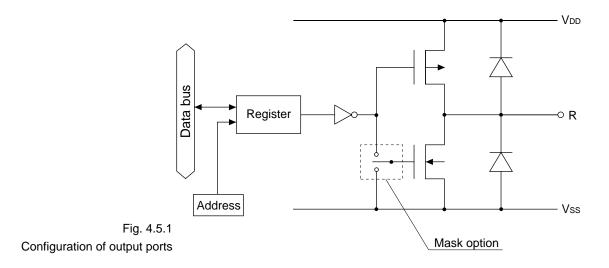

| Output ports      |                        | 8 bits (BZ, BZ, FOUT                                                                        | outputs are available th | nrough mask option) |                         |  |  |

| Input/output por  | ts                     | 8 bits (pull-down resistor is added during input data read-out)                             |                          |                     |                         |  |  |

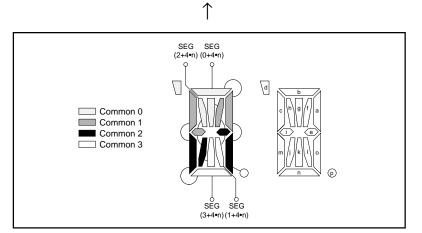

| LCD driver        |                        | Either 38 segments × 4 or 3 or 2 common *1                                                  |                          |                     |                         |  |  |

|                   |                        | V-3V 1/4 or 1/3 or 1/2 duty (regulated voltage circut and booster voltage circuit built-in) |                          |                     |                         |  |  |

| Time base count   | ter                    | Two types (timer and stopwatch)                                                             |                          |                     |                         |  |  |

| Watchdog timer    | -                      | Built-in (can be disabled through mask option)                                              |                          |                     |                         |  |  |

| Event counter     |                        | One 8-bit inputs                                                                            |                          |                     |                         |  |  |

| Analog compara    | ator                   | Inverted input x 1, noninverted input x 1                                                   |                          |                     |                         |  |  |

| Supply voltage d  | etection circuit (SVD) | 2.4 V                                                                                       | 1.2 V                    | 1.2 V               | 2.4 V                   |  |  |

| External interrup | pt                     | Input port interrupt; du                                                                    | al system                |                     |                         |  |  |

| Internal interrup | ot                     | Time base counter inte                                                                      | errupt; dual system      |                     |                         |  |  |

| Supply voltage 3  | *2                     | 3.0 V (1.8–3.6 V)                                                                           | 1.5 V (0.9–1.8 V)        | 1.5 V (0.9–3.6 V)   | 3.0 V (1.8–3.6 V)       |  |  |

| Consumed          | CLK = 32.768 kHz       | 1.2 µA                                                                                      | 1.0 µA                   | 1.0 µA              | 1.5 µA                  |  |  |

| current           | (when halted)          | 1.2 μΑ                                                                                      | 1.0 μΑ                   | 1.0 μΑ              | 1.5 μΑ                  |  |  |

|                   | CLK = 32.768 kHz       | 4.5 μΑ                                                                                      | 4.0 µA                   | 4.0 µA              | 6.0 µA                  |  |  |

| (Typ. value)      | (when executed)        | т.5 µЛ                                                                                      | 4.0 µA                   | τ.υ μΛ              | 0.0 μΑ                  |  |  |

|                   | CLK = 1 MHz            | _                                                                                           | _                        | _                   | 300 µA                  |  |  |

|                   | (when executed)        | _                                                                                           | _                        |                     | 500 µA                  |  |  |

| Form when ship    | ped                    | 80-pin QFP (plastic) o                                                                      | r chip                   |                     |                         |  |  |

\*1 Selected by mask option

\*2 The supply voltage range of the E0C6S32 and E0C6SA32 is 2.2 to 3.6 V when an LCD panel is used.

In this manual, BLD and SVD (supply voltage detection) have the same meaning.

# 1.3 Block Diagram

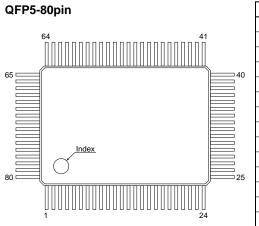

# 1.4 Pin Layout Diagram

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | SEG17    | 21      | SEG36    | 41      | R00      | 61      | COM2     |

| 2       | TEST     | 22      | SEG37    | 42      | R12      | 62      | COM1     |

| 3       | SEG18    | 23      | AMPP     | 43      | R11      | 63      | COM0     |

| 4       | SEG19    | 24      | AMPM     | 44      | R10      | 64      | SEG0     |

| 5       | SEG20    | 25      | K10      | 45      | R13      | 65      | SEG1     |

| 6       | SEG21    | 26      | K03      | 46      | Vss      | 66      | SEG2     |

| 7       | SEG22    | 27      | K02      | 47      | RESET    | 67      | SEG3     |

| 8       | SEG23    | 28      | K01      | 48      | OSC4     | 68      | SEG4     |

| 9       | SEG24    | 29      | K00      | 49      | OSC3     | 69      | SEG5     |

| 10      | SEG25    | 30      | P03      | 50      | VS1      | 70      | SEG6     |

| 11      | SEG26    | 31      | P02      | 51      | OSC2     | 71      | SEG7     |

| 12      | SEG27    | 32      | P01      | 52      | OSC1     | 72      | SEG8     |

| 13      | SEG28    | 33      | P00      | 53      | VDD      | 73      | SEG9     |

| 14      | SEG29    | 34      | P13      | 54      | VL3      | 74      | SEG10    |

| 15      | SEG30    | 35      | P12      | 55      | VL2      | 75      | SEG11    |

| 16      | SEG31    | 36      | P11      | 56      | VL1      | 76      | SEG12    |

| 17      | SEG32    | 37      | P10      | 57      | N.C.     | 77      | SEG13    |

| 18      | SEG33    | 38      | R03      | 58      | CB       | 78      | SEG14    |

| 19      | SEG34    | 39      | R02      | 59      | CA       | 79      | SEG15    |

| 20      | SEG35    | 40      | R01      | 60      | COM3     | 80      | SEG16    |

N.C.: No connection

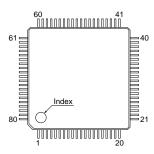

| Pin No. | Pin Name |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | AMPP     | 21      | R11      | 41      | COM0     | 61      | SEG18    |

| 2       | AMPM     | 22      | R10      | 42      | SEG0     | 62      | SEG19    |

| 3       | K10      | 23      | R13      | 43      | SEG1     | 63      | SEG20    |

| 4       | K03      | 24      | Vss      | 44      | SEG2     | 64      | SEG21    |

| 5       | K02      | 25      | RESET    | 45      | SEG3     | 65      | SEG22    |

| 6       | K01      | 26      | OSC4     | 46      | SEG4     | 66      | SEG23    |

| 7       | K00      | 27      | OSC3     | 47      | SEG5     | 67      | SEG24    |

| 8       | P03      | 28      | VS1      | 48      | SEG6     | 68      | SEG25    |

| 9       | P02      | 29      | OSC2     | 49      | SEG7     | 69      | SEG26    |

| 10      | P01      | 30      | OSC1     | 50      | SEG8     | 70      | SEG27    |

| 11      | P00      | 31      | VDD      | 51      | SEG9     | 71      | SEG28    |

| 12      | P13      | 32      | VL3      | 52      | SEG10    | 72      | SEG29    |

| 13      | P12      | 33      | VL2      | 53      | SEG11    | 73      | SEG30    |

| 14      | P11      | 34      | VL1      | 54      | SEG12    | 74      | SEG31    |

| 15      | P10      | 35      | N.C.     | 55      | SEG13    | 75      | SEG32    |

| 16      | R03      | 36      | CB       | 56      | SEG14    | 76      | SEG33    |

| 17      | R02      | 37      | CA       | 57      | SEG15    | 77      | SEG34    |

| 18      | R01      | 38      | COM3     | 58      | SEG16    | 78      | SEG35    |

| 19      | R00      | 39      | COM2     | 59      | SEG17    | 79      | SEG36    |

| 20      | R12      | 40      | COM1     | 60      | TEST     | 80      | SEG37    |

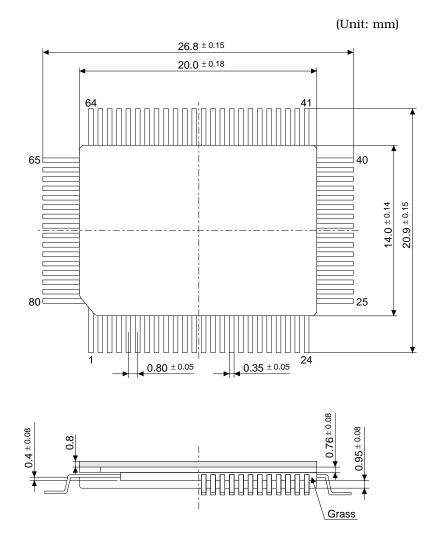

### QFP14-80pin

Fig. 1.4.1(b) Pin layout diagram

N.C.: No connection

Fig. 1.4.1(a) Pin layout diagram

# 1.5 Pin Description

| Die Norse | Pin N    | umber    | Input/ | Function                                                                 |  |

|-----------|----------|----------|--------|--------------------------------------------------------------------------|--|

| Pin Name  | QFP5-80  | QFP14-80 | Output |                                                                          |  |

| Vdd       | 53       | 31       | (I)    | Power source positive terminal                                           |  |

| Vss       | 46       | 24       | (I)    | Power source negative terminal                                           |  |

| VS1       | 50       | 28       | _      | Constant voltage output terminal for oscillation                         |  |

| VL1       | 56       | 34       | _      | Constant voltage output terminal for LCD (approx1.05 V)                  |  |

| VL2       | 55       | 33       | _      | Booster output terminal for LCD (VL1 $\times$ 2)                         |  |

| VL3       | 54       | 32       | -      | Booster output terminal for LCD (VL1 $\times$ 3)                         |  |

| CA, CB    | 58, 59   | 36, 37   | -      | Booster condenser connector terminal                                     |  |

| OSC1      | 52       | 30       | Ι      | Crystal oscillator input terminal                                        |  |

| OSC2      | 51       | 29       | 0      | Crystal oscillator output terminal                                       |  |

| OSC3      | 49       | 27       | Ι      | *1                                                                       |  |

| OSC4      | 48       | 26       | 0      | *2                                                                       |  |

| K00–10    | 25–29    | 3–7      | Ι      | Input terminal                                                           |  |

| P00–13    | 30–37    | 8–15     | I/O    | Input/output terminal                                                    |  |

| R00–03    | 38–41    | 16–19    | 0      | Output terminal                                                          |  |

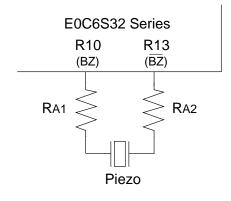

| R10       | 44       | 22       | Ο      | Output terminal (Can output BZ through mask option.)                     |  |

| R13       | 45       | 23       | Ο      | Output terminal (Can output $\overline{\text{BZ}}$ through mask option.) |  |

| R11       | 43       | 21       | Ο      | Output terminal                                                          |  |

| R12       | 42       | 20       | Ο      | Output terminal (Can output FOUT through mask option.)                   |  |

| AMPP      | 23       | 1        | Ι      | Analog comparator noninverted input terminal                             |  |

| AMPM      | 24       | 2        | Ι      | Analog comparator inverted input terminal                                |  |

| SEG0-37   | 1, 3–22, | 42–59,   | 0      | LCD segment output terminal                                              |  |

|           | 64–80    | 61–80    |        | (DC output available through mask option.)                               |  |

| COM0-3    | 60–63    | 38–41    | 0      | LCD common output terminal                                               |  |

| RESET     | 47       | 25       | Ι      | Initial setting input terminal                                           |  |

| TEST      | 2        | 60       | Ι      | Test input terminal                                                      |  |

Table 1.5.1 Pin description

\*1 6S32/6SL32/6SB32: Not connected

|    | 6SA32:            | CR or ceramic oscillation input terminal  |

|----|-------------------|-------------------------------------------|

|    |                   | (Switchable through mask option.)         |

| *2 | 6S32/6SL32/6SB32: | Not connected                             |

|    | 6SA32:            | CR or ceramic oscillation output terminal |

|    |                   | (Switchable through mask option.)         |

|    |                   |                                           |

# CHAPTER 2 POWER SUPPLY AND INITIAL RESET

# 2.1 Power Supply

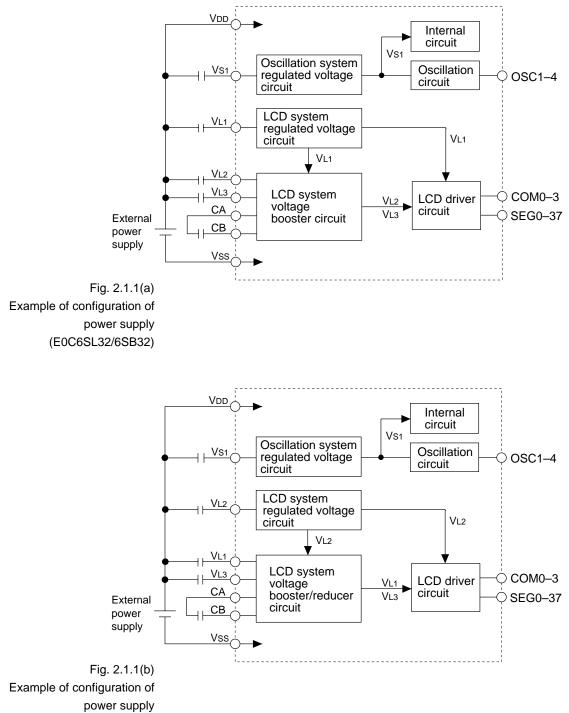

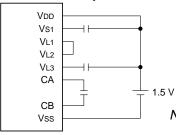

With a single external power supply (\*1) supplied to VDD through Vss, the EOC6S32 Series generates the necessary internal voltage with the regulated voltage circuit (<Vs1> for oscillators, <VL1> for LCDs) and the voltage booster circuit (<VL2, VL3> for LCDs). Or the EOC6S32 Series generates the necessary internal voltage with the regulated voltage circuit (<Vs1> for oscillators, <VL2> for LCDs) and the voltage booster circuit (<VL1, VL3> for LCDs).

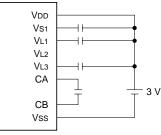

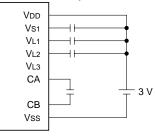

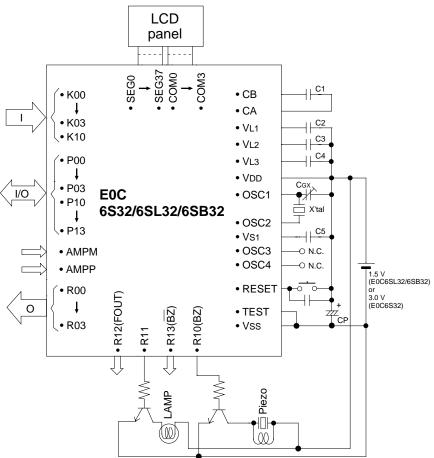

Figures 2.1.1(a) and 2.1.1(b) show the configuration of power supply.

\*1 Supply voltage: 6S32 .. 1.8 (2.2)-3.6 V 6SL32 .. 0.9-1.8 V 6SB32 .. 0.9-3.6 V 6SA32 .. 1.8 (2.2)-3.6 V The values enclosed with ( ) are mini-

mum voltages for applications that use LCD display.

- Note External loads cannot be driven by the regulated voltage and voltage booster circuit's output voltage.

- See "7 ELECTRICAL CHARACTERISTICS" for voltage values.

(E0C6S32/6SA32)

The LCD system regulated voltage circuit use can be prohibited by setting the mask option. In this case, external elements can be minimized because the external capacitors for the LCD system regulated voltage circuit are not necessary. However when the LCD system regulated voltage circuit is not used, the display quality of the LCD panel, when the supply voltage fluctuates (drops), is inferior to when the LCD system regulated voltage circuit is used. The E0C6SB32 always uses the the LCD system regulated voltage circuit, therefore the external capacitors are required. Figure 2.1.2 shows the external elements when the the LCD system regulated voltage circuit is not used.

• E0C6SA32

4.5 V LCD panel

Note: VL2 is shorted to VSS inside the IC.

### • E0C6S32/E0C6SA32

3 V LCD panel 3 V LCD panel

1/4, 1/3, 1/2 duty, 1/3 bias

Vss

Note: VL3 is shorted to VSS inside the IC.

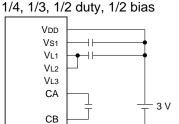

• E0C6SL32

3 V LCD panel

1/4, 1/3, 1/2 duty, 1/2 bias

Fig. 2.1.2 External elements when LCD system regulated voltage circuit is not used

Note: VL1 is shorted to VSS inside the IC.

### LCD system power supply

For the LCD system power supply, either "internal" (to generate internally) or "external" (to supply from outside of the IC) can be selected. The LCD panel voltage has been decided depending on the model and selection of the LCD system power supply.

When "external" is selected by the mask option, the specified LCD drive voltage terminal is connected to the VSS inside the IC.

| 1/3 Bias | Internal  | External  |           |           |  |  |

|----------|-----------|-----------|-----------|-----------|--|--|

|          | Vl1 / Vl2 | VL1 = VSS | VL2 = VSS | VL3 = VSS |  |  |

| E0C6S32  | 3.0 V LCD | ×         | ×         | 3.0 V LCD |  |  |

| E0C6SA32 | 3.0 V LCD | ×         | 4.5 V LCD | 3.0 V LCD |  |  |

| E0C6SL32 | 3.0 V LCD | ×         | ×         | ×         |  |  |

| E0C6SB32 | 3.0 V LCD | Х         | ×         | ×         |  |  |

| 1/2 Bias | Internal | External  |           |           |  |

|----------|----------|-----------|-----------|-----------|--|

|          | VL1/VL2  | VL1 = VSS | VL2 = VSS | VL3 = VSS |  |

| E0C6S32  | ×        | ×         | ×         | 3.0 V LCD |  |

| E0C6SA32 | ×        | ×         | Х         | 3.0 V LCD |  |

| E0C6SL32 | ×        | 3.0 V LCD | Х         | ×         |  |

Combinations that are marked with an " $\!\times\!$ " cannot be selected.

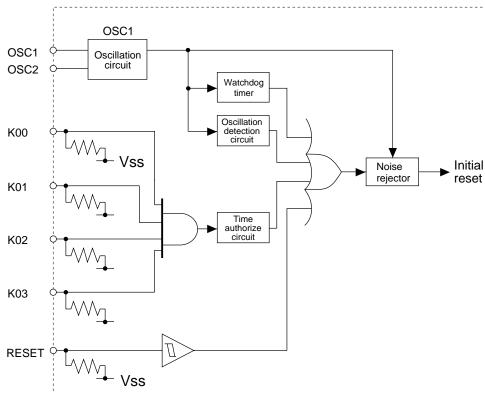

# 2.2 Initial Reset

To initialize the EOC6S32 Series circuits, initial reset must be executed. There are four ways of doing this. Four types of initial reset factors are available, however be sure to use (1) or (2) for resetting because (3) and (4) are auxiliary reset factors.

- (1) External initial reset by the RESET terminal

- (2) External initial reset by simultaneous high input to terminals K00–K03

- (3) Initial reset by watchdog timer

- (4) Initial reset by the oscillation detection circuit

Figure 2.2.1 shows the configuration of the initial reset circuit.

**Reset pin (RESET)**Initial reset can be executed externally by setting the reset<br/>terminal to the high level. This high level must be main-<br/>tained for at least 5 msec (when oscillating frequency is<br/>fosc1 = 32 kHz, after oscillation circuit start up), because<br/>the initial reset circuit contains a noise rejector circuit.<br/>When the reset terminal goes low the CPU begins to operate.

# Simultaneous high input to input ports (K00–K03)

Another way of executing initial reset externally is to input a high signal simultaneously to the input ports (K00–K03) selected with the mask option. The specified input port terminals must be kept high for at least 5 msec (when oscillating frequency is fOSC1 = 32 kHz, after oscillation circuit start up), because the initial reset circuit contains a noise rejector circuit. Table 2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.1 Input port combinations

| Α | Not used        |

|---|-----------------|

| В | K00*K01         |

| С | K00*K01*K02     |

| D | K00*K01*K02*K03 |

When, for instance, mask option D (K00\*K01\*K02\*K03) is selected, initial reset is executed when the signals input to the four ports K00–K03 are all high at the same time.

Further, when the input time of the simultaneous HIGH input is tested and found to be the same or more than the defined time (1–3 sec), the time test circuit that performs initial reset can be selected with the mask option.

If you use this function, make sure that the specified ports do not go high at the same time during ordinary operation.

# Watchdog timer (Auxiliary reset)

If the CPU runs away for some reason, the watchdog timer will detect this situation and output an initial reset signal. See "4.2 Resetting Watchdog Timer" for details.

| Oscillation detection | The oscillation detection circuit outputs the initial reset     |

|-----------------------|-----------------------------------------------------------------|

| circuit (Auxiliary    | signal at power-on until the crystal oscillation circuit (OSC1) |

| reset)                | begins oscillating, or when this crystal oscillation circuit    |

| 16361)                | (OSC1) halts oscillating for some reason.                       |

|                       | However, depending on the power-on sequence (voltage rise       |

|                       | timing), the circuit may not work properly. Therefore, use      |

|                       | the reset terminal or reset by simultaneous high input to the   |

|                       | input port (K00–K03) for initial reset after turning power on.  |

# Internal register at initial setting

Initial reset initializes the CPU as shown in the table below.

### Table 2.2.2

Initial values

| 2 C                        | PU Core | l              |               |

|----------------------------|---------|----------------|---------------|

| Name                       | Signal  | Number of Bits | Setting Value |

| Program counter step       | PCS     | 8              | 00H           |

| Program counter page       | PCP     | 4              | 1H            |

| New page pointer           | NPP     | 4              | 1H            |

| Stack pointer              | SP      | 8              | Undefined     |

| Index register X           | X       | 9              | Undefined     |

| Index register Y           | Y       | 9              | Undefined     |

| Register pointer           | RP      | 4              | Undefined     |

| General-purpose register A | A       | 4              | Undefined     |

| General-purpose register B | В       | 4              | Undefined     |

| Interrupt flag             | I       | 1              | 0             |

| Decimal flag               | D       | 1              | Undefined     |

| Zero flag                  | Z       | 1              | Undefined     |

| Carry flag                 | C       | 1              | Undefined     |

| Peripheral Circuits      |                |               |  |  |  |  |  |  |  |

|--------------------------|----------------|---------------|--|--|--|--|--|--|--|

| Name                     | Number of Bits | Setting Value |  |  |  |  |  |  |  |

| RAM                      | 4              | Undefined     |  |  |  |  |  |  |  |

| Segment data             | 4              | Undefined     |  |  |  |  |  |  |  |

| Other peripheral circuit | 4              | *1            |  |  |  |  |  |  |  |

\*1 See "4.1 Memory Map"

# 2.3 Test Terminal (TEST)

This terminal is used when the IC load is being detected. During ordinary operation be certain to connect this terminal to Vss.

# CHAPTER 3

# CPU, ROM, RAM

# 3.1 CPU

The E0C6S32 Series employs the core CPU E0C6200A for the CPU, so that register configuration, instructions and so forth are virtually identical to those in other family processors using the E0C6200A.

Refer to "E0C6200/6200A Core CPU Manual" for details about the E0C6200A.

Note the following points with regard to the E0C6S32 Series:

- (1) The SLEEP operation is not assumed, so the SLP instruction cannot be used.

- (2) Because the ROM capacity is 2,048 words, bank bits are unnecessary and PCB and NBP are not used.

- (3) The RAM page is set at 0 only, so that the page part (XP, YP) of the index register that performs address specification is invalid.

| PUSH | XP   | PUSH | YP   |

|------|------|------|------|

| POP  | XP   | POP  | YP   |

| LD   | XP,r | LD   | YP,r |

| LD   | r,XP | LD   | r,YP |

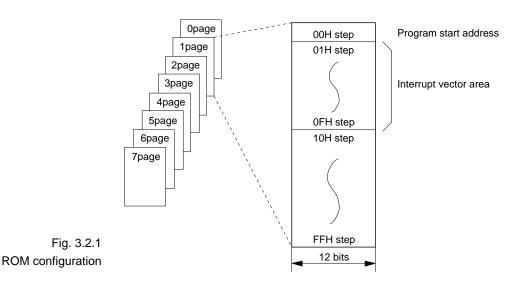

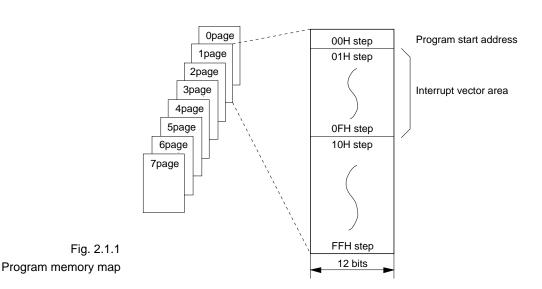

# 3.2 ROM

The built-in ROM, a mask ROM for loading the program, has a capacity of 2,048 steps, 12 bits each. The program area is 8 pages (0–7), each of 256 steps (00H–FFH). After initial reset, the program beginning address is page 1, step 00H. The interrupt vector is allocated to page 1, steps 01H–0FH.

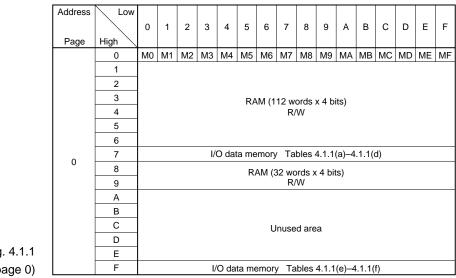

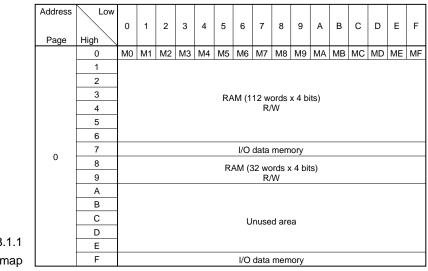

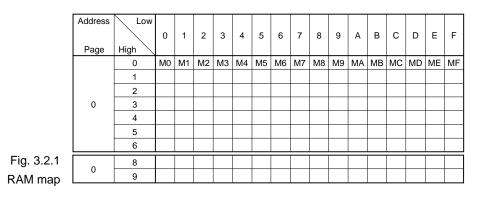

## 3.3 RAM

The RAM, a data memory storing a variety of data, has a capacity of 144 words, each of four bits. When programming, keep the following points in mind.

- (1) Part of the data memory can be used as stack area when saving subroutine calls and registers, so be careful not to overlap the data area and stack area.

- (2) Subroutine calls and interrupts take up three words of the stack area.

- (3) The data memory 000H–00FH is for the register pointers (RP), and is the addressable memory register area.

- (4) The data memory is split into two areas, 000H–06FH and 080H–09FH, so take care when allocating the data. (See "4.1 Memory Map" for details.)

# CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

Peripheral circuits (timer, I/O, and so on) of the E0C6S32 Series are memory mapped, and interfaced with the CPU. Thus, all the peripheral circuits can be controlled by using the memory operation command to access the I/O data memory in the memory map.

The following sections describe how the peripheral circuits operation.

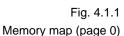

# 4.1 Memory Map

Data memory of the E0C6S32 Series has an address space of 160 words, of which 48 words are allocated to segment data memory and 32 words to I/O data memory. Figures 4.1.1 and 4.1.2 present the overall memory maps of the E0C6S32 Series, and Tables 4.1.1(a)–4.1.1(f) the peripheral circuits' (I/O space) memory maps.

|                                                | Address | Low    |                                                          |   |   |   |      |       |       |      |        |       |        |        |   |   |   |   |

|------------------------------------------------|---------|--------|----------------------------------------------------------|---|---|---|------|-------|-------|------|--------|-------|--------|--------|---|---|---|---|

|                                                |         |        | 0                                                        | 1 | 2 | 3 | 4    | 5     | 6     | 7    | 8      | 9     | Α      | В      | С | D | Е | F |

| Fig. 4.1.2                                     | Page    | High 🔪 |                                                          |   |   |   |      |       |       |      |        |       |        |        |   |   |   |   |

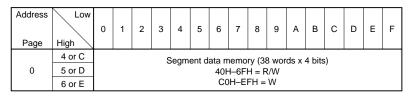

| Memory map                                     |         | 4 or C |                                                          |   |   | S | eame | nt da | ata m | emor | rv (38 | s wor | ds x 4 | 1 hits | ) |   |   |   |

| , ,                                            | 0       | 5 or D | Segment data memory (38 words x 4 bits)<br>40H–6FH = R/W |   |   |   |      |       |       |      |        |       |        |        |   |   |   |   |

| (segment area) $6 \text{ or } E$ $C0H-EFH = W$ |         |        |                                                          |   |   |   |      |       |       |      |        |       |        |        |   |   |   |   |

Note (1) See Tables 4.1.1(a)–4.1.1(f) for details of I/O data memory.

(2) The mask option can be used to select whether to assign the overall area of segment data memory to 40H–6FH or C0H– EFH.

> When 40H–6FH is selected, read/write is enabled. When C0H–EFH is selected, write only is enabled.

If 40H–6FH is assigned, RAM is used as the segment area (48 words).

(3) Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these areas.

| Address  |      | Reg  | ister |      |      |       |      |     | Comment                             |

|----------|------|------|-------|------|------|-------|------|-----|-------------------------------------|

| 71001033 | D3   | D2   | D1    | D0   | Name | SR *1 | 1    | 0   | Common                              |

|          | TM3  | TM2  | TM1   | TM0  | TM3  | 0     |      |     | Timer data (clock timer 2 Hz)       |

| 070H     |      | I    | R     |      | TM2  | 0     |      |     | Timer data (clock timer 4 Hz)       |

| 0700     |      |      |       |      | TM1  | 0     |      |     | Timer data (clock timer 8 Hz)       |

|          |      |      |       |      | TM0  | 0     |      |     | Timer data (clock timer 16 Hz)      |

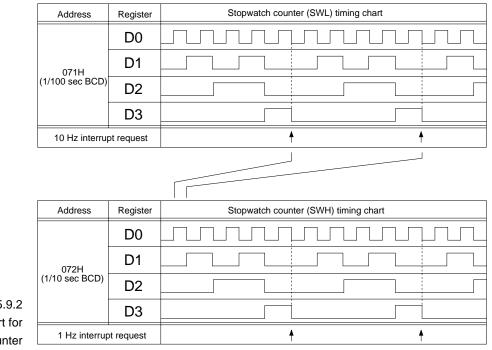

|          | SWL3 | SWL2 | SWL1  | SWL0 | SWL3 | 0     |      |     | MSB                                 |

| 071H     |      | l    | R     |      | SWL2 | 0     |      |     | Stopwatch counter                   |

| 0/18     |      |      |       |      | SWL1 | 0     |      |     | 1/100 sec (BCD)                     |

|          |      |      |       |      | SWL0 | 0     |      |     | LSB                                 |

|          | SWH3 | SWH2 | SWH1  | SWH0 | SWH3 | 0     |      |     | MSB                                 |

| 072H     |      | I    | R     |      | SWH2 | 0     |      |     | Stopwatch counter<br>1/10 sec (BCD) |

| 0720     |      |      |       |      | SWH1 | 0     |      |     | 1/10 sec (BCD)                      |

|          |      |      |       |      | SWH0 | 0     |      |     | LSB                                 |

|          | K03  | K02  | K01   | K00  | К03  | _ *2  | High | Low |                                     |

| 073H     |      | I    | R     |      | K02  | _ *2  | High | Low | Level and (K00, K02)                |

| 0/30     |      |      |       |      | K01  | _ *2  | High | Low | Input port (K00–K03)                |

|          |      |      |       |      | K00  | - *2  | High | Low |                                     |

Table 4.1.1(a) I/O memory map (070H–073H)

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| Address                                 |       | Reg        | ister   |         |         |       |               |        | Comment                                      |

|-----------------------------------------|-------|------------|---------|---------|---------|-------|---------------|--------|----------------------------------------------|

| /////////////////////////////////////// | D3    | D2         | D1      | D0      | Name    | SR *1 | 1             | 0      | Comment                                      |

|                                         | DFK03 | DFK02      | DFK01   | DFK00   | DFK03   | 0     | Falling       | Rising | 7                                            |

| 074H                                    |       | R          | /W      |         | DFK02   | 0     | Falling       | Rising | Differential register<br>(K00–K03)           |

| 07-111                                  |       |            |         |         | DFK01   | 0     | Falling       | Rising | (K00-K03)                                    |

|                                         |       |            |         |         | DFK00   | 0     | Falling       | Rising |                                              |

|                                         | EIK03 | EIK02      | EIK01   | EIK00   | EIK03   | 0     | Enable        | Mask   |                                              |

| 075H                                    |       | R          | w       |         | EIK02   | 0     | Enable        | Mask   | Interrupt mask register<br>(K00–K03)         |

| 07511                                   |       |            |         |         | EIK01   | 0     | Enable        | Mask   | (K00-K03)                                    |

|                                         |       |            |         |         | EIK00   | 0     | Enable        | Mask   |                                              |

|                                         | HLMOD | BLD<br>BLS | EISWIT1 | EISWITO | HLMOD   | 0     | Heavy<br>load | Normal | Heavy load protection mode register          |

|                                         | R/W   | R          | R       | W       | BLD     |       | Low voltage   | Normal | SVD evaluation data                          |

| 076H                                    | 1011  | W          |         |         | BLS     | 0     | ON            | OFF    | SVD ON/OFF                                   |

|                                         |       |            |         |         | EISWIT1 | 0     | Enable        | Mask   | Interrupt mask register<br>(stopwatch 1 Hz)  |

|                                         |       |            |         |         | EISWITO | 0     | Enable        | Mask   | Interrupt mask register<br>(stopwatch 10 Hz) |

|                                         | 0     | EIK10      | DFK10   | K10     | 0       | _ *2  |               |        | Unused                                       |

| 077H                                    | R     | R          | W       | R       | EIK10   | 0     | Enable        | Mask   | Interrupt mask register (K10)                |

|                                         |       |            |         |         | DFK10   | 0     | Falling       | Rising | Differential register (K10)                  |

|                                         |       |            |         |         | K10     | - *2  | High          | Low    | Input port (K10)                             |

Table 4.1.1(b) I/O memory map (074H–077H)

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| Address  |      | Reg  | ister |       |                     |       |         |         | Comment                                        |

|----------|------|------|-------|-------|---------------------|-------|---------|---------|------------------------------------------------|

| 71001033 | D3   | D2   | D1    | D0    | Name                | SR *1 | 1       | 0       | Common                                         |

|          | CSDC | ETI2 | ETI8  | ETI32 | CSDC                | 0     | Dynamic | ALL OFF | LCD drive switch                               |

| 078H     |      | R    | /W    |       | ETI2                | 0     | Enable  | Mask    | Interrupt mask register<br>(clock timer 2 Hz)  |

| 0700     |      |      |       |       | ETI8                | 0     | Enable  | Mask    | Interrupt mask register<br>(clock timer 8 Hz)  |

|          |      |      |       |       | ETI32               | 0     | Enable  | Mask    | Interrupt mask register<br>(clock timer 32 Hz) |

|          | 0    | TI2  | TI8   | TI32  | 0                   | _ *2  |         |         | Unused                                         |

| 079H     |      |      | R     |       | TI2 *4              | 0     | Yes     | No      | Interrupt factor flag<br>(clock timer 2 Hz)    |

| 07511    |      |      |       |       | TI8 <sup>*4</sup>   | 0     | Yes     | No      | Interrupt factor flag<br>(clock timer 8 Hz)    |

|          |      |      |       |       | TI32 <sup>*4</sup>  | 0     | Yes     | No      | Interrupt factor flag<br>(clock timer 32 Hz)   |

|          | IK1  | IK0  | SWIT1 | SWIT0 | IK1 <sup>*4</sup>   | 0     | Yes     | No      | Interrupt factor flag<br>(K10)                 |

| 07AH     |      |      | R     |       | IK0 <sup>*4</sup>   | 0     | Yes     | No      | Interrupt factor flag<br>(K00–K03)             |

| UTAN     |      |      |       |       | SWIT1 <sup>*4</sup> | 0     | Yes     | No      | Interrupt factor flag<br>(stopwatch 1 Hz)      |

|          |      |      |       |       | SWIT0 <sup>*4</sup> | 0     | Yes     | No      | Interrupt factor flag<br>(stopwatch 10 Hz)     |

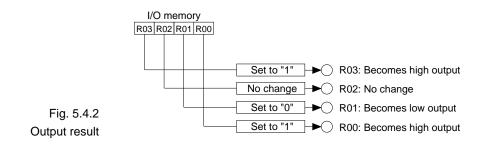

|          | R03  | R02  | R01   | R00   | R03                 | 0     | High    | Low     |                                                |

| 07BH     |      | R    | /W    |       | R02                 | 0     | High    | Low     | Output port (R00–R03)                          |

| 0/01     |      |      |       |       | R01                 | 0     | High    | Low     |                                                |

|          |      |      |       |       | R00                 | 0     | High    | Low     |                                                |

Table 4.1.1(c) I/O memory map (078H–07BH)

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| Address |       | Reg   | ister |      |                     |       |        |       | Comment                                                |

|---------|-------|-------|-------|------|---------------------|-------|--------|-------|--------------------------------------------------------|

| Address | D3    | D2    | D1    | D0   | Name                | SR *1 | 1      | 0     | Comment                                                |

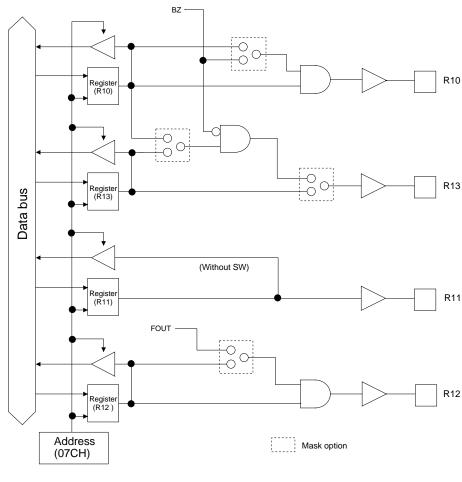

|         | R13   | R12   | R11   | R10  | R13                 | 0     | High   | Low   | Output port (R13, $\overline{\text{BZ}}$ )             |

| 07CH    |       | R     | W     |      | R12                 | 0     | High   | Low   | Output port (R12, FOUT)                                |

|         |       |       |       |      | R11                 | 0     | High   | Low   | Output port (R11)                                      |

|         |       |       |       |      | R10                 | 0     | High   | Low   | Output port (R10, BZ)                                  |

|         | P03   | P02   | P01   | P00  | P03                 | _ *2  | High   | Low   |                                                        |

| 07DH    |       | R     | w     |      | P02                 | - *2  | High   | Low   | I/O port (P00–P03)<br>Output latch reset at time of SR |

|         |       |       |       |      | P01                 | _ *2  | High   | Low   | Output facts reset at time of SK                       |

|         |       |       |       |      | P00                 | _ *2  | High   | Low   |                                                        |

|         | TMRST | SWRUN | SWRST | IOC0 | TMRST <sup>*5</sup> | Reset | Reset  | -     | Clock timer reset                                      |

| 07EH    | w     | R/W   | W     | R/W  | SWRUN               | 0     | RUN    | STOP  | Stopwatch counter RUN/STOP                             |

|         |       |       |       |      | SWRST <sup>*5</sup> | Reset | Reset  | -     | Stopwatch counter reset                                |

|         |       |       |       |      | IOC0                | 0     | Output | Input | I/O control register 0 (P00–P03)                       |

|         | WDRST | WD2   | WD1   | WD0  | WDRST <sup>*5</sup> | Reset | Reset  |       | Watchdog timer reset                                   |

| 07FH    | W     |       | R     |      | WD2                 | 0     |        |       | Timer data<br>(watchdog timer 1/4 Hz)                  |

|         |       |       |       |      | WD1                 | 0     |        |       | Timer data<br>(watchdog timer 1/2 Hz)                  |

|         |       |       |       |      | WD0                 | 0     |        |       | Timer data<br>(watchdog timer 1 Hz)                    |

Table 4.1.1(d) I/O memory map (07CH–07FH)

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| Address                                 |      | Reg  | ister |       |       |       |       |       | Comment                                 |

|-----------------------------------------|------|------|-------|-------|-------|-------|-------|-------|-----------------------------------------|

| /////////////////////////////////////// | D3   | D2   | D1    | D0    | Name  | SR *1 | 1     | 0     | Comment                                 |

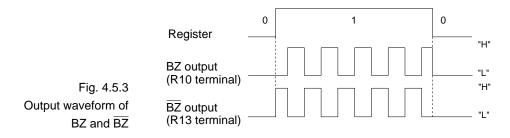

|                                         | BZFQ | 0    | 0     | 0     | BZFQ  | 0     | 2 kHz | 4 kHz | Buzzer frequency selection register     |

| 0F6H                                    | R/W  |      | R     |       | 0     | - *2  |       |       | Unused                                  |

|                                         |      |      |       |       | 0     | _ *2  |       |       | Unused                                  |

|                                         |      |      |       |       | 0     | _ *2  |       |       | Unused                                  |

|                                         | 0    | 0    | AMPDT | AMPON | 0     | _ *2  |       |       | Unused                                  |

| 0F7H                                    |      | R    |       | R/W   | 0     | _ *2  |       |       | Unused                                  |

|                                         |      |      |       |       | AMPDT | 1     | + > - | - > + | Analog comparator data                  |

|                                         |      |      |       | -     | AMPON | 0     | ON    | OFF   | Analog comparator ON/OFF                |

|                                         | EV03 | EV02 | EV01  | EV00  | EV03  | 0     |       |       | 7                                       |

| 0F8H                                    |      |      | R     |       | EV02  | 0     |       |       | Event counter<br>Low order (EV00–EV03)  |

|                                         |      |      |       |       | EV01  | 0     |       |       |                                         |

|                                         |      |      |       |       | EV00  | 0     |       |       |                                         |

|                                         | EV07 | EV06 | EV05  | EV04  | EV07  | 0     |       |       |                                         |

| 0F9H                                    |      | I    | R     |       | EV06  | 0     |       |       | Event counter<br>High order (EV04–EV07) |

|                                         |      |      |       |       | EV05  | 0     |       |       |                                         |

|                                         |      |      |       |       | EV04  | 0     |       |       |                                         |

Table 4.1.1(e) I/O memory map (0F6H–0F9H)

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| Address |     | Regi   | ster |       |                     |       |        |       | Comment                                                |

|---------|-----|--------|------|-------|---------------------|-------|--------|-------|--------------------------------------------------------|

| Audiess | D3  | D2     | D1   | D0    | Name                | SR *1 | 1      | 0     | Comment                                                |

|         | 0   | EVRUN  | 0    | EVRST | 0                   | _ *2  |        |       | Unused                                                 |

| 0FCH    | R   | R/W    | R    | w     | EVRUN               | 0     | RUN    | STOP  | Event counter RUN/STOP                                 |

|         |     |        |      |       | 0                   | _ *2  |        |       | Unused                                                 |

|         |     |        |      |       | EVRST <sup>*5</sup> | Reset | Reset  |       | Event counter reset                                    |

|         | P13 | P12    | P11  | P10   | P13                 | _ *2  | High   | Low   |                                                        |

| 0FDH    |     | R/     | W    |       | P12                 | _ *2  | High   | Low   | I/O port (P10–P13)<br>Output latch reset at time of SR |

|         |     |        |      |       | P11                 | _ *2  | High   | Low   | Output faich reset at time of SK                       |

|         |     |        |      |       | P10                 | - *2  | High   | Low   |                                                        |

|         | 0   | CLKCHG | OSCC | IOC1  | 0                   | _ *2  |        |       | Unused                                                 |

| OFEH    | R   |        | R/W  |       | CLKCHG              | 0     | OSC3   | OSC1  | CPU clock switch                                       |

|         |     |        |      |       | OSCC                | 0     | ON     | OFF   | OSC3 oscillator ON/OFF                                 |

|         |     |        |      |       | IOC1                | 0     | Output | Input | I/O control register 1 (P10–P13)                       |

Table 4.1.1(f) I/O memory map (0FCH–0FEH)

\*2 Not set in the circuit

\*3 Undefined

\*4 Reset (0) immediately after being read

\*5 Constantly "0" when being read

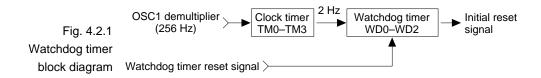

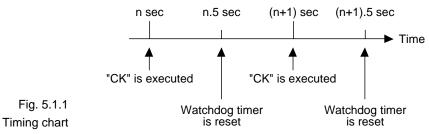

# 4.2 Resetting Watchdog Timer

# Configuration of watchdog timer

The E0C6S32 Series incorporates a watchdog timer as the source oscillator for OSC1 (clock timer 2 Hz signal). The watchdog timer must be reset cyclically by the software. If reset is not executed in at least 3 or 4 seconds, the initial reset signal is output automatically for the CPU. Figure 4.2.1 is the block diagram of the watchdog timer.

The watchdog timer, configured of a three-bit binary counter (WD0–WD2), generates the initial reset signal internally by overflow of the MSB.

Watchdog timer reset processing in the program's main routine enables detection of program overrun, such as when the main routine's watchdog timer processing is bypassed. Ordinarily this routine is incorporated where periodic processing takes place, just as for the timer interrupt routine.

The watchdog timer operates in the halt mode. If the halt status continues for 3 or 4 seconds, the initial reset signal restarts operation.

### Mask option

You can select whether or not to use the watchdog timer with the mask option. When "Not use" is chosen, there is no need to reset the watchdog timer.

# Control of watchdog timer

Table 4.2.1 lists the watchdog timer's control bits and their addresses.

| Address | Register |     |     |     |                     |       |       |   | Comment                               |

|---------|----------|-----|-----|-----|---------------------|-------|-------|---|---------------------------------------|

| Addless | D3       | D2  | D1  | D0  | Name                | SR *1 | 1     | 0 | Comment                               |

| 07FH    | WDRST    | WD2 | WD1 | WD0 | WDRST <sup>*5</sup> | Reset | Reset |   | Watchdog timer reset                  |

|         | W        | R   |     |     | WD2                 | 0     |       |   | Timer data<br>(watchdog timer 1/4 Hz) |

|         |          |     |     |     | WD1                 | 0     |       |   | Timer data<br>(watchdog timer 1/2 Hz) |

|         |          |     |     |     | WD0                 | 0     |       |   | Timer data<br>(watchdog timer 1 Hz)   |

\*1 Initial value at the time of initial reset

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

WDRST: This is the bit for resetting the watchdog timer.

| Watchdog timer reset<br>(07FH·D3) | When "1" is written :<br>When "0" is written :<br>Read-out :                                                                                                                                                                                       | Watchdog timer is reset<br>No operation<br>Always "0" |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

|                                   | When "1" is written to WDRST , the watchdog timer is reset,<br>and the operation restarts immediately after this. When "0"<br>is written to WDRST, no operation results.<br>This bit is dedicated for writing, and is always "0" for read-<br>out. |                                                       |  |  |  |

| Programming note                  | When the watchdog timer is being used, the software must<br>reset it within 3-second cycles, and timer data (WD0–WD2)<br>cannot be used for timer applications.                                                                                    |                                                       |  |  |  |

# 4.3 Oscillation Circuit

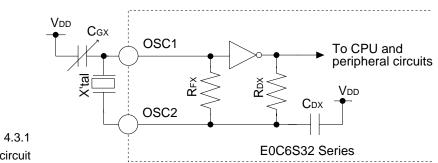

# OSC1 oscillation circuit

The E0C6S32 Series has a built-in crystal oscillation circuit. As an external element, the OSC1 oscillation circuit generates the operating clock for the CPU and peripheral circuitry by connecting the crystal oscillator (Typ. 32.768 kHz) and trimmer capacitor (5–25 pF).

Figure 4.3.1 is the block diagram of the OSC1 oscillation circuit.

Fig. 4.3.1 OSC1 oscillation circuit

As Figure 4.3.1 indicates, the crystal oscillation circuit can be configured simply by connecting the crystal oscillator (X'tal) between terminals OSC1 and OSC2 to the trimmer capacitor (CGx) between terminals OSC1 and VDD.

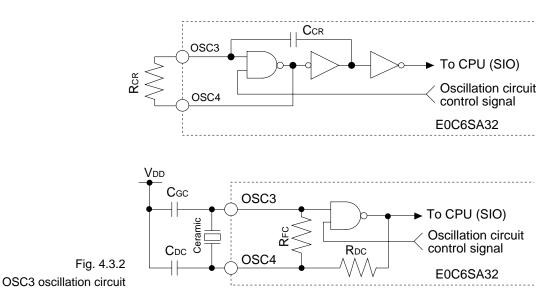

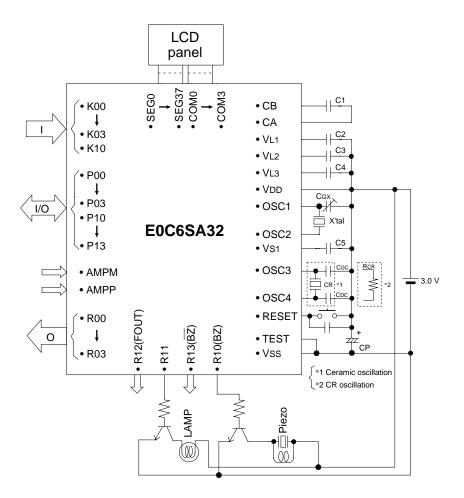

# OSC3 oscillation<br/>circuitIn the E0C6S32 Series, the E0C6SA32 has twin clock speci-<br/>fication. The mask option enables selection of either the CR<br/>or ceramic oscillation circuit (OSC3 oscillation circuit) as the<br/>CPU's subclock. Because the oscillation circuit itself is built-<br/>in, it provides the resistance as an external element when<br/>CR oscillation is selected, but when ceramic oscillation is<br/>selected both the ceramic oscillator and two capacitors (gate<br/>and drain capacitance) are required.<br/>Figure 4.3.2 is the block diagram of the OSC3 oscillation<br/>circuit.

# Note The figure above is an equivalent circuit and is different from the actual circuit.

As indicated in Figure 4.3.2, the CR oscillation circuit can be configured simply by connecting the resistor (RCR) between terminals OSC3 and OSC4 when CR oscillation is selected. When 33 k $\Omega$  is used for RCR, the oscillation frequency is about 1 MHz. When ceramic oscillation is selected, the ceramic oscillation circuit can be configured by connecting the ceramic oscillator (Typ. 1 MHz) between terminals OSC3 and OSC4 to the two capacitors (CGC and CDC) located between terminals OSC3 and OSC4 and VDD. For both CGC and CDC, connect capacitors that are about 100 pF. To lower current consumption of the OSC3 oscillation circuit, oscillation can be stopped through the software.

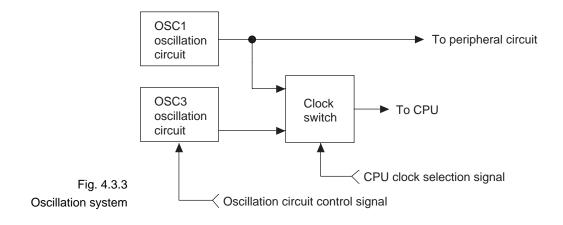

# Configuration of<br/>oscillation circuitThe E0C6S32, 6SL32 and 6SB32 have one oscillation circuit<br/>(OSC1), and the E0C6SA32 has two oscillation circuits<br/>(OSC1 and OSC3). OSC1 is a crystal oscillation circuit that<br/>supplies the operating clock the CPU and peripheral cir-<br/>cuits. OSC3 is either a CR or ceramic oscillation circuit.<br/>When processing with the E0C6SA32 requires high-speed<br/>operation, the CPU operating clock can be switched from<br/>OSC1 to OSC3.

Figure 4.3.3 is the block diagram of this oscillation system.

For EOC6SA32, selection of either OSC1 or OSC3 for the CPU's operating clock can be made through the software.

## Control of oscillationTable 4.3.1 lists the control bits and their addresses for the<br/>oscillation circuit.

| Address |    | Regi   | ster |        | Comment |       |        |                  |                                  |

|---------|----|--------|------|--------|---------|-------|--------|------------------|----------------------------------|

| Addless | D3 | D2     | D1   | D0     | Name    | SR *1 | 1      | 0                | Comment                          |

|         | 0  | CLKCHG | OSCC | IOC1   | 0       | _ *2  |        |                  | Unused                           |

| OFEH    | R  | R/W    |      | CLKCHG | 0       | OSC3  | OSC1   | CPU clock switch |                                  |

|         |    |        |      |        | oscc    | 0     | ON     | OFF              | OSC3 oscillator ON/OFF           |

|         |    |        |      |        | IOC1    | 0     | Output | Input            | I/O control register 1 (P10-P13) |

Table 4.3.1 Control bits of oscillation circuit and prescaler

\*1 Initial value at the time of initial reset

- \*2 Not set in the circuit

- \*3 Undefined

- \*4 Reset (0) immediately after being read

- \*5 Constantly "0" when being read

| OSCC:<br>OSC3 oscillation control | Controls oscillation ON/OFF for the OSC3 oscillation circuit.<br>(E0C6SA32 only.)                                                                                                                                                                                                                                           |                                                           |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|

| (0FEH-D1)                         | <ul> <li>When "1" is written : The OSC3 oscillation ON</li> <li>When "0" is written : The OSC3 oscillation OFF</li> <li>Read-out : Valid</li> <li>When it is necessary to operate the CPU of the E0C6SA32</li> <li>high speed, set OSCC to "1". At other times, set it to "0" to lessen the current consumption.</li> </ul> |                                                           |  |  |  |  |  |

|                                   | For the E0C6S32, 6SL32 and 6SB32, keep OSCC set to "0".<br>At initial reset, OSCC is set to "0".                                                                                                                                                                                                                            |                                                           |  |  |  |  |  |

| The CPU's clock switch            | The CPU's operation clock is selected with this register.<br>(E0C6SA32 only.)                                                                                                                                                                                                                                               |                                                           |  |  |  |  |  |

| (0FEH·D2)                         |                                                                                                                                                                                                                                                                                                                             | OSC3 clock is selected<br>OSC1 clock is selected<br>Valid |  |  |  |  |  |

|                                   | When the E0C6SA32's CPU clock is to be OSC3, set CLKCHG to "1"; for OSC1, set CLKCHG to "0". This register                                                                                                                                                                                                                  |                                                           |  |  |  |  |  |

|                                   | cannot be controlled for the E0C6S32, 6SL32 and 6SB32, so that OSC1 is selected no matter what the set value.                                                                                                                                                                                                               |                                                           |  |  |  |  |  |

|                                   | At initial reset, CLKCHG is set to "0".                                                                                                                                                                                                                                                                                     |                                                           |  |  |  |  |  |

| Programming notes | (1) It takes at least 5 ms from the time the OSC3 oscillation |

|-------------------|---------------------------------------------------------------|

| • •               | circuit goes ON until the oscillation stabilizes. Conse-      |

|                   | quently, when switching the CPU operation clock from          |

|                   | OSC1 to OSC3, do this after a minimum of 5 ms have            |

|                   | elapsed since the OSC3 oscillation went ON.                   |

|                   | Further, the oscillation stabilization time varies depend-    |

|                   | ing on the external oscillator characteristics and condi-     |

|                   | tions of use, so allow ample margin when setting the wait     |

|                   | time.                                                         |

|                   |                                                               |

(2) When switching the clock form OSC3 to OSC1, use a separate instruction for switching the OSC3 oscillation OFF. An error in the CPU operation can result if this processing is performed at the same time by the one instruction.

#### 4.4 Input Ports (K00-K03, K10)

## Configuration of input ports

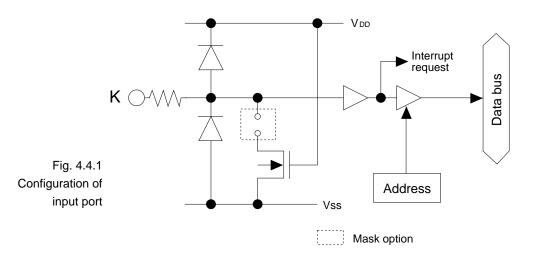

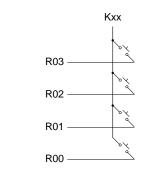

The E0C6S32 Series has five bits general-purpose input ports. Each of the input port terminals (K00–K03, K10) provides internal pull-down resistor. Pull-down resistor can be selected for each bit with the mask option. Figure 4.4.1 shows the configuration of input port.

Selection of "pull-down resistance enabled" with the mask option suits input from the push switch, key matrix, and so forth. When "pull-down resistance disabled" is selected, the port can be used for slide switch input and interfacing with other LSIs.

Further, the input port terminal K10 or K03 is used as the input terminals for the event counter. (See "4.10 Event Counter" for details.)

#### Differential registers and interrupt function

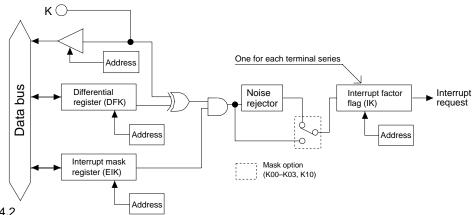

All five bits of the input ports (K00–K03, K10) provide the interrupt function. The conditions for issuing an interrupt can be set by the software. Further, whether to mask the interrupt function can be selected individually for all five bits by the software.

Figure 4.4.2 shows the configuration of K00–K03 and K10.

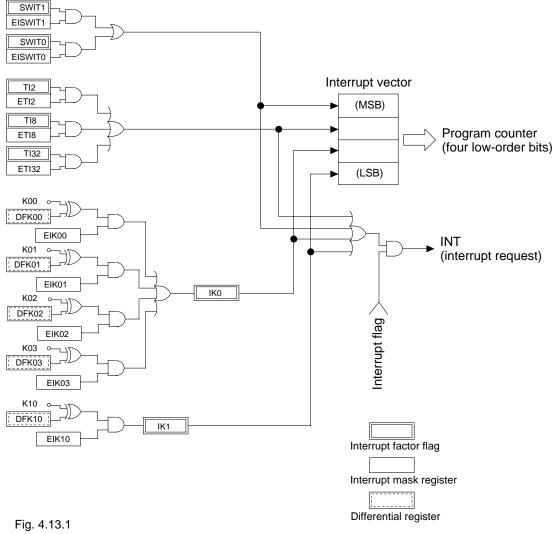

Fig. 4.4.2 Input interrupt circuit configuration (K00–K03, K10)

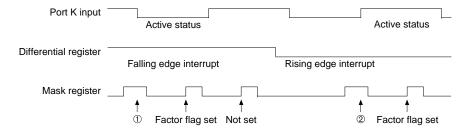

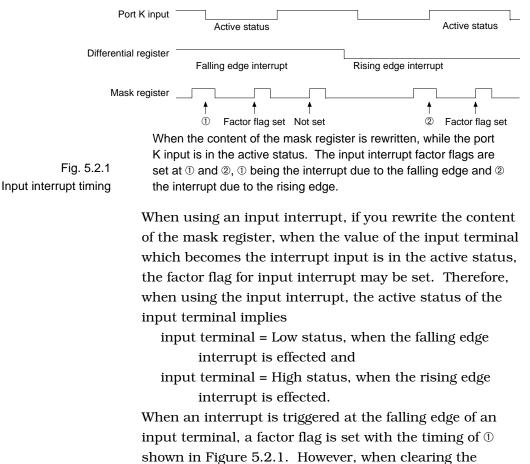

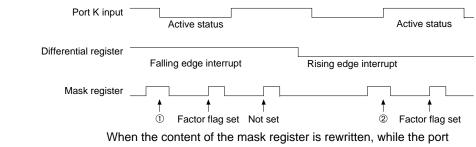

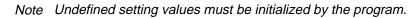

The input interrupt timing for K00–K03 and K10 depends on the value set for the differential registers (DFK00–DFK03 and DFK10). Interrupt can be selected to occur at the rising or falling edge of the input.

The interrupt mask registers (EIK00–EIK03, EIK10) enables the interrupt mask to be selected individually for K00–K03 and K10. However, whereas the interrupt function is enabled inside K00–K03, the interrupt occurs when the contents change from matching those of the differential register to non-matching contents. Interrupt for K10 can be generated by setting the same conditions individually.

When the interrupt is generated, the interrupt factor flag (IK0 and IK1) is set to "1".

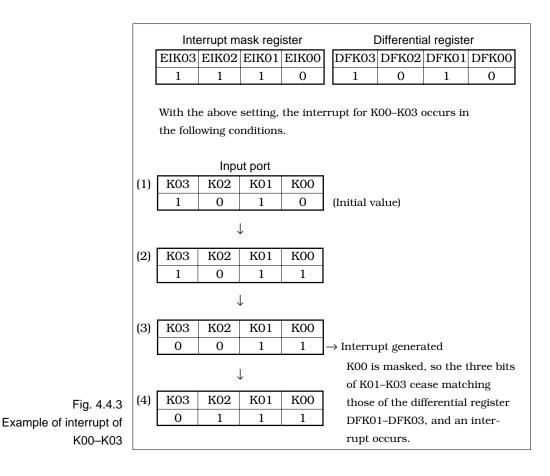

Figure 4.4.3 shows an example of an interrupt for K00–K03.

K00 is masked by the interrupt mask register (EIK00), so that an interrupt does not occur at (2). At (3), K03 changes to "0"; the data of the terminal that is interrupt enabled no longer matches the data of the differential register, so that interrupt occurs. As already explained, the condition for the interrupt to occur is the change in the port data and contents of the differential register from matching to nonmatching. Hence, in (4), when the nonmatching status changes to another nonmatching status, an interrupt does not occur. Further, terminals that have been masked for interrupt do not affect the conditions for interrupt generation.

## Mask optionThe contents that can be selected with the input port mask<br/>option are as follows:

- (1) Internal pull-down resistor can be selected for each of the five bits of the input ports (K00–K03, K10).

When you have selected "pull-down resistor disabled", take care that the floating status does not occur for the input. Select "pull-down resistor enabled" for input ports that are not being used.

- (2) The input interrupt circuit contains a noise rejector for preventing interrupt occurring through noise. The mask option enables selection of whether to use the noise rejector for each separate terminal series.When "Use" is selected, a maximum delay of 1 ms occurs from the time interrupt condition is established until the interrupt factor flag (IK) is set to "1".

## **Control of input ports** Table 4.4.1 list the input ports control bits and their addresses.

| Address |       | Reg   | ister |       |                     |       |         |        | Comment                                    |

|---------|-------|-------|-------|-------|---------------------|-------|---------|--------|--------------------------------------------|

| Address | D3    | D2    | D1    | D0    | Name                | SR *1 | 1       | 0      | Comment                                    |