CMOS 32-BIT SINGLE CHIP MICROCOMPUTER **E0C33 Family**

# **APPLICATION NOTES**

### **P**REFACE

Written for developers of application systems incorporating the E0C33 Family of microcomputers, this manual explains how to write a program, design basic circuitry, and produce audio output using the E0C33 chips, particularly the E0C33208. The sample code provided in this manual is excerpted from E0C33 Family C Compiler Package Ver. 2 or later.

### **CONTENTS**

| 1 | ABc   | OUT THE E0C33000 CPU CORE                | 1    |

|---|-------|------------------------------------------|------|

|   | 1.1   | Outline                                  | 1    |

|   | 1.2   | Memory Map                               | 2    |

|   | 1.3   | Trap Table                               | 2    |

|   | 1.4   | CPU Registers                            | 3    |

|   | 1.5   | Instruction Set Features                 | 3    |

|   | 1.6   | Instruction Execution Speed              | 6    |

|   | 1.7   | Multiplier/Accumulator Functions         | 7    |

|   | 1.8   | Instruction Set List                     | 8    |

| 2 | $W_R$ | RITING PROGRAMS FOR THE E0C33            | 9    |

|   | 2.1   | Vector Table and Boot Routine            | 9    |

|   | 2.2   | Interrupt Handling Routines              | . 14 |

|   | 2.3   | C and Assembler Mixed Programming        | . 17 |

|   | 2.4   | Tools and Files for Assembly             | . 19 |

|   | 2.5   | C and Code Optimization                  | . 29 |

|   | 2.6   | Mapping by Linker                        | . 37 |

| 3 | Pro   | OGRAMMING THE EOC33 PERIPHERAL FUNCTIONS | 41   |

|   | 3.1   | Setting Up BCU                           | . 41 |

|   | 3.2   | Setting Up the 8-bit Timer               | . 46 |

|   | 3.3   | Setting Up 16-bit Timer                  | . 49 |

|   | 3.4   | Setting Up Serial Interface              | . 54 |

|   | 3.5   | Setting Up A/D Converter                 | . 58 |

|   | 3.6   | About IDMA Settings                      | . 63 |

|   | 3.7   | Setting Up HSDMA                         | . 65 |

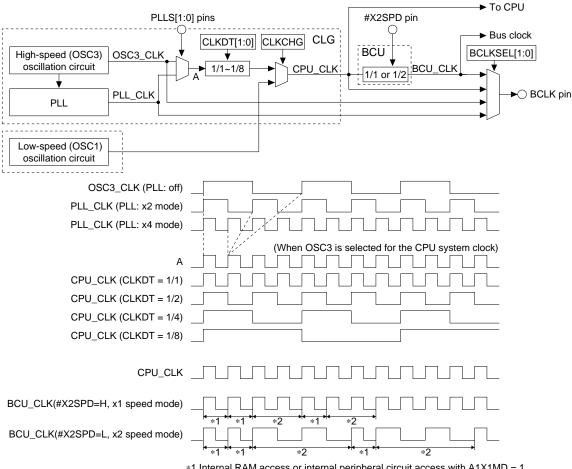

|   | 3.8   | Clock Settings                           | . 69 |

|   | 3.9   | SLEEP                                    | . 73 |

|   | 3.10  | Other Sample Programs                    | . 77 |

| 4 | Тн    | E BASIC E0C33 CHIP BOARD CIRCUIT         | 78   |

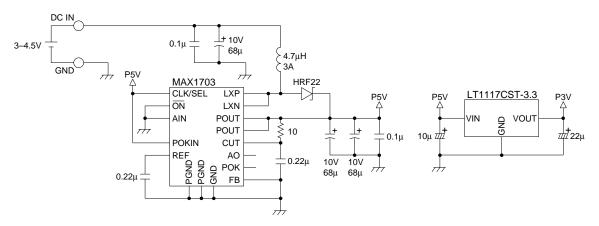

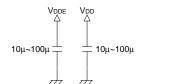

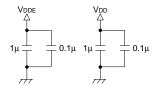

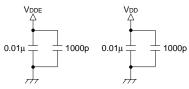

|   | 4.1   | Power Supply                             | . 78 |

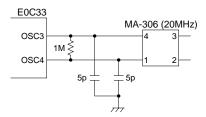

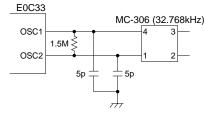

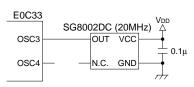

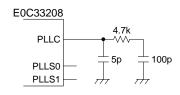

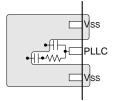

|   | 4.2   | Oscillation Circuit                      | . 80 |

|   | 4.3   | Reset Circuit                            | . 81 |

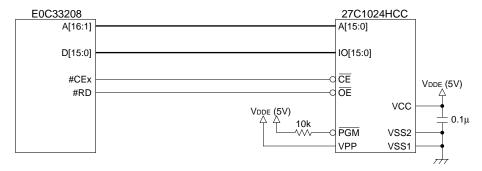

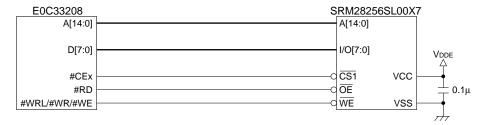

|   | 4.4   | Connecting ROM                           | . 83 |

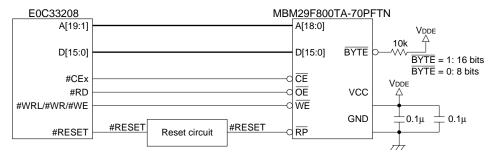

|   | 4.5   | Connecting Flash Memory                  | . 83 |

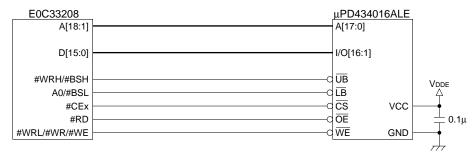

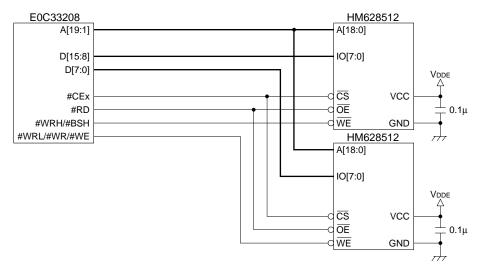

|   | 4.6   | Connecting SRAM                          | . 84 |

### CONTENTS

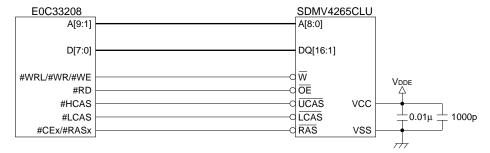

|   | 4.7  | Connecting DRAM                                              | 85       |

|---|------|--------------------------------------------------------------|----------|

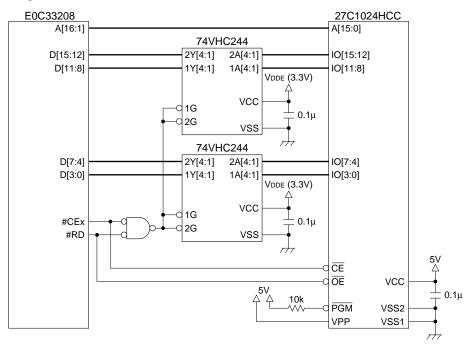

|   | 4.8  | Connecting 5 V ROM and 3.3 V Bus                             | 86       |

|   | 4.9  | Ports                                                        |          |

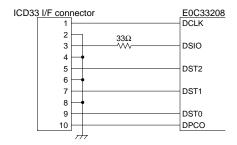

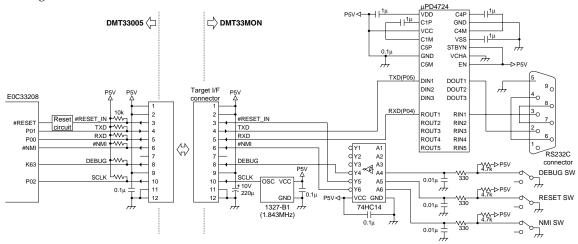

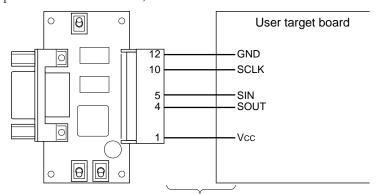

|   | 4.10 | Connections for Debugging                                    | 88       |

| 5 | SPE  | EAKER OUTPUT AND EXTERNAL ANALOG CIRCUIT USING FINE PWM _    | 90       |

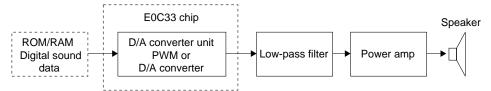

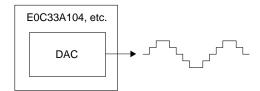

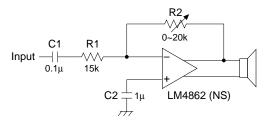

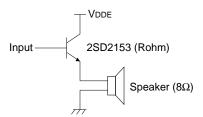

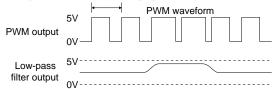

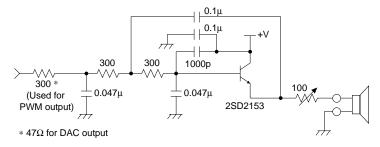

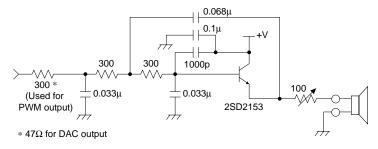

|   | 5.1  | General Sound Output Circuits Based on Microcomputer         | 90<br>93 |

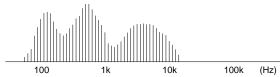

|   | 5.2  | About Sampling Frequency and Bit Precision vs. Audio Quality | 95       |

|   | 5.3  | 10-bit D/A Conversion by PWM                                 | 96       |

|   | 5.4  | Examples of Audio Output Analog Circuits                     | 99       |

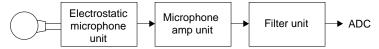

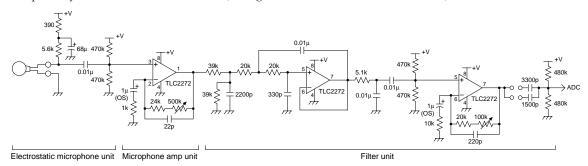

|   | 5.5  | Example of a Sound Input Analog Circuit                      |          |

|   | 5.6  | 15-bit D/A Conversion by PWM                                 | 107      |

|   | 5.7  | Melody Output using a Piezoelectric Buzzer                   | 112      |

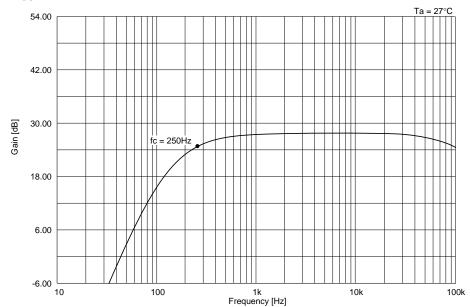

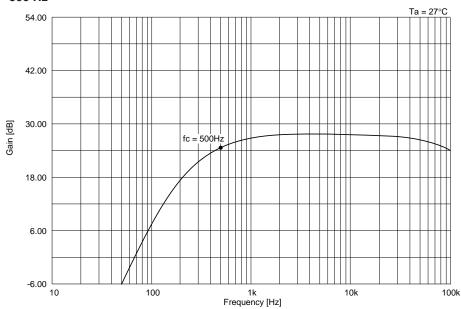

|   | 5.8  | Reference Data Characteristic Graphs                         |          |

# 1 ABOUT THE EOC33000 CPU CORE

The E0C33000 is the CPU core shared by all chips in the E0C33 Family of 32-bit CMOS single-chip microcomputers. Arranged around this core are various peripheral components, such as ROM, RAM, DMA, A/D converters, and timers, which together make up the Seiko Epson line of E0C33 Family processors.

The main features of the E0C33000 are as follows.

- A highly code-efficient instruction set

- Fast operation and multiplier/accumulator function

- Small CPU core size

- Low curr ent consumption

The E0C33000 supports a wide range of built-in applications, from portable to OA and FA equipment, and from digital signal processors to various types of controllers.

### 1.1 Outline

| • Type                            | . Seiko Epson original 32-bit RISC core                                                                                                                                                             |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating frequency               | . DC to 60 MHz (varies with the type of E0C33XXX)                                                                                                                                                   |

| • Instruction set                 | <ul><li>. 16-bit fixed length</li><li>105 discrete instructions</li><li>Main instructions can be executed in one cycle.</li></ul>                                                                   |

| • Multiplier/accumulator function | . MAC instruction (16 bits $\times$ 16 bits + 64 bits $\rightarrow$ 64 bits) Executed in 2 cycles per MAC operation                                                                                 |

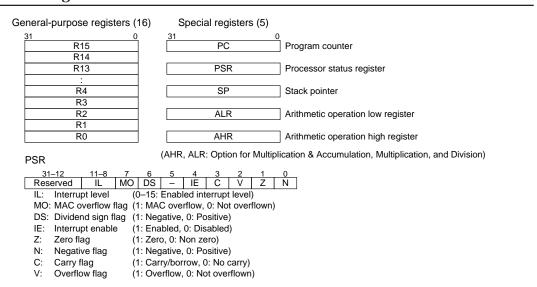

| • Register set                    | . 32-bit general-purpose register $\times$ 16 32-bit special register $\times$ 5                                                                                                                    |

| Memory space                      | . 28-bit (256 MB) space<br>Instruction, data, and I/O mixed type linear space<br>Divided into 19 areas, for which the select signal is output by the<br>core                                        |

| Immediate extension               | . Immediate data of instructions are extended to 32 bits by EXT instruction.                                                                                                                        |

| • Interrupt                       | Reset, NMI, and external interrupt × 216 sources Software exception × 4 sources, 2 types of instruction execution exception Vectors are fetched from trap table when branching to the jump address. |

| • Reset                           | Cold reset (all internal circuits reset) Hot reset (buses not reset) Trap table can be selected between internal or external ROM at boot time and can then be relocated.                            |

| Power-down mode                   | . HALT instruction (only the core halted) SLP instruction (all internal circuits halted)                                                                                                            |

| • Other                           | Little endian (standard)/ big endian<br>Harvard architecture                                                                                                                                        |

# 1.2 Memory Map

|           |         |                 | Area size |

|-----------|---------|-----------------|-----------|

| 0xFFFFFFF | Area 18 | External memory | 64MB      |

|           | Area 17 | External memory | 64MB      |

|           | Area 16 | External memory | 32MB      |

|           | Area 15 | External memory | 32MB      |

|           | Area 14 | External memory | 16MB      |

|           | Area 13 | External memory | 16MB      |

|           | Area 12 | External memory | 8MB       |

| 0x1000000 | Area 11 | External memory | 8MB       |

| 0x0C00000 | Area 10 | External memory | 4MB       |

| 0,0000000 | Area 9  | External memory | 4MB       |

|           | Area 8  | External memory | 2MB       |

|           | Area 7  | External memory | 2MB       |

|           | Area 6  | External I/O    | 1MB       |

|           | Area 5  | External memory | 1MB       |

| 0x0100000 | Area 4  | External memory | 1MB       |

| 0x0080000 | Area 3  | On-chip ROM     | 512KB     |

| 0x0060000 | Area 2  | Reserved        | 128KB     |

| 0x0040000 | Area 1  | Internal I/O    | 128KB     |

| 0x0000000 | Area 0  | On-chip RAM     | 256KB     |

|           | Area 0  | On-chip RAM     | 256KB     |

# 1.3 Trap Table

|                                 | Address offset |

|---------------------------------|----------------|

| Reserved                        | 1023           |

| External maskable interrupt 215 | 929            |

| :                               |                |

| External maskable interrupt 0   | 64             |

| Software exception 3            | 60             |

| :                               |                |

| Software exception 0            | 48             |

| Reserved                        | 32–44          |

| NMI                             | 28             |

| Address error                   | 24             |

| Reserved                        | 20             |

| Zero division                   | 16             |

| Reserved                        | 4–12           |

| Reset                           | 0              |

Trap table start address

At cold-reset, it is set to 0x0C00000.

The trap table can be relocated using the trap table base register TTBR (memory-mapped register) after resetting the CPU.

Vectors will be fetched from the trap table for booting and interrupts.

### Interrupt sequence

- 1) The PC is saved to the stack.

- 2) The PSR is saved to the stack and IE is disabled.

- 3) The vector is fetched from the trap table.

- 4) Control jumps to the vector address.

### Reset sequence

- 1) The reset vector is fetched.

- 2) Control jumps to the vector address.

## 1.4 CPU Registers

### 1.5 Instruction Set Features

### Types of instructions

Instructions are functionally classified as one of the following eight types:

#### 8, 16, or 32-bit data transfer instructions

LD.B, LD.UB, LD.H, LD.UH, LD.W

Performs 8, 16, or 32-bit data transfers between the register and memory, or between two registers.

#### 32-bit arithmetic/logic operation instructions

AND, OR, XOR, NOT, ADD, ADC, SUB, SBC, CMP, MLT.H, MLTU.H (16-bit), MLT.W, MLTU.W, DIV0S, DIV1S, DIV2S, DIV3S

Performs 32-bit arithmetic/logic operation on two register values, or on register and immediate values.

### • 32-bit shift and rotate instructions

SRL, SLL, SRA, SLA, RR, RL

Shifts or rotates 32-bit register data by 0 to 8 bits.

#### . Bit-manipulating instructions

BTST, BSET, BCLR, BNOT

Operates on byte data in memory to set or reset bitwise.

### • Stack-manipulating instructions

PUSHN, POPN

Saves or restores the contents of R0 to Rn successively to or from the stack.

#### Branch instructions

JRGT, JRGE, JRLT, JRLE, JRUGT, JRUGE, JRULT, JRULE, JREQ, JRNE, CALL, JP, RET, RETI, RETD, INT, BRK

Performs various conditional jump, call, or return operations.

#### System control instructions

HALT, SLP, NOP

Used to place the device in power-down mode or inserted to perform no operation.

#### Other instructions

MAC, SCAN0, SCAN1, SWAP, MIRROR, EXT

Performs a MAC, data scan, or replacement operation.

### Addressing modes

### (1) Basic addressing modes

These addressing modes can be implemented in one instruction.

### · 6-bit immediate data addressing

```

{\tt LD.W} \quad {\tt \$R1, sign6} \qquad Sign \ extends \ 6\text{-bit data before loading it into the R1 register.}

```

ADD %R2, imm6 Adds 6-bit data to the R2 register.

In this mode, the operations are performed upon 6-bit signed/unsigned immediate data and register.

### · Register direct addressing

```

LD.W %R1, %R2 Transfers data from the R2 to the R1 register.

JP %R3 Jumps to the address held by the R3 register.

In this mode, operations are performed only on register values.

```

### · Register indirect addressing

```

LD.B %R2, [%R15] Loads signed 8-bit data from the address specified by R15.

```

LD.W R2, [%R15] + Loads 32-bit data from the address specified by R15 and then increments the R15 register.

In this mode, a memory address is set in a register and operations are performed on data at that address.

### · SP indirect addressing with displacement

```

LD.UB R15, [$SP+imm6] Loads unsigned 8-bit data from the address indicated by SP + imm6. LD.W R15, [$SP+imm6] Loads 32-bit data from the address indicated by SP + (imm6 \times 4). In this mode, an offset address is specified from the stack pointer and operations performed on data within the stack.

```

### · Signed 8-bit PC relative addressing

| JP   | sign8 | Jumps to a location up to 127 instructions ahead of or 128 instructions behind |

|------|-------|--------------------------------------------------------------------------------|

|      |       | the current PC address.                                                        |

| CALL | sign8 | Calls a subroutine located up to 127 instructions ahead of or 128 instructions |

|      |       | behind the current PC address.                                                 |

In this mode, the jump address is specified by a relative address from the PC.

### (2) Extended addressing modes

The basic addressing modes can be extended with the EXT instruction.

### · Extended immediate data addressing

```

EXT imm13 + ADD %R1,imm6 \rightarrow ADD %R1,imm19

EXT imm13 + EXT imm13 + ADD %R1,imm6 \rightarrow ADD %R1,imm32

The immediate size can be extended to 19 or 32 bits with the EXT instruction.

```

#### Extended register indirect addressing

```

EXT imm13 + LD.W R2, [R15] + DD.W R2, [R15+imm13] EXT imm13 + EXT imm13 + LD.W R2, [R15+imm26] A 13-bit or 26-bit offset address can be added using the EXT instruction.

```

### · SP indirect addressing with extended displacement

```

EXT imm13 + LD.B %R15, [%SP+imm6] \rightarrow LD.B %R15, [%SP+imm19] EXT imm13 + EXT imm13 + LD.B %R15, [%SP+imm6] \rightarrow LD.B %R15, [%SP+imm32] The offset can be extended to 19 or 32 bits by the EXT instruction.

```

#### Extended PC relative addressing

```

EXT imm13 + CALL sign8 \rightarrow CALL sign21 EXT imm13 + EXT imm13 + CALL sign8 \rightarrow CALL sign31

```

The address range to which to branch may be extended to 22 or 32 bits by the EXT instruction.

### • Extended 3 operand mode

```

EXT imm13 + ADD %R1,%R2 \rightarrow ADD %R1,%R2,imm13 EXT imm13 + EXT imm13 + ADD %R1,%R2 \rightarrow ADD %R1,%R2,imm26

```

The instruction Reg1  $\leftarrow$  Reg1 OP Reg2 is changed to a 3-operand instruction Reg1  $\leftarrow$  Reg2 OP imm13/26 by the EXT instruction.

### High code density for C language

Based on the following two concepts, the E0C33 CPU core creates high code density for C language.

- 1. As often as possible, frequent operation patterns in C are processed by one instruction.

- 2. Other operation patterns are suppressed to as few instructions as possible using the EXT instruction, preventing worsening code density in less frequently used patterns.

### (1) Branch patterns

#### Conditional branch

```

JRNE sign8 (Jump area of +127 to -128 instructions)

Supports more than 90% of conditional branching cases with one instruction (2 bytes).

EXT imm13 + JRNE sign8 → JRNE sign21 (±1M jump area)

Supports other conditional branching with two instructions (4 bytes).

```

#### Subroutine call

```

EXT imm13 + CALL sign8 → CALL sign21 (±1M jump area)

Supports almost all subroutine calls with two instructions (4 bytes).

EXT imm13 + EXT imm13 + JRNE sign9 → JRNE sign31 (Can jump to any area)

Supports other subroutine calls with three instructions (6 bytes).

```

### (2) Variable access patterns

#### Auto variable access

```

LD.W %R2, [%SP+imm6] (Accesses SP + 0 to 255 area for int access) Supports more than 80% of auto-variable access cases with one instruction (2 bytes).

EXT imm13 + LD.W %R2, [%SP+imm6] \rightarrow LD.W %R2, [%SP+imm19] (Accesses 512K-byte area) Supports other auto-variable access cases with two instructions (4 bytes).

```

#### Pointer variable access

```

LD.B %R2, [%R3]

One instruction (2 bytes)

```

#### Static variable access (based on global pointer)

```

EXT imm13 + LD.H %R2, [%R8] → LD.H %R2, [%R8+imm13] (Accesses 4K-byte area from R8) Two instructions (4 bytes)

EXT imm13 + EXT imm13 + LD.H %R2, [%R8] → LD.W %R2, [%SP+imm26]

Three instructions (6 bytes)

```

#### (3) Arithmetic patterns

#### · 2-operand, register to immediate

```

ADD %R2,imm6 (Adds 0-63 to R2)

One instruction (2 bytes)

EXT imm13 + ADD %R2,imm6 → ADD %R2,imm19 (Adds 0-512K to R2)

Two instructions (4 bytes)

EXT imm13 + EXT imm13 + ADD %R2,imm6 → ADD %R2,imm32

Three instructions (6 bytes)

```

### · 2-operand, register to register

```

ADD %R2,%R3 (Adds R3 to R2)

One instruction (2 bytes)

```

#### • 3-operand, register to immediate

```

EXT imm13 + ADD %R2, [%R3] \rightarrow ADD %R2,%R3,imm13 (R2 = R3 + imm13)

Two instructions (4 bytes)

EXT imm13 + EXT imm13 + ADD %R2,imm6 \rightarrow ADD %R2,%R3,imm26 (R2 = R3 + imm26)

Three instructions (6 bytes)

```

#### 1 ABOUT THE E0C33000 CPU CORE

### (4) Other

#### · Call, return

CALL sign8 Saves PC automatically

RET Restores PC automatically

One instruction reduced for each

### • Push, pop

PUSHN %Rn Saves R0-Rn to the stack

POPN %Rn Restores R0-Rn from the stack

Number of instructions reduced for each subroutine

#### Data conversion

LD.B %R2, %R3 Converts signed 8-bit data to 32-bit data

LD.UB/LD.H/LD.UH Also supports signed/unsigned 8-bit and 16-bit data

Ideal for data cast in C

### • Bit manipulation

BSET [%R5], 2 Sets bit 2 of [%R5] (memory data in bytes) to 1

BCLR/BTST/BNOT Clears, tests, or inverts a bit

Permits read-modify-write operation with one instruction.

# 1.6 Instruction Execution Speed

The following shows the number of instruction cycles. Note that these apply when the program resides in internal ROM and data exists in RAM operating in the Harvard architecture. Wait cycles are added for access to external memory.

### Register to register operation (arithmetic, logic, system, etc.)

AND, OR, XOR, NOT, ADD, ADC, SUB, SBC, CMP, MLT.H, MLTU.H, DIV0S, DIV1S, DIV2S, DIV3S, SRL, SLL, SRA, SLA, RR, RL, HALT, SLP, NOP, LD.B, LD.UB, LD.H, LD.UH, LD.W

One cycle per instruction

MLT.W, MLTU.W

Five cycles per instruction

### • Memory to register operation (Id.w, Id.b, Id.ub, Id.h, Id.uh)

%RD, [%RB] (without interlock), [%RB], %RS, %RD, [%SP+imm6], [%SP+imm6], %RS, [%RB]+, %RS One cycle per instruction

%RD, [%RB]+, %RD, [%RB] (with interlock)

Two cycles per instruction

### . Memory to memory operation

BTST, BSET, BCLR, BNOT

Three cycles per instruction

#### Branch operation

JRGT, JRGE, JRLT, JRLE, JRUGT, JRUGE, JRULT, JRULE, JREQ, JRNE, JP

Ordinary branching: Two cycles per instruction; delayed jump (xxx.d): One cycle per instruction

CALL, JP, RET, RETI, RETD, INT, BRK

Two to 10 cycles per instruction

### · Other operations

MAC  $2 \times N + 4$  cycles PUSHN, POPN  $1 \times N$  cycles

SCAN0, SCAN1, SWAP, MIRROR One cycle per instruction

# 1.7 Multiplier/Accumulator Functions

The MAC instruction is capable of executing a 16 bits  $\times$  16 bits  $\times$  46 bits sum-of-products operation in one instruction every 2 clock periods, up to 2 G times.

Example: MAC %R13

R13: Repetition counter (maximum 4 G)

R14: Source 1 address (post incremented)

R15: Source 2 address (post incremented)

The source 1 and source 2 16-bit data are read from each memory location and multiplied. The 32-bit data resulting from the multiplication is added to a 64-bit register consisting of AHR:ALR. This is repeated once every 2 clock periods (given that source 1 and source 2 both exist in the internal RAM).

# 1.8 Instruction Set List

# Instruction format and operation

(The number of execution cycles applies here when the internal RAM is accessed for data with instructions residing in internal ROM.)

| Classification                                                 | Instruction                                                                | Typical instruction format | Operation                                    | Number of cycles                  |

|----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------|----------------------------------------------|-----------------------------------|

| Relative branch                                                | jp, jrgt, jrge, jrlt, jrle, jrugt, jruge, jrult<br>jrule, jreq, jrne, call | jp sing8                   | Branch to PC + (sign8 × 2)                   | 1,2(when branching)<br>3 for call |

| Relative delayed                                               | jp.d, jrgt.d, jrge.d, jrlt.d, jrle.d, jrugt.d                              | jp.d sing8                 | Branch to PC + (sign8 × 2)                   | 1                                 |

| branch                                                         | jruge.d, jrult.d, jrule.d, jreq.d, jrne.d, call.d                          |                            | Execute next instruction upon branching      | 2 for call                        |

| Absolute branch                                                | call, jp, call.d, jp.d                                                     | call %rb                   | Branch to address indicated by %rb           | 1–3                               |

| Special branch                                                 | ret, ret.d, int imm2, reti, brk, retb                                      |                            | Return, interrupt, etc.                      | 3–10                              |

| Logic operation                                                | and, or, xor, not                                                          | and %rd, %rs               | %rd = %rd & %rs                              | 1                                 |

|                                                                |                                                                            | and %rd, sign6             | %rd = %rd & sign6                            |                                   |

| Arithmetic                                                     | add, sub                                                                   | add %rd, %rs               | %rd = %rd + %rs                              | 1                                 |

| operation                                                      | ·                                                                          | add %rd, imm6              | %rd = %rd + imm6                             |                                   |

|                                                                |                                                                            | add %sp, imm12             | %sp = %sp + imm12                            |                                   |

| Compare                                                        | cmp                                                                        | cmp %rd, %rs               | %rd - %rs, flag only changes                 | 1                                 |

| operation                                                      | ·                                                                          | cmp %rd, sign6             | %rd - sign6                                  |                                   |

| Carry operation                                                | adc, sbc                                                                   | adc %rd, %rs               | %rd = %rd + %rs + carry flag                 | 1                                 |

| Multiplication                                                 | mlt.h, mlt.uh (16bit)                                                      | mlt.h %rd, %rs             | %alr = %rd × %rs (32 = $16 \times 16$ )      | 1                                 |

|                                                                | mlt.w, mlt.uw (32bit)                                                      |                            | %ahr:%alr = %rd × %rs (64 = $32 \times 32$ ) | 5                                 |

| Division                                                       | div0s, div0u, div1, div2s, div3s                                           |                            | Execute division using these in combination  | 1                                 |

| Shift srl, sll (logical shift) srl %rd, imm4 %rd = %rd >> imm4 |                                                                            | %rd = %rd >> imm4          | 1                                            |                                   |

|                                                                | sra, sla (arithmetical shift)                                              | srl %rd, %rs               | %rd = %rd >> %rs                             |                                   |

|                                                                | rr, rl (rotate)                                                            | ,                          | Shift by 0 to 8 bits                         |                                   |

| Memory load                                                    | ld.b (signed 8bit load)                                                    | ld.w %rd, [%sp+imm6]       |                                              | 1–2                               |

| ,                                                              | ld.ub (unsigned 8bit load)                                                 | ld.w [%sp+imm6], %rs       | [%sp+imm6] = %rs                             |                                   |

|                                                                | ld.h (signed 16bit load)                                                   | ld.w %rd, [%rb]            | %rd = [%rb], register address access         |                                   |

|                                                                | ld.uh (unsigned 16bit load)                                                | ld.w %rd, [%rb]+           | %rd = [%rb], %rb = %rb + 4, post inc.        |                                   |

|                                                                | ld.w (32bit load)                                                          | ld.w [%rb], %rs            | [%rb] = %rs                                  |                                   |

|                                                                | (====,                                                                     | ld.w [%rb]+, %rs           | [%rb] = %rs, %rb = %rb + 4                   |                                   |

| Register load                                                  | ld.w                                                                       | ld.w %rd, %rs              | Copy between registers                       | 1                                 |

|                                                                |                                                                            | ld.w %rd, sign6            | Store immediate value                        |                                   |

|                                                                |                                                                            | ld.w %rd, %ss              | Copy from special register                   |                                   |

|                                                                |                                                                            | ld.w %ss, %rs              | Copy to special register                     |                                   |

| Conversion                                                     | ld.b, ld.ub, ld.h, ld.uh                                                   | ld.b %rd, %rs              | Convert types                                | 1                                 |

| Bit operation                                                  | btst, bset, bclr, bnot                                                     | btst [%rb], imm3           | Test, set, clear, or invert a bit            | 3                                 |

| System                                                         | nop, slp, hlt                                                              |                            | No operation, stock clock                    | 1                                 |

| Mac operation                                                  | mac                                                                        |                            | Repeat %ahr:%alr= [%r14] × [%r15] +          | 2 × N + 4                         |

| p                                                              |                                                                            |                            | %ahr:%alr %r13 times                         |                                   |

| Stack operation                                                | pushn, popn                                                                | pushn %rs                  | Successively push/pop from %r0 to %rs        | 1 × N                             |

| Scan                                                           | scan0, scan1                                                               | scan0 %rd, %rs             | Scan 1 or 0 from MSB, up to 8 bits           | 1                                 |

|                                                                | ,                                                                          |                            |                                              | ·                                 |

| Swap                                                           | swap, miror                                                                | swap %rd, %rs              | Swap or mirror bits bytewise                 | 1 1                               |

signX, immX: immediate value, %XX: register

# • Immediate extension by EXT instruction

|          | Instruction only | One EXT instruction is added | Two EXT instructions are added |

|----------|------------------|------------------------------|--------------------------------|

|          | call sign8       | ext imm13                    | ext imm13                      |

| Example: |                  | call sign8 (= call sign21)   | ext imm13                      |

| •        |                  |                              | call sign8 (= call sign31)     |

| Classification | Instruction                                       | Typical format for 1 | Typical operation when 1 | Typical operation when 2   |

|----------------|---------------------------------------------------|----------------------|--------------------------|----------------------------|

| Ciassification | Instruction                                       | instruction          | EXT instruction is added | EXT instructions are added |

| Relative       | jp, jrgt, jrge, jrlt, jrle, jrugt, jruge, jrult,  | jp sing8             | jp sign21                | jp sign31                  |

| branch         | jrule, jreq, jrne, call, and delayed branch inst. |                      |                          |                            |

| 3-operand      | add, sub, and, or, xor, not, cmp                  | add %rd, %rs         | add %rd, %rs, imm13      | add %rd, %rs, imm26        |

| operation      |                                                   |                      | 3-operand operation      | 3-operand operation        |

| Operation      | add, sub, and, or, xor, not, cmp, ld.w            | add %rd, imm6 /sign6 | add %rd, imm19/sign19    | add %rd, imm32             |

| Stack load     | ld.b, ld.ub, ld.h, ld.uh, ld.w                    | ld.w %rd, [%sp+imm6] | [%sp+imm19]              | [%sp+imm32]                |

|                |                                                   | ld.w [%sp+imm6], %rs | Extend offset value      | Extend offset value        |

| Absolute load  | ld.b, ld.ub, ld.h, ld.uh, ld.w                    | ld.w %rd, [%rb]      | [%rb+imm13]              | [%rb+imm28]                |

|                |                                                   | ld.w %rd, [%rb]+     | Add offset value         | Add offset value           |

|                |                                                   | ld.w [%rb], %rs      |                          |                            |

|                |                                                   | ld.w [%rb]+, %rs     |                          |                            |

| Bit operation  | btst, bset, bclr, bnot                            | btst [%rb], imm3     | [%rb+imm13]              | [%rb+imm26]                |

|                |                                                   |                      | Add offset value         | Add offset value           |

signX, immX: immediate value, %XX: register

# 2 Writing Programs for the E0C33

This chapter explains how to write programs for the E0C33. The method described here applies to all microcomputers in the E0C33 Family.

### 2.1 Vector Table and Boot Routine

The E0C33 program must have at least a vector table and a boot routine. When cold reset at power-on, the E0C33 chip normally fetches the reset vector from address 0xC00000 and begins executing a program from that address. The simplest assembler resembles the one show below.

```

.abs

; Directive command located beginning with 0xC00000

0xc000000

.org

code

.word

BOOT

; Vector table (consisting of only one boot line)

BOOT:

xld.w

%r8,0x800

; Boot program

ld.w

%sp,%r8

; Sets SP and calls main

xcall

main

```

In addition, the actual application may require a vector table for exceptions and interrupts, and a boot routine that includes processing required to set up the BCU and initialize peripheral functions. Code examples, one in assembler and one in C, are provided below.

### Code example in assembler

The following code is included in cc33\sample\drv33a104\.

Vector table [drv33a104\16timer\vector.s]

```

. code

.word

RESET

; Vector table

RESERVED

.word

.word

RESERVED

RESERVED

.word

.word

ZERODIV

.word

RESERVED

ADDRERR

.word

.word

NMI

.word

RESERVED

.word

RESERVED

.word

RESERVED

RESERVED

.word

.word

SOFTINT0

.word

SOFTINT1

.word

SOFTINT2

.word

SOFTINT3

INTO

.word

INT1

.word

.word

INT2

.word

INT3

INT4

.word

.word

INT5

(INT6-INT49)

.word

INT50

.word

INT51

.word

INT52

.word

INT53

.word

INT54

INT55

.word

RESET:

; Dummy label for undefined vector

ZERODIV:

ADDRERR:

```

#### 2 WRITING PROGRAMS FOR THE E0C33

```

NMI:

RESERVED:

SOFTINTO:

SOFTINT1:

SOFTINT2:

SOFTINT3:

INTO:

INT1:

INT2:

INT3:

INT4:

INT5:

(INT6-INT49)

INT50:

INT51:

INT52:

INT53:

INT54:

INT55:

.global INT LOOP

INT LOOP:

; Trap routine for undefined vector

nop

INT LOOP

αĖ

reti

```

In this file, the vector table for boot to hardware interrupts is defined in the format

#### .word label

This allows storage of 32-bit jump addresses in the vector table. For safety, addresses that are not specifically defined are vectored to INT\_LOOP at the bottom of the file. Note that the program assumes the vectors actually used will be redefined by another name. (The processing routine may also be written by moving the jump address below to another location.)

When an invalid interrupt is generated, the CPU jumps to INT\_LOOP. It may be convenient to have a breakpoint set here when debugging the program. The address error exception (ADDRERR), 7th from the top in the vector table, occurs especially frequently in undebugged code. Although the address error exception in the preceding sample code is not separated from other exceptions or interrupts, we recommend that address invalid exceptions be vectored to another routine. Note that an address error exception occurs when an attempt is made to access an odd address during 16-bit memory read/writes, or when accessing a nonword-aligned address (not a multiple of 4) during 32-bit memory read/writes. In the E0C33, these memory accesses are prohibited.

### Redefinition of interrupt vectors [drv33a104\16timer\vector.h]

```

;; Vector define

#define

RESET

BOOT

#define

TNT12

int 16timer u00

#define

INT15

int 16timer c01

int 16timer u11

#define

TNT18

#define

INT23

int 16timer c21

int 16timer c31

```

Redefine the exception/interrupt vector labels actually used in vectors by another name, letting the CPU jump to the appropriate routine. In the preceding example, the reset vector and 16-bit timer interrupt vectors are redefined using the label names of the actual processing routines.

### Boot routine [drv33a104\common\boot.s]

```

/*

*/

Copyright (C) SEIKO EPSON CORP. 1997 - 1998

/*

*/

/*

File name: vector.h

/*

*/

This is interrupt vector header file.

/************************

#include

"..\bcu\drv bcu.h"

;; Stack top

#define SP_TOP

0 \times 0.7 ff

; sp is in end of 2KB internal RAM

;; Global pointer

#define GP ADDR

0x0000

; global pointer is 0x0

.code

;; BOOT

;;

Type:

void

Ret val: none

;;

;;

Argument: void

Function: Boot program.

.global BOOT

BOOT:

xld.w

%r8,SP TOP

; Set stack pointer

ld.w

%sp, %r8

xld.w

%r8,GP_ADDR

; Set global pointer

_init_bcu

; Initialize BCU on boot time in bcu.s

xcall

xcall

init_sys

; Call _init_sys() in sys.c to use simulated I/O

xcall

main

; Go to main

xcall

exit

; In last, go to exit in sys.c to use simulated I/O

;; _init_bcu

Type:

void

;;

Ret val: none

;;

Argument: void

;;

Function: Initialize BCU on boot time.

.global _init_bcu

init bcu:

;; Set area 9-10 setting

Area 9-10 setting ... Device size 16 bits, output disable delay 1.5,

;;

wait control 2, burst ROM is not used in area 9-10,

;;

burst ROM burst read cycle wait control 0

;;

xld.w

%r5,BCU A10 ADDR

xld.w

%r4,BCU BW 0 BCU DRAH NOT BCU DRAL NOT BCU SZL 16 BCU DFL 15 BCU WTL 2

ld.h

[%r5],%r4

ret.

```

This boot routine (BOOT) initializes the stack pointer, the R8 (used in ext33 for global pointer-based optimization), and the BCU before calling the main routine.

Since the CPU uses the stack if any exception or interrupt occurs, make sure the stack pointer is set before other processing. Always confirm that the BCU is set before accessing memory or device.

### Code example written in C

The following illustrative code is found in cc33\sample\drv33208\.

Vector table, boot routine [drv33208\16timer\vector.c]

```

/***********************

Copyright (C) SEIKO EPSON CORP. 1999

File name: vector.c

This is vector and interrupt program with C.

*************************

/* Prototype */

void boot(void);

void dummy(void);

extern void _init_bcu(void);

extern void _init_int(void);

extern void _init_sys(void);

extern void _exit(void);

extern void int 16timer c0 (void);

extern void int 16timer u1(void);

extern void int 16timer c2(void);

extern void int 16timer u3 (void);

/* vector table */

const unsigned long vector[] = {

(unsigned long)boot,

// 0

// 4

// 8

0,

// 12

Ο.

// 16

// 20

(unsigned long) dummy,

// 24

(unsigned long) dummy,

// 28

(unsigned long) dummy,

7

// 32

// 36

0,

// 40

// 44

// 48

10

0,

11

12

(unsigned long) dummy,

// <del>1</del>0

// 52

(unsigned long) dummy,

(56 14 - 120 30)

(unsigned long)int_16timer_c0, // 124

31

32

// 128 32

// 132 33

(unsigned long) dummy,

(unsigned long) dummy,

(unsigned long) int 16timer u1, // 136 34

(unsigned long) dummy,

// 140 35

(unsigned long) dummy,

(unsigned long) dummy,

(unsigned long) dummy,

// 144 36

// 148 37

38

(unsigned long) dummy,

// 164 41

(unsigned long) dummy,

(unsigned long)int_16timer_u3, // 168 42

(unsigned long) dummy,

// 172 43

(176 \ 44 - 268 \ 67)

// 272

(unsigned long) dummy,

(unsigned long) dummy,

(unsigned long) dummy,

68

// 276 69

// 280 70

(unsigned long) dummy

// 284 71

};

```

```

/****************************

* boot

Type :

void

Ret val : none

Argument : void

Function: Boot program.

void boot (void)

// Set SP in end of 8KB internal RAM

asm("xld.w %r8,0x2000");

asm("ld.w %sp,%r8");

asm("ld.w %r8,0b10000"); // Set PSR to interrupt enable

asm("ld.w %psr,%r8");

asm("ld.w %r8,0x0"); // Set GPR is 0x0

_init_bcu();

// Initialize BCU on boot time

_init_int();

// Initialize interrupt controller

_init_sys();

// Initialize for sys.c

main();

// Call main

_exit();

// In last, go to exit in sys.c to use simulated I/O

}

/*****************************

* dummy

Type :

void

Ret val : none

Argument : void

Function: Dummy interrupt program.

void dummy(void)

INT LOOP:

goto

INT LOOP;

asm("reti");

```

This file contains a vector table and a boot routine.

The vector table is defined as a const-type 32-bit array to allow storage of 32-bit jump addresses in ROM. The comment for each vector (//x y) is a decimal value indicating the offset address (x) from the top of the table and the vector number (y). In this example, the start addresses of externally-referenced interrupt processing functions are written directly. Unused interrupts are vectored to dummy routines.

The boot routine is functionally equivalent to the preceding example written in assembler. The SP and PSR are initialized using the asm() instruction.

The reti instruction for the dummy exception/interrupt handler routine is written using the asm() instruction.

# 2.2 Interrupt Handling Routines

This section describes interrupt handling routines, in particular methods for saving and restoring the registers. Other routines are written like other ordinary processing routines.

#### Routine written in assembler

Example for handling 16-bit timer interrupts [Excerpt from cc33\sample\drv33a104\16timer\demo\_16tint.s]

```

;; int 16timer u00

void

Type :

Ret val : none

;;

Argument : void

;;

Function: 16-bit timer 00 underflow interrupt function.

Read 16-bit timer 3 counter data and stop 16-bit timer 00.

.global int 16timer u00

int 16timer u00:

pushn

%r15

xld.w

%r12,T16P TC30 ADDR ; %r12 <- 16-bit timer 3 counter data reg. addr

; %r10 <- 16-bit timer 3 counter data

xcall

read 16timer cnt

[timer00],%r10

xld.w

xld.w

%r12,T16P PRUN00 ADDR

stop_16timer

; %r12 <- 16-bit timer 00 run/stop register addr

xcall

ld.w

%r4,0x01

; 16-bit timer 00 interrupt flag on

[t16int00 flg],%r4

xld.w

xld.w

%r5,INT F16T0 F16T1 ADDR ; %r5 <- Interrupt factor register address</pre>

%r4,INT F16TU00

xld.w

; Reset 16-bit timer 00 underflow int.factor flag

ld.b

[%r5],%r4

popn

%r15

reti

```

The start label of this routine (int\_16timer\_u00) is defined as a 16-bit timer interrupt vector (16-bit timer 00 underflow interrupt). When this interrupt occurs, the CPU saves the PC and PSR to the stack before executing this routine. Start by saving all general-purpose registers to the stack using pushn %r15. Then write the required processing code. Finally, restore the contents of the stack to the general-purpose registers using popn %r15, and return to the location where the interrupt occurred using reti. To return from the interrupt handling routine, you must use the reti instruction, which restores the PSR and PC to their states immediately before the interrupt occurrence.

Since multiply/divide operations or MAC operation are unnecessary in this example, the AHR and ALR registers will never be modified within the routine. But if you use the AHR and ALR registers, always save the contents of these registers to the stack, along with those of general-purpose registers, as shown below.

```

pushn

%r15

ld.w

%r0,%ahr

ld.w

%r1,%alr

pushn

%r1

popn

%r1

%ahr,%r0

ld.w

ld.w

%alr,%r1

ngog

reti

```

Conversely, if register use is limited, there is no need to save all general-purpose registers. For example, if you are using only R0 to R3, specify R3 in the pushn and popn instructions. Limiting the registers to be saved helps reduce time and the stack area required for the save.

#### Routine written in C

Example for handling 16-bit timer interrupts [Excerpt from cc33\sample\drv33208\16timer\demo\_16tint.c]

```

* int 16timer c0

Type :

void

Ret val : none

Argument : void

Function: 16bit timer0 comparison match A interrupt function.

******************************

void int 16timer c0(void)

extern volatile int timer0;// Timer counter variable for 16bit timer0

INT BEGIN;

timer0 = read 16timer cnt(T16P TC3 ADDR);

*(volatile unsigned char *) INT F16T0 F16T1 ADDR = INT F16TC0;

// Reset 16bit timer0 comparison match A interrupt factor flag

stop_16timer(T16P_PRUN0_ADDR);

INT END;

```

The respective processing for saving and restoring the registers is defined in INT-BEGIN and INT\_END, as follows:

Here, all general-purpose registers are saved and restored as in the example written in assembler.

Save all general-purpose registers with C, since you do not know which registers will be used. You may also need to save the AHR and ALR registers. In C, multiplication operations are used to calculate addresses for array processing, not just for multiply/divide operations.

Variables in C are sometimes saved to the stack using the pushn instruction. In this case, the preceding example may operate erratically, since the stack pointer loses consistency. This is because the preceding example contains popn and ret after reti, which means popn will not be executed. For this processing, use the sed exe file provided as a utility. The following example illustrates this, using cc33\sample\int\_c as an example.

\$ (SED) -f int.sed int.ps > int.ps2 \$ (EXT33) \$ (EXT33\_FLAG) int.ps2 int.o: int.ms \$ (AS33) \$ (AS33\_FLAG) int.ms

Here, int.c is filtered by sed after being compiled.

(Filter definition in int.sed)

```

pushn.*/;/

s/

popn.*/;/

s/

s/; \.frame.*/;/

\.mask.*/;/

s/;

pushn

\.fmask.*/

%r15\

s/;

ld.w %r0,%ahr\

%r1,%alr\

ld.w

ld.w

%r2,%sp\

pushn %r2/

s/ret/popn %r2\

%ahr,%r0\

ld.w

ld.w

%alr,%r1\

ld.w

%sp,%r2\

%r15\

ngog

reti/

```

#### 2 WRITING PROGRAMS FOR THE E0C33

For example, the SED processing result of the div0() function in int.c is like the one shown below.

```

void div0()

{

int_num = 4;

00060 void div0()

00080068 020F pushn

%r15

00061

0008006A A430 ld.w

%r0,%ahr

0008006C A421 ld.w

%r1,%alr

%r2,%sp

0008006E A412 ld.w

00080070 0202 pushn

%r2

00080072 6C4A ld.w

%r10,0x4

00062

int num = 4;

00080074 C000 ext

0x0

00080076 C000 ext

0x0

00080078 3C8A ld.w

[%r8],%r10

0008007A 0242 popn

00063

}

%r2

0008007C A003 ld.w

%ahr,%r0

0008007E A012 ld.w

%alr,%r1

00080080 A021 ld.w

%sp,%r2

00080082 024F popn

%r15

00080084 04C0 reti

```

In this way, the code required to save and restore the general-purpose registers R0–R15 and other registers AHR, ALR, and SP is added before and after function processing, with the reti instruction used for return.

Note: Files processed by sed may not have any function written in them other than exception/interrupt handling.

# 2.3 C and Assembler Mixed Programming

Control can pass between C and assembler routines as desired, providing that rules for arguments, return values, and register content protection are observed.

### Creating an assembler routine called from C

cc33\utility\lib\_src\ansilib33\string\src\strcpy.s

```

string copy from src to dest until 0 terminate

; arguments : %r12:dest addr, %r13:src addr (0 terminate string)

; return : %r10:dest addr

.qlobal strcpy

strcpy:

ld.w

%r10, %r12

; return dest add

strcpy loop:

ld.ub

%r4, [%r13]+

; copy src 1 byte to dest

[%r12]+, %r4

cmp

%r4, 0

; continue until 0 terminate

jrne strcpy loop

ret

```

This routine is called from a C routine as follows.

(Excerpt from cc33\sample\ansilib\sansilib.c)

The first and the second arguments are respectively placed in the R12 and the R13 registers when passed, and the return value is stored in the R10 register.

As in this example, arguments and return values must be exchanged using registers, as follows:

- The first to fourth arguments are placed in the R12 to the R14 registers when passed.

- In special cases, the preceding arguments and the fifth and subsequent arguments are placed in the stack when passed. (Refer to the compiled code.)

- The return value is stored in the R10 register when returned.

The limitations on register usage within the assembler routine called from a C routine are as follows:

- The R0 to R3 registers must be restored directly without modifying their contents when called. When using these registers, use the pushn/popn instructions to save and restore their contents.

- The contents of the R4 to R15 registers do not need to be saved. However, avoid using registers R9 and R8 whenever possible, since R9 is used to expand the extend instructions of ext33, while R8 is used for global pointer-based optimization by ext33. Be especially careful if you do use these registers

- The contents of the AHR, ALR, and PSR registers do not need to be saved.

For example, cc33\utility\lib\_src\emulib33\fp\src\adddf3.s processes double-precision, floating-point additions. Since this routine uses all registers, the contents of the R0 to R3 registers are saved and restored before returning.

```

__adddf3:

pushn %r3 ; save register values

popn %r3 ; restore register values

ret

```

### • Creating an assembler routine that calls a C function

C functions are compiled by the preceding rules. When creating an assembler routine that calls a C function, pay attention to the following:

### Rules for delivering arguments and return values

- The first to fourth arguments are placed in the R12 to R14 registers when passed.

- The R10 register is used to receive the return value.

### Register status at return

- The R0 to R3 registers hold the contents possessed when called.

- The R4 to R15 registers and other registers AHR, ALR, or PSR may have been modified.

# 2.4 Tools and Files for Assembly

The user-created assembly source files are assembled using the following three software tools:

| Tools                         | Input files           | Output files    |

|-------------------------------|-----------------------|-----------------|

| 1. Preprocessor pp33          | ${\rm file.} {\bf s}$ | file. <b>ps</b> |

| 2. Instruction extender ext33 | file. <b>ps</b>       | file. <b>ms</b> |

| 3. Assembler as33             | file.ms               | file. <b>o</b>  |

<sup>\*</sup> The assembly sources (.ps) obtained by compiling C sources cannot be fed into the preprocessor pp33. They must be entered to ext33.

### Types of assembly source files

Shown below are an example and the differences between each assembly source file (.s, .ps, and .ms).

#### Assembly source (.s) created by user

```

; boot.s

; boot program

#define SP INI 0x0800

; sp is in end of 2KB internal RAM

(1)

#define GP INI 0x0000 ; global pointer %r8 is 0x0

(1)

.code

(3)

.word

BOOT

; BOOT VECTOR

(3)

BOOT:

(2)

xld.w

%r8,SP INI

ld.w

%sp,%r8

; set SP

ld.w

%r8,GP INI

; set global pointer

xcall

main

; goto main

(2)

(2)

BOOT

; infinity loop

```

- (1) Quasi directives processed by pp33

- (2) Extended instructions processed by ext33

- (3) Directive commands processed by as33

Processing this file by pp33 results in the following:

### Preprocessor output file (.ps)

```

.file

"boot.s"

(3)

; boot.s

; boot program

; sp is in end of 2KB internal RAM

;#define SP INI 0x0800

(1)

;#define GP INI 0x0000

; global pointer %r8 is 0x0

.code

.word BOOT

; BOOT VECTOR

BOOT:

.loc

(3)

%r8,0x0800

xld.w

(2)

.loc

(3)

11

ld.w

%sp,%r8

; set SP

.loc

12

(3)

%r8,0x0000

; set global pointer

(2)

ld.w

13

(3)

.loc

; goto main

xcall

main

(3)

.loc

14

BOOT

; infinity loop

xjp

.endfile

(3)

```

Shown below are sections of the .s file processed by pp33.

- (1) The directive commands of pp33 beginning with # are processed, with the statements themselves changed to comments.

- (2) When the symbol defined by #define in (1) appears, it is replaced with the value or string defined for that symbol.

- (3) When pp33 is executed after specifying the -g option, the information necessary for source-level debugging is inserted.

Processing this file by ext33 results in the following:

#### Instruction extender output file (.ms)

```

.file

"boot.s"

; boot.s

; boot program

;#define SP INI 0x0800

; sp is in end of 2KB internal RAM

;#define GP INI 0x0000

; global pointer %r8 is 0x0

.code

.word BOOT

; BOOT VECTOR

BOOT:

.loc

10

ext

0x20

xld.w %r8,0x0800

(1)

ld.w

%r8,0x0

.loc

11

ld.w

%sp,%r8

; set SP

.loc

12

ld.w

%r8,0x0000

; set global pointer

.loc

13

main@rh

xcall main

(2)

ext

; goto main

ext

main@rm

main@rl

call

.loc

14

дį

BOOT

хjр

BOOT

; infinity loop

(3)

.endfile

```

Shown below are sections of the .ps file processed by ext33.

The extended instructions of ext33 beginning with x in (1) to (3) are expanded into the basic as33 instructions according to operand values. At this time, the number of instructions expanded is limited to the smallest possible.

- (1) is expanded into two instructions required for the immediate data of 0x800.

- (2) is a label in another file and its address unknown; it is expanded into three instructions that can always be called.

- (3) is a label within the same file, so that its relative address is calculated; as a result, it is expanded into one instruction.

#### Preprocessor instructions

The instructions beginning with "#" are quasi preprocessor directives, which provide additional functions, such as macro instructions, conditional assembly instructions, or symbol definitions of values and strings, which help create readable assembler code. These instructions are processed by pp33 and expanded into basic instructions that can be assembled by as33. The operators used to specify numeric values with an expression are also processed by pp33.

### Preprocessor quasi directives [cc33\sample\asm\pp.s]

```

1998.1.5

; sample source for pp33

#include "pp.def"

; include file

#define SP_IRAM

; definition for #ifdef

#ifdef SP IRAM

; condition assemble

#define SP INIT ADDR 0x400

; set number to defnum symbol

#else

#define SP INIT ADDR 0x880000

#endif

#define BLK ADDR 0x0+0x10

; You can use arithmetic operators.

; operators : +,-,*,/,%%,>>,<<,&,!,^,~,; ^H,^M,^L,^AH,^AL,(,)

#define gpr %r8

#define GP INIT ADDR 0x0

```

```

#macro FILL AREA $1 $2 $3

; macro argument is $1, $2, --- $32

xld.w

%r1,$1

; $1 is start address

%r2,$2

; $2 is fill pattern (8bit)

xld.w

xld.w

%r3,$3

; $3 is fill size (byte address)

$$1:

; $$1 -- $$64 is local jump label

cmp

%r3,0

$$2

jreq

ld.b

[%r1]+,%r2

sub

%r3,1

$$1

jр

$$2:

#endm

.word BOOT

BOOT:

ext

SP_INIT_ADDR^H

SP_INIT_ADDR^M

ext

ld.w

%r0,SP_INIT_ADDR^L

ld.w

%sp,%r0

gpr, GP INIT ADDR

ld.w

BLK ADDR 0b01010101 10

FILL AREA

; fill 0x10-0x1f with 0x55

BLK ADDR+0x10 0 10

; fill 0x20-0x2f with 0x00

FILL_AREA

BOOT

```

#### Assembler directive commands

The assembler directive commands beginning with "." are primarily used to define data written into sections and ROM. The assembler directive commands are not processed until fed into as33.

Assembler directive commands [cc33\sample\asm\as\_directive.ms]

```

; absolute file

; as directive.ms

1997.2.15

; sample source for as33 directives

.set RAM1 0x0

; set absolute data

.code

; start code section

.global BOOT

; BOOT become global symbol

0x80000

; set absolute address

.org

BOOT

: 32bit data

.word

BOOT:

; label in code section

ld.w

%r8,0

xld.w

%r1,[DATA1]

xld.w

[RAM1],%r1

xld.ub

%r2, [DATA1+8]

xld.b

[COMM1],%r2

qį

BOOT

.half

0x0000

; same with nop

.data

; start data section

; align to 4 byte boundary

.align

DATA1:

; label in data section

; 32bit data

.word

0x12345678

.half 0x1234,0x5678

; 16bit data

.byte

0x90

; 8bit data

.ascii

"abc"

; string data

4

; 4bytes 0

.space

.org

0x0

. COMM

COMM1 4

; 4 byte global bss data area

; 4 byte local bss data area

.lcomm

LCOMM1 4

```

### Primary assembler instructions

When programming with the assembler, the programmer must understand how to write the following instructions.

- Instructions supported by as33 and owned by the CPU core itself (basic instructions)

- Macro instructions expanded by ext33 (extended instructions)

Pooling all instructions of these two types produces a large number of available instructions, particularly an extensive list of instructions for ext33.

Until you are familiar with programming the E0C33, we recommend using the two types of extended instructions shown below and the primary basic instructions of the CPU core, and then gradually increasing the number of extended instructions according to the purposes.

### Two types of extended instructions

```

xld.w %r8,0x12345678 ; Stores immediate value in register

xcall sub ; Call to label

```

### Commonly used basic instructions

### **Arithmetic operation**

%r1,%r2

%r3,3

```

adc %r5,%r3

cmp %r7,%r9

cmp %r15,-1

mlt.h %r9,%r8 ; unsigned mltu.h and mltu.w also available

mlt.w %r1,%r2 ; div is supported in subroutine form

```

; Same as for sub and sbc

### Logical operation

```

and %r2,%r1 ; Same as for or and xor

and %r1,0b0111

not %r2,%r1

not %r1,-1

```

### **Shift**

add

add

```

srl %r10,5 ; Same as for sll, sra, sla, rr, and rl

srl %r9,%r5

```

### Register copy

```

ld.b %r2,%r3 ; Same as for ld.ub, ld.h, ld,uh, and ld,w

ld.w %r8,%alr ; Same as for sp, ahr, alr, and psr

ld.w %sp,%r9

```

#### Memory access

```

ld.b %r9,[%r9] ; Same as for ld.ub, ld.h, ld,uh, and ld,w

ld.b %r15,[%r0]+

ld.b [%r3],%r2 ; Same as for ld.h, and ld.w

ld.b [%r4]+,%r0

btst [%r9],0x1 ; Same as for bset, bclr, and bnot

```

### **Branch**

```

jrgt SYM ; Same as for jrXX, jp, jrXX.d, and jp.d

```

### Return

ret.d

#### Interrupt

```

reti

int 3

```

#### **Extended instruction**

```

ext  0x123

Other

pushn %r15

popn %r0

mac %r12

nop

halt

slp

```

#### Basic instructions

Basic instructions refer to the E0C33000 instruction set, which are assembled into machine codes by as33. Write the core CPU mnemonics directly as is. For operands that specify addresses with immediate data, you may write a predefined label by itself, or in combination with displacement or symbol mask.

```

Example: jr LABEL ; Specify label

ext LABEL+4@h ; Specify label + displacement + symbol mask

ext LABEL+4@m

ld.w %r9,LABEL+4@l

ld.w %r1,[%r9]

```

The following lists the basic instructions. The instructions in bold can be written only in basic instructions, while the others can be written in the extended ext33 instructions.

### Basic instruction list [cc33\sample\asm\as\_inst.ms]

```

; as inst.ms

1997.2.23

; shift & rotation operations

; sample source for as33 instructions

%r10,5

srl

srl

%r9,%r5

; arithmetic operations

sll

%r10,5

%r9,%r5

%r1,%r2

sll

add

add

%r3,3

sra

%r10,5

add

%sp,0x123

%r9,%r5

sra

%r5,%r3

adc

sla

%r10,5

%r1,%r2

%r9,%r5

sub

sla

%r3,3

sub

rr

%r10,5

sub

%sp,0x123

%r9,%r5

rr

%r5,%r3

%r10,5

sbc

rl

cmp

%r7,%r9

rl

%r9,%r5

%r15,-1

cmp

mlt.h

%r9,%r8

; etc

mltu.h

%r7,%r4

pushn

%r15

mlt.w

%r1,%r2

popn

%r0

mltu.w

%r5,%r1

mac

%r13

div0s

%r1

nop

div0u

%r2

halt

div2s

%r3

slp

div3s

scan0

%r1,%r2

%r3,%r4

scan1

; logical operations

%r5,%r6

swap

and

%r2,%r1

mirror

%r7,%r7

and

%r1,0b0111

or

%r2,%r1

; bit operations

or

%r1,11

btst

[%r9],0x1

%r2,%r1

bset.

[%r0],7

xor

%r1,0x11

bclr

[%r15],0b1

xor

not

%r2,%r1

bnot.

[%r10],5

not

%r1,-1

```

#### 2 WRITING PROGRAMS FOR THE E0C33

```

; ext operations

irlt.d

SYM@rl

ext

0x123

irle

-1

jrle

SYM

SYM@ah

ext.

ext

SYM+0x56@ah

jrle

SYM@rl

SYM@al

jrle.d

ext.

ext.

SYM+0x56@al

jrle.d

SYM

ext.

SYM@h

irle.d

SYM@rl

SYM+0x56@h

ext

iruqt

-1

SYM

ext

SYM@m

jrugt

SYM@rl

SYM+0x56@m

jrugt

ext

ext

SYM@rh

jrugt.d 2

jrugt.d SYM

ext

SYM@rm

jrugt.d SYM@rl

; load operations

-1

jruge

ld.b

%r2,%r3

SYM

jruge

ld.b

%r9,[%r9]

jruge

SYM@rl

ld.b

%r15,[%r0]+

jruge.d 2

jruge.d SYM

jruge.d SYM@rl

ld.b

%r6,[%sp+8]

ld.b

[%r3],%r2

ld.b

[%r4]+,%r0

jrult

- 1

ld.b

[%sp+0x10],%r11

jrult

SYM

ld.ub

%r2,%r3

jrult

SYM@rl

ld.ub

%r9,[%r9]

jrult.d 2

ld.ub

%r15,[%r0]+

jrult.d SYM

ld.ub

%r6,[%sp+8]

jrult.d SYM@rl

%r2,%r3

ld.h

jrule

-1

ld.h

%r9,[%r9]

jrule

SYM

ld.h

%r15,[%r0]+

jrule

SYM@rl

ld.h

%r6,[%sp+8]

jrule.d 2

jrule.d SYM

ld.h

[%r3],%r2

ld.h

[%r4]+,%r0

jrule.d SYM@rl

ld.h

[%sp+0x10],%r11

-1

jreq

ld.uh

%r2,%r3

SYM

jreq

ld.uh

%r9,[%r9]

SYM@rl

jreq

ld.uh

%r15,[%r0]+

jreq.d

ld.uh

%r6,[%sp+8]

jreq.d

SYM

jreq.d

ld.w

SYM@rl

%r2,%r3

ld.w

%r8,%alr

jrne

-1

ld.w

%sp,%r9

jrne

SYM

SYM@rl

ld.w

%r9,[%r9]

jrne

ld.w

%r15,[%r0]+

jrne.d

2

ld.w

%r6,[%sp+8]

irne.d

SYM

ld.w

[%r3],%r2

jrne.d

SYM@rl

ld.w

[%r4]+,%r0

call

_ 1

ld.w

[%sp+0x10],%r11

call

SYM

ld.w

%r9,SYM@l

call

SYM@rl

call

%r5

; branch operations

call.d 2

call.d SYM

jrqt

-1

jrqt

SYM

call.d SYM@rl

SYM@rl

call.d

%r8

jrgt

jrgt.d

2

-1

jр

jrgt.d

SYM

SYM

qŗ

SYM@rl

SYM@rl

jrgt.d

jр

%r5

jrge

- 1

jр

jp.d

jrge

SYM

2

jrge

SYM@rl

jp.d

SYM

SYM@rl

jrge.d

2

jp.d

jrge.d

SYM

jp.d

%r8

jrge.d

SYM@rl

ret

jrlt

- 1

ret.d

SYM

reti

jrlt

SYM@rl

retd

jrlt

jrlt.d

2

int

3

jrlt.d

SYM

brk

```

### Extended instructions

The extended instructions beginning with "x" are provided to facilitate the use of the instruction extension function supported by the ext instruction. These extended instructions are expanded into basic instructions with or without the ext instruction according to the operand value.

### Extended instructions [cc33\sample\asm\ext.ms]

```

1997.4.30

; ext.ms

; sample source for ext33 extended instructions

; not for execution, just for ext33 extension only

.word BOOT

BOOT.

; summary of major patterns

; xld.w

xld.w

%r8,0

; immediate load

; symbol immediate load

w.blx

%r1,DATA1

xld.w

%r2,DATA1+4

; symbol+offset

xadd

%r1,%r2,0x12345678

; 3 operand for xadd, xsub

xand

%r14,%r15,0xff000000

; 3 operand for xand, xoor, xxor

%r8,0b1111100000

xnot.

xsrl

%r3,8

; immediate shift

%r7,%r8

; register shift

xrr

; for xsrl, xsll, xsra, xsla, xrr, xrl

; immediate address

xld.w

%r1,[0x1234568]

xld.ub %r5,[DATA1]

; symbol address

; symbol address + offset

xbtst

[COMM1+0x400], 2

xld.uh %r10,[%sp+0x222]

; sp relative

xld.b

[%sp],%r7

; sp relative

xld.uh %r1,[%r15+0x1234568]

; resister + immediate address

xld.h %r5,[%r11+DATA1]

; register + symbol address

[%r9+COMM1+0x400],2

; register + symbol address + offset

xbset.

; for xld.w, xld.uh, xld.h, xld.ub, xld.b,

xbset, xbclr, xbtst, xbnot

; immediate relative

xjp

-2

xjrgt.d BOOT

; symbol relative

; for xjp, xjreq, xjrne, xjrgt, xjrge, xjrlt,

; xjrle, xjrugt, xjruge, xjrult, xjrule, xcall

; And with ".d"

; more detail samples

; xld.w

load immediate to register operation

xld.w

%r8,0

; decimal

%r0,0x12345678

xld.w

; hex

xld.w

%r0,0b10101

; binary

xld.w

%r1,DATA1

; symbol

%r2,DATA1+4

xld.w

; symbol+offset(hex,dec,bin)

xld.w

%r2,DATA1+0x5

xld.w

%r2,DATA1+0b110

; xadd, xsub add and sub, arithmetic operations

xadd

%r1,%r2,0x12345678

; 3 operand No.1

xsub

%r2,%r1,0x12345

; 3 operand No.2

xadd

%r0,%r1,1

; 3 operand No.3

xsub

%r2,%r2,5

; 3 operand No.4

; for C compiler

xadd

%r1,%r2,%sp

%sp, %sp, %r1

; for C compiler

xsub

; xand, xoor, xxor, xnot

and, or, xor, and not, logical operations

%r14,%r15,0xff000000

; 3 operand No.1

xand

%r12,%r11,0xfedc

; 3 operand No.2

; 3 operand No.3

xxor

%r9,%r9,-1

%r8,0b1111100000

xnot

```

```

; xsrl, xsll, xsra, xsla, xrr, xrl

shift operations

%r3,8

; immediate shift No.1

xsrl

; immediate shift No.2

xsll

%r4,15

; immediate shift No.3

xsra

%r5,17

xsla

%r6,31

; immediate shift No.4

xrr

%r7,%r8

; register shift

; xld.w, xld.uh, xld.h, xld.ub, xld.b, xbset, xbclr, xbtst, xbnot

load, bit operation from/to absolute address

xld.w

%r1,[0x1234568]

; immediate address No.1

; immediate address No.2

xld.uh %r2,[0xABC]

; immediate address No.3

[10], %r3

xld.h

; immediate address No.4

xld.ub

%r4,[0]

; symbol address No.1

xld.b

%r5,[DATA1]

[COMM1],1

; symbol address No.2

xhnot.

xbtst

[COMM1 + 0x400], 2

; symbol address + offset No.1

xbset

[COMM1+0x10],3

; symbol address + offset No.2

[COMM1+1], 4

; symbol address + offset No.3

xbclr

; xld.w, xld.uh, xld.h, xld.ub, xld.b, xbset, xbclr, xbtst, xbnot

load, bit operation from/to SP relative address

%r15,[%sp+0x4444444]

; sp relative No.1

xld.w

xld.uh %r10,[%sp+0x222]

; sp relative No.2

; sp relative No.3

xld.b

[%sp],%r7

[\$sp+0x14],5

; sp relative No.4

xhset

; xld.w, xld.uh, xld.h, xld.ub, xld.b, xbset, xbclr, xbtst, xbnot

load, bit operation from/to register relative address

%r1,[%r15+0x1234568] ; + immediate address No.1

xld.w

xld.uh %r2,[%r14+0xABC] ; + immediate address No.2

[%r13+10], %r3

; + immediate address No.3

xld.h

; + immediate address No.4

%r4,[%r12]

xld.ub

%r5,[%r11+DATA1]

xld.b

; + symbol address No.1

xbnot

[%r10+COMM1],1

; + symbol address No.2

[%r9+COMM1+0x400],2 ; + symbol address + offset No.1

[%r8+COMM1+0x10],3 ; + symbol address + offset No.2

[%r7+COMM1+1] 4

xbtst

xbset

[%r7+COMM1+1],4

; + symbol address + offset No.3

xbclr

; xld.w

load word operation from sp register for C support

xld.w

[%sp],%sp

xld.w

[%sp+0x2468],%sp

xld.w

[0x12340],%sp

xld.w

[COMM1],%sp

xld.w

[COMM1+4],%sp

xld.w

[%r5],%sp

w.blx

[%r6+0b1100],%sp

w.blx

[%r7+DATA1],%sp

xld.w [%r7+DATA1+200],%sp

; xjp, xjreq, xjrne, xjrgt, xjrge, xjrlt, xjrle, xjrugt, xjruge, xjrult

relative branchs

; xjrule, xcall and with .d

NEAR .

; immediate relative No.1

xjp.d

-2

; immediate relative No.2

xjreq

800

0x1000000

; immediate relative No.3

xjrne

xjrgt.d BOOT

; symbol relative No.1

COMM1

; symbol relative No.2

xirqe

xjruge

NEAR

; symbol relative No.3

.data

DATA1:

0x12345678

.word

.comm COMM1 4

```

### make file

Execution of make is indispensable in obtaining the final object file by efficient execution of the necessary tools after correcting source files. Shown below are examples of make files: one with suffixes defined, and one with suffixes undefined. In most cases, you can use either make file, since they are easily created with wb33. But in cases involving manual correction for additional processed files, the make file with suffixes defined may prove preferable.

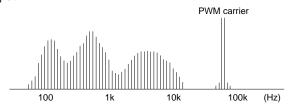

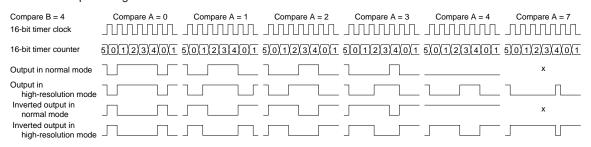

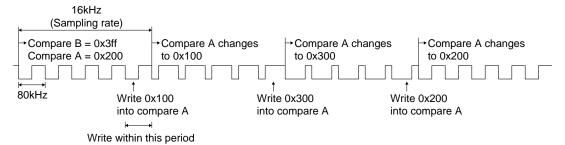

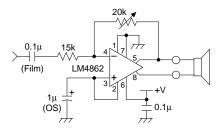

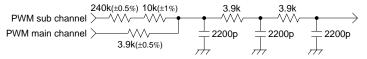

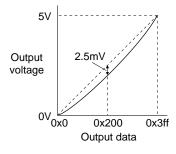

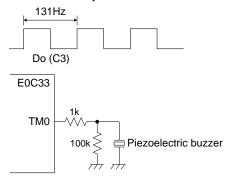

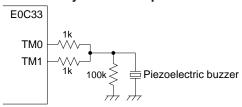

### make file using suffix definition