# CMOS 32-BIT SINGLE CHIP MICROCOMPUTER **E0C33 Family**

# DMT/EPOD/MEM BOARD MANUAL

- DMT33004/DMT33004PD

- DMT33005/DMT33005PD

- DMT33006LV/DMT33006PDLV

- DMT33007/DMT33007PD

- DMT33MON/DMT33MONLV

- DMT33AMP

- DMT33AMP2

- DMT33AMP3

- DMT33CF

- EPOD33001/EPOD33001LV

- EPOD33208/EPOD33208LV

- EPOD332L01LV

- MEM33201/MEM33201LV

- MEM33202/MEM33202LV

- MEM33DIP42

- MEM33TSOP48

- MEM33Board Connection

**SEIKO EPSON CORPORATION**

| NOWEE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOTICE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| NOTICE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from |

PC/AT and IBM are registered trademarks of International Business Machines Corporation, U.S.A.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

Windows98 is a registered trademark of Microsoft Corporation, U.S.A.

## **CONTENTS**

| <b>DMT</b> | <sup>2</sup> 33004/DMT33004PD |

|------------|-------------------------------|

|            | Description1                  |

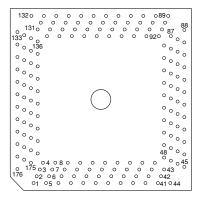

|            | Package 1                     |

|            | Specifications                |

|            | Block Diagram2                |

|            | Connector Pin Assignment2     |

|            | Precautions                   |

| DMT        | 33005/DMT33005PD              |

|            | Description                   |

|            | Package 3                     |

|            | <i>Specifications 3</i>       |

|            | Block Diagram4                |

|            | Connector Pin Assignment4     |

|            | Precautions                   |

| <b>DMT</b> | C33006LV/DMT33006PDLV         |

|            | Overview                      |

|            | Package                       |

|            | Power Supply                  |

|            | Memory Map                    |

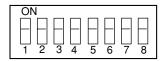

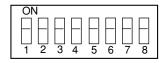

|            | Clock and Boot Settings8      |

|            | Switches 8                    |

|            | Connectors8                   |

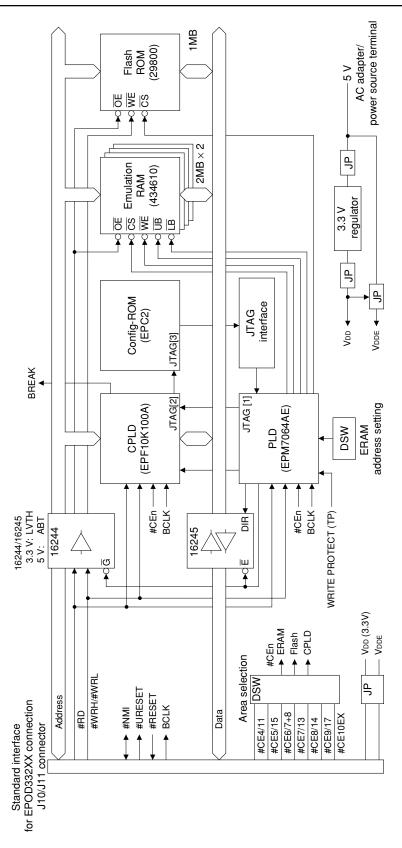

|            | Block Diagram9                |

|            | DIP Switch DSW1 Settings      |

|            | DIP Switch DSW2 Settings      |

|            | Jumper Settings11             |

|            | Pin Assignments               |

|            | Usage Notes                   |

|            | Specifications                |

| <b>DMT</b> | T33007/DMT33007PD1            |

|            | Description                   |

|            | Package                       |

|            | Block Diagram                 |

|            | Pin Assignments               |

|            | Usage Notes                   |

|            | Specifications                |

| DM' | T33MON/DMT33MONLV                      | 17 |

|-----|----------------------------------------|----|

|     | Description                            | 17 |

|     | Package                                |    |

|     | System Configuration                   | 17 |

|     | Block Diagram                          |    |

|     | Connector Pin Assignment               |    |

|     | Precautions                            | 18 |

|     | Specifications                         |    |

| DM' | T33AMP                                 | 19 |

|     | Description                            |    |

|     | Package                                | 19 |

|     | Board Layout                           | 19 |

|     | Block Diagram                          | 20 |

|     | Precautions                            | 20 |

|     | Specifications                         | 20 |

| DM' | T33AMP2                                | 21 |

|     | Description                            |    |

|     | Package                                | 21 |

|     | Board Layout                           |    |

|     | Block Diagram                          | 22 |

|     | Precautions                            | 22 |

|     | Specifications                         | 22 |

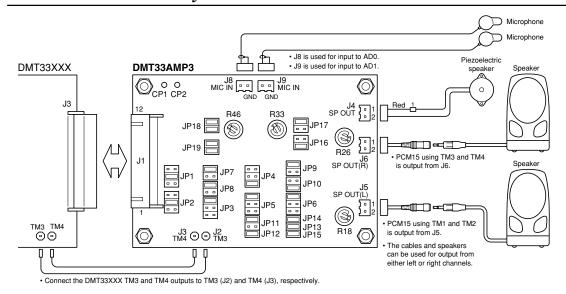

| DM' | T33AMP3                                | 23 |

|     | Description                            | 23 |

|     | Package Contents                       | 23 |

|     | DMT33AMP3 Board Layout and Connections | 24 |

|     | Settings                               | 24 |

|     | Microphone connection                  | 26 |

|     | Jumper Settings                        | 27 |

|     | Volume control settings                | 28 |

|     | Block Diagram                          | 29 |

|     | Specifications                         | 29 |

|     | Precautions                            | 29 |

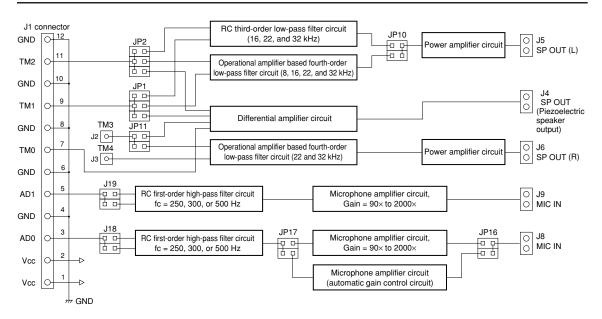

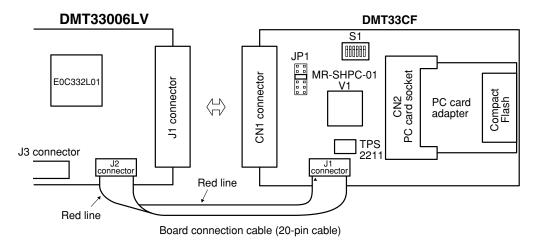

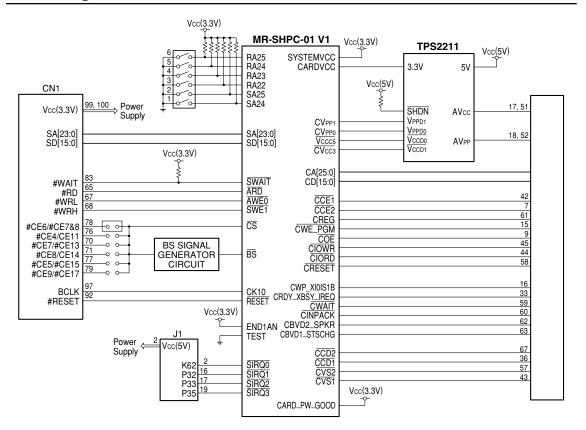

| DM' | T33CF                                  | 30 |

|     | Description                            |    |

|     | Package Contents                       | 30 |

|     | Board Layout                           | 30 |

|     | Block Diagram                          | 31 |

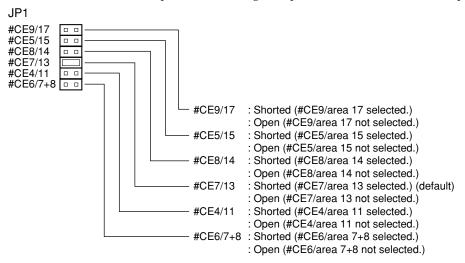

|     | Usage                                  | 31 |

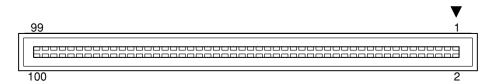

|     | Standard Interface Connector (CN1)     | 34 |

|            | CN2 Connector (PC card connector)                                       |    |

|------------|-------------------------------------------------------------------------|----|

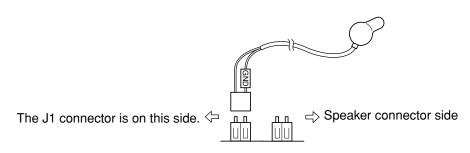

|            | J1 Connector                                                            |    |

|            | Specifications                                                          |    |

|            | Precautions                                                             | 35 |

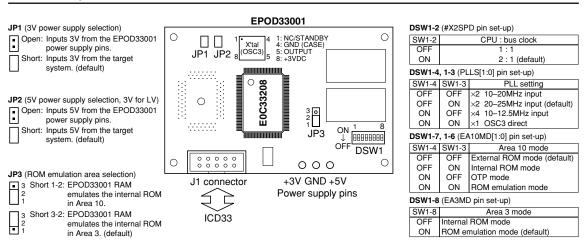

| <b>EPO</b> | DD33001/EPOD33001LV                                                     | 36 |

|            | Description                                                             | 36 |

|            | Package                                                                 |    |

|            | Board Layout                                                            |    |

|            | Block Diagram                                                           |    |

|            | Connecting the EPOD33001                                                |    |

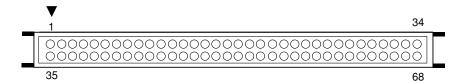

|            | Board-Mounting QFP Adapter Pin Assignment                               |    |

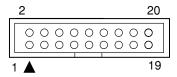

|            | J1 Connector Pin Assignment                                             |    |

|            | Power Supply                                                            |    |

|            | Internal ROM Emulation                                                  |    |

|            |                                                                         |    |

|            | High-Speed (OSC3) Oscillation Clock                                     |    |

|            | Precautions                                                             |    |

|            | Specifications                                                          | 40 |

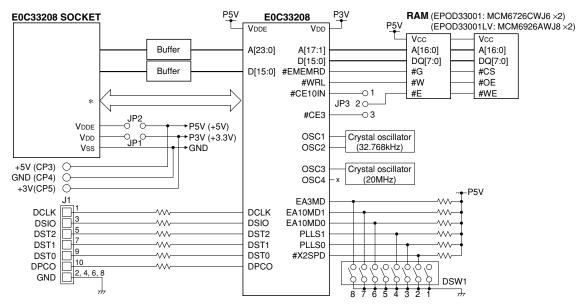

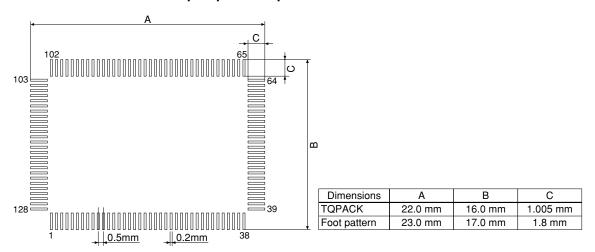

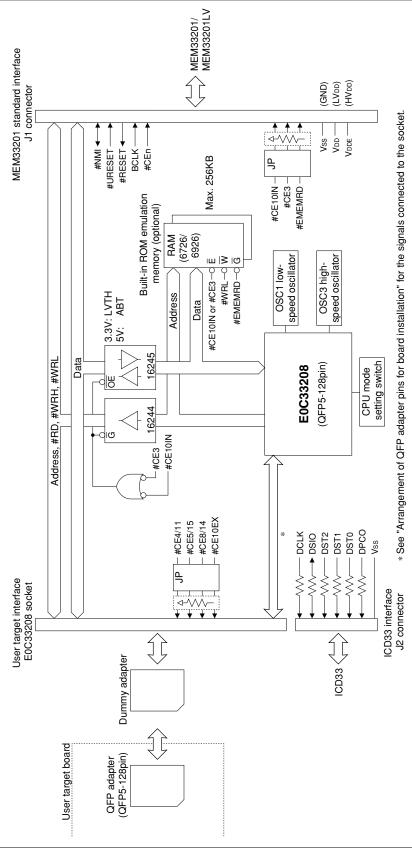

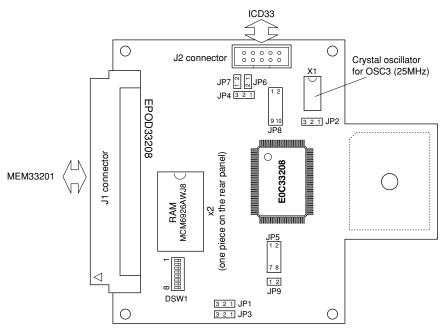

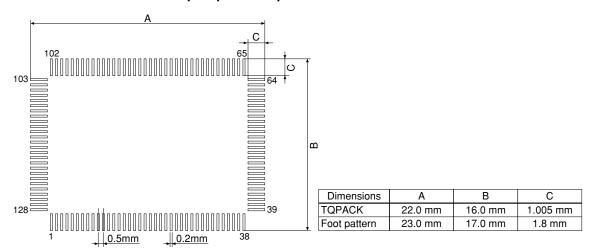

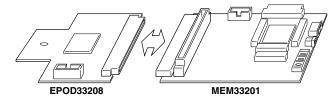

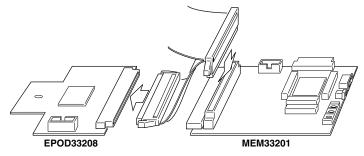

| <i>EPO</i> | DD33208/EPOD33208LV                                                     | 41 |

|            | Overview                                                                | 41 |

|            | Package Contents                                                        | 42 |

|            | Specifications                                                          |    |

|            | Block Diagram                                                           |    |

|            | Unit Operations                                                         |    |

|            | Setting the Jumper Pins                                                 |    |

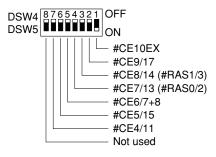

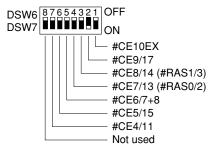

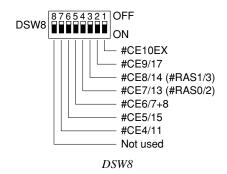

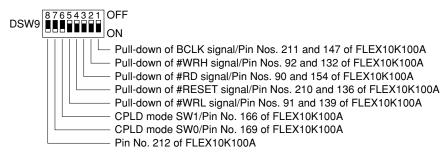

|            | Setting the DIP Switches                                                |    |

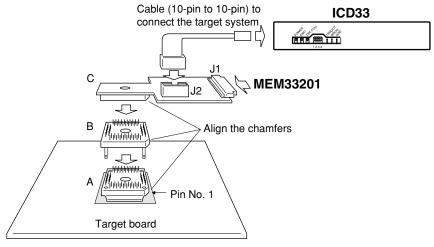

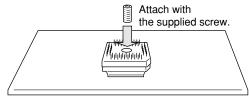

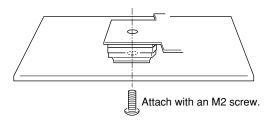

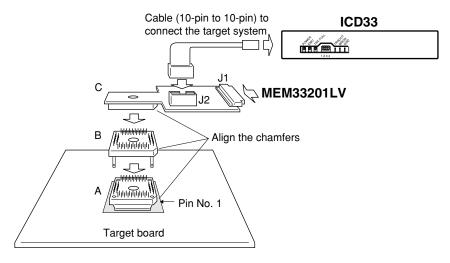

|            | Installation to the User Target  Connecting the MEM33201 Board          |    |

|            | Supplying Power                                                         |    |

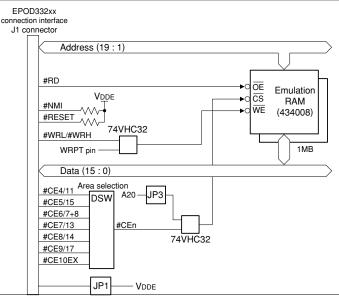

|            | Built-in ROM Emulation                                                  | 50 |

|            | OSC3 Crystal Oscillator                                                 |    |

|            | Pin Arrangement                                                         |    |

|            | QFP Adapter for Board Installation<br>Connector for MEM33201 Connection |    |

|            | Connector for ICD33 Connection                                          |    |

|            | Precautions                                                             | 54 |

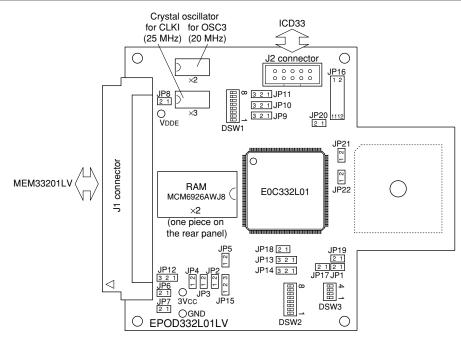

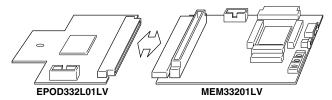

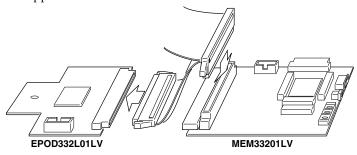

| <b>EPO</b> | DD332L01LV                                                              | 56 |

|            | Overview                                                                |    |

|            | Package Contents                                                        | 57 |

|            | Specifications                                                          | 57 |

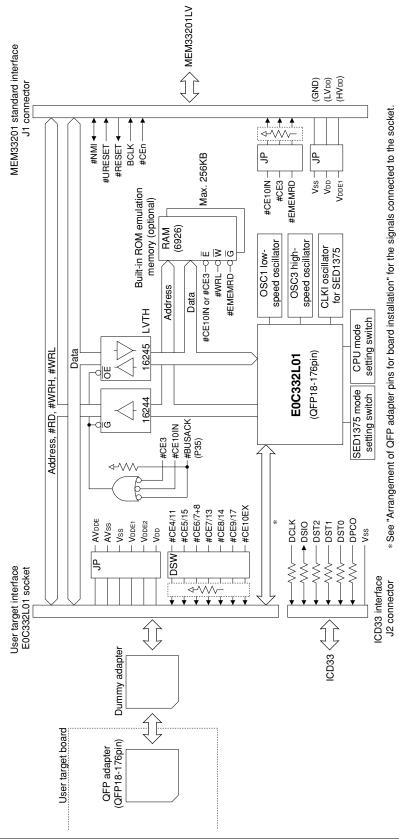

|            | Block Diagram                                                           | 58 |

|            | Unit Operations                                                         | 59 |

|            | Setting the Jumper Pins                                                 |    |

|            | Setting the DIP Switches Installation to the User Target                |    |

|            | Connecting the MEM33201LV Board                                         |    |

#### CONTENTS

| Supplying Power                                            | 68  |

|------------------------------------------------------------|-----|

| Built-in ROM Emulation                                     |     |

| Crystal Oscillator                                         | 70  |

| Pin Arrangement                                            |     |

| QFP Adapter for Board Installation                         |     |

| Connector for MEM33201LV Connection                        |     |

| Precautions                                                |     |

| Precautions                                                | /3  |

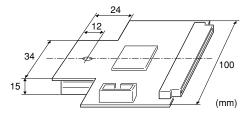

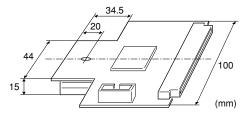

| MEM33201/MEM33201LV                                        | 75  |

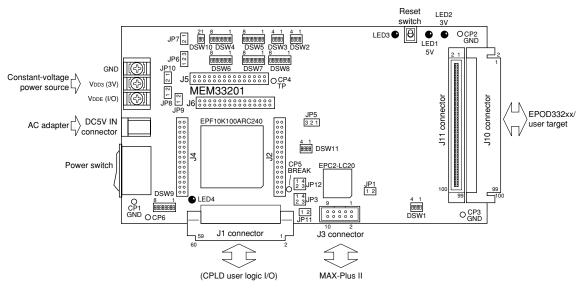

| Overview                                                   | 75  |

| Package Contents                                           | 76  |

| Specifications                                             | 76  |

| Block Diagram                                              | 77  |

| Unit Operations                                            | 78  |

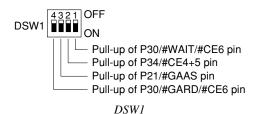

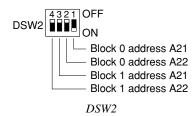

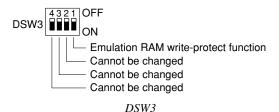

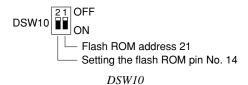

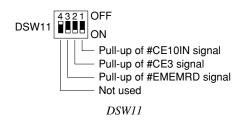

| Switches                                                   | 78  |

| Setting the Jumper Pins                                    |     |

| Setting the DIP Switches                                   |     |

| LEDs                                                       |     |

| Test Pins                                                  |     |

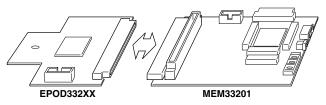

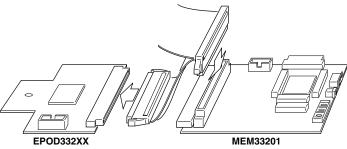

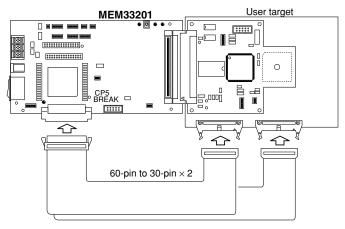

| Connecting the MEM33201 to an EPOD332XX/User Target Board. |     |

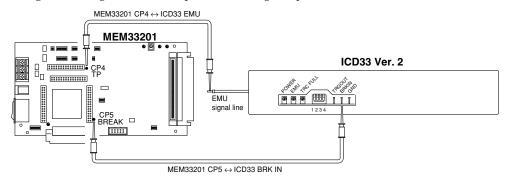

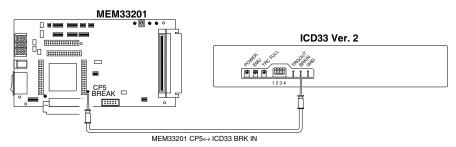

| Connection to ICD33                                        |     |

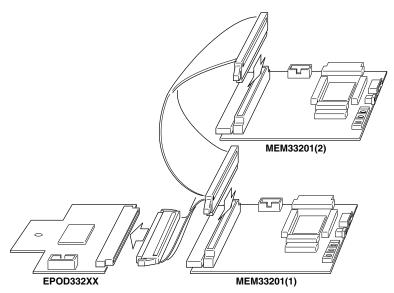

| Cascade-Connecting the MEM33201                            | 91  |

| Connecting the CPLD User Logic Signal                      |     |

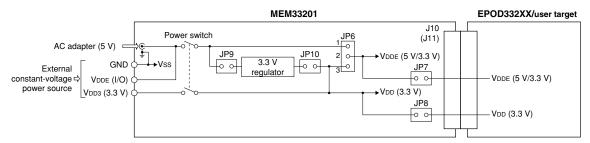

| Supplying Power                                            |     |

| MEM33201 Mapping                                           |     |

| CPLD (FLEX10K100A)                                         |     |

| Overview  Installing User Logic                            |     |

| Writing User Logic with the JTAG                           |     |

| Debug Function Extended Circuit                            |     |

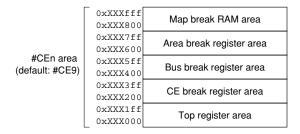

| Additional Break Functions                                 |     |

| How to Use the Break Function                              |     |

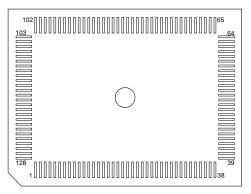

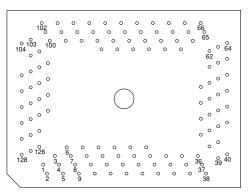

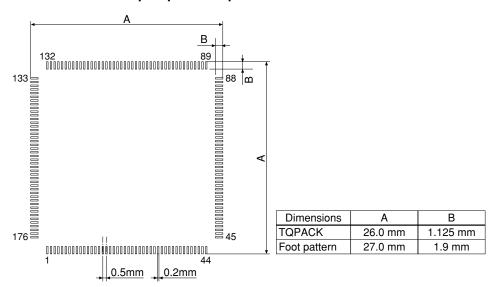

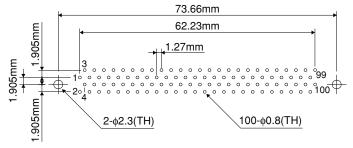

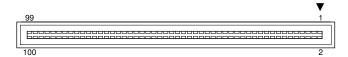

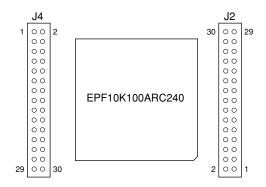

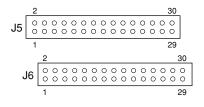

| Pin Arrangement                                            | 109 |

| Standard Interface Connectors (J10, J11)                   |     |

| CPLD User Logic I/O Connector (J1)                         |     |

| JTAG Connector (J3)                                        |     |

| CPLD Monitor Pins (J2, J4)                                 |     |

| EOC33 Bus Monitor Pins (J5, J6)                            |     |

| Precautions                                                | 113 |

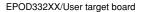

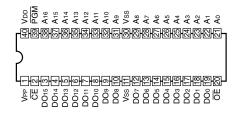

| MEM33202/MEM33202LV                                        | 116 |

| Description                                                | 116 |

| Features                                                   | 116 |

| Product Types                                              | 116 |

| Package Contents                                           |     |

| Specifications                                             | 117 |

| Block Diagram                                              |     |

| Board Layout                                               |     |

| Jumpers                                                    |     |

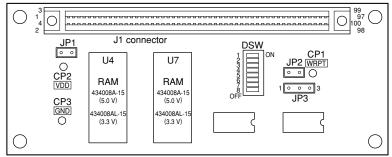

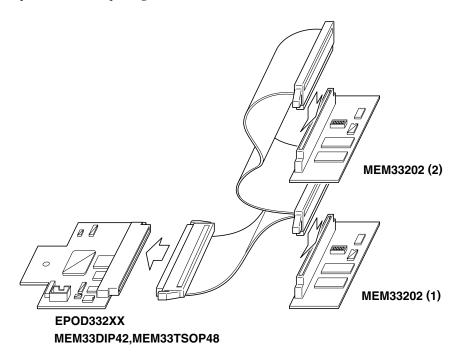

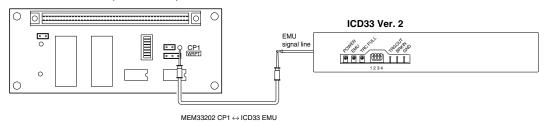

|             | Connecting the MEM33202 to the EPOD332XX, MEM33DIP42 and MEM33TSOP48 |     |

|-------------|----------------------------------------------------------------------|-----|

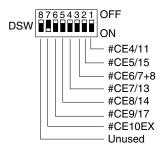

|             | DIP Switch Settings                                                  |     |

|             | Input Pins                                                           |     |

|             | Power Supply                                                         |     |

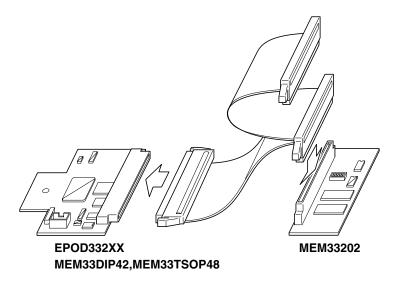

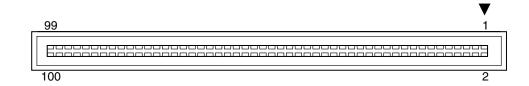

|             | Pin Assignment (J1 standard connector)                               |     |

|             | Precautions                                                          |     |

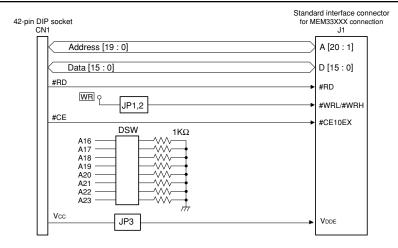

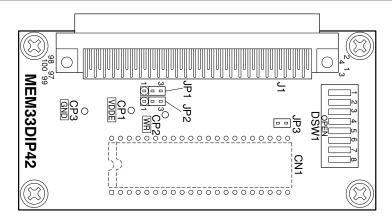

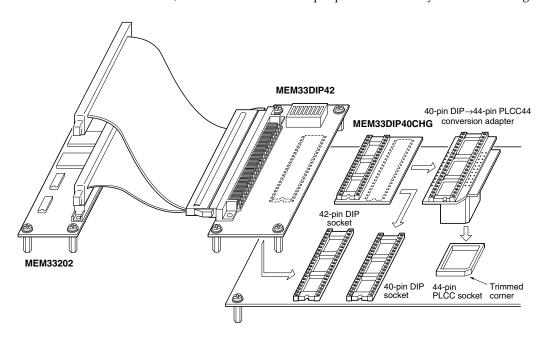

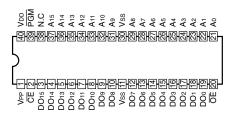

| <b>ME</b> l | M33DIP42                                                             | 123 |

|             | Description                                                          | 123 |

|             | Package Contents                                                     |     |

|             | Specifications                                                       | 123 |

|             | Block Diagram                                                        | 124 |

|             | Board Layout                                                         | 124 |

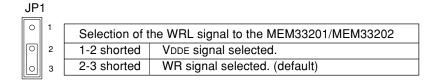

|             | Jumpers                                                              | 124 |

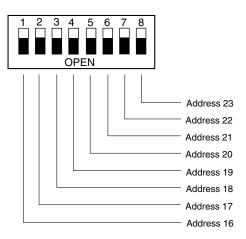

|             | DIP switch (DSW1) settings                                           | 125 |

|             | I/O pins                                                             | 126 |

|             | Connecting to the MEM33XX                                            | 127 |

|             | Connecting to the user target board                                  | 127 |

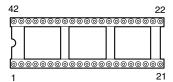

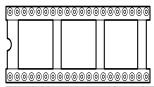

|             | Pin Assignment (42-pin DIP socket) (CN1)                             | 127 |

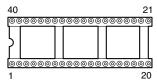

|             | Pin Assignment (40-pin DIP socket) (CN1)                             | 128 |

|             | Pin Assignment (40-pin DIP socket) (CN2)                             | 128 |

|             | Pin Assignment (J1 standard interface connector)                     | 129 |

|             | Precautions                                                          | 129 |

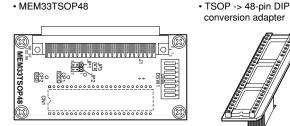

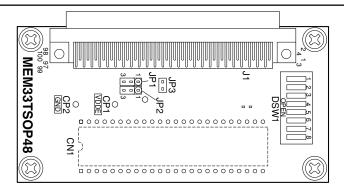

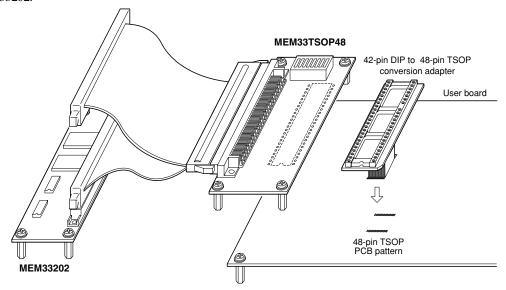

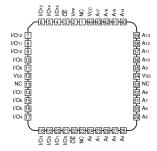

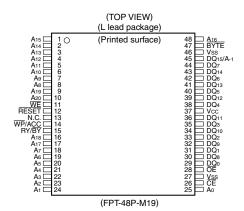

| <b>ME</b> I | M33TSOP48                                                            | 130 |

|             | Description                                                          | 130 |

|             | Package Contents                                                     | 130 |

|             | Specifications                                                       | 130 |

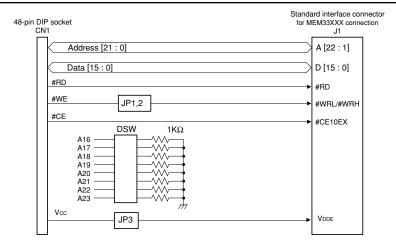

|             | Block Diagram                                                        | 131 |

|             | Board Layuot                                                         | 131 |

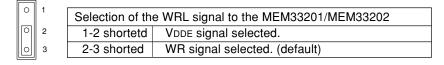

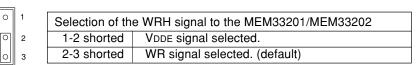

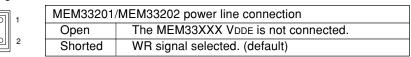

|             | Jumpers                                                              | 131 |

|             | DIP switch (DSW1) settings                                           |     |

|             | I/O pins                                                             | 133 |

|             | Connection to the MEM33XXX                                           | 133 |

|             | Connection to the user target board                                  | 133 |

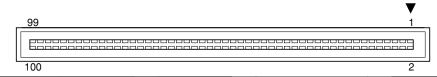

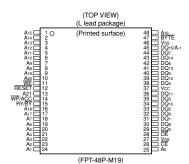

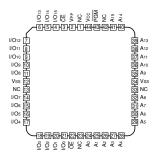

|             | Pin Assignment (J1 standard interface connector)                     | 134 |

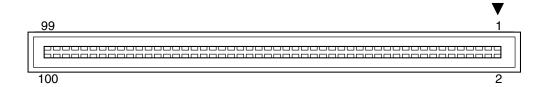

|             | Pin Assignment (CN1 48-pin TSOP socket)                              | 134 |

|             | Precautions                                                          |     |

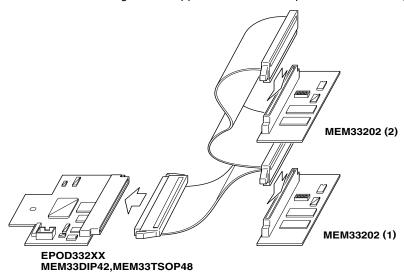

| MEM33 Board Connection                                                                                                                                    | 135 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1. Overview                                                                                                                                               | 135 |

| 2. MEM33202 Emulation Using ROM Sockets                                                                                                                   |     |

| 2-2. 40-pin DIP (1 Mbit × 16, 2 Mbit × 16)<br>2-3. 40-pin DIP and 42-pin DIP                                                                              | 137 |

| (4 Mbit × 16, 8 Mbit × 16, and 16 Mbit × 16)                                                                                                              |     |

| 3. MEM33202 Emulation for Flash Memory                                                                                                                    |     |

| 4. MEM33202 Emulation Using DMT33006LV, DMT33008LV, EPOD332XX, and a User Target Board                                                                    |     |

| (Use the MEM33202 for a 5.0 V supply voltage)                                                                                                             |     |

| 5. MEM33201 Emulation Using the ROM Socket5-1. MEM33201 DIP switch and jumper settings                                                                    |     |

| 5-2. MEM33201 Emulation using the 44-pin PLCC (1 Mbit $\times$ 16, 2 Mbit $\times$ 16, or 4 Mbit $\times$ 16)5-3. MEM33201 Emulation using the 40-pin DIP | 149 |

| (1 Mbit × 16 or 2 Mbit × 16)                                                                                                                              | 149 |

| (4 Mbit × 16, 8 Mbit × 16, or 16 Mbit × 16)                                                                                                               | 150 |

| 6. MEM33201 Emulation for Flash Memory<br>6-1. 48-pin TSOP (2 Mbit × 16, 4 Mbit × 16, 8 Mbit × 16, 16 Mbit × 16,<br>or 32 Mbit × 16)                      |     |

| 7. MEM33201 Emulation Using the DMT33006LV, the DMT33008LV, the EPOD332XX, and a User Target Board                                                        |     |

| 8. Precautions                                                                                                                                            |     |

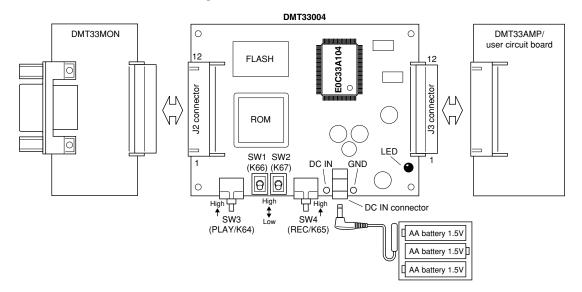

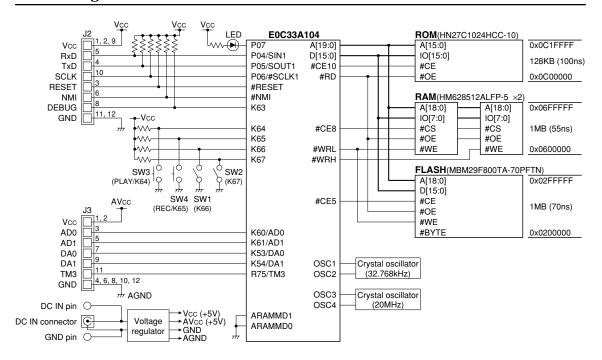

### **E0C33A104 Demonstration Board**

# DMT33004/DMT33004PD

## Description

The DMT33004 is a demonstration tool of the E0C33A104 32-bit RISC type microcomputer. The DMT33004 board contains a 128KB ROM, a 1MB RAM, a 1MB Flash memory, and two connectors, one for interfacing with the DMT33MON board and the other for a voice I/O circuit board such as DMT33AMP. This board can be used as a development tool for the voice application as well as various applications that use the E0C33A104. The DMT33004PD contains the QFP type socket used to connect the POD33001 as a substitute for the E0C33A104 chip.

## **Package**

The DMT33004 package contains the following items:

| (1) DMT33004 board1                | (5) DMT33004/DMT33004PD Manual 1 (E&J) |

|------------------------------------|----------------------------------------|

| (2) Battery holder1                | (6) User registration card 1 (E&J)     |

| (3) DC power cable1                | (7) Warranty card 1 (E&J)              |

| (4) I/F connectors for user board2 | (8) Usage precautions                  |

| No. | Component          | Item                       | Specifications                                               | Remarks                      |

|-----|--------------------|----------------------------|--------------------------------------------------------------|------------------------------|

| 1   | DMT33004           | Dimensions                 | $80\text{mm}(L) \times 60\text{mm}(W) \times 25\text{mm}(H)$ |                              |

|     |                    | CPU                        | E0C33A104                                                    |                              |

|     |                    | ROM                        | 128KB, 100ns, HN27C1024HCC-10(Hitachi, PLCC)                 | Area 10(0x0c00000-0x0c1ffff) |

|     |                    | RAM                        | 1MB, 55ns, HM628512ALFP-5(Hitachi)                           | Area 8(0x0600000-0x06fffff)  |

|     |                    | FLASH                      | 1MB, 70ns, MBM29F800TA-70PFTN(Fujitsu)                       | Area 5(0x0200000-0x02fffff)  |

|     |                    | Operating (input) voltage  | 5V(+3V to +5V)                                               |                              |

|     |                    | Current consumption (typ.) | Approx. 75mA                                                 |                              |

|     |                    |                            | (varies according to the memory access condition)            |                              |

|     |                    | J2 connector               | S12B-XH-A1(Nichiatsu)                                        |                              |

|     |                    | J3 connector               | 12JQ-ST(Nichiatsu)                                           |                              |

| 2   | Supplied connector |                            | S12B-XH-A1(Nichiatsu)                                        | ×2                           |

| 3   | Battery holder     |                            | AA battery × 3(ELPA)                                         |                              |

| 4   | DC power cable     | Length                     | Approx. 60cm                                                 |                              |

|     |                    | Plug                       | JXP4802(Hoshiden)                                            |                              |

### **Block Diagram**

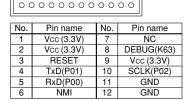

## Connector Pin Assignment

#### J2 connector (for connecting DMT33MON)

| No. | Pin name | No. | Pin name   |

|-----|----------|-----|------------|

| 1   | Vcc (5V) | 7   | NC         |

| 2   | Vcc (5V) | 8   | DEBUG(K63) |

| 3   | RESET    | 9   | Vcc (5V)   |

| 4   | TxD(P05) | 10  | SCLK(P06)  |

| 5   | RxD(P04) | 11  | GND        |

| 6   | NMI      | 12  | GND        |

#### **J3 connector** (for connecting DMT33AMP/user board)

| No. | Pin name | No. | Pin name |

|-----|----------|-----|----------|

| 1   | Vcc (5V) | 7   | DA0(K53) |

| 2   | Vcc (5V) | 8   | GND      |

| 3   | AD0(K60) | 9   | DA1(K54) |

| 4   | GND      | 10  | GND      |

| 5   | AD1(K61) | 11  | TM3(R75) |

| 6   | GND      | 12  | GND      |

#### **Precautions**

- Make sure that the power of all boards/equipment of the system are off before installing/removing boards to/from the DMT33004.

- The power for the DMT33004 can be supplied between the DC IN and GND pins instead of the DC IN connector. The supply voltage range must be within the range of 3V to 5V and do not confuse the polarity (+ and -) as it may cause a malfunction.

- If the DEBUG signal of the J2 connector is set to high or is left open (such as when the DMT33MON is not connected) when the DMT33004 is turned on, the DMT33004 loads the reset vector stored in the Flash memory to the Program Counter to execute the program from that address. (After shipping, the demonstration program that makes the LED blink is executed.) If the DEBUG signal is set to low (SW3 of the DMT33MON = ON), the debug monitor in the ROM will start up.

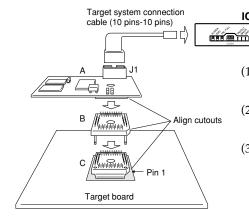

- When connecting the DMT33004PD to the POD33001, align the cutout of each socket.

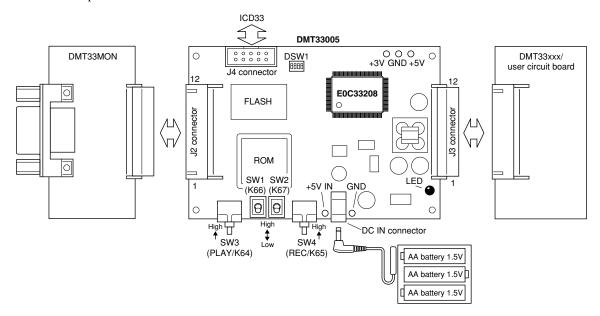

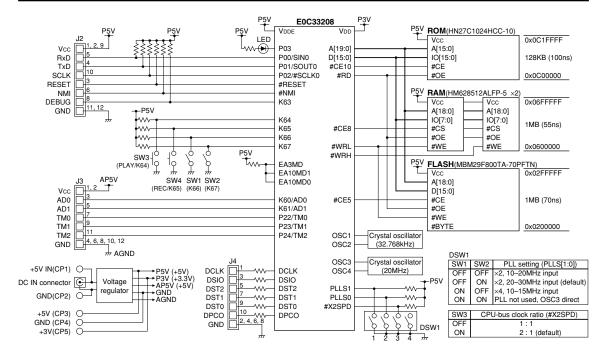

### **E0C33208 Demonstration Board**

# DMT33005/DMT33005PD

## Description

The DMT33005 is a demonstration tool of the E0C33208 32-bit RISC type microcomputer. The DMT33005 board contains a 128KB ROM, a 1MB RAM, a 1MB Flash memory, and three connectors for interfacing with the DMT33MON board, for an option board or user circuit board and for the ICD33 debug tool. This board can be used as a development tool for various applications that use the E0C33208. The DMT33005PD contains the QFP type socket used to connect the EPOD33001 as a substitute for the E0C33208 chip.

## **Package**

The DMT33005 package contains the following items:

| (1) DMT33005 board1                | (5) DMT33005/DMT33005PD Manual 1 (E&J) |

|------------------------------------|----------------------------------------|

| (2) Battery holder1                | (6) User registration card 1 (E&J)     |

| (3) DC power cable1                | (7) Warranty card 1 (E&J)              |

| (4) I/F connectors for user board2 | (8) Usage precautions1 (E&J)           |

| No. | Component          | Item                       | Specifications                                               | Remarks                      |

|-----|--------------------|----------------------------|--------------------------------------------------------------|------------------------------|

| 1   | DMT33005           | Dimensions                 | $80\text{mm}(L) \times 60\text{mm}(W) \times 25\text{mm}(H)$ |                              |

|     |                    | CPU                        | E0C33208                                                     |                              |

|     |                    | ROM                        | 128KB, 100ns, HN27C1024HCC-10(Hitachi, PLCC)                 | Area 10(0x0c00000-0x0c1ffff) |

|     |                    | RAM                        | 1MB, 55ns, HM628512ALFP-5(Hitachi)                           | Area 8(0x0600000-0x06fffff)  |

|     |                    | FLASH                      | 1MB, 70ns, MBM29F800TA-70PFTN(Fujitsu)                       | Area 5(0x0200000-0x02fffff)  |

|     |                    | Operating (input) voltage  | 5V(+3V to +5V)                                               |                              |

|     |                    | Current consumption (typ.) | Approx. 75mA                                                 |                              |

|     |                    |                            | (varies according to the memory access condition)            | [                            |

|     |                    | J2 connector               | S12B-XH-A1(Nichiatsu)                                        |                              |

|     |                    | J3 connector               | 12JQ-ST(Nichiatsu)                                           |                              |

| 2   | Supplied connector |                            | S12B-XH-A1(Nichiatsu)                                        | × 2                          |

| 3   | Battery holder     |                            | AA battery × 3(ELPA)                                         |                              |

| 4   | DC power cable     | Length                     | Approx. 60cm                                                 |                              |

|     |                    | Plug                       | JXP4802(Hoshiden)                                            |                              |

## Block Diagram

## Connector Pin Assignment

#### J2 connector

| No. | Pin name | No. | Pin name   |

|-----|----------|-----|------------|

| 1   | Vcc (5V) | 7   | NC         |

| 2   | Vcc (5V) | 8   | DEBUG(K63) |

| 3   | RESET    | 9   | Vcc (5V)   |

| 4   | TxD(P01) | 10  | SCLK(P02)  |

| 5   | RxD(P00) | 11  | GND        |

| 6   | NMI      | 12  | GND        |

### J3 connector

| No. | Pin name   | No. | Pin name |

|-----|------------|-----|----------|

| 1   | 1 Vcc (5V) |     | TM0(P22) |

| 2   | Vcc (5V)   | 8   | GND      |

| 3   | AD0(K60)   | 9   | TM1(P23) |

| 4   | GND        | 10  | GND      |

| 5   | AD1(K61)   | 11  | TM2(P24) |

| 6   | GND        | 12  | GND      |

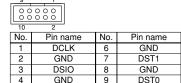

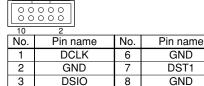

#### J4 connector

| 10  | 2        |     |          |

|-----|----------|-----|----------|

| No. | Pin name | No. | Pin name |

| 1   | DCLK     | 6   | GND      |

| 2   | GND      | 7   | DST1     |

| 3   | DSIO     | 8   | GND      |

| 4   | GND      | 9   | DST0     |

| 5   | DST2     | 10  | DPCO     |

#### **Precautions**

- Make sure that the power of all boards/equipment of the system are off before installing/removing boards to/from the DMT33005.

- The power for the DMT33005 can be supplied between the DC IN and GND pins instead of the DC IN connector. The supply voltage range must be within the range of 3V to 5V and do not confuse the polarity (+ and -) as it may cause a malfunction.

- If the DEBUG signal of the J2 connector is set to high or is left open (such as when the DMT33MON is not connected) when the DMT33005 is turned on, the DMT33005 loads the reset vector stored in the Flash memory to the Program Counter to execute the program from that address. (After shipping, the demonstration program that makes the LED blink is executed.) If the DEBUG signal is set to low (SW3 of the DMT33MON = ON), the debug monitor in the ROM will start up.

- When connecting the DMT33004PD to the EPOD33001, align the cutout of each socket.

#### **E0C332L01 Demonstration Board**

# DMT33006LV/DMT33006PDLV

#### **Overview**

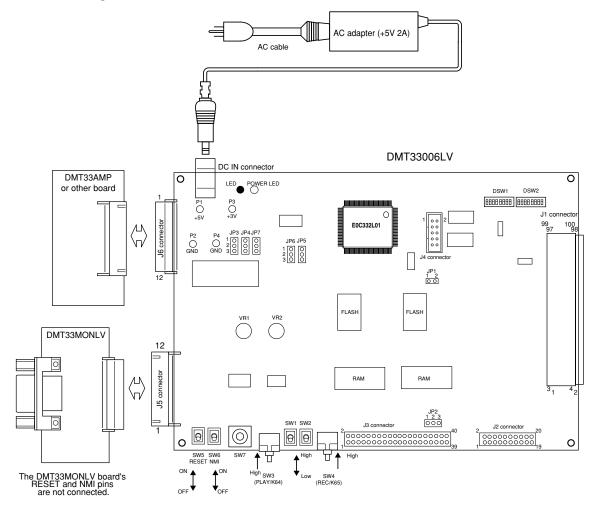

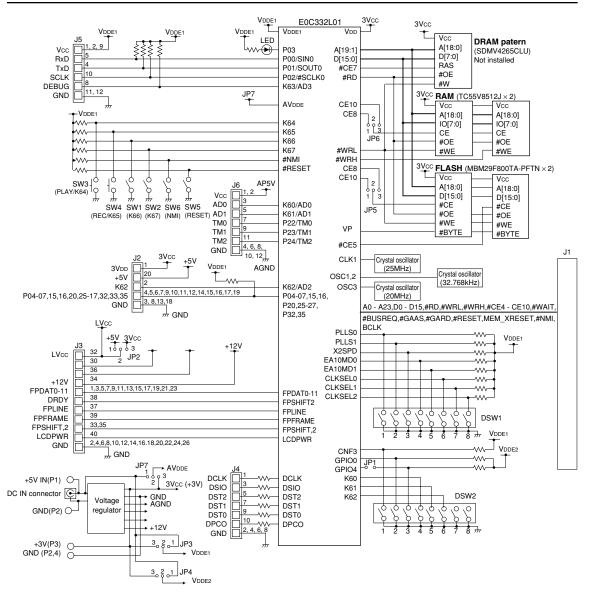

The DMT33006LV board demonstrates the E0C332L01, a 32-bit Seiko Epson microcomputer with a built-in LCD controller. The circuit board includes two blocks with 1 Mbyte of RAM and Flash memory each plus interface connectors for the DMT33MON board, the DMT33AMP board, an LCD panel, additional I/O, and the ICD33 debugging tool. The DMT33006LV board is thus also the core of a development environment for developing applications for the E0C332L01.

The DMT33006PDLV version replaces the E0C332L01 chip with a QFP socket accepting an EPOD332L01LV. One of the 1Mbyte of Flash memory blocks contains a debug monitor(MON33) support software development via the DMT33MONLV board.

### **Package**

| The DMT33006LV package contains the following items.   |  |

|--------------------------------------------------------|--|

| (1) DMT33006LV board                                   |  |

| (2) DMT33006LV specifications (this document) 1        |  |

| (3) AC adapter (5V DC output), with cable 1            |  |

| (4) Interface connectors for user application system 2 |  |

## **Power Supply**

Connecting a 5-V power supply to the DC IN connector lights the POWER LED and starts the board. The board derives its internal 3.3-V and 12-V power supplies from this single 5-V power supply. The board operates the E0C332L01 chip, memory, and other components at 3.3 V.

- VDD, the E0C332L01 internal logic power supply, is always 3.3 V.

- VDDE1, the E0C332L01 power supply voltage for I/O, Flash memory, and SRAM, is specified by the jumper JP3. Always use 3.3 V.

- VDDE2, the E0C332L01 LCD interface power supply, and LCDVDD, the power supply to the LCD panel (J3 pin 32), have default settings of 5 V to match the DMT33LCD26/37 board. These may be changed to 3.3 V, however, with the jumpers JP2 and JP4, respectively.

- AVDDE, the E0C332L01 analog power supply, has a default setting of 5 V to match the DMT33AMP board. This may be changed to 3.3 V, however, with the jumper JP7.

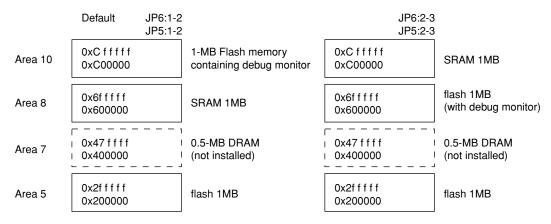

## Memory Map

The jumpers JP6 and JP5 control the address mapping of the 1-MB Flash memory containing the debug monitor and the 1-MB SRAM chip to areas 10 and 8. Using the debug monitor requires the default settings (1-2). Do not use any combination other than those appearing below.

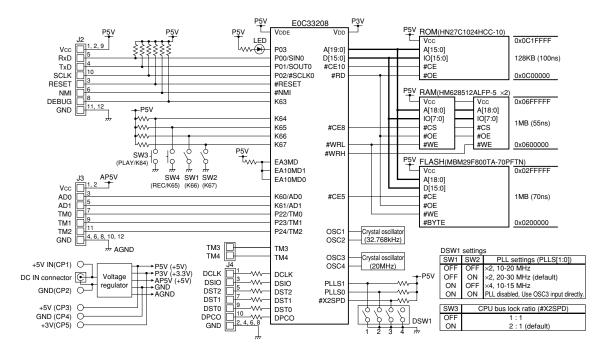

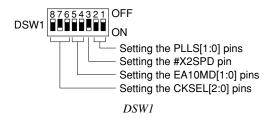

### Clock and Boot Settings

- The E0C332L01 accepts a 20-MHz clock signal from the oscillator attached the OSC3 pin. (This oscillator may be changed, but must operate at 3.3 V.)

- The default DSW1 settings of SW1 ON and SW2 OFF double this input to 40 MHz for the E0C33 CPU core clock input.

- The default DSW1 setting of SW3 ON then halves this latter frequency to 20 MHz for the bus. This configuration supports, for example, read/write access to 70-ns Flash memory with one wait (100 ns).

- The default DSW1 settings of SW4 and SW5 both OFF boots from the external ROM—that is, address 0xC0000 in the 1-MB Flash memory containing the debug monitor.

- The default DSW1 settings of SW6, SW7, and SW8 divide the 20-MHz OSC3 pin input frequency by three to produce the internal LCD controller clock (CLKI).

- The EPOD332L01 version disconnects these clock signals and uses its own settings.

#### **Switches**

- Pressing SW3 (PLAY) connects High level input to the pin K64. The normal pin state is Low level.

- Pressing SW4 (REC) connects High level input to the pin K65. The normal pin state is Low level.

- Setting SW1 (K66) to the "3" position indicated on the circuit board connects High level input to the pin K66. The "1" position connects Low level input.

- Setting SW2 (K67) to the "3" position indicated on the circuit board connects High level input to the pin K67. The "1" position connects Low level input.

- Setting SW5 (RESET) or SW4 (NMI) to the "3" positions indicated on the circuit board connects Low level input to the corresponding pin. Note that pressing the RESET and NMI pins on the DMT33MONLV board does nothing.

- SW7 controls input to pins K50, K51, K52, K53, and K54. The normal input level for these pins is Low level. Pressing SW7 downward connects High level input to pin K54. Pressing SW7 to its "U," "L," "D," and "R" positions connects High level input to pins K50, K51, K52, and K53, respectively. Pressing SW7 at an angle between two positions connects High level input to the two corresponding pins.

#### **Connectors**

- J5 is for connecting the DMT33MONLV board.

- J6 is for connecting the DMT33AMP board.

- J3 is for connecting the DMT33LCD26/37 board.

- J2 provides access to all I/O pins not covered by the above.

- J1 provides access to the address bus, data bus, and memory control signals.

- J4 is for connecting the ICD33 debugging tool.

## **Block Diagram**

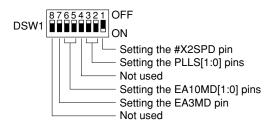

# DIP Switch DSW1 Settings

| SW1 | SW2 | PLL multiplier (PLLS)                                   |

|-----|-----|---------------------------------------------------------|

| OFF | OFF | ×2 for OSC3 input frequencies of 10 to 20 MHz           |

| ON  | OFF | ×2 for OSC3 input frequencies of 20 to 25 MHz (default) |

| OFF | ON  | ×4 for OSC3 input frequencies of 10 to 12.5 MHz         |

| ON  | ON  | ×1 (PLL disabled)                                       |

| SW4 | SW5 | EA10MD0 and EA10MD1 setting |

|-----|-----|-----------------------------|

| OFF | OFF | External ROM mode (default) |

| ON  | OFF | Internal ROM mode           |

| OFF | ON  | OTP mode                    |

| ON  | ON  | Internal ROM emulation      |

| SW3 | Ratio of CPU clock to bus clock (X2 SPD) |

|-----|------------------------------------------|

| ON  | CPU clock:BUS clock 2:1 (default)        |

| OFF | CPU clock:BUS clock 1:1                  |

| SW6 | SW7 | SW8 | CKSEL0 to CKSEL2 settings (CLKI) |

|-----|-----|-----|----------------------------------|

| OFF | OFF | OFF | Not allowed                      |

| ON  | OFF | OFF | 1375 disabled                    |

| OFF | ON  | OFF | External clock form CLK1 input   |

| ON  | ON  | OFF | OSC3 clock × 1/4                 |

| OFF | OFF | ON  | OSC3 clock × 1/3 (default)       |

| OFF | ON  | ON  | OSC3 clock × 1/2                 |

| ON  | ON  | ON  | PLL output                       |

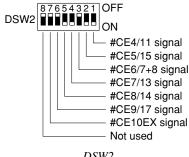

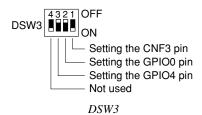

# DIP Switch DSW2 Settings

|     |     | SED1375 settings                             |

|-----|-----|----------------------------------------------|

| SW1 | ON  | CNF pin: Low level (little-endian) (default) |

|     | OFF | CNF pin: High level (big-endian)             |

| SW2 | ON  | GPI00 pin: Low level                         |

|     | OFF | GPI00 pin: High level (default)              |

| SW3 | ON  | GPI04 pin: Low level                         |

|     | OFF | GPI04 pin: High level (default)              |

| SW4 | ON  | K60 pin: Low level                           |

|     | OFF | K60 pin: High level (default)                |

| SW5 | ON  | K61 pin: Low level                           |

|     | OFF | K61 pin: High level (default)                |

| SW6 | ON  | K62 pin: Low level                           |

|     | OFF | K62 pin: High level (default)                |

# Jumper Settings

#### JP1

|   | GP104/INVE | GP104/INVERSE setting       |  |  |

|---|------------|-----------------------------|--|--|

| ĺ | Open       | FPDAT11 output (default)    |  |  |

|   | Short      | GPI04/INVERSE setting input |  |  |

#### JP5

| Flash memo | Flash memory location |  |  |

|------------|-----------------------|--|--|

| 1-2 short  | Area 10 (default)     |  |  |

| 2-3 open   | Area 8                |  |  |

#### JP2

|                            | LCDVDD = | LCDVDD = LCD panel supply voltage (J3 pin 32) |  |  |  |  |

|----------------------------|----------|-----------------------------------------------|--|--|--|--|

| 1-2 short   +5 V (default) |          |                                               |  |  |  |  |

|                            | 2-3 open | +3.3 V                                        |  |  |  |  |

#### JP6

| RAM location |                  |  |  |  |  |

|--------------|------------------|--|--|--|--|

| 1-2 short    | Area 8 (default) |  |  |  |  |

| 2-3 open     | Area 10          |  |  |  |  |

#### JP3

| VDDE1 = Power supply voltage for I/O and memory |                  |                  |  |  |  |  |

|-------------------------------------------------|------------------|------------------|--|--|--|--|

|                                                 | 1-2 short   +5 V |                  |  |  |  |  |

|                                                 | 2-3 open         | +3.3 V (default) |  |  |  |  |

#### JP7

| Analog power supply voltage |                |  |  |  |  |  |

|-----------------------------|----------------|--|--|--|--|--|

| 1-2 short                   | +5 V (default) |  |  |  |  |  |

| 2-3 open                    | +3.3 V         |  |  |  |  |  |

#### JP4

| VDDE2 = Pov | wer supply voltage for LCD interface |

|-------------|--------------------------------------|

| 1-2 short   | +5 V (default)                       |

| 2-3 open    | +3.3 V                               |

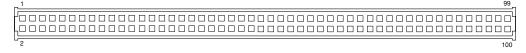

# Pin Assignments

#### J1 connector

| No. | Pin name   | No. | Pin name | No. | Pin name | No. | Pin name            | No. | Pin name          |

|-----|------------|-----|----------|-----|----------|-----|---------------------|-----|-------------------|

| 1   | VDDE1      | 21  | A15      | 41  | D4       | 61  | D14                 | 81  | #CE10IN           |

| 2   | VDDE1      | 22  | GND      | 42  | GND      | 62  | GND                 | 82  | GND               |

| 3   | A0         | 23  | A16      | 43  | D5       | 63  | D15                 | 83  | P30(#WAIT/#CE4+5) |

| 4   | A1         | 24  | A17      | 44  | GND      | 64  | GND                 | 84  | GND               |

| 5   | A2         | 25  | A18      | 45  | D6       | 65  | #RD                 | 85  | P34(#BUSREQ/#CE6) |

| 6   | A3         | 26  | A19      | 46  | GND      | 66  | GND                 | 86  | GND               |

| 7   | GND        | 27  | GND      | 47  | D7       | 67  | #WRL/#WR/#WE/LWE    | 87  | P21(#GAAS)        |

| 8   | A4         | 28  | A20      | 48  | GND      | 68  | #WRH/BSH/UWE        | 88  | P31(#GARD)        |

| 9   | A5         | 29  | A21      | 49  | D8       | 69  | GND                 | 89  | GND               |

| 10  | A6         | 30  | A22      | 50  | GND      | 70  | #CE7/13/#RAS0/#RAS2 | 90  | #CE3IN            |

| 11  | <b>A</b> 7 | 31  | A23      | 51  | D9       | 71  | #CE8/14/#RAS1/#RAS3 | 91  | #EMEMRD           |

| 12  | GND        | 32  | GND      | 52  | GND      | 72  | GND                 | 92  | #URESET           |

| 13  | A8         | 33  | D0       | 53  | D10      | 73  | #HCAS/#UWE          | 93  | #RESET            |

| 14  | A9         | 34  | GND      | 54  | GND      | 74  | #LCAS/#LWE          | 94  | GND               |

| 15  | A10        | 35  | D1       | 55  | D11      | 75  | GND                 | 95  | #NMI              |

| 16  | A11        | 36  | GND      | 56  | GND      | 76  | #CE4/11             | 96  | GND               |

| 17  | GND        | 37  | D2       | 57  | D12      | 77  | #CE5/15             | 97  | BCLK              |

| 18  | A12        | 38  | GND      | 58  | GND      | 78  | #CE6/7+8            | 98  | GND               |

| 19  | A13        | 39  | D3       | 59  | D13      | 79  | #CE9/17             | 99  | 3VDD (3.3V)       |

| 20  | A14        | 40  | GND      | 60  | GND      | 80  | #CE10EX             | 100 | 3VDD (3.3V)       |

#### J2 connector

| No. | Pin name    | No. | Pin name |

|-----|-------------|-----|----------|

| 1   | 3VDD (3.3V) | 11  | P20      |

| 2   | K62         | 12  | P25      |

| 3   | GND         | 13  | GND      |

| 4   | P04         | 14  | P26      |

| 5   | P05         | 15  | P27      |

| 6   | P06         | 16  | P32      |

| 7   | P07         | 17  | P33      |

| 8   | GND         | 18  | GND      |

| 9   | P15         |     | P35      |

| 10  | P16         | 20  | +5V      |

#### J3 connector

| No. | Pin name |

|-----|----------|-----|----------|-----|----------|-----|----------|

| 1   | FPDAT0   | 11  | FPDAT5   | 21  | FPDAT10  | 31  | N.C      |

| 2   | GND      | 12  | GND      | 22  | GND      | 32  | LCDVDD   |

| 3   | FPDAT1   | 13  | FPDAT6   | 23  | FPDAT11  | 33  | FPSHIFT  |

| 4   | GND      | 14  | GND      | 24  | GND      | 34  | +12V     |

| 5   | FPDAT2   | 15  | FPDAT7   | 25  | N.C      | 35  | FPSHIFT2 |

| 6   | GND      | 16  | GND      | 26  | GND      | 36  | VDDH     |

| 7   | FPDAT3   | 17  | FPDAT8   | 27  | N.C      | 37  | FPLINE   |

| 8   | GND      | 18  | GND      | 28  | N.C      | 38  | DRDY     |

| 9   | FPDAT4   | 19  | FPDAT9   | 29  | N.C      | 39  | FPFRAME  |

| 10  | GND      | 20  | GND      | 30  | VLCD     | 40  | LCDPWR   |

#### J4 connector

10

DPC0

#### J5 connector

#### J6 connector

3

4

5

6

9

10

11

12

TM1(P23)

GND

TM2(P24)

GND

AD0(K60)

GND

AD1(K61)

GND

## Usage Notes

DST2

5

- Make sure that the power supplies to all boards and equipment in the entire setup are off before connecting or disconnecting boards to the DMT33006 board.

- An alternate to the power supply connection at the DC IN connector is the pair of pins (+5 V and GND) on either side. Note that this alternate power supply must have a nominal voltage of +5 V. Double-check the connections because reversed polarity can damage the board.

- When the power is first applied, the DMT33006LV board checks the J5 connector DEBUG signal from the DMT33MONLV board. High level input or an open connection (that is, no DMT33MONLV board) loads the Program Counter (PC) from the reset vector from the address 0x200000 in the Flash memory to begin execution of the program stored at that address. (The factory default is a demonstration program that flashes the onboard LED.) Low level input (produced by setting SW3 on the DMT33MONLV board to its ON position), on the other hand, starts the debug monitor in ROM.

- When connecting the EPOD332L01LV to the DMT33006PDLV board, align the cutouts on the sockets.

- Do not set SW4 to ON and SW5 to OFF. This setting causes the board to boot from the internal ROM, which currently does not contain valid program code.

| No. | Component                              | Item                                                                                 | Specifications                         | Notes         |

|-----|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------|---------------|

| 1   | DMT33006LV/                            | Dimentsons                                                                           | 193mm(L) × 135mm(W) × 20mm(H)          |               |

|     | DMT33006PDLV                           | CPU                                                                                  | E0C332L01                              |               |

|     |                                        | RAM                                                                                  | 1MB, 12ns, TC55V8512J-12(Toshiba)      |               |

|     |                                        | DRAM (not installed)                                                                 | 0.5MB, 60ns, SDMV4265CLTM(EPSON)       |               |

|     |                                        | FLASH                                                                                | 1MB, 70ns, MBM29F800TA-70PFTN(Fujitsu) | × 2           |

|     |                                        | Operating (input) voltage                                                            | 3.3V (I/O, memory, LCD circuit)        |               |

|     |                                        |                                                                                      | 5V (Analog circuit) (+3V to +5V)       |               |

|     |                                        | Current consumption (Typ.) Approx. 110mA(Value varies with memory access conditions) |                                        |               |

|     | J1 connector (MEM) 8830E-100-170L(KEL) |                                                                                      |                                        |               |

|     | J3 connector (ICD)                     |                                                                                      |                                        |               |

|     |                                        | J5 connector                                                                         | S12B-XH-A1(Nichiatsu)                  |               |

|     |                                        | J6 connector                                                                         | 12JQ-ST(Nichiatsu)                     |               |

| 2   | Supplied connector                     |                                                                                      | S12B-XH-A1(Nichiatsu)                  |               |

|     | 8801                                   |                                                                                      | 8801-100-170L(KEL)                     |               |

| 3   | AC adaptor                             |                                                                                      | Input: AC100 to 240V Output: DC5V 2A   | with AC cable |

| 4   | AC cable                               |                                                                                      | 1.8m, with GNDs                        |               |

### **E0C33208 Demonstration Board**

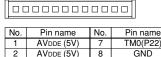

# DMT33007/DMT33007PD

## Description

The DMT33007 board is for developing applications for the EOC33208 32-bit RISC microcomputer. Main components include 128 KB of ROM, 1 MB of RAM, 1 MB of Flash memory, and three connectors for interfacing with the DMT33MON board, the DMT33AMP board, and the ICD33 debugger. The DMT33007PD version replaces the EOC33208 chip with a QFP socket for connecting the EPOD33001. The 128 KB of ROM contains a debug monitor (MON33) support software development via the DMT33MON board.

## **Package**

The DMT33007 package contains the following items.

(1) DMT33007 board

1

(2) DMT33007 specifications (this document)

1

(3) AC adapter (5V DC output), with cable

1

(4) DC power supply cable

1

(5) Interface connectors for user application system

2

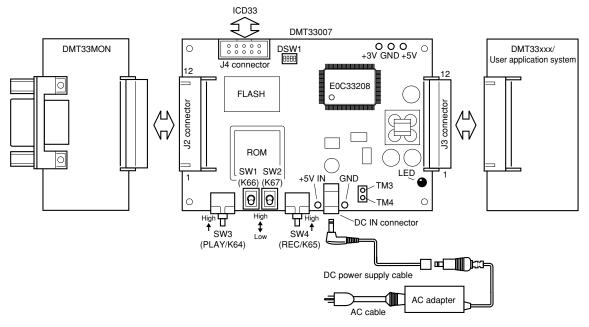

### Pin Assignments

#### J2 connector

| No. | Pin name | No. | Pin name   |

|-----|----------|-----|------------|

| 1   | Vcc (5V) | 7   | NC         |

| 2   | Vcc (5V) | 8   | DEBUG(K63) |

| 3   | RESET    | 9   | Vcc (5V)   |

| 4   | TxD(P01) | 10  | SCLK(P02)  |

| 5   | RxD(P00) | 11  | GND        |

| 6   | NMI      | 12  | GND        |

#### J3 connector

| me  |

|-----|

| 22) |

| )   |

| 23) |

| )   |

| 24) |

| )   |

|     |

#### J4 connector

| 00000 |          |     |          |  |  |  |  |  |  |  |

|-------|----------|-----|----------|--|--|--|--|--|--|--|

| 10 2  |          |     |          |  |  |  |  |  |  |  |

| No.   | Pin name | No. | Pin name |  |  |  |  |  |  |  |

| 1     | DCLK     | 6   | GND      |  |  |  |  |  |  |  |

| 2     | GND      | 7   | DST1     |  |  |  |  |  |  |  |

| 3     | DSIO     | 8   | GND      |  |  |  |  |  |  |  |

| 4     | GND      | 9   | DST0     |  |  |  |  |  |  |  |

| 5     | DST2     | 10  | DPCO     |  |  |  |  |  |  |  |

## Usage Notes

- Make sure that the power supplies to all boards and equipment in the entire setup are off before connecting or disconnecting boards to the DMT33007 board.

- An alternate to the power supply connection at the DC IN connector is the pair of pins (IN and GND) on either side. Note that this alternate power supply must have a nominal voltage of +5 V. Double-check the connections because reversed polarity can damage the board.

- When the power is first applied, the DMT33007 board checks the J2 connector DEBUG signal from the DMT33MON board. High level input or an open connection (that is, no DMT33MON board) loads the Program Counter (PC) from the reset vector in the Flash memory to begin execution of the program stored at that address. (The factory default is a demonstration program that flashes the onboard LED.) Low level input (produced by setting SW3 on the DMT33MON board to its ON position), on the other hand, starts the debug monitor in ROM.

- When connecting the EPOD33001 to the DMT33007PD board, align the cutouts on the sockets.

| No.                        | Component               | Item                       | Specifications                                               | Notes                        |

|----------------------------|-------------------------|----------------------------|--------------------------------------------------------------|------------------------------|

| 1                          | 1 DMT33007 Dimensions 8 |                            | $80\text{mm}(L) \times 60\text{mm}(W) \times 25\text{mm}(H)$ |                              |

|                            |                         | CPU                        | E0C33208                                                     |                              |

|                            |                         | ROM                        | 128KB, 100ns, HN27C1024HCC-10(Hitachi, PLCC)                 | Area 10(0x0c00000~0x0c1ffff) |

|                            |                         | RAM                        | 1MB, 55ns, HM628512ALFP-5(Hitachi)                           | Area 8(0x0600000~0x06fffff)  |

|                            |                         | FLASH                      | 1MB, 70ns, MBM29F800TA-70PFTN(Fujitsu)                       | Area 5(0x0200000~0x02fffff)  |

|                            |                         | Operating (input) voltage  | 5V                                                           |                              |

| Current consumption (typ.) |                         | Current consumption (typ.) | Approx. 75 mA (Value varies with memory access conditions)   |                              |

|                            |                         | J2 connector               | S12B-XH-A1(Nichiatsu)                                        |                              |

|                            |                         | J3 connector               | 12JQ-ST(Nichiatsu)                                           |                              |

| 2                          | Supplied connectors     |                            | S12B-XH-A1(Nichiatsu)                                        | × 2                          |

| 3                          | AC adapter              |                            | Input: AC100 to 240V Output: DC5V 2A                         | with AC cable                |

| 4                          | DC power supply         | Length                     | Approx. 60cm                                                 |                              |

|                            | cable                   | Plug                       | JXP4802(Hoshiden)                                            |                              |

|                            |                         | Plug                       | HEC0470-01-630(Hoshiden)                                     |                              |

### **E0C33 Family Debug Monitor Interface Board**

# DMT33MON/DMT33MONLV

### **Description**

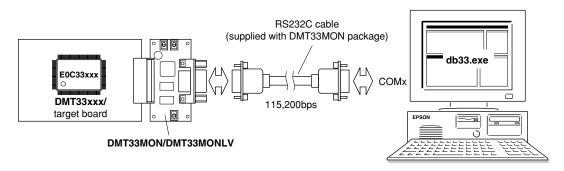

The DMT33MON board provides the interface for the debug monitor to the demonstration tools such as the DMT33004/33005 or the user target board. The DMT33MON allows on-board debugging using the debugger (db33.exe) on a personal computer by connecting it to the target board in which the E0C33 Family debug monitor (MON33) has been implemented. The DMT33MON board is for 5V operation and the DMT33MONLV is for 3.3V operation.

For details on how to use the DMT33MON, refer to the "E0C33 Family MON33 Debug Monitor Manual".

## **Package**

The DMT33MON package contains the following items:

- (1) DMT33MON board

1

(2) PC connection cable (RS232C)

1

(3) I/F connectors for connecting target board

2

(4) DMT33MON/DMT33MONLV Manual

1 (E&J)

(5) User registration card

1 (E&J)

(6) Warranty card

1 (E&J)

(7) Usage precautions

1 (E&J)

- MON33 Debug Monitor" package and the "E0C33 Family C Compiler" package containing the debugger separately.

Please prepare the "E0C33 Family

## System Configuration

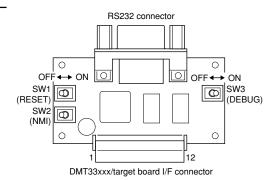

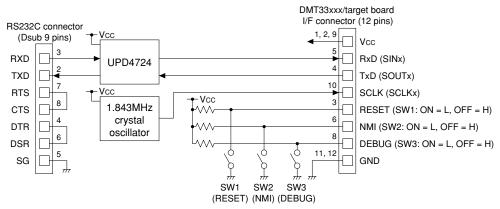

## **Block Diagram**

## Connector Pin Assignment

#### Target board I/F connector

| No. | Pin name   | No. | Pin name   |

|-----|------------|-----|------------|

| 1   | Vcc        | 7   | NC         |

| 2   | Vcc        | 8   | DEBUG(SW3) |

| 3   | RESET(SW1) | 9   | Vcc        |

| 4   | TxD(SOUT)  | 10  | SCLK       |

| 5   | RxD(SIN)   | 11  | GND        |

| 6   | NMI(SW2)   | 12  | GND        |

#### PC I/F (RS-232C) connector

| No. | Pin name | No. | Pin name |

|-----|----------|-----|----------|

| 1   | _        | 6   | DSR      |

| 2   | TXD      | 7   | RTS      |

| 3   | RXD      | 8   | CTS      |

| 4   | DTR      | 9   | _        |

| 5   | SG       |     |          |

#### **Precautions**

- Make sure that the power of the DMT33xxx/target board and the personal computer are off before connecting or disconnecting the system.

- Use a +5V±0.5V power supply for the DMT33MON and a +3.3V±0.3V for the DMT33MONLV. Supplying any other voltage may cause a malfunction. Also, do not confuse the polarity (+ and -).

- Do not connect the DMT33MONLV to a DMT33xxx board with 5V specification as it may cause a malfunction.

| No. | Component        | Item                       | Specifications                                               | Remarks |

|-----|------------------|----------------------------|--------------------------------------------------------------|---------|

| 1   | DMT33MON/        | Dimensions                 | $30\text{mm}(L) \times 60\text{mm}(W) \times 20\text{mm}(H)$ |         |

|     | DMT33MONLV       | Operating (input) voltage  | DMT33MON: +5V±0.5V                                           |         |

|     |                  |                            | DMT33MONLV: +3.3V±0.3V                                       |         |

|     |                  | Current consumption (typ.) | Approx. 10mA                                                 |         |

| 2   | RS-232C cable    | Length                     | 3m                                                           |         |

|     | (for IBM-PC/AT)/ | Cable connector            | DMT side: D-sub 9pins(female)                                |         |

|     | connector        |                            | Host side: D-sub 9pins(male)                                 |         |

|     |                  | Connector on DMT           | DELC-J9SAF-23L0(JAE)                                         |         |

| 3   | Target board I/F | Connector on DMT           | 12JQ-ST(Nichiatsu)                                           |         |

|     | connector        | Connector for target board | S12B-XH-A1(Nichiatsu)                                        | × 2     |

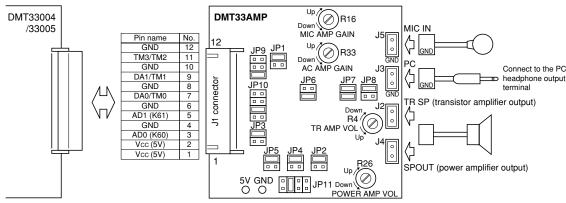

## Voice Input/Output Board for DMT

# DMT33AMP

### Description

The DMT33AMP is an optional board that provides a voice I/O function for the DMT33004/33005 and the user target board. The DMT33AMP allows voice input or output with the microphone and on-board amplifier. It is suitable for developing voice applications. It also allows configuration of the on-board low-pass and high-pass filters for the microphone input and speaker output signals to test the effects.

## **Package**

The DMT33AMP package contains the following items:

| (1) DMT33AMP board 1                       |

|--------------------------------------------|

| (2) Speaker 1                              |

| (3) Microphone 1                           |

| (4) I/F connector for user board 1         |

| (5) PC headphone output connection cable 1 |

## **Board Layout**

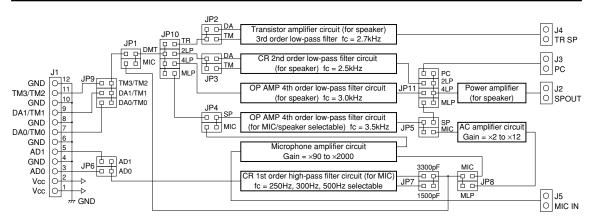

| Jum | per switch —                               |                                                                                                                               |                       |                               |                                                                                                                                                                                           |

|-----|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

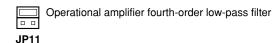

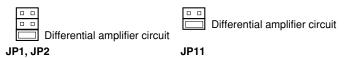

| JP1 | DMT                                        | Selects the voice source to be output. DMT: DMT33004/33005 output (default) MIC: Microphone input of this board               | JP8 🗀 🛚               | MIC<br>MLP                    | Selects whether the OP AMP 4th order filter circuit for the MIC circuit is used or not.  MIC: Not used (default)                                                                          |

| JP2 | DA<br>IIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIII | Selects an input for the transistor amplifier circuit. DA: DMT33004 D/A output (default) TM: DMT33005 PWM output              | JP9 🙃                 | TM3/TM2<br>DA1/TM1<br>DA0/TM0 | MLP: Used Selects a DMT33004/33005 output signal. TM3/TM2: DMT33004 TM3 or DMT33005 TM2                                                                                                   |

| JP3 | DA<br>D TM                                 | Selects an input for the CR 2nd order filter circuit. DA: DMT33004 D/A output (default) TM: DMT33005 PWM output               | JP10 🗀                | TR                            | DA1/TM1: DMT33004 DA1 or DMT33005 TM1 DA1/TM1: DMT33004 DA0 or DMT33005 TM0 (default) Selects the circuit to be used for voice output.                                                    |

| JP4 | SP MIC                                     | Selects a filter in the OP AMP 4th order filter circuit (for speaker and MIC). SP: For speaker (default) MIC: For microphone  |                       | 2LP<br>4LP<br>MLP             | TR: Transistor amplifier circuit 2LP: CR 2nd order filter circuit 4LP: OP AMP 4th order filter circuit (for speaker) (default) MLP: OP AMP 4th order filter circuit (for speaker and MIC) |

| JP5 | SP MIC                                     | Selects an filter in the OP AMP 4th order filter circuit (for speaker and MIC). SP: For speaker (default) MIC: For microphone | 0, , , , , ,          | PC<br>2LP<br>— 4LP<br>— MLP   | Selects a power amplifier input. PC: PC headphone output 2LP: CR 2nd order filter circuit 4LP: OP AMP 4th order filter circuit (for speaker) (default)                                    |

| JP6 | □ □ AD1<br>□ □ AD0                         | Selects the A/D channel on the DMT33004/33005 used to convert the MIC input. AD0: Channel 0 (default) AD1: Channel 1          |                       | OMT33AMP                      | MLP: OP AMP 4th order filter circuit (for speaker and MIC) is set for connecting the DMT33004 by default. When using with select TM using JP2 and JP3, and DA1/TM1 using JP9.             |

| JP7 | 3300pF<br>1500pF                           | Selects a cutoff frequency in the CR 1sr order high-pass filter circuit.                                                      | Control -<br>R26 Volu | ume adjustn                   | nent for the power amplifier                                                                                                                                                              |

Short 3300pF only: 300 Hz

Short 1500pF only: 500 Hz

Short both: 250 Hz (default)

Volume adjustment for the transistor amplifier

Gain adjustment for the AC amplifier (x2 to x12)

Gain adjustment for the microphone input (microphone amplifier) (×90 to ×2000)

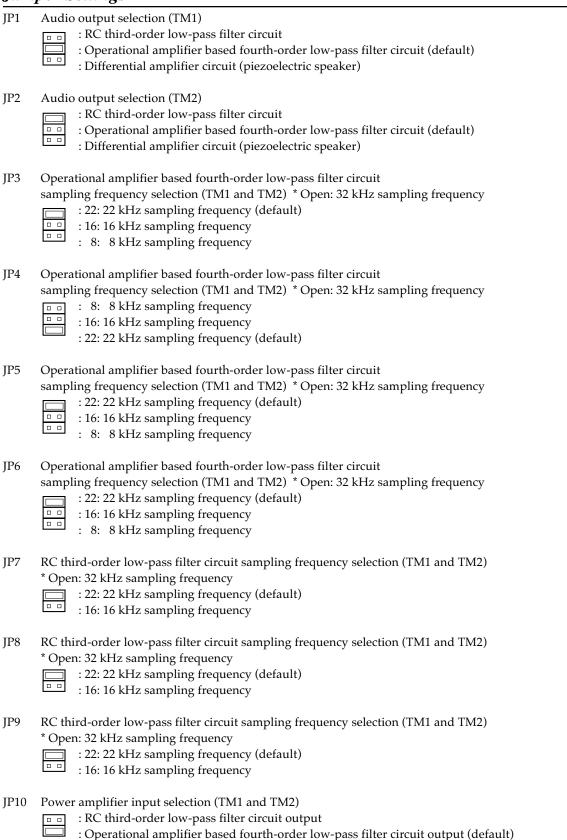

## Block Diagram

#### **Precautions**

- Make sure that the power of all boards/equipment of the system are off before installing/removing boards to/from the DMT33AMP.

- The +5V source voltage is supplied to the DMT33AMP through the 5V and GND pins or the J1 connector. Do not connect the power supply to the 5V and GND pins when supplying the source voltage through the J1 connector (such as when the DMT33004/33005 is connected).

| No.                              | Component                          | Item                              | Specifications                                               | Remarks |

|----------------------------------|------------------------------------|-----------------------------------|--------------------------------------------------------------|---------|

| 1                                | DMT33AMP                           | Dimensions                        | $60\text{mm}(L) \times 60\text{mm}(W) \times 20\text{mm}(H)$ |         |

|                                  |                                    | Operating (input) voltage         | +5V±0.5V                                                     |         |

|                                  |                                    | Current consumption (typ.)        | Approx. 10mA (idling), Approx. 100mA (speaker driven)        |         |

|                                  |                                    | I/F connector (male)              | S12B-XH-A1(Nichiatsu)                                        |         |

| 2                                | 2 Accessory Condencer microphone V |                                   | WM-034DM(Panasonic)                                          |         |

|                                  | Speaker 8Ω, 0.25W, TO5             |                                   | 8Ω, 0.25W, TO50S11A000(Foster)                               |         |

| PC connection cable Length: appr |                                    | PC connection cable               | Length: approx. 50cm                                         |         |

|                                  |                                    |                                   | Connector: HKP02FS01(HONDA)                                  |         |

|                                  |                                    | Connector for user board (female) | 12JQ-ST(Nichiatsu)                                           |         |

## Voice Input/Output Board for DMT

# DMT33AMP2

## Description

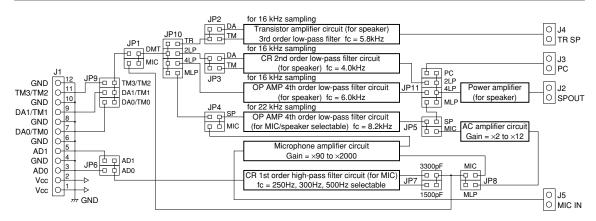

The DMT33AMP2 is an optional board that provides a voice I/O function for the DMT33004/33005 and the user target board. The DMT33AMP2 allows voice input or output with the microphone and on-board amplifier. It is suitable for developing voice applications. It also allows configuration of the on-board low-pass and high-pass filters for the microphone input and speaker output signals to test the effects. The DMT33AMP2 supports 16kHz and 22kHz sampling rate (8kHz is not available). For 8kHz sampling, DMT33AMP is available.

### **Package**

The DMT33AMP2 package contains the following items:

| (1) DMT33AMP2 board 1                      | (6) DMT33AMP2 Manual 1 (E&J)       |

|--------------------------------------------|------------------------------------|

| (2) Speaker 1                              | (7) User registration card 1 (E&J) |

| (3) Microphone 1                           | (8) Warranty card 1 (E&J)          |

| (4) I/F connector for user board 1         | (9) Usage precautions 1 (E&J)      |

| (5) PC headphone output connection cable 1 |                                    |

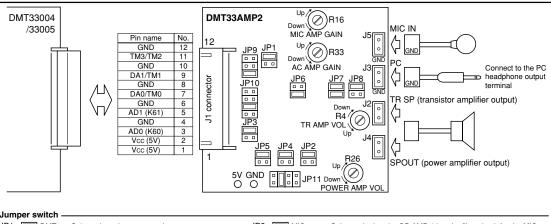

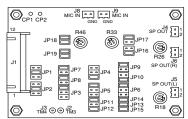

## **Board Layout**

| Jum | per switch — |                                                                                                                                                         |                      |                                                                                                                                                                                                                                            |

|-----|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|