# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER E0C62M2 DEVELOPMENT TOOL MANUAL

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. Please note that "EOC" is the new name for the old product "SMC". If "SMC" appears in other manuals understand that it now reads "EOC".

MS-DOS and EDLIN are registered trademarks of Microsoft Corporation, U.S.A. PC-DOS, PC/AT, VGA, EGA and IBM are registered trademarks of International Business Machines Corporation, U.S.A. NEC PC-9801 Series and NEC are registered trademarks of NEC Corporation. All other product names mentioned herein are trademarks and/or registered trademarks of their respective owners.

# E0C62M2 Development Tool Manual

# PREFACE

This manual mainly explains the outline of the development support tool for the 4-bit Single Chip Microcomputer E0C62M2.

Refer to the "E0C62 Family Development Tool Reference Manual" for the details (common to all models) of each development support tool. Manuals for hardware development tools are separate, so you should also refer to the below manuals.

| Development tools     | æ  | E0C62 Family Development Tool Reference Manual<br>EVA62M2 Manual<br>ICE6200 Hardware Manual |

|-----------------------|----|---------------------------------------------------------------------------------------------|

| Development procedure | ¢. | E0C62 Family Technical Guide                                                                |

| Device (E0C62M2)      | ¢. | E0C62M2 Technical Manual                                                                    |

| Instructions          | æ  | E0C6200/6200A Core CPU Manual                                                               |

# **CONTENTS**

| 1 | COM  | POSITION OF DEVELOPMENT SUPPORT TOOL        | 1            |

|---|------|---------------------------------------------|--------------|

|   | 1.1  | Configuration of DEV62M2 1                  |              |

|   | 1.2  | Developmental Environment                   |              |

|   | 1.3  | Development Flow                            |              |

|   | 1.4  | Production of Execution Disk                |              |

| 2 | DEVE | LOPMENT TOOL MANAGEMENT SYSTEM DMS6200      | 4            |

|   | 2.1  | DMS6200 Outline                             |              |

|   | 2.2  | DMS6200 Quick Reference                     |              |

| 3 | CROS | S ASSEMBLER ASM62M2                         | 5            |

|   | 3.1  | ASM62M2 Outline                             | -            |

|   | 3.2  | E0C62M2 Restrictions                        |              |

|   | 3.3  | ASM62M2 Quick Reference                     |              |

| 4 | FUNC | CTION OPTION GENERATOR FOG62M2              | 8            |

|   | 4.1  | FOG62M2 Outline                             |              |

|   | 4.2  | E0C62M2 Option List                         |              |

|   | 4.3  | Option Specifications and Selection Message |              |

|   | 4.4  | FOG62M2 Quick Reference                     |              |

|   | 4.5  | Sample File                                 |              |

| 5 | SEGM | IENT OPTION GENERATOR SOG62M2               | 15           |

|   | 5.1  | SOG62M2 Outline                             |              |

|   | 5.2  | Option List                                 | <del>,</del> |

|   | 5.3  | Segment Ports Output Specifications         |              |

|   | 5.4  | SOG62M2 Quick Reference                     |              |

|   | 5.5  | Sample Files                                |              |

|   |      |                                             |              |

| 6  | ICE C | CONTROL SOFTWARE ICS62M2       | 20 |

|----|-------|--------------------------------|----|

|    |       | ICS62M2 Outline                |    |

|    | 6.2   | ICS62M2 Restrictions           |    |

|    | 6.3   | ICS62M2 Quick Reference        |    |

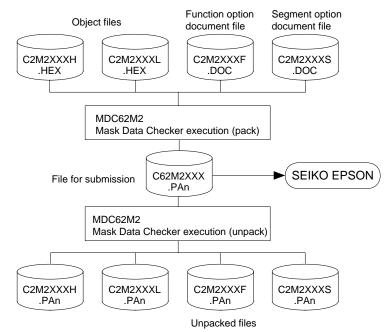

| 7  | MASK  | K DATA CHECKER MDC62M2         | 25 |

|    |       | MDC62M2 Outline                |    |

|    | 7.2   | MDC62M2 Quick Reference        |    |

| A. | PPENL | DIX A. E0C62M2 INSTRUCTION SET | 28 |

|    |       | B. E0C62M2 RAM MAP             | 32 |

|    |       | C. E0C62M2 I/O MEMORY MAP      | 34 |

|    |       | D. TROUBLESHOOTING             | 38 |

# 1 COMPOSITION OF DEVELOPMENT SUPPORT TOOL

Here we will explain the composition of the software for the development support tools, developmental envilonment and how to generate the execution disk.

# 1.1 Configuration of DEV62M2

The below software are included in the product of the E0C62M2 development support tool DEV62M2.

- 1. Development Tool Management System DMS6200 ..... Menu selection for each software / start-up software

- 2. Cross Assembler ASM62M2 ..... Cross assembler for program preparation

- 3. Function Option Generator FOG62M2 ...... Function option data preparation program

- 4. Segment Option Generator SOG62M2 ...... Segment option data preparation program

- 5. ICE Control Software ICS62M2..... ICE control program

- 6. Mask Data Checker MDC62M2 ...... Mask data preparation program

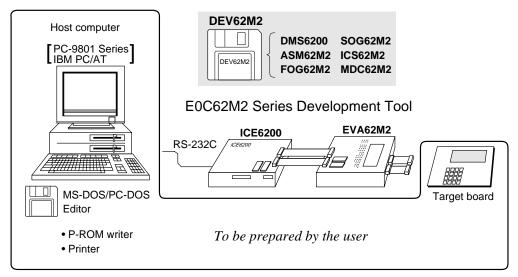

# 1.2 Developmental Environment

The software product of the development support tool DEV62M2 operates on the following host systems:

- IBM PC/AT (at least PC-DOS Ver. 2.0)

- NEC PC-9801 Series (at least MS-DOS Ver. 3.1)

When developing the E0C62M2, the above-mentioned host computer, editor, P-ROM writer, printer, etc. must be prepared by the user in addition to the development tool which is normally supported by Seiko Epson.

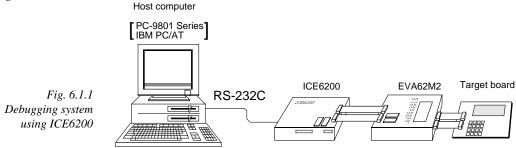

Fig. 1.2.1 System configuration

Note The DEV62M2 system requires a host computer with a RAM capacity of about 140K bytes. Since the ICE6200 is connected to the host computer with a RS-232C serial interface, adapter board for asynchronous communication will be required depending on the host computer used.

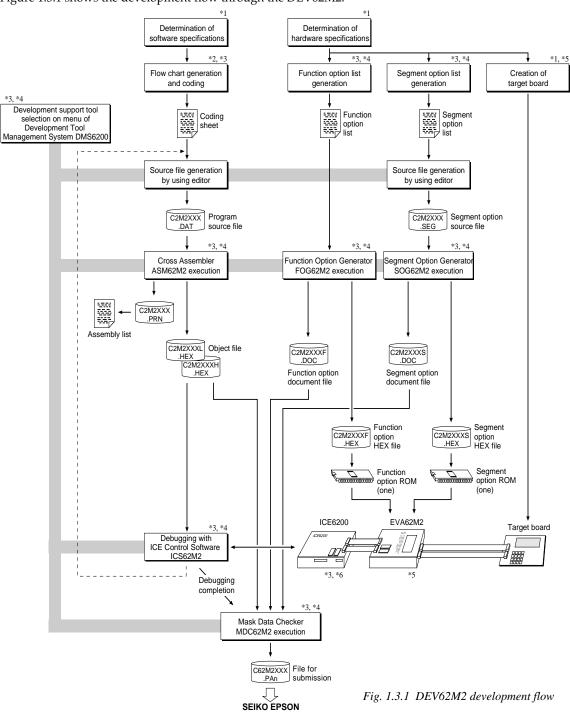

# 1.3 Development Flow

Figure 1.3.1 shows the development flow through the DEV62M2.

### **Concerning file names**

All the input-output file name for the each development support tool commonly use "C2M2XXX". In principle each file should be produced in this manner. Seiko Epson will designate the "XXX" for each customer.

#### Reference Manual

- \*1 E0C62M2 Technical Manual

- \*2 E0C6200/6200A Core CPU Manual

- \*3 E0C62 Family Development Tool Reference Manual

- \*4 E0C62M2 Development Tool Manual (this manual)

- \*5 EVA62M2 Manual

- \*6 ICE6200 Hardware Manual

# 1.4 Production of Execution Disk

Execution files for each software development support tool and batch and parameter files for the ICE6200 are recorded in the DEV62M2 floppy disk.

The content of the files contained in the DEV62M2 floppy disk are shown below.

| PC-DOS version | MS-DOS version | Contents                                          |

|----------------|----------------|---------------------------------------------------|

| ASM62M2.EXE    | ASM62M2.EXE    | Cross Assembler execution file                    |

| DMS6200.EXE    | DMS6200.EXE    | Development Tool Management System execution file |

| FOG62M2.EXE    | FOG62M2.EXE    | Function Option Generator execution file          |

| ICS62M2B.BAT   | ICS62M2.BAT    | ICE Control Software batch file                   |

| ICS62M2W.EXE   | ICS62M2J.EXE   | ICE Control Software execution file               |

| ICS62M2P.PAR   | ICS62M2P.PAR   | ICE Control Software parameter file               |

| MDC62M2.EXE    | MDC62M2.EXE    | Mask Data Checker execution file                  |

| SOG62M2.EXE    | SOG62M2.EXE    | Segment Option Generator execution file           |

First copy the entire content of this disk using commands such as DISKCOPY then make the execution disk. Carefully conserve the original floppy disk for storage purposes.

When copying into a hard disk, make a sub-directory with an appropriate name (DEV62M2, etc.) then copy the content of the floppy disk into that subdirectory using the COPY command.

Next make a CONFIG.SYS file using Editor or the like.

When a CONFIG.SYS has previously been made using a hard disk system, check the setting of the FILES within it. (If there is none add it.) Set the number of files to be described in CONFIG.SYS at 10 or more, so that the Mask Data Checker MDC62M2 will handle many files.

Note The driver for the RS-232C must be included in CONFIG.SYS by the host computer.

It is a good idea to copy the editor into the disk to be copied and the subdirectory so you can also select the editor from the DMS6200 menu.

■ In "ICS62M2(B).BAT" the batch process is indicated such that the ICS62M2J(W).EXE is executed after the execution of the command for the setting of the RS-232C communication parameters. When first executing the ICE Control Software after resetting the host computer, select then activate this batch file from the DMS6200 menu.

The SPEED (MS-DOS) or MODE (PC-DOS) command is used for setting the RS-232C, so you should copy these commands into the disk to be executed or specify a disk or directory with the command using the PATH command.

Note The DMS6200 prepares a menu from files that are in the current directory. Consequently, be sure to arrange the above mentioned files in the same disk or the same directory.

#### Example:

*Copying into a floppy disk* Insert the original disk into the A drive and the formatted disk to be copied into B drive, then execute the DISKCOPY command.

A>DISKCOPY A: B:

*Copying into a hard disk (C drive)* Make a subdirectory (DEV62M2), then insert the original disk into the A drive and execute the COPY command.

C\>MD DEV62M2 J

C\>CD DEV62M2 🖵

C\DEV62M2\>COPY A:\*.\* J

#### Example:

Setting of FILES (CONFIG.SYS) C\>TYPE CONFIG.SYS

FILES=20

*RS-232C Setting (PC-DOS version)* MODE COM2: 4800, n, 8, 1, p

RS-232C Setting (MS-DOS version) SPEED R0 9600 B8 PN S1

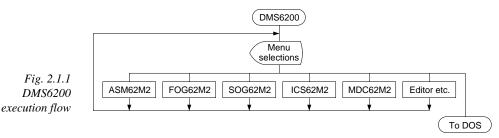

# 2 DEVELOPMENT TOOL MANAGEMENT SYSTEM DMS6200

# 2.1 DMS6200 Outline

The DMS6200 (Development Tool Management System) is a software which selects the DEV62M2 software development support tool and the program such as an editor in menu form and starts it. In this way the various software frequently executed during debugging can be effectively activated.

Refer to the "E0C62 Family Development Tool Reference Manual" for detailes of the operation.

# 2.2 DMS6200 Quick Reference

## Starting command

Execution file:

DMS6200.EXE

Starting command: DMS6200

## Display examples

| *** E0C62                            | 00 Development | tool  | Manageme | nt Syst | em   | Ver 1.0 | * * *  |

|--------------------------------------|----------------|-------|----------|---------|------|---------|--------|

| EEEEEEEE                             | PPPPPPPP       | SSS   | SSSS     | 0000    | 0000 | NNN     | NNN    |

| EEEEEEEEE                            | PPPPPPPPPP     | SSS   | SSSS     | 000     | 000  | NNNN    | NNN    |

| EEE                                  | PPP PPP        | SSS   | SSS      | 000     | 000  | NNNNN   | NNN    |

| EEE                                  | PPP PPP        | SSS   |          | 000     | 000  | NNNNN   | I NNN  |

| EEEEEEEEE                            | PPPPPPPPPP     | SSS   | SSS      | 000     | 000  | NNN NN  | IN NNN |

| EEEEEEEEE                            | PPPPPPPP       |       | SSSS     | 000     | 000  | NNN N   | INNNNN |

| EEE                                  | PPP            |       | SSS      | 000     | 000  | NNN     | NNNNN  |

| EEE                                  | PPP            | SSS   | SSS      | 000     | 000  | NNN     | NNNN   |

| EEEEEEEEE                            | PPP            | SSSS  | SSS      | 000     | 000  | NNN     | NNN    |

| EEEEEEEEE                            | PPP            | SSS   | SSSS     | 0000    | 0000 | NNN     | NN     |

| (C) Copyright 1988 SEIKO EPSON CORP. |                |       |          |         |      |         |        |

|                                      |                | STRIK | E ANY KE | Υ.      |      |         |        |

E0C6200 Development tool Management System. --- Ver 1.0 \*\*\* 1) ASM62M2 .EXE 2) FOG62M2 .EXE 3) ICS62M28.BAT 4) ICS62M29.EXE 5) MDC62M2 .EXE 6) SOG62M2 .EXE Input Number ? [1 ]

E0C6200 Development tool Management System. --- Ver 1.0 \*\*\* 1) ASM62M2 .H 2) C2M20A0 .DAT 3) FOG62M2 .FDT 4) ICS62M2P.PAR 5) MDC62M2 .H 6) SOG62M2 .SDT Input Number ? [1 ] Edit > [ASM62M2 C2M2XXX ] J indicates the Return key. J

### Start message

When DMS6200 is started, the following message is displayed. For "STRIKE ANY KEY.", press any key to advance the program execution.

To suspend execution, press the "CTRL" and "C" keys together: the sequence returns to the DOS command level.

### Menu screen (PC-DOS Version)

A list of all executable files will appear on this menu screen.

Input the number of the development support tool you wish to start and then press the "RETURN" key. To return to DOS at this point, press the "ESC" key.

#### Source file selection screen

To starting ASM62M2, select the source file on this screen. When the source file is selected by number, the edit line enclosed in [] will appear; enter the option parameter if necessary. Press the "RETURN" key when input is completed. When starting, press the "RETURN" key twice particularly for the support tools which do not require source files. To return to DOS at this point, press the "ESC" key.

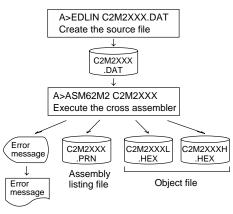

# 3 CROSS ASSEMBLER ASM62M2

# 3.1 ASM62M2 Outline

The ASM62M2 cross assembler is an assembler program for generating the machine code used by the E0C62M2 4-bit, single-chip microcomputers. The Cross Assembler ASM62M2 will assemble the program source files which have been input by the user's editor and will generate an object file in Intel-Hex format and assembly list file.

In this assembler, program modularization has been made possible through macro definition functions and programming independent of the ROM page structure has been made possible through the auto page set function. In addition, consideration has also been given to precise error checks for program capacity (ROM capacity) overflows, undefined codes and the like, and for debugging of such things as label tables for assembly list files and cross reference table supplements.

Fig. 3.1.1 ASM62M2 execution flow

The format of the source file and its operating method are same as for the E0C62 Family. Refer to the "E0C62 Family Development Tool Reference Manual" for details.

# 3.2 E0C62M2 Restrictions

Note the following when generating a program by the E0C62M2:

| ■ <b>ROM area</b>                                                                                                                                                    | <i>Memory configuration:</i>                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The capacity of the E0C62M2                                                                                                                                          | Bank: Only bank 0, Page: 6 pages (0 to 05H), each 256 steps                                                                                                   |

| ROM is 1,536 steps (0000H to<br>05FFH).<br>Therefore, the specification<br>range of the memory setting<br>pseudo-instructions and PSET<br>instruction is restricted. | Significant specification range:ORGpseudo-instruction:0000H to 05FFHPAGEpseudo-instruction:00H to 05HBANKpseudo-instruction:Only 0HPSETinstruction:00H to 05H |

## RAM area

The capacity of the E0C62M2 RAM is 184 words (000H to 0FFH, 4 bits/word). However, note the following points when programming.

- (1) The following addresses become unused area. Memory access is invalid when the unused area is specified. 080H–09FH, 0B0H–0BFH, 0C5H–0C7H, 0CBH, 0D2H–0D3H, 0D7H–0DFH, 0ECH–0EFH, 0F7H–0FFH

- (2) Since RAM is set only 1 page, the page section (XP, YP) of the index register which specifies address is not effective.

## Undefined codes

The following instructions have not been defined in the E0C62M2 instruction sets.

| PUSH | XP   | PUSH | ΥP   |

|------|------|------|------|

| POP  | XP   | POP  | ΥP   |

| LD   | XP,r | LD   | YP,r |

| LD   | r,XP | LD   | r,YP |

# 3.3 ASM62M2 Quick Reference

|                                       | <b>Starting comman</b><br><i>Execution file:</i> |                     | d and input/output files<br>ASM62M2.EXE                                                                                                                                                                                                                                                               | _ indicates a blank.<br>J indicates the Return key.<br>A parameter enclosed by [ ] can be omitted. |  |  |

|---------------------------------------|--------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

|                                       | Starting comm                                    | nand:               | ASM62M2_ [drive-name:] source-file-name [.shp] _ [-N] -                                                                                                                                                                                                                                               |                                                                                                    |  |  |

|                                       | Option:                                          | .shp<br>s<br>h<br>p | Specifies the file I/O drives.<br>Specifies the drive from which the source file is to<br>Specifies the drive to which the object file is to be<br>Specifies the drive to which the assembly listing fi<br>@: Current drive, Z: File is not generated<br>The code (FFH) in the undefined area of prog | output. (A–P, @, Z)<br>le is to be output. (A–P, @, Z)                                             |  |  |

| Input file: C2M2XXX.DAT (Source file) |                                                  |                     |                                                                                                                                                                                                                                                                                                       |                                                                                                    |  |  |

|                                       | Output file:                                     |                     | C2M2XXXL.HEX (Object file, low-order)<br>C2M2XXXH.HEX (Object file, high-order)<br>C2M2XXX.PRN (Assembly listing file)                                                                                                                                                                                | XXH.HEX (Object file, high-order)                                                                  |  |  |

## Display example

|                                                                                                               | *** ASM62M2 CR0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | OSS ASSEMBLER.                                                                                                                                                                                                                                                                                                                                              | Ver                                                           | 2.00 ***                                             |       |                                                                  |

|---------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------|-------|------------------------------------------------------------------|

| EEEEEEEEE<br>EEE<br>EEE<br>EEEEEEEEEE<br>EEE<br>EEE<br>E                                                      | PPPPPPPPP           PP         PPP           PPP         PPP           PPPPPPPPP         PPPPPPP           PPP         PPP           PPP         PPP         PPP           PPP         PPP         PPP         PPP           PPP         PPP         PPP         PPP           PPP         PPP | SSSSSSS           SSS         SSS           SSSS         SSS           SSSS         SSS | 00000<br>000<br>000<br>000<br>000<br>000<br>000<br>000<br>000 | 000<br>000<br>000<br>000<br>000<br>000<br>000<br>000 | NNN N | NNN<br>NNN<br>NNN<br>NNN<br>NNNN<br>NNNN<br>NNNN<br>NNNN<br>NNNN |

|                                                                                                               | (C) COPYRIGHT 1988 SEIKO EPSON CORP.<br>SOURCE FILE NAME IS " C2M2XXX.DAT "                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                             |                                                               |                                                      |       |                                                                  |

|                                                                                                               | THIS SOFTWARE MAKES NEXT FILES.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |                                                               |                                                      |       |                                                                  |

| C2M2XXXH.HEX HIGH BYTE OBJECT FILE.<br>C2M2XXXL.HEX LOW BYTE OBJECT FILE.<br>C2M2XXX .PRN ASSEMBLY LIST FILE. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |                                                               |                                                      |       |                                                                  |

| DO YOU NEE                                                                                                    | ED AUTO PAGE SET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ?? (Y/N) Y                                                                                                                                                                                                                                                                                                                                                  |                                                               |                                                      |       | . (1)                                                            |

| DO YOU NEE                                                                                                    | D CROSS REFEREN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NCE TABLE? (Y/N                                                                                                                                                                                                                                                                                                                                             | ) Y                                                           |                                                      |       | . (2)                                                            |

When ASM62M2 is started, the start-up message is displayed. At (1), select whether or not the auto-page-

When the above operation is completed, ASM62M2 assembles the source file. To suspend execution, press the "CTRL" and "C" keys together at stage (1) or (2).

## Operators

| Arithmetic | operators                                  | Logical operators    |                                           |  |

|------------|--------------------------------------------|----------------------|-------------------------------------------|--|

| +a         | Monadic positive                           | a_AND_b              | Logical product                           |  |

| -a         | Monadic negative                           | a_OR_b               | Logical sum                               |  |

| a+b        | Addition                                   | a_XOR_b              | Exclusive logical sum                     |  |

| a-b        | Subtraction                                | NOT_a                | Logical negation                          |  |

| a*b        | Multiplication                             | Relational operators |                                           |  |

| a/b        | Division                                   | a_EQ_b               | True when a is equal to b                 |  |

| a_MOD_b    | Remainder of a/b                           | a_NE_b               | True when a is not equal to b             |  |

| a_SHL_b    | Shifts a b bits to the left                | a_LT_b               | True when a is less than b                |  |

| a_SHR_b    | Shifts a b bits to the right               | a_LE_b               | True when a is less than or equal to b    |  |

| HIGH_a     | Separates the high-order eight bits from a | a_GT_b               | True when a is greater than b             |  |

| LOW_a      | Separates the low-order eight bits from a  | a_GE_b               | True when a is greater than or equal to b |  |

| Bsoudo  | instruction   | Meaning                              |                | Example of    |         |

|---------|---------------|--------------------------------------|----------------|---------------|---------|

|         | Instruction   | Inteaning                            | Example of Use |               | USE     |

| EQU     | (Equation)    | To allocate data to label            | ABC            | EQU           | 9       |

|         |               |                                      | BCD            | EQU           | ABC+1   |

| SET     | (Set)         | To allocate data to label            | ABC            | SET           | 0001н   |

|         |               | (data can be changed)                | ABC            | SET           | 0002н   |

| DW      | (Define Word) | To define ROM data                   | ABC            | DW            | 'AB'    |

|         |               |                                      | BCD            | DW            | OFFBH   |

| ORG     | (Origin)      | To define location counter           |                | ORG           | 100H    |

|         |               |                                      |                | ORG           | 256     |

| PAGE    | (Page)        | To define boundary of page           |                | PAGE          | 1H      |

|         |               |                                      |                | PAGE          | 3       |

| SECTION | (Section)     | To define boundary of section        |                | SECTION       |         |

| END     | (End)         | To terminate assembly                |                | END           |         |

| MACRO   | (Macro)       | To define macro                      | CHECK<br>LOCAL | MACRO<br>LOOP | DATA    |

| LOCAL   | (Local)       | To make local specification of label | LOOP           | CP            | MX,DATA |

|         | · · · · · /   | during macro definition              |                | JP            | NZ,LOOP |

| ENDM    | (End Macro)   | To end macro definition              |                | ENDM          |         |

|         | (             |                                      |                | CHECK         | 1       |

# Pseudo-instructions

# Error messages

|                        | Error message               | Explanation                                                               |

|------------------------|-----------------------------|---------------------------------------------------------------------------|

| S (Syntax Error)       |                             | An unrecoverable syntax error was encountered.                            |

| U                      | (Undefined Error)           | The label or symbol of the operand has not been defined.                  |

| Μ                      | (Missing Label)             | The label field has been omitted.                                         |

| 0                      | (Operand Error)             | A syntax error was encountered in the operand, or the operand could       |

|                        |                             | not be evaluated.                                                         |

| Р                      | (Phase Error)               | The same label or symbol was defined more than once.                      |

| R                      | (Range Error)               | • A statement exceeded a page boundary although its location was not      |

|                        |                             | specified.                                                                |

|                        |                             | • The location counter value exceeded the upper limit of the program      |

|                        |                             | memory, or a location exceeding the upper limit was specified.            |

|                        |                             | • A value greater than that which the number of significant digits of the |

|                        |                             | operand will accommodate was specified.                                   |

| ! (Warning)            |                             | • Memory areas overlapped because of a "PAGE" or "ORG" pseudo-            |

|                        |                             | instruction or both.                                                      |

| FILE                   | NAME ERROR                  | The source file name was longer than 8 characters.                        |

| FILE                   | NOT PRESENT                 | The specified source file was not found.                                  |

| DIRE                   | ECTORY FULL                 | No space was left in the directory of the specified disk.                 |

| FATAL DISK WRITE ERROR |                             | The file could not be written to the disk.                                |

| LABEL TABLE OVERFLOW   |                             | The number of defined labels and symbols exceeded the label table         |

|                        |                             | capacity (4000).                                                          |

| CRC                    | SS REFERENCE TABLE OVERFLOW | The label/symbol reference count exceeded the cross-reference table       |

|                        |                             | capacity (only when the cross-reference table is generated).              |

# 4 FUNCTION OPTION GENERATOR FOG62M2

# 4.1 FOG62M2 Outline

With the 4-bit single-chip E0C62M2 microcomputers, the customer may select three hardware options. By modifying the mask patterns of the E0C62M2 according to the selected options, the system can be customized to meet the specifications of the target system.

The Function Option Generator FOG62M2 is a software tool for generating data files used to generate mask patterns. It enables the customer to interactively select and specify pertinent items for each hardware option. From the data file created with FOG62M2, the E0C62M2 mask pattern is automatically generated by a general purpose computer.

The HEX file for the evaluation board (EVA62M2) hardware option ROM is simultaneously generated with the data file.

The operating method is same as for the E0C62 Family. Refer to the "E0C62 Family Development Tool Reference Manual" for details.

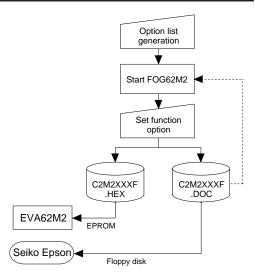

Fig. 4.1.1 FOG62M2 execution flow

□ 2. Gate Direct

2. Gate Direct

□ 2. Pch-OpenDrain

# 4.2 E0C62M2 Option List

Multiple specifications are available in each option item as indicated in the Option List. Using "4.3 Option Specifications and Selection Message" as reference, select the specifications that meet the target system. Be sure to record the specifications for unused ports too, according to the instructions provided.

## 1. INPUT PORT PULL DOWN RESISTOR

- K00 ......□ 1. With Resistor

K01 .....□ 1. With Resistor

K02 ....□ 1. With Resistor

K03 ....□ 1. With Resistor

K10 ....□ 1. With Resistor

K11 ....□ 1. With Resistor

K12 ....□ 1. With Resistor

- K12 ..... □ 1. With Resistor

K13 ...... □ 1. With Resistor

# 2. OUTPUT PORT OUTPUT SPECIFICATION

- R00 ..... 🗆 1. Complementary

- R01 ..... 🗆 1. Complementary

- R02 ..... 1. Complementary

- R03 ..... 1. Complementary

- BZ ..... 🗆 1. Complementary

- /BZ ..... 🗆 1. Complementary

# 3. I/O PORT OUTPUT SPECIFICATION

- P00 ...... □ 1. Complementary

P01 ..... □ 1. Complementary

P02 ..... □ 1. Complementary

P03 .... □ 1. Complementary

□ 2. Pch-OpenDrain

□ 2. Pch-OpenDrain

□ 2. Pch-OpenDrain

□ 2. Pch-OpenDrain

- 8

# 4.3 Option Specifications and Selection Message

Screen that can be selected as function options set on the E0C62M2 are shown below, and their specifications are also described.

## 1 Input port pull down resistor

```

*** OPTION NO.1 ***

--- INPUT PORT PULL DOWN RESISTOR ---

K00

1. WITH RESISTOR

2. GATE DIRECT

PLEASE SELECT NO.(1) ? 1.

K01

1. WITH RESISTOR

2 GATE DIRECT

PLEASE SELECT NO.(1) ? 14

(Selection for K02 to K12)

PLEASE SELECT NO.(1) ? 1.

K13

1. WITH RESISTOR

2. GATE DIRECT

PLEASE SELECT NO.(1) ? 1

к00

1. WITH RESISTOR

SELECTED

K01

1. WITH RESISTOR

SELECTED

K02

1. WITH RESISTOR

SELECTED

K03

1. WITH RESISTOR

SELECTED

K10

1. WITH RESISTOR

SELECTED

K11

1. WITH RESISTOR

SELECTED

K12

1 WITH RESISTOR

SELECTED

K13

WITH RESISTOR

SELECTED

1.

```

# 2 Output port output specification

| *** OPTION NO.2 ***                   |                                                                                                                                                                            |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPUT PORT OUTPUT                    | SPECIFICATION                                                                                                                                                              |

| NO0                                   | <ol> <li>COMPLEMENTARY</li> <li>PCH-OPEN DRAIN</li> </ol>                                                                                                                  |

| PLEASE SELECT NO.(1) ?                | 1.                                                                                                                                                                         |

| (Selec                                | tion for R01 to R03)                                                                                                                                                       |

| PLEASE SELECT NO.(1) ?                | 1.                                                                                                                                                                         |

| BZ                                    |                                                                                                                                                                            |

|                                       | <ol> <li>COMPLEMENTARY</li> <li>PCH-OPEN DRAIN</li> </ol>                                                                                                                  |

| PLEASE SELECT NO.(1) ?                | 11                                                                                                                                                                         |

| /BZ                                   | <ol> <li>COMPLEMENTARY</li> <li>PCH-OPEN DRAIN</li> </ol>                                                                                                                  |

| PLEASE SELECT NO.(1) ?                | 1.                                                                                                                                                                         |

| R00<br>R01<br>R02<br>R03<br>BZ<br>/BZ | 1. COMPLEMENTARY SELECTED<br>1. COMPLEMENTARY SELECTED<br>1. COMPLEMENTARY SELECTED<br>1. COMPLEMENTARY SELECTED<br>1. COMPLEMENTARY SELECTED<br>1. COMPLEMENTARY SELECTED |

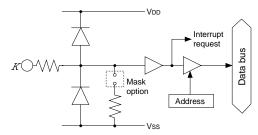

Select whether input ports (K00–K03 and K10–K13) will each be supplemented with pull down resistors or not. When "Gate Direct" is selected, see to it that entry floating state does not occur. Select "With Resistor" pull down resistor for unused ports. Moreover, the input port status is changed from high level (VDD) to low (VSS) with pull down resistors, a delay in waveform fall time will occur depending on the pull down resistor and entry load time constant. Because of this, when input reading is to be conducted, ensure the appropriate wait time with the program.

The configuration of the pull down resistor circuit is shown in Figure 4.3.1.

Fig. 4.3.1 Configuration of pull down resistor circuit

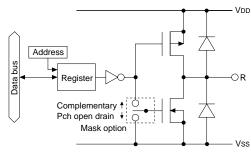

Select the output specification for the output ports (R00–R03, BZ and  $\overline{\text{BZ}}$ ).

Either complementary output or Pch open drain output may be selected.

When output port is to be used on key matrix configuration, select Pch open drain output. For unused output ports, select complementary output.

The output circuit configuration is shown in Figure 4.3.2.

Fig. 4.3.2 Configuration of output circuit

# 3 I/O port output specification

| *** OPTION NO.3 ***       |                                                                                                      |

|---------------------------|------------------------------------------------------------------------------------------------------|

| I/O PORT OUTPUT SPECIFI   | ICATION                                                                                              |

|                           | . COMPLEMENTARY<br>. PCH-OPEN DRAIN                                                                  |

| PLEASE SELECT NO.(1) ? 1  |                                                                                                      |

|                           | . COMPLEMENTARY<br>. PCH-OPEN DRAIN                                                                  |

| PLEASE SELECT NO.(1) ? 1. |                                                                                                      |

|                           | COMPLEMENTARY<br>PCH-OPEN DRAIN                                                                      |

| PLEASE SELECT NO.(1) ? 1  |                                                                                                      |

|                           | COMPLEMENTARY<br>PCH-OPEN DRAIN                                                                      |

| PLEASE SELECT NO.(1) ? 1  |                                                                                                      |

| P01 1.<br>P02 1.          | COMPLEMENTARY SELECTED<br>COMPLEMENTARY SELECTED<br>COMPLEMENTARY SELECTED<br>COMPLEMENTARY SELECTED |

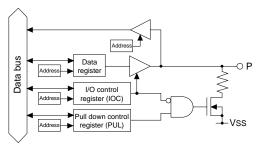

Select the output specification to be used during I/O ports (P00–P03) output mode selection. Either complementary output or Pch open drain output may be selected.

The circuit configuration of the output driver is the same as that of output ports (Rxx shown in Figure 4.3.2).

Select complementary output for unused ports.

The I/O ports can control the input/output direction according to the IOC00–IOC03 register (C8 address, D0 bit–D3 bit); at "1" and "0" settings, it is set to output port and input port, respectively.

When the serial interface function is selected, the output specification of the terminals SOUT, SCLK (during the master mode) and SRDY (during the slave mode) that is used as output in the input/ output port of the serial interface is respectively selected by the mask options of P01, P02 and P03. Selects complementary output for the SIN (P00) output specification.

The I/O port circuit configuration is shown in Figure 4.3.3.

Fig. 4.3.3 Circuit configuration of I/O Port

# 4.4 FOG62M2 Quick Reference

## Starting command and input/output files

| Execution file:   | FOG62M2.EXE                                                                            |                             |

|-------------------|----------------------------------------------------------------------------------------|-----------------------------|

| Starting command: | FOG62M2                                                                                | J indicates the Return key. |

| Input file:       | C2M2XXXF.DOC (Function option document file                                            | e, when modifying)          |

| Output file:      | C2M2XXXF.DOC (Function option document file<br>C2M2XXXF.HEX (Function option HEX file) | e)                          |

#### Display example

| ſ | * * *                                                                                 | E0C62M2 | FUNCTION | OPTION  | GENER. | ATOR    | Ver 3 | .14 *** |       |  |  |

|---|---------------------------------------------------------------------------------------|---------|----------|---------|--------|---------|-------|---------|-------|--|--|

|   | EEEEEEEE                                                                              | E PPPP  | PPPP     | SSSS    | SSS    | 0000    | 00000 | NNN     | NNN   |  |  |

|   | EEEEEEEEE                                                                             | E PPPPI | PPPPPP   | SSS     | SSSS   | 000     | 000   | NNNN    | NNN   |  |  |

| I | EEE                                                                                   | PPP     | PPP      | SSS     | SSS    | 000     | 000   | NNNNN   | NNN   |  |  |

| I | EEE                                                                                   | PPP     | PPP      | SSS     |        | 000     | 000   | NNNNN   | NNN   |  |  |

| I | EEEEEEEEE                                                                             | E PPPPI | PPPPPP   | SSSS    | SS     | 000     | 000   | NNN NNN | INNN  |  |  |

| I | EEEEEEEEE                                                                             | E PPPPI | PPPP     | S       | SSS    | 000     | 000   | NNN NN  | INNNN |  |  |

| I | EEE                                                                                   | PPP     |          |         | SSS    | 000     | 000   | NNN N   | INNNN |  |  |

| I | EEE                                                                                   | PPP     |          | SSS     | SSS    | 000     | 000   | NNN     | NNNN  |  |  |

| I | EEEEEEEEE                                                                             | E PPP   |          | SSSS    | SSS    | 000     | 000   | NNN     | NNN   |  |  |

| I | EEEEEEEEE                                                                             | E PPP   |          | SSSS    | SSS    | 0000    | 00000 | NNN     | NN    |  |  |

|   |                                                                                       | (C)     | COPYRIGH | r 1994  | SEIKO  | EPSON ( | CORP. |         |       |  |  |

|   | THIS SOFTWARE MAKES NEXT FILES.                                                       |         |          |         |        |         |       |         |       |  |  |

|   | C2M2XXXF.HEX FUNCTION OPTION HEX FILE.<br>C2M2XXXF.DOC FUNCTION OPTION DOCUMENT FILE. |         |          |         |        |         |       |         |       |  |  |

|   |                                                                                       |         | S        | TRIKE A | NY KEY |         |       |         |       |  |  |

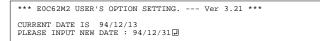

\*\*\* E0C62M2 USER'S OPTION SETTING. --- Ver 3.14 \*\*\* CURRENT DATE IS 1994/12/13 PLEASE INPUT NEW DATE : 1994/12/31

| *** OPERATION SELECT        | MENU *** |

|-----------------------------|----------|

| 1. INPUT NEW                | FILE     |

| 2. EDIT FILE                |          |

| <ol><li>RETURN TO</li></ol> | DOS      |

| PLEASE SELECT NO.?          |          |

| *** OPERATION SELECT MEN                                                                                 | J ***                                                               |

|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 1. INPUT NEW FIL<br>2. EDIT FILE<br>3. RETURN TO DOS                                                     | 2                                                                   |

| PLEASE SELECT NO.? 1<br>PLEASE INPUT FILE NAME ?<br>PLEASE INPUT USER'S NAME<br>PLEASE INPUT ANY COMMENT | ? SEIKO EPSON CORP (2)                                              |

| ( ONE LINE IS 50 CHRS )                                                                                  | ? TOKYO DESIGN CENTER(3)<br>? 421-8 HINO HINO-SHI TOKYO 191 JAPAN ? |

| PLEASE | INPUT | FILE  | NAME ?  | , | C2M20A0 🚽 |

|--------|-------|-------|---------|---|-----------|

| EXISTS | OVERV | WRITE | (Y/N)?  | 2 | ΝIJ       |

| PLEASE | INPUT | FILE  | NAME ?  | 2 | С2М20В0 🚽 |

| PLEASE | INPUT | USER  | 'S NAME | 2 | ?         |

#### Start-up message

When FOG62M2 is started, the start-up message is displayed. For "STRIKE ANY KEY.", press any key to advance the program execution.

To suspend execution, press the "CTRL" and "C" keys together: the sequence returns to the DOS command level.

#### Date input

Enter the 2-digit year, month, and day of the month by delimiting them with a slash ("/"). When not modifying the date, press the RETURN key " []" to continue.

#### **Operation selection menu**

Enter a number from 1 to 3 to select a subsequent operation.

- 1. To set new function options.

- 2. To modify the document file.

- 3. To terminate FOG62M2.

#### Setting new function options

Select "1" on the operation selection menu. (1) Enter the file name.

- (2) Enter the customer's company name.

- (3) Enter any comment.

(Within 50 characters x 10 lines) Next, start function option setting from option No. 1.

In case a function option document file with the same name as the file name specified in the current drive exists, the user is asked whether overwrition is desired. Enter "Y" or "N" accordingly.

| *** OPERATIC                                               | N SELECT MENU **                                                                                                         | *       |                          |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|

| 2. E                                                       | NPUT NEW FILE<br>DIT FILE<br>RETURN TO DOS                                                                               |         |                          |

| PLEASE SELEC                                               | T NO.? 24                                                                                                                |         |                          |

| *** SOURCE F                                               | 'ILE(S) ***                                                                                                              |         |                          |

| C2M20A0                                                    | C2M20B0                                                                                                                  | C2M20C0 | (1)                      |

| PLEASE INPUT<br>PLEASE INPUT<br>( ONE LINE<br>PLEASE INPUT | C FILE NAME ? C2M<br>C USER'S NAME ?<br>C ANY COMMENT<br>IS 50 CHRS ) ?<br>C EDIT NO.? 1<br>:<br>totion option settings) |         | (2)<br>(3)<br>(4)<br>(5) |

| PLEASE INPUT                                               | :<br>7 EDIT NO.? E                                                                                                       |         |                          |

In step (1), if no modifiable source exists, the following message is displayed and the sequence returns to the operation selection menu.

```

*** SOURCE FILE(S) ***

FUNCTION OPTION DOCUMENT FILE IS NOT FOUND.

```

In step (2), if the function option document file is not in the current drive, the following message is displayed, prompting entry of other file name.

| PLEASE INPUT | FILE NAME ? | C2M20N0 🖵   |        |

|--------------|-------------|-------------|--------|

| FUNCTION OPT |             | FILE IS NOT | FOUND. |

| PLEASE INPUT | FILE NAME ? |             |        |

In addition, if specified file format is different (such as document file for the other model), the following message is displayed and FOG62M2 is terminated.

BAD FUNCTION OPTION DOCUMENT FILE.

| *** OPTION NO     | .1 ***                             |

|-------------------|------------------------------------|

| INPUT PORT<br>K00 | PULL DOWN RESISTOR                 |

|                   | 1. WITH RESISTOR<br>2. GATE DIRECT |

| PLEASE SELECT     | NO.(1) ? 2.                        |

| K01               | 1. WITH RESISTOR<br>2. GATE DIRECT |

| PLEASE SELECT     | NO.(1) ? BJ                        |

| *** OPTION NO     | .1 ***                             |

| INPUT PORT<br>K00 | PULL DOWN RESISTOR                 |

|                   | 1. WITH RESISTOR<br>2. GATE DIRECT |

| PLEASE SELECT     | NO.(2) ?                           |

#### Modifying function option settings

Select "2" on the operation selection menu.

- (1) Will display the files on the current drive.

- (2) Enter the file name.

- (3) Enter the customer's company name.

- (4) Enter any comment.Previously entered data can be used by pressing the RETURN key " " at (3) and (4).

- (5) Enter the number of the function option to be modified. When selection of one option is complete, the system prompts entry of another function option number. Repeat selection until all options to be modified are selected. Enter "E..." to end option setting. Then, move to the confirmation procedure for HEX file generation.

#### **Option** selection

The selections for each option correspond one to one to the option list. Enter the selection number. The value in parentheses () indicates the default value, and is set when only the RETURN key "]" is pressed.

In return, the confirmation is displayed. When you wish to modify previously set function options in the new setting process, enter "B. " to return 1 step back to the previous function option setting operation.

#### **EPROM** selection

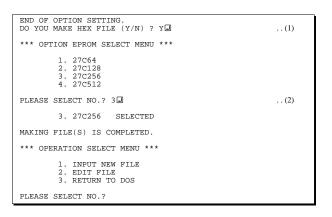

When setting function options setting is completed, the following message is output to ask the operator whether to generate the HEX file.

- When debugging the program with EVA62M2, HEX file is needed, so enter "Y ]". If "N ]" is entered, no HEX file is generated and only document file is generated.

- (2) For the option ROM selection menu displayed when "Y ]" is entered in Step (1), select the EPROM to be used for setting EVA62M2 options.

When a series of operations are complete, the sequence returns to the operation selection menu.

# 4.5 Sample File

```

Example of function option document file

* E0C62M2 FUNCTION OPTION DOCUMENT V 3.14

* FILE NAME

C2M20A0F.DOC

* USER'S NAME SEIKO EPSON CORP.

* INPUT DATE

1994/12/31

* COMMENT

TOKYO DESIGN CENTER

421-8 HINO HINO-SHI TOKYO 191 JAPAN

*

*

OPTION NO.1

*

< INPUT PORT PULL DOWN RESISTOR >

WITH RESISTOR ----- SELECTED

K00

*

K01

WITH RESISTOR ----- SELECTED

*

K02

WITH RESISTOR ----- SELECTED

*

K03

WITH RESISTOR ----- SELECTED

*

WITH RESISTOR ----- SELECTED

K10

*

K11

WITH RESISTOR ----- SELECTED

*

WITH RESISTOR ----- SELECTED

K12

WITH RESISTOR ----- SELECTED

K13

OPT0101 01

OPT0102 01

OPT0103 01

OPT0104 01

OPT0105 01

OPT0106 01

OPT0107 01

OPT0108 01

* OPTION NO.2

*

< OUTPUT PORT OUTPUT SPECIFICATION >

*

R00

COMPLEMENTARY

----- SELECTED

*

R01

COMPLEMENTARY ----- SELECTED

*

R02

COMPLEMENTARY

_____

SELECTED

*

R03

COMPLEMENTARY

_____

SELECTED

*

BZ

COMPLEMENTARY

----- SELECTED

COMPLEMENTARY ----- SELECTED

/R7

OPT0201 01

OPT0202 01

OPT0203 01

OPT0204 01

OPT0205 01

OPT0206 01

* OPTION NO.3

* < I/O PORT OUTPUT SPECIFICATION >

*

P00

COMPLEMENTARY ----- SELECTED

*

P01

COMPLEMENTARY ----- SELECTED

*

P02

COMPLEMENTARY ----- SELECTED

P03

COMPLEMENTARY ----- SELECTED

OPT0301 01

OPT0302 01

OPT0303 01

OPT0304 01

```

E0C62M2 Development Tool Manual (FOG62M2)

```

*

* SEIKO EPSON'S AREA

*

*

*

* OPTION NO.4

OPT0401 01

*

* OPTION NO.5

OPT0501 01

*

* OPTION NO.6

OPT0601 01

*

* OPTION NO.7

OPT0701 01

*

* OPTION NO.8

OPT0801 01

*

* OPTION NO.9

OPT0901 01

*

* OPTION NO.10

OPT1001 01

\ \ END

```

Note End mark "¥¥END" may be used instead of "\\END" depending on the PC used. (The code of \ and ¥ is 5CH.)

# 5 SEGMENT OPTION GENERATOR SOG62M2

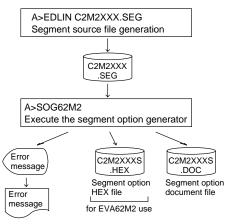

# 5.1 SOG62M2 Outline

With the 4-bit single-chip E0C62M2 microcomputers, the customer may select the LCD segment options. By modifying the mask patterns of the E0C62M2 according to the selected options, the system can be customized to meet the specifications of the target system. The Segment Option Generator SOG62M2 is a software tool for generating data file used to generate mask patterns. From the data file created with SOG62M2, the E0C62M2 mask pattern is automatically generated by a general purpose computer.

The HEX file for the evaluation board (EVA62M2) segment option ROM is simultaneously generated with the data file.

The operating method is same as for the E0C62 Family. Refer to the "E0C62 Family Development Tool Reference Manual" for details.

Fig. 5.1.1 SOG62M2 execution flow

|          |                                                                                                                                                                           |      |      |      | Α     | DD     |      |       |                          |      |     |   |                                    |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--------|------|-------|--------------------------|------|-----|---|------------------------------------|--|

| TERMINAL | COM0                                                                                                                                                                      |      |      | COM1 |       |        | COM2 |       |                          | COM3 |     | 3 | OUTPUT SPECIFICATION               |  |

| NAME     | Н                                                                                                                                                                         | L    | D    | Н    | L     | D      | Н    | L     | D                        | Н    | L   | D |                                    |  |

| SEG0     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG1     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🗌 C 🔤 P                  |  |

| SEG2     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG3     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🗌 P                  |  |

| SEG4     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG5     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🔤 P                  |  |

| SEG6     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG7     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🛛 P                  |  |

| SEG8     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG9     |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🛛 P                  |  |

| SEG10    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG11    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🛛 P                  |  |

| SEG12    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG13    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🛛 C 🛛 P                  |  |

| SEG14    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | SEG output                         |  |

| SEG15    |                                                                                                                                                                           |      |      |      |       |        |      |       |                          |      |     |   | DC output 🗌 C 🗌 P                  |  |

| Legend:  | </td <td>ADD</td> <td>RES</td> <td>S&gt;</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td><output specification=""></output></td> | ADD  | RES  | S>   |       |        |      |       |                          |      |     |   | <output specification=""></output> |  |

|          |                                                                                                                                                                           | H: H | High | orde | r add | lress, | L: L | low o | order                    | addr | ess |   | C: Complementary output            |  |

|          | H: High order address, L: Low order address<br>D: Data bit                                                                                                                |      |      |      |       |        |      |       | P: Pch open drain output |      |     |   |                                    |  |

# 5.2 Option List

Note:

1. Even if there are unused areas, set "---" (hyphens) such that there are no blank columns.

2. When DC output is selected, the display memory of the COM0 column becomes effective.

# 5.3 Segment Ports Output Specifications

For the output specification of the segment output ports SEG0–SEG15, segment output and DC output can be selected in units of two terminals. When used for liquid crystal panel drives, select segment output; when used as regular output port, select DC output. When DC output is selected, either complementary output or Pch open drain output may further be selected.

However, for segment output ports that will not be used, select segment output.

Refer to the "E0C62 Family Development Tool Reference Manual" for the segment option source file creation.

### When segment output is selected

The segment output port has a segment decoder built-in, and the data bit of the optional address in the display memory area (A0H–AFH) can be allocated to the optional segment. With this, up to 64 segments (48 segments when 1/3 duty is selected, respectively) of liquid crystal panel could be driven. The display memory may be allocated only one segment and multiple setting is not possible. The allocated segment displays when the bit for this display memory is set to "1", and goes out when bit

The allocated segment displays when the bit for this display memory is set to "1", and goes out when bit is set to "0".

Segment allocation is set to H for high address (A), to L for low address (0–F), and to D for data bit (0–3) and are recorded in their respective column in the option list. For segment ports that will not be used, write "---" (hyphen) in the H, L, and D columns of COM0–COM3.

#### Examples

| • When 1/4 duty is selected |     |     |     |     |   |  |  |  |  |  |  |  |  |

|-----------------------------|-----|-----|-----|-----|---|--|--|--|--|--|--|--|--|

| 0                           | A00 | A01 | A02 | A03 | S |  |  |  |  |  |  |  |  |

| 1                           | A10 | A11 | A12 | A13 | S |  |  |  |  |  |  |  |  |

• When 1/3 duty is selected

0 A00 A01 A02 --- S

1 A10 A11 A12 --- S

### ■ When DC output is selected

The DC output can be selected in units of two terminals and up to 16 terminals may be allocated for DC output. Also, either complementary output or Pch open drain output is likewise selected in units of two terminals. When the bit for the selected display memory is set to "1", the segment output port goes high (VDD), and goes low (VSS) when set to "0". Segment allocation is the same as when segment output is selected but for the while the display memory allocated to COM1–COM3 becomes ineffective. Write three hyphens ("---") in the COM1–COM3 columns in the option list.

#### Example

• When complementary output is set to SEG12 and SEG13, and Pch open drain output is set to SEG14 and SEG15.

| 12 | AC0 | <br> | <br>С |

|----|-----|------|-------|

| 13 | AD0 | <br> | <br>С |

|    | AE0 |      |       |

| 15 | AF0 | <br> | <br>Ρ |

Note Only complementary output is enabled as the DC output of the SEG ports of EVA62M2. Therefore, complementary output is enabled even if Pch open drain output is selected. Respond to it by adding external circuits as required.

# 5.4 SOG62M2 Quick Reference

| Starting command and input/output files |                                                                                                            |                                                     |  |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| Execution file:                         | SOG62M2.EXE                                                                                                | _ indicates a blank.<br>♫ indicates the Return key. |  |  |  |

| Starting command:                       | SOG62M2_[-H] -                                                                                             | A parameter enclosed by [] can be omitted.          |  |  |  |

| Option:                                 | -H: Specifies the segment option document file for input file of SOG62M2.                                  |                                                     |  |  |  |

| Input file:                             | C2M2XXX.SEG (Segment option source file)<br>C2M2XXXS.DOC(Segment option document file, when -H option use) |                                                     |  |  |  |

| Output file:                            | C2M2XXXS.DOC(Segment option document file<br>C2M2XXXS.HEX (Segment option HEX file)                        | 2)                                                  |  |  |  |

## Display example

| *** E                                                                               | 0C62M2                          | SEGMENT  | OPTION   | GENERA  | FOR      | Ver 3.2 | 21 *** | ÷       |

|-------------------------------------------------------------------------------------|---------------------------------|----------|----------|---------|----------|---------|--------|---------|

| EEEEEEEEE                                                                           | PPPPP                           | PPP      | SSSS     | SSSS    | 0000     | 0000    | NNN    | NNN     |

| EEEEEEEEE                                                                           | PPPPF                           | PPPPPP   | SSS      | SSSS    | 000      | 000     | NNNN   | NNN     |

| EEE                                                                                 | PPP                             | PPP      | SSS      | SSS     | 000      | 000     | NNNNN  | J NNN   |

| EEE                                                                                 | PPP                             | PPP      | SSS      |         | 000      | 000     | NNNNN  | IN NNN  |

| EEEEEEEEE                                                                           | PPPPF                           | PPPPP    | SSSS     | SSS     | 000      | 000     | NNN N  | INN NNN |