MF740-03

# CMOS 4-BIT SINGLE CHIP MICROCOMPUTER

## E0C6247 Technical Hardware E0C6247 Technical Software

**SEIKO EPSON CORPORATION**

#### NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency. Please note that "E0C" is the new name for the old product "SMC". If "SMC" appears in other manuals understand that it now reads "E0C".

## PREFACE

This manual is individually described about the hardware and the software of the E0C6247.

## I. E0C6247 Technical Hardware

This part explains the function of the E0C6247, the circuit configurations, and details the controlling method.

## II. E0C6247 Technical Software

This part explains the programming method of the E0C6247.

# E0C6247 Technical Hardware

## **CONTENTS**

| CHAPTER 1 | OverviewI-1                    |                                                                                              |             |  |  |  |  |  |  |  |  |

|-----------|--------------------------------|----------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|--|--|--|

|           | 1.1                            | Features                                                                                     | I-1         |  |  |  |  |  |  |  |  |

|           | 1.2                            | Block Diagram                                                                                | <i>I-2</i>  |  |  |  |  |  |  |  |  |

|           | 1.3                            | Pin Layout Diagram                                                                           |             |  |  |  |  |  |  |  |  |

|           |                                |                                                                                              |             |  |  |  |  |  |  |  |  |

|           | 1.4                            | Pin Description                                                                              | 1-4         |  |  |  |  |  |  |  |  |

| CHAPTER 2 | Power Supply and Initial Reset |                                                                                              |             |  |  |  |  |  |  |  |  |

|           | 2.1                            | Power Supply                                                                                 | <i>I-5</i>  |  |  |  |  |  |  |  |  |

|           |                                | 2.1.1 Voltage <vd1> for oscillation circuit and internal circuits</vd1>                      | I-6         |  |  |  |  |  |  |  |  |

|           |                                | 2.1.2 Voltage <vc1–vc5> for LCD driving</vc1–vc5>                                            |             |  |  |  |  |  |  |  |  |

|           |                                | 2.1.3 Voltage doubler/halver and operating mode                                              | <i>I-7</i>  |  |  |  |  |  |  |  |  |

|           | 2.2                            | Initial Reset                                                                                |             |  |  |  |  |  |  |  |  |

|           |                                | 2.2.1 Reset terminal ( $\overline{RESET}$ )                                                  |             |  |  |  |  |  |  |  |  |

|           |                                | 2.2.2 Simultaneous low input to terminals K00–K03                                            |             |  |  |  |  |  |  |  |  |

|           |                                | 2.2.3 Oscillation detection circuit                                                          |             |  |  |  |  |  |  |  |  |

|           |                                | 2.2.4 Watchdog timer<br>2.2.5 Internal register at initial resetting                         |             |  |  |  |  |  |  |  |  |

|           |                                | 2.2.5 Internal register at initial resetting<br>2.2.6 Terminal settings at initial resetting |             |  |  |  |  |  |  |  |  |

|           | 2.3                            | Test Terminal (TEST)                                                                         |             |  |  |  |  |  |  |  |  |

|           | 2.3                            | Test Terminut (TEST)                                                                         | 1-10        |  |  |  |  |  |  |  |  |

| CHAPTER 3 | СР                             | U, ROM, RAM                                                                                  | I-1         |  |  |  |  |  |  |  |  |

|           | 3.1                            | <i>CPU</i>                                                                                   | <i>I-11</i> |  |  |  |  |  |  |  |  |

|           | 3.2                            | ROM                                                                                          | I-11        |  |  |  |  |  |  |  |  |

|           | 3.3                            | RAM                                                                                          |             |  |  |  |  |  |  |  |  |

|           |                                |                                                                                              |             |  |  |  |  |  |  |  |  |

|           | 3.4                            | External Memory                                                                              | 1-11        |  |  |  |  |  |  |  |  |

| CHAPTER 4 | Pei                            | RIPHERAL CIRCUITS AND OPERATION                                                              | I-1         |  |  |  |  |  |  |  |  |

|           | 4.1                            | Memory Map                                                                                   | <i>I-12</i> |  |  |  |  |  |  |  |  |

|           | 4.2                            | Setting of Power Supply and Operating Mode                                                   | <i>I-22</i> |  |  |  |  |  |  |  |  |

|           |                                | 4.2.1 Control of supply voltage doubler/halver                                               |             |  |  |  |  |  |  |  |  |

|           |                                | 4.2.2 Operating mode for oscillation system regulated voltage circuit                        |             |  |  |  |  |  |  |  |  |

|           |                                | and internal operating voltage                                                               |             |  |  |  |  |  |  |  |  |

|           |                                | 4.2.3 Operating mode for LCD system voltage circuit and reference voltag                     |             |  |  |  |  |  |  |  |  |

|           |                                | for LCD driving                                                                              |             |  |  |  |  |  |  |  |  |

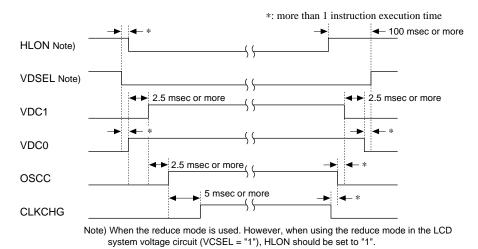

|           |                                | 4.2.4 Control of power supply and operating mode<br>4.2.5 Programming notes                  |             |  |  |  |  |  |  |  |  |

|           | 1 2                            |                                                                                              |             |  |  |  |  |  |  |  |  |

|           | 4.3                            | Resetting Watchdog Timer                                                                     |             |  |  |  |  |  |  |  |  |

|           |                                | 4.3.2 Mask option                                                                            |             |  |  |  |  |  |  |  |  |

|           |                                | 4.3.3 Control of watchdog timer                                                              |             |  |  |  |  |  |  |  |  |

|           |                                | 4.3.4 Programming note                                                                       |             |  |  |  |  |  |  |  |  |

|           | 4.4                            | Oscillation Circuit                                                                          |             |  |  |  |  |  |  |  |  |

|           | 7.4                            | 4.4.1 Configuration of oscillation circuit                                                   |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.2 OSC1 oscillation circuit                                                               |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.3 OSC3 oscillation circuit                                                               |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.4 Switching of operating voltage                                                         |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.5 Clock frequency and instruction execution time                                         |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.6 Control of oscillation circuit                                                         |             |  |  |  |  |  |  |  |  |

|           |                                | 4.4.7 Programming notes                                                                      | I-32        |  |  |  |  |  |  |  |  |

## CONTENTS

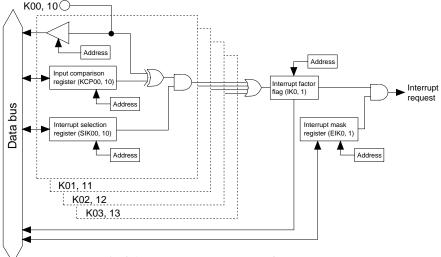

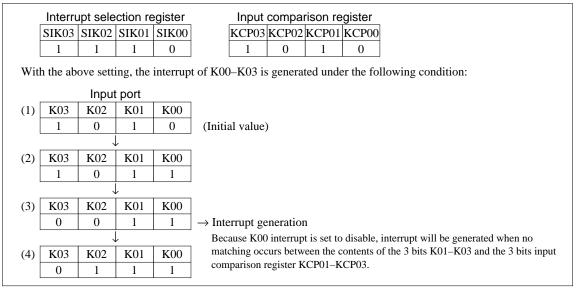

| 4.5  | Input Ports (K00–K03 and K10–K13)                                 | <i>I-33</i>  |

|------|-------------------------------------------------------------------|--------------|

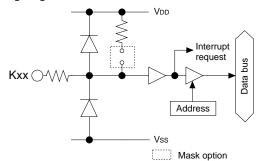

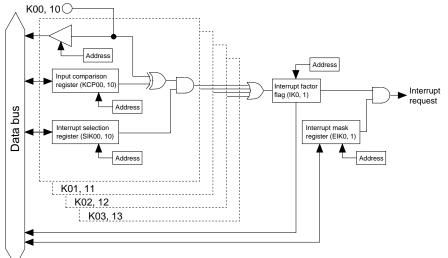

|      | 4.5.1 Configuration of input ports                                |              |

|      | 4.5.2 Interrupt function                                          |              |

|      | 4.5.3 Mask option                                                 |              |

|      | 4.5.4 Control of input ports                                      |              |

|      | 4.5.5 Programming notes                                           |              |

|      |                                                                   |              |

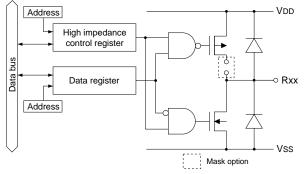

| 4.6  | Output Ports (R00-R03, R10-R13, R20-R23, R30-R33 and R40-R4.      |              |

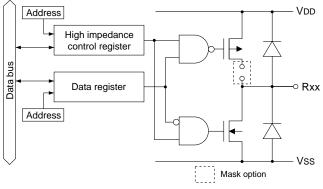

|      | 4.6.1 Configuration of output ports                               | <i>I-3</i> 8 |

|      | 4.6.2 Mask option                                                 | I-39         |

|      | 4.6.3 High impedance control                                      | I-39         |

|      | 4.6.4 Control of output ports                                     |              |

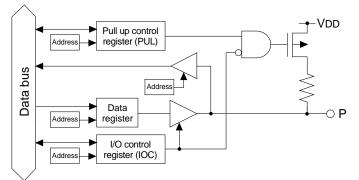

| 17   | <i>I/O Ports (P00–P03, P10–P13, P20–P23, P30–P33 and P40–P43)</i> |              |

| 4.7  |                                                                   |              |

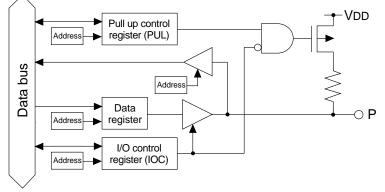

|      | 4.7.1 Configuration of I/O ports                                  |              |

|      | 4.7.2 I/O control registers and input/output mode                 |              |

|      | 4.7.3 Pull up during input mode                                   |              |

|      | 4.7.4 Mask option                                                 | I-44         |

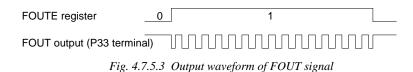

|      | 4.7.5 Special outputs (CL, FR, PTOVF, FOUT)                       | I-45         |

|      | 4.7.6 Control of I/O ports                                        | I-47         |

|      | 4.7.7 Programming notes                                           | I-52         |

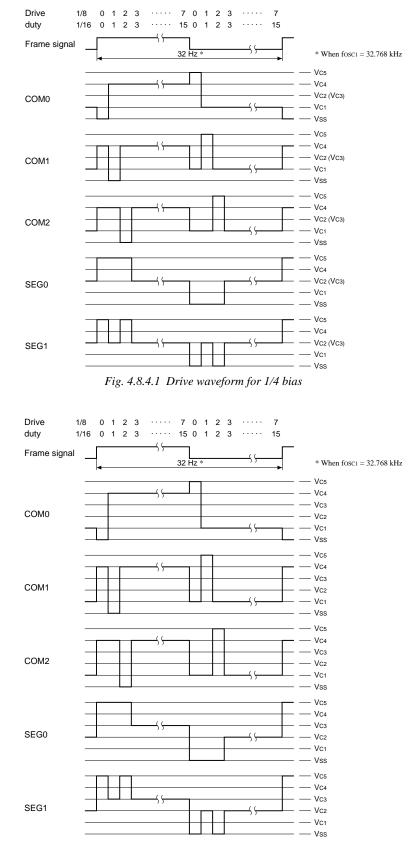

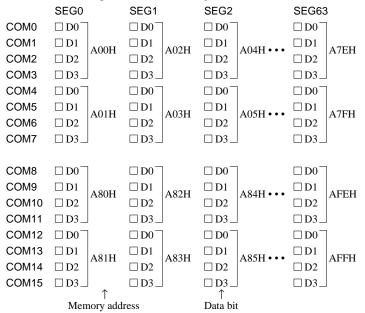

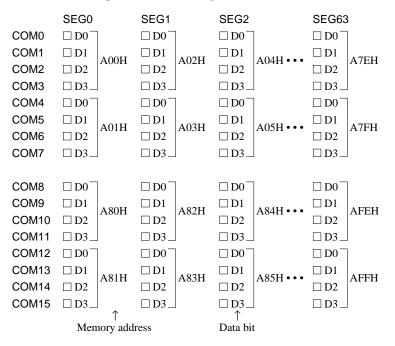

| 4.8  | LCD Driver (COM0–COM15, SEG0–SEG63)                               | 1 53         |

| 4.0  |                                                                   |              |

|      | 4.8.1 Configuration of LCD driver                                 |              |

|      | 4.8.2 Power supply for LCD driving                                |              |

|      | 4.8.3 Mask option                                                 |              |

|      | 4.8.4 LCD display control (ON/OFF) and switching of duty          |              |

|      | 4.8.5 Display memory                                              |              |

|      | 4.8.6 LCD contrast adjustment                                     | I-56         |

|      | 4.8.7 Control of LCD driver                                       | I-57         |

|      | 4.8.8 Programming note                                            | I-58         |

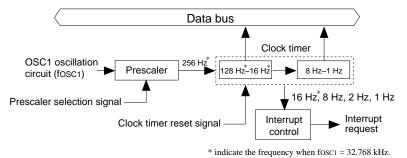

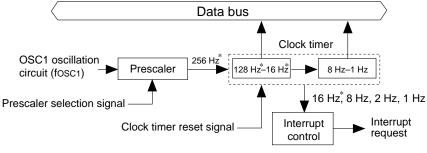

| 4.9  | Clock Timer                                                       | 1 50         |

| 4.9  |                                                                   |              |

|      | 4.9.1 Configuration of clock timer                                |              |

|      | 4.9.2 Data reading and hold function                              |              |

|      | 4.9.3 Interrupt function                                          |              |

|      | 4.9.4 Control of clock timer                                      |              |

|      | 4.9.5 Programming notes                                           | I-62         |

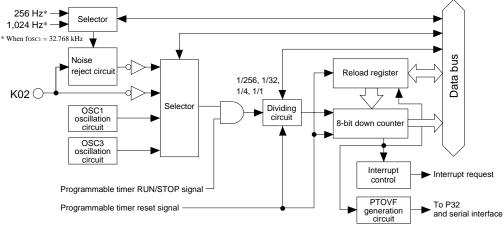

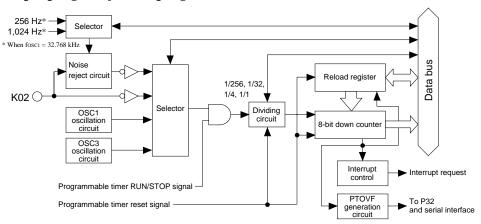

| 4.10 | Programmable Timer                                                | I-63         |

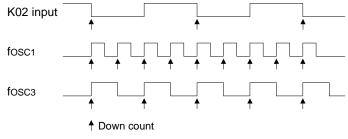

|      | 4.10.1 Configuration of programmable timer                        |              |

|      | 4.10.2 Input clock and pre-divider                                |              |

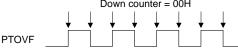

|      | 4.10.3 Operation of programmable timer                            |              |

|      | 4.10.4 Interrupt function                                         |              |

|      | 4.10.5 Control of programmable timer                              |              |

|      |                                                                   |              |

|      | 4.10.6 Programming notes                                          | 1-09         |

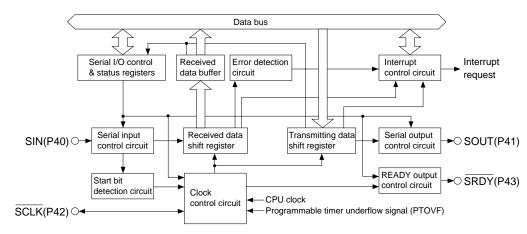

| 4.11 | Serial Interface                                                  | <i>I-70</i>  |

|      | 4.11.1 Configuration of serial interface                          | I-70         |

|      | 4.11.2 Mask option                                                |              |

|      | 4.11.3 Transfer modes                                             |              |

|      | 4.11.4 Clock source                                               |              |

|      | 4.11.5 Transmit-receive control                                   |              |

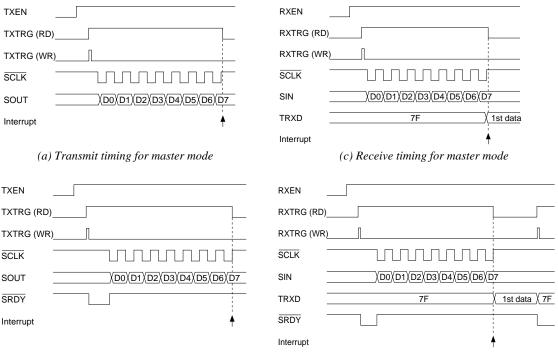

|      | 4.11.6 Operation of clock synchronous transfer                    |              |

|      | 4.11.7 Operation of asynchronous transfer                         |              |

|      |                                                                   |              |

|      | 4.11.8 Interrupt function                                         |              |

|      | 4.11.9 Control of serial interface                                |              |

|      | 4.11.10 Programming notes                                         | 1-90         |

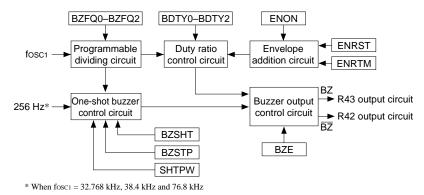

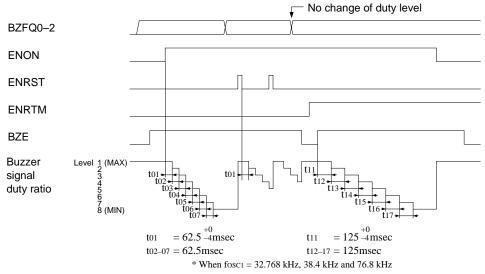

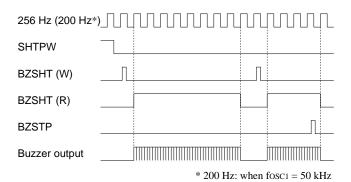

| 4.12 | Sound Generator                                                   | <i>I-91</i>  |

| _    | 4.12.1 Configuration of sound generator                           |              |

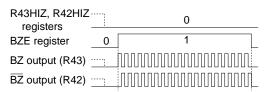

|      | 4.12.2 Control of buzzer output                                   |              |

|      | 4.12.3 Setting of buzzer frequency and sound level                |              |

|      | 4.12.5 Setting of buzzer frequency and sound tever                |              |

|      | 1.12. 1 Digital chreiope                                          | 1-75         |

## CONTENTS

|           |             | 4.12.5 One-shot output                                                                                                                        | <i>I-93</i>   |

|-----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|           |             | 4.12.6 Control of sound generator                                                                                                             |               |

|           |             | 4.12.7 Programming note                                                                                                                       | I-97          |

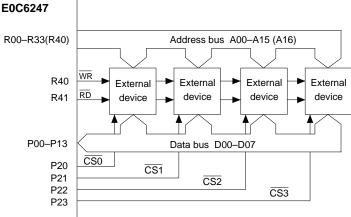

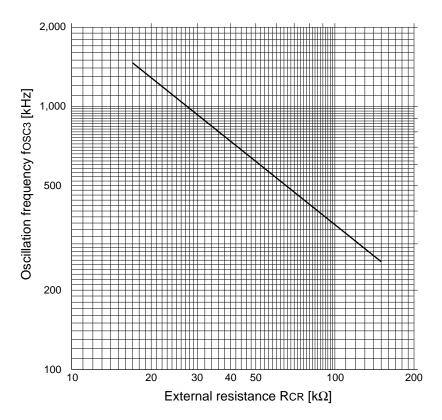

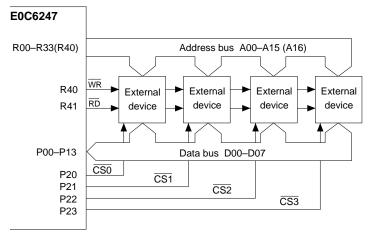

|           | 4.13        | External Memory Access                                                                                                                        | <i>I-9</i> 8  |

|           |             | 4.13.1 Address bus                                                                                                                            |               |

|           |             | 4.13.2 Data bus                                                                                                                               |               |

|           |             | 4.13.3 Write signal ( $\overline{WR}$ ) and read signal ( $\overline{RD}$ )<br>4.13.4 Chip select signals ( $\overline{CSO}-\overline{CS3}$ ) |               |

|           |             | 4.13.5 High impedance control for external bus                                                                                                |               |

|           |             | 4.13.6 External memory read/write sequence                                                                                                    |               |

|           |             | 4.13.7 Control of external memory access function                                                                                             |               |

|           |             | 4.13.8 Programming note                                                                                                                       | I-105         |

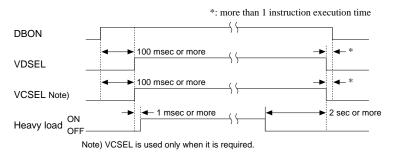

|           | 4.14        | SVD (Supply Voltage Detection) Circuit                                                                                                        | I-106         |

|           |             | 4.14.1 Configuration of SVD circuit                                                                                                           | I-106         |

|           |             | 4.14.2 SVD operation                                                                                                                          |               |

|           |             | 4.14.3 Control of SVD circuit                                                                                                                 |               |

|           |             | 4.14.4 Programming notes                                                                                                                      |               |

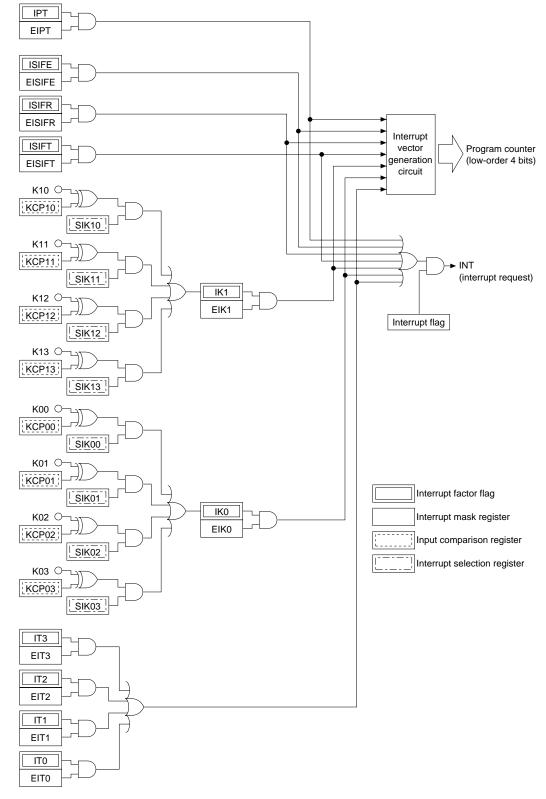

|           | 4.15        | Interrupt and HALT                                                                                                                            |               |

|           |             | 4.15.1 Interrupt factor                                                                                                                       |               |

|           |             | 4.15.2 Interrupt mask<br>4.15.3 Interrupt vector                                                                                              |               |

|           |             | 4.15.4 Control of interrupt                                                                                                                   |               |

|           |             | 4.15.5 Programming notes                                                                                                                      |               |

| CHAPTER 5 | Sum         | IMARY OF NOTES                                                                                                                                | I-114         |

|           | 5.1         | Notes for Low Current Consumption                                                                                                             | <i>I-114</i>  |

|           | 5.2         | Summary of Notes by Function                                                                                                                  |               |

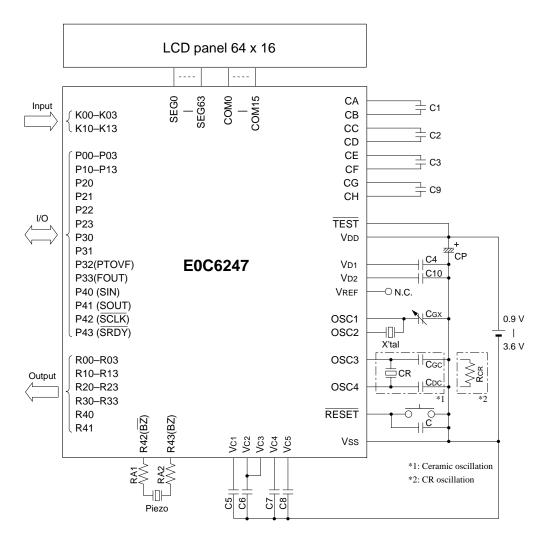

| CHAPTER 6 | BAS         | IC EXTERNAL WIRING DIAGRAM                                                                                                                    | <i>I-118</i>  |

| CHAPTER 7 | Ele         | CTRICAL CHARACTERISTICS                                                                                                                       | I-119         |

|           | 7.1         |                                                                                                                                               |               |

|           |             | Absolute Maximum Rating                                                                                                                       |               |

|           | 7.2         | Recommended Operating Conditions                                                                                                              |               |

|           | 7.3         | DC Characteristics                                                                                                                            |               |

|           | 7.4         | Analog Circuit Characteristics and Power Current Consumption                                                                                  |               |

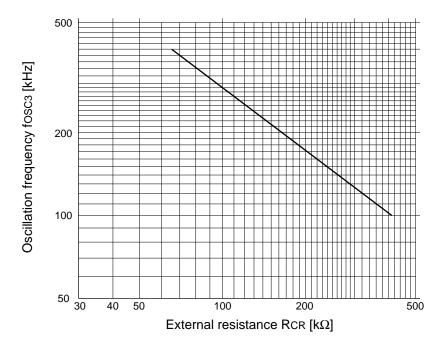

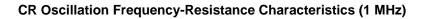

|           | 7.5         | Oscillation Characteristics                                                                                                                   | <i>I-124</i>  |

|           | 7.6         | External Memory Access AC Characteristics                                                                                                     | <i>I-126</i>  |

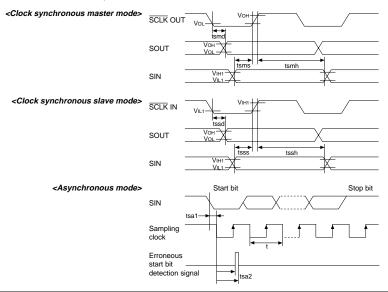

|           | 7.7         | Serial Interface AC Characteristics                                                                                                           | <i>I-127</i>  |

|           | 7.8         | Timing Chart                                                                                                                                  | <i>I-12</i> 8 |

| CHAPTER 8 | PAC         | KAGE                                                                                                                                          | <i>I-129</i>  |

|           | 8.1         | Plastic Package                                                                                                                               |               |

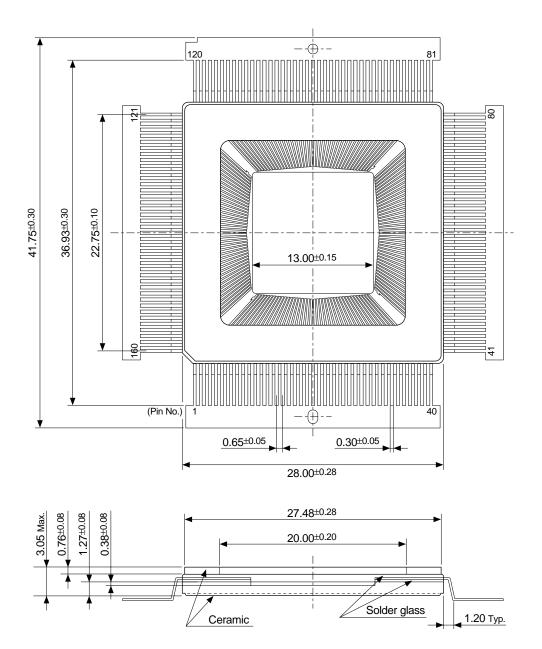

|           | 8.2         | Ceramic Package for Test Samples                                                                                                              |               |

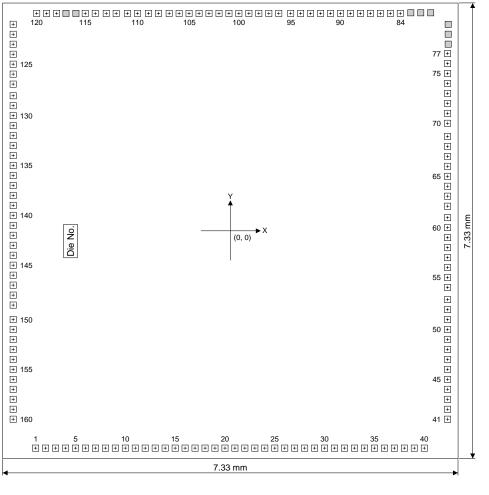

| CHAPTER 9 | <b>P</b> AD | LAYOUT                                                                                                                                        | I-131         |

|           | 9.1         | Diagram of Pad Layout                                                                                                                         |               |

|           | 9.2         | Pad Coordinates                                                                                                                               |               |

## CHAPTER 1 OVERVIEW

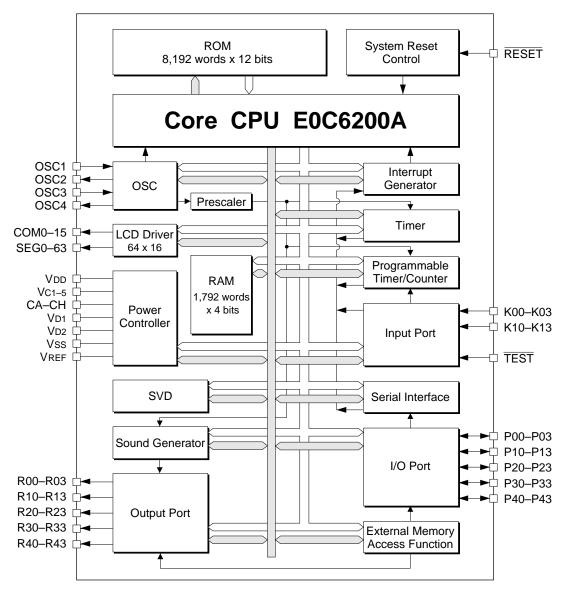

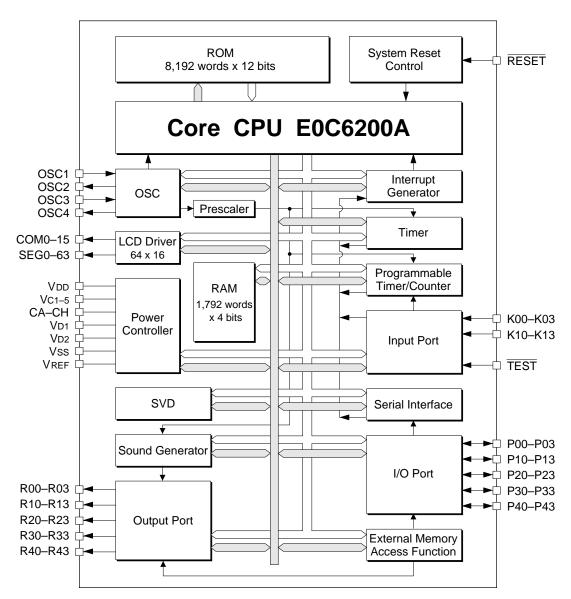

The E0C6247 is a single-chip microcomputer made up of the 4-bit core CPU E0C6200A, ROM (8,192 words, 12 bits to a word), RAM (1,792 words, 4 bits to a word), dot matrix LCD driver, serial interface, watchdog timer, programmable timer, time base counter and SVD circuit. Moreover, in the E0C6247 external memory device control is possible, and are most suitable for applications with equipment requiring large memory and dot matrix display functions such as a highly functional electronic pocketbook.

## 1.1 Features

| OSC1 oscillation circuit                                            | 32.768 kHz/38.4 kHz/50 kHz/76.                                                                                      | 8 kHz (Typ.) crystal oscillation circuit                                                                                                                                                                                                                                            |  |  |  |  |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OSC3 oscillation circuit                                            | 200 kHz/1 MHz (Typ.) CR or cer                                                                                      |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Instruction set                                                     | 108 types                                                                                                           |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| <i>Instruction execution time</i> (differ depending on instruction) | During operation at 32 kHz:<br>During operation at 38.4 kHz:                                                        | 153 μsec,       214 μsec,       366 μsec         130 μsec,       182 μsec,       313 μsec         100 μsec,       140 μsec,       240 μsec         65 μsec,       91 μsec,       156 μsec         25 μsec,       35 μsec,       60 μsec         5 μsec,       7 μsec,       12 μsec |  |  |  |  |

| ROM capacity                                                        | 8,192 words $\times$ 12 bits                                                                                        |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| RAM capacity                                                        | Data memory:1,792 wordsDisplay memory:256 words ×                                                                   |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| External memory capacity                                            | Read/write (RAM): max. 512K-<br>Read only (ROM): max. 1M-bit                                                        |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Input port                                                          | 8 bits (Pull up resistors may                                                                                       | be supplemented *1)                                                                                                                                                                                                                                                                 |  |  |  |  |

| Output port                                                         | 20 bits (Switching to external                                                                                      | memory bus and buzzer output are possible *2)                                                                                                                                                                                                                                       |  |  |  |  |

| I/O port                                                            | and serial inputs/outputs are possible *2)rface1 port(Clock synchronous system, Asynchronous system 8-bit/7-bit *2) |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Serial interface                                                    | 1 port (Clock synchronous sy                                                                                        | vstem, Asynchronous system 8-bit/7-bit *2)                                                                                                                                                                                                                                          |  |  |  |  |

| LCD driver                                                          |                                                                                                                     |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Time base counter                                                   | er Clock timer: 1 system                                                                                            |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Programmable timer                                                  | Built-in, 1 input $\times$ 8 bits with even                                                                         | nt counter function                                                                                                                                                                                                                                                                 |  |  |  |  |

| Watchdog timer                                                      | Built-in                                                                                                            |                                                                                                                                                                                                                                                                                     |  |  |  |  |

| SVD (supply voltage detection)                                      | 16 values programmable (1.05-2.                                                                                     | 60 V)                                                                                                                                                                                                                                                                               |  |  |  |  |

| External interrupt                                                  | Input port interrupt:                                                                                               | 2 systems                                                                                                                                                                                                                                                                           |  |  |  |  |

| Internal interrupt                                                  | Clock timer interrupt:<br>Programmable timer interrupt:<br>Serial interface interrupt:                              | 1 system<br>1 system<br>3 systems                                                                                                                                                                                                                                                   |  |  |  |  |

| Supply voltage                                                      | 0.9-3.6 V (during operation at 1 I                                                                                  | MHz: 2.2–3.6 V)                                                                                                                                                                                                                                                                     |  |  |  |  |

| Current consumption                                                 | Single clock:<br>During HALT                                                                                        | 1.5 V (normal, LCD power OFF)2 μA1.5 V (normal, LCD power ON)6.5 μA3.0 V (halver ON, LCD power ON)5 μA                                                                                                                                                                              |  |  |  |  |

|                                                                     | During operation at 32 kHz                                                                                          |                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                     | Twin clock:<br>During operation at 200 kHz<br>During operation at 1 MHz                                             | 3.0 V (normal, LCD power ON)40 μA3.0 V (normal, LCD power ON)300 μA                                                                                                                                                                                                                 |  |  |  |  |

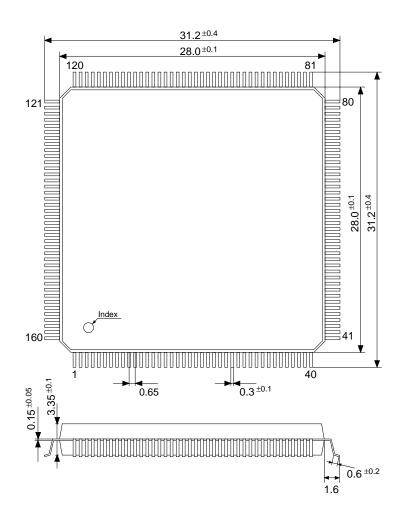

| Package                                                             | QFP8-160pin (plastic) or chip                                                                                       |                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                                                     | *1 May be selected with mask opt                                                                                    | ion.                                                                                                                                                                                                                                                                                |  |  |  |  |

\*2 May be selected with software.

## 1.2 Block Diagram

Fig. 1.2.1 Block diagram

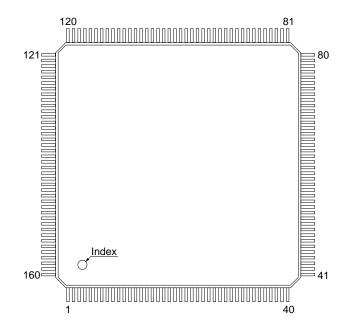

## QFP8-160pin

| Pin No. | Pin name |

|---------|----------|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | SEG52    | 33      | SEG20    | 65      | K03      | 97      | R01      | 129     | VC1      |

| 2       | SEG51    | 34      | SEG19    | 66      | K10      | 98      | R02      | 130     | VC2      |

| 3       | SEG50    | 35      | SEG18    | 67      | K11      | 99      | R03      | 131     | VC3      |

| 4       | SEG49    | 36      | SEG17    | 68      | K12      | 100     | R10      | 132     | VC4      |

| 5       | SEG48    | 37      | SEG16    | 69      | K13      | 101     | R11      | 133     | VC5      |

| 6       | SEG47    | 38      | SEG15    | 70      | P00      | 102     | R12      | 134     | CH       |

| 7       | SEG46    | 39      | SEG14    | 71      | P01      | 103     | R13      | 135     | CG       |

| 8       | SEG45    | 40      | SEG13    | 72      | P02      | 104     | R20      | 136     | CF       |

| 9       | SEG44    | 41      | SEG12    | 73      | P03      | 105     | R21      | 137     | CE       |

| 10      | SEG43    | 42      | SEG11    | 74      | P10      | 106     | R22      | 138     | CD       |

| 11      | SEG42    | 43      | SEG10    | 75      | P11      | 107     | R23      | 139     | CC       |

| 12      | SEG41    | 44      | SEG9     | 76      | P12      | 108     | R30      | 140     | CB       |

| 13      | SEG40    | 45      | SEG8     | 77      | P13      | 109     | R31      | 141     | CA       |

| 14      | SEG39    | 46      | SEG7     | 78      | N.C.     | 110     | R32      | 142     | COM0     |

| 15      | SEG38    | 47      | SEG6     | 79      | N.C.     | 111     | R33      | 143     | COM1     |

| 16      | SEG37    | 48      | SEG5     | 80      | N.C.     | 112     | R40      | 144     | COM2     |

| 17      | SEG36    | 49      | SEG4     | 81      | N.C.     | 113     | R41      | 145     | COM3     |

| 18      | SEG35    | 50      | SEG3     | 82      | N.C.     | 114     | R42      | 146     | COM4     |

| 19      | SEG34    | 51      | SEG2     | 83      | N.C.     | 115     | R43      | 147     | COM5     |

| 20      | SEG33    | 52      | SEG1     | 84      | P20      | 116     | N.C.     | 148     | COM6     |

| 21      | SEG32    | 53      | SEG0     | 85      | P21      | 117     | N.C.     | 149     | COM7     |

| 22      | SEG31    | 54      | COM15    | 86      | P22      | 118     | TEST     | 150     | SEG63    |

| 23      | SEG30    | 55      | COM14    | 87      | P23      | 119     | RESET    | 151     | SEG62    |

| 24      | SEG29    | 56      | COM13    | 88      | P30      | 120     | VREF     | 152     | SEG61    |

| 25      | SEG28    | 57      | COM12    | 89      | P31      | 121     | VDD      | 153     | SEG60    |

| 26      | SEG27    | 58      | COM11    | 90      | P32      | 122     | OSC4     | 154     | SEG59    |

| 27      | SEG26    | 59      | COM10    | 91      | P33      | 123     | OSC3     | 155     | SEG58    |

| 28      | SEG25    | 60      | COM9     | 92      | P40      | 124     | VD1      | 156     | SEG57    |

| 29      | SEG24    | 61      | COM8     | 93      | P41      | 125     | OSC2     | 157     | SEG56    |

| 30      | SEG23    | 62      | K00      | 94      | P42      | 126     | OSC1     | 158     | SEG55    |

| 31      | SEG22    | 63      | K01      | 95      | P43      | 127     | Vss      | 159     | SEG54    |

| 32      | SEG21    | 64      | K02      | 96      | R00      | 128     | VD2      | 160     | SEG53    |

Fig. 1.3.1 Pin layout diagram

## 1.4 Pin Description

| Pin name   | Pin No.        | In/Out | Function                                                                                                |

|------------|----------------|--------|---------------------------------------------------------------------------------------------------------|

| VDD        | 121            | -      | Power (+) supply pin                                                                                    |

| Vss        | 127            | _      | Power (-) supply pin                                                                                    |

| VD1        | 124            | _      | Oscillation/internal logic system regulated voltage output pin                                          |

| VD2        | 128            | _      | Power voltage doubling/halving output pin                                                               |

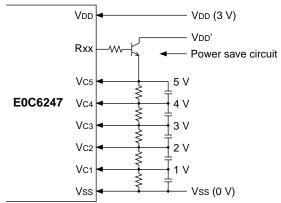

| VC1-VC5    | 129–133        | _      | LCD system power supply pin                                                                             |

|            |                |        | 1/4 bias generated internally, 1/5 bias impressed externally (selected by mask option)                  |

| VREF       | 120            | 0      | LCD system power test pin                                                                               |

| CA–CF      | 141-136        | _      | LCD system boosting/reducing condenser connecting pins                                                  |

| CG, CH     | 135, 134       | _      | Power voltage boosting/reducing condenser connecting pins                                               |

| OSC1       | 126            | Ι      | Crystal osciration input pin                                                                            |

| OSC2       | 125            | 0      | Crystal oscillation output pin                                                                          |

| OSC3       | 123            | Ι      | Ceramic or CR oscillation input pin (selected by mask option)                                           |

| OSC4       | 122            | 0      | Ceramic or CR oscillation output pin (selected by mask option)                                          |

| K00-K03    | 62–65          | Ι      | Input pins                                                                                              |

| K10-K13    | 66–69          | Ι      | Input pins                                                                                              |

| P00-P03    | 70–73          | I/O    | I/O pins (Switching to external data bus D00–D03 is possible by software)                               |

| P10-P13    | 74–77          | I/O    | I/O pins (Switching to external data bus D04–D07 is possible by software)                               |

| P20-P23    | 84-87          | I/O    | I/O pins (Switching to chip select $\overline{CSO}$ – $\overline{CS3}$ outputs is possible by software) |

| P30        | 88             | I/O    | I/O pins (Switching to CL output is possible by software)                                               |

| P31        | 89             | I/O    | I/O pins (Switching to FR output is possible by software)                                               |

| P32        | 90             | I/O    | I/O pins (Switching to PTOVF output is possible by software)                                            |

| P33        | 91             | I/O    | I/O pins (Switching to FOUT output is possible by software)                                             |

| P40-P43    | 92–95          | I/O    | I/O pins (Switching to serial I/F input/output is possible by software)                                 |

| R00-R03    | 96–99          | 0      | Output pins (Switching to external address bus A00-A03 is posible by software)                          |

| R10-R13    | 100-103        | 0      | Output pins (Switching to external address bus A04-A07 is posible by software)                          |

| R20–R23    | 104–107        | 0      | Output pins (Switching to external address bus A08-A12 is posible by software)                          |

| R30–R33    | 108-111        | 0      | Output pins (Switching to external address bus A13-A15 is posible by software)                          |

| R40        | 112            | 0      | Output pin (Switching to A16 or $\overline{WR}$ output is possible by software)                         |

| R41        | 113            | 0      | Output pin (Switching to $\overline{RD}$ output is possible by software)                                |

| R42        | 114            | 0      | Output pin (Switching to $\overline{BZ}$ output is possible by software)                                |

| R43        | 115            | 0      | Output pin (Switching to BZ output is possible by software)                                             |

| COM0-COM15 | 142–149, 61–54 | 0      | LCD common output pins (1/8 or 1/16 duty can be selected by software)                                   |

| SEG0-SEG63 | 53-1, 160-150  | 0      | LCD segment output pins                                                                                 |

| RESET      | 119            | Ι      | Initial reset input pin                                                                                 |

| TEST       | 118            | Ι      | Testing input pin (connect to VDD pin in normal operation)                                              |

Table 1.4.1 Pin description

# CHAPTER 2 POWER SUPPLY AND INITIAL RESET

## 2.1 Power Supply

The E0C6247 operating power voltage is as follows:

0.9 V to 3.6 V

- Note: When the range of 0.9 V to 1.25 V is used as the operating power voltage, software control is necessary (see Section 4.2).

- Power voltage must be within 2.2 V to 3.6 V when the OSC3 oscillation circuit with a 1 MHz clock is used.

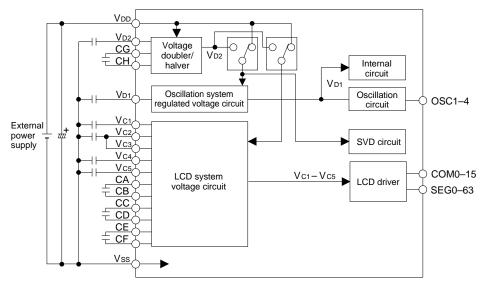

The E0C6247 operates when a single power supply within the above range is applied between VDD and Vss. Even if the voltage is not within the above range necessary for the internal circuits, the IC itself can generate the following built-in power circuits.

| Circuit                                      | Power supply circuit       | Output voltage |

|----------------------------------------------|----------------------------|----------------|

| Oscillation circuit                          | Oscillation system         | VD1            |

| and internal circuits                        | regulated voltage circuit  |                |

| LCD driver                                   | LCD system voltage circuit | VC1–VC5        |

| Oscillation system regulated voltage circuit | Voltage doubler/halver     | VD2            |

| and LCD system voltage circuit               |                            |                |

Table 2.1.1 Power supply circuits

- Note: External loads cannot be driven by the output voltages from the internal power supply circuits.

- Vc3 is used only when the driving voltage of the LCD system will be supplied externally (1/5 bias); when using the internal LCD system voltage circuit (1/4 bias), it is shorted with Vc2.

- See Chapter 7, "ELECTRICAL CHARACTERISTICS", for voltage values and drive capacity.

Fig. 2.1.1 Configuration of power supply

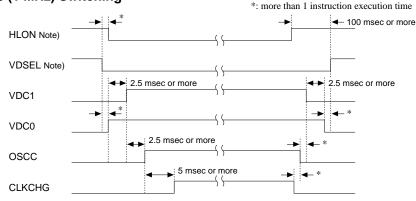

## 2.1.1 Voltage <VD1> for oscillation circuit and internal circuits

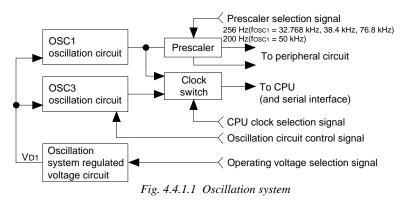

VD1 is a voltage for the oscillation circuit and the internal logic circuits, and is generated by the oscillation system regulated voltage circuit for stabilizing the oscillation.

The E0C6247 is designed with twin clock specification; it has two types of oscillation circuits OSC1 and OSC3 built-in. Use OSC1 clock for normal operation, and switch it to OSC3 by the software when high-speed operation is necessary. When switching the clock, the operating voltage VD1 must be switched by the software to stabilize the operation of the oscillation circuit and internal circuits of the clock to be switched. The oscillation system regulated voltage circuit can output the following three types of VD1 voltage, it should be set at the value according to the oscillation circuit and oscillation frequency by the software.

- 1. Single clock operation (OSC1): VD1 = 1.2 V

- 2. Twin clock operation (OSC3, 200 kHz): VD1 = approx. 1.4 V

- 3. Twin clock operation (OSC3, 1 MHz): VD1 = 2.1 V

See Section 4.4, "Oscillation Circuit", for the VD1 switching procedure.

To generate the voltage above, a larger voltage is needed for the oscillation system regulated voltage circuit. Thus the oscillation system regulated voltage circuit can be driven by the voltage VD2 that is boosted to double the supply voltage (details are explained later). Either the VDD or VD2 can be set by the software to drive the oscillation system regulated voltage circuit.

However, when a 1 MHz clock (item 3 of above) is used, 2.2 V or more supply voltage is necessary and it cannot be operated with the boosted voltage.

## 2.1.2 Voltage <VC1-VC5> for LCD driving

VC1–VC5 are driving voltages for the LCD, and for which either the voltages generated by the LCD system regulated voltage circuit or voltages to be supplied from outside can be used. The built-in LCD system regulated voltage circuit generates four electric potentials (1/4 bias) for VC1, VC2, VC4 and VC5 except for VC3. These four output voltages can be supplied to the outside only for the externally expanded LCD driver.

When external voltages are supplied, 1/5 bias driving can be made by inputting five electric potentials to the VC1–VC5 terminals (including VC3).

Either the internal generated voltages or external voltages used for the LCD drive voltage can be selected by the mask option.

The LCD system voltage circuit generates VC1 or VC2 with the regulated voltage circuit incorporated in itself, and generates three other electric potentials by boosting or reducing the voltage of VC1 or VC2. Table 2.1.2.1 shows the VC1, VC2, VC4 and VC5 voltage values and boost/reduce status.

| LCD drive voltage | VDD = 0.9-3.6 V   | VDD = 2.6-3.6 V     |

|-------------------|-------------------|---------------------|

| Vc1 (0.975–1.2 V) | VC1 (standard)    | $1/2 \times V_{C2}$ |

| Vc2 (1.950–2.4 V) | $2 \times V_{C1}$ | VC2 (standard)      |

| VC4 (2.925-3.6 V) | $3 \times V_{C1}$ | $3/2 \times V_{C2}$ |

| Vc5 (3.900-4.8 V) | $4 \times V_{C1}$ | $2 \times V_{C2}$   |

Table 2.1.2.1 LCD drive voltage when generated internally

## Note: The LCD drive voltage can be adjusted by the software (see Section 4.8.6). Values in the above table are typical values.

Either the VC1 or VC2 used for the standard is selected according to the supply voltage by the software. The VC2 standard improves the display quality and reduces current consumption, however, the supply voltage VDD must be 2.6 V or more. 1.25 V or more voltage is needed even in the VC1 standard, the LCD system voltage circuit can also be driven with the VD2 voltage boosted from the supply voltage, if the supply voltage is less than 1.25 V, same as the oscillation system regulated voltage circuit. This selection can be done separately from the oscillation system regulated voltage circuit.

See Section 4.2, "Setting of Power Supply and Operating Mode", for control of the LCD drive voltage.

## 2.1.3 Voltage doubler/halver and operating mode

The power supply circuit has the voltage doubler/halver built-in to generate the above mentioned voltages for the oscillation circuit/internal circuits and LCD driving even if the supply voltage is less than those setting voltages, or to reduce current consumption when the supply voltage has some redundancy. The voltage doubler/halver doubles or halves the voltage supplied from outside, and generates the VD2 voltage for the internal power supply circuits (oscillation system regulated voltage circuit and LCD system voltage circuit).

There are the following three operation modes depending on the status of the voltage doubler/halver, and switching between them is done by the software. Further the mode setting can be done for the oscillation system regulated circuit and the LCD system voltage circuit, independently.

## (1) Boost mode

The E0C6247 operates with 0.9–3.6 V supply voltage. However, a minimum 1.25 V supply voltage during single clock operation (OSC1) or a minimum 2.2 V during twin clock operation (OSC3, 200 kHz) is needed for the oscillation system regulated voltage circuit. Therefore, when operating with the following supply voltage (VDD), perform a doubling using the voltage doubler/halver and drive the oscillation system regulated voltage circuit with the VD2.

- During single clock operation (OSC1): VDD = 0.9–1.25 V (VD2 = 1.8–2.5 V, with doubling)

- During twin clock operation (OSC3, 200 kHz): VDD = 0.9-2.2 V (VD2 = 1.8-4.4 V, with doubling)

Operating mode at this time is the boost mode.

When the LCD system power circuit is used (the LCD drive voltage is generated internally), a minimum 1.25 V supply voltage is necessary same as above. Therefore, when operating with 0.9–1.25 V supply voltage VDD, perform a doubling using the voltage doubler/halver and drive the oscillation system regulated voltage circuit with VD2. Since this control can independently be done from the oscillation system regulated voltage circuit, when the supply voltage VDD is more than 1.25 V, it is not necessary to operate the LCD system power circuit with the boost mode even if the oscillation system regulated voltage circuit is operated with the boost mode for OSC3 (200 kHz).

When the supply voltage is more than needed for operation, do not set in this mode because boosting voltage increases current consumption.

- Note: 1. Set the boost mode when supply voltage drop is detected by the SVD circuit, such as during heavy load operation (buzzer sounds or a lamp lights) or by the battery life. (\*)

- 2.1 MHz OSC3 oscillation circuit cannot be used in this mode even when 2.2 V or more voltage is generated by boosting. Turning the OSC3 oscillation circuit (1 MHz) ON in this mode may cause malfunction.

#### (2) Normal mode

In this mode, the internal power circuit directly operates by the supply voltage VDD within the range of 1.25–3.6 V (2.2–3.6 V when the OSC3 clock is used) without the voltage doubler/halver. The OSC3 oscillation circuit can be used when supplying a 2.2 V or more supply voltage. At initial reset, this mode is set.

## (3) Reduce mode

The reduce mode can be set when a 2.6–3.6 V supply voltage is used to operate. This mode halves the supply voltage using the halver, and operates the internal power circuit using its output voltage. Therefore, current consumption can be reduced to about half of the normal mode.

Note: The OSC3 oscillation circuit cannot be used in the reduce mode. Turning the OSC3 oscillation circuit ON in this mode may cause malfunction.

| Power circuit    | Operating    | Supply voltage VDD (V) |                |              |                       |  |  |

|------------------|--------------|------------------------|----------------|--------------|-----------------------|--|--|

| Fower circuit    | condition    | 0.9–1.25               | 1.25-2.2       | 2.2–2.6      | 2.6-3.6               |  |  |

| Oscillation      | OSC1         | Boost mode Normal      |                | mode*        | Reduce or normal mode |  |  |

| system regulated | OSC3, 200kHz | Boost                  | mode           | Normal mode* |                       |  |  |

| voltage circuit  | OSC3, 1MHz   | Cannot be used         |                | Normal mode  |                       |  |  |

| LCD system       | VC1 standard | Boost mode Norma       |                | l mode       | Reduce or normal mode |  |  |

| voltage circuit  | VC2 standard | (                      | Cannot be used | 1            | Normal mode           |  |  |

Table 2.1.3.1 Correspondence between supply voltage and operating mode

\* See above Note 1.

See Section 4.2, "Setting of Power Supply and Operating Mode", for setting method of the operating mode.

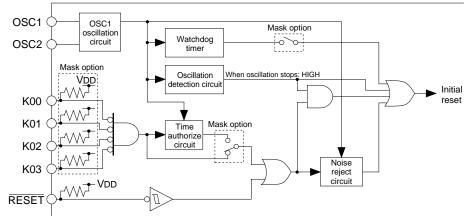

## 2.2 Initial Reset

To initialize the E0C6247 circuits, initial reset must be executed. There are four ways of doing this.

- (1) External initial reset by the RESET terminal

- (2) External initial reset by simultaneous low input to terminals K00-K03 (mask option setting)

- (3) Initial reset by the oscillation detection circuit

- (4) Initial reset by watchdog timer (mask option setting)

Be sure to use reset functions (1) or (2) at power-on and be sure to initialize securely. In normal operation, the circuit may be initialized by any of the above four types.

Figure 2.2.1 shows the configuration of the initial reset circuit.

Fig. 2.2.1 Configuration of initial reset circuit

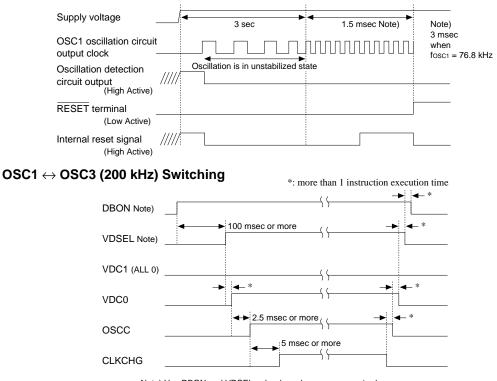

## 2.2.1 Reset terminal (RESET)

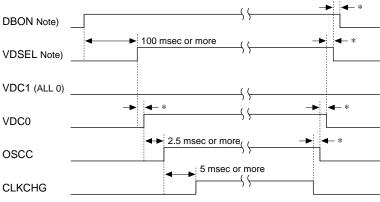

The initial resetting can be done by externally setting the reset terminal to a low level. However, be sure to observe the following precautions, because the  $\overline{\text{RESET}}$  signal passes through the noise reject circuit. When the reset terminal is used for initial resetting during operation, a pulse (low level) of 0.3 msec (0.2 msec when the oscillation frequency fosc1 = 76.8 kHz) or less is considered to be noise by the noise reject circuit. Maintain a low level of 1.5 msec (3 msec when fosc1 = 76.8 kHz) to securely perform the initial reset. When the reset terminal goes high, the CPU begins to operate.

Since the noise reject circuit does not operate when oscillation is stopped, the noise reject circuit is bypassed until it starts oscillation. For this reason, be sure to maintain a low level the reset input in the oscillation stopped status at power-on, until starting oscillation.

## 2.2.2 Simultaneous low input to terminals K00-K03

Another way of executing initial reset externally is to input a low signal simultaneously to the input ports (K00–K03) selected with the mask option.

Since this initial reset also passes through the same noise reject circuit as the reset terminal, you should maintain the specified input port terminal at low level for 1.5 msec (3 msec when fOSC1 = 76.8 kHz) or more during operation and until it begins oscillation at times such as when making power.

Table 2.2.2.1 shows the combinations of input ports (K00–K03) that can be selected with the mask option.

Table 2.2.2.1 Combinations of input ports

|   | J J J J         |

|---|-----------------|

| 1 | Not use         |

| 2 | K00*K01*K02*K03 |

| 3 | K00*K01*K02     |

| 4 | K00*K01         |

When, for instance, mask option 2 (K00\*K01\*K02\*K03) is selected, initial reset is executed when the signals input to the four ports K00–K03 are all low at the same time. The initial reset is done, even when a key entry including a combination of selected input ports is made.

Further, the time authorize circuit can be selected with the mask option. The time authorize circuit performs initial reset, when the input time of the simultaneous low input is authorized and found to be the same or more than the defined time (1 to 2 sec).

If you use this function, make sure that the specified ports do not go low at the same time during ordinary operation.

## 2.2.3 Oscillation detection circuit

The oscillation detection circuit outputs the initial reset signal at power-on until the OSC1 oscillation circuit begins oscillating, or when the OSC1 oscillation circuit halts oscillating for some reason. In addition, it uses a simultaneous low input of the input ports (K00–K03) or reset terminal for the initial reset at power-on and you should not execute it by this function alone.

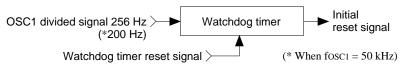

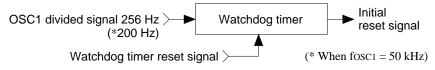

## 2.2.4 Watchdog timer

If the CPU runs away for some reason, the watchdog timer will detect this situation and output an initial reset signal. See Section 4.3, "Resetting Watchdog Timer" for details.

As with the oscillation detection circuit, you should not do an initial reset at power-on using this function.

## 2.2.5 Internal register at initial resetting

Initial reset initializes the CPU as shown in the table below.

Other peripheral circuits

| CPU core                   |            |                |               |  |  |  |  |  |

|----------------------------|------------|----------------|---------------|--|--|--|--|--|

| Name                       | Symbol     | Number of bits | Setting value |  |  |  |  |  |

| Program counter step       | PCS        | 8              | 00H           |  |  |  |  |  |

| Program counter page       | PCP        | 4              | 1H            |  |  |  |  |  |

| Program counter bank       | PCB        | 1              | 0             |  |  |  |  |  |

| New page pointer           | NPP        | 4              | 1H            |  |  |  |  |  |

| New bank pointer           | NBP        | 1              | 0             |  |  |  |  |  |

| Stack pointer              | SP         | 8              | Undefined     |  |  |  |  |  |

| Index register IX          | IX         | 12             | Undefined     |  |  |  |  |  |

| Index register IY          | IY         | 12             | Undefined     |  |  |  |  |  |

| Register pointer           | RP         | 4              | Undefined     |  |  |  |  |  |

| General-purpose register A | А          | 4              | Undefined     |  |  |  |  |  |

| General-purpose register B | В          | 4              | Undefined     |  |  |  |  |  |

| Interrupt flag             | Ι          | 1              | 0             |  |  |  |  |  |

| Decimal flag               | D          | 1              | 0             |  |  |  |  |  |

| Zero flag                  | Z          | 1              | Undefined     |  |  |  |  |  |

| Carry flag                 | С          | 1              | Undefined     |  |  |  |  |  |

|                            |            |                |               |  |  |  |  |  |

|                            | Peripheral |                |               |  |  |  |  |  |

| Name                       |            | Number of bits | Setting value |  |  |  |  |  |

| RAM                        |            | 4              | Undefined     |  |  |  |  |  |

| Display memory             |            | 4              | Undefined     |  |  |  |  |  |

|                            |            |                |               |  |  |  |  |  |

Table 2.2.5.1 Initial values

\* See Section 4.1, "Memory Map".

## 2.2.6 Terminal settings at initial resetting

The output port (R) terminals and I/O port (P) terminals are combined with the bus terminals for external memory accessing or the special output terminals, and these functions are selected by the software. At initial reset, these terminals are set to the general purpose output port terminals and I/O port terminals. Settings according to the system should be set with the initial routine in the application. In addition, take care of the initial status of output terminals when designing a system. Table 2.2.6.1 shows the list of the combined terminal settings.

| Terminal | Terminal status         | Wher                                              | n external                        | memory is                                         | used                                              | When special output is used |    |    |    |       |      | When serial I/F is used     |         |         |

|----------|-------------------------|---------------------------------------------------|-----------------------------------|---------------------------------------------------|---------------------------------------------------|-----------------------------|----|----|----|-------|------|-----------------------------|---------|---------|

| name     | at initial reset        | 1M-bit                                            | 512K-bit                          | 256K-bit                                          | 64K-bit                                           | ΒZ                          | ΒZ | CL | FR | PTOVF | FOUT | Master                      | Slave   | Async.  |

| R00-R03  | R00-R03(High output)    | A00-A03                                           | A00-A03                           | A00-A03                                           | A00-A03                                           |                             |    |    |    |       |      |                             |         |         |

| R10-R13  | R10-R13(High output)    | A04-A07                                           | A04-A07                           | A04-A07                                           | A04-A07                                           |                             |    |    |    |       |      |                             |         |         |

| R20-R23  | R20-R23(High output)    | A08-A11                                           | A08-A11                           | A08-A11                                           | A08-A11                                           |                             |    |    |    |       |      |                             |         |         |

| R30      | R30(High output)        | A12                                               | A12                               | A12                                               | A12                                               |                             |    |    |    |       |      |                             |         |         |

| R31      | R31(High output)        | A13                                               | A13                               | A13                                               | R31                                               |                             |    |    |    |       |      |                             |         |         |

| R32      | R32(High output)        | A14                                               | A14                               | A14                                               | R32                                               |                             |    |    |    |       |      |                             |         |         |

| R33      | R33(High output)        | A15                                               | A15                               | R33                                               | R33                                               |                             |    |    |    |       |      |                             |         |         |

| R40      | R40(High output)        | A16                                               | WR                                | WR                                                | WR                                                |                             |    |    |    |       |      |                             |         |         |

| R41      | R41(High output)        | RD                                                | RD                                | RD                                                | RD                                                |                             |    |    |    |       |      |                             |         |         |

| R42      | R42(Low output)         |                                                   |                                   |                                                   |                                                   | $\overline{\text{BZ}}$      |    |    |    |       |      |                             |         |         |

| R43      | R43(Low output)         |                                                   |                                   |                                                   |                                                   |                             | ΒZ |    |    |       |      |                             |         |         |

| P00-P03  | P00-P03(Input & PullUp) | D00-D03                                           | D00-D03                           | D00-D03                                           | D00-D03                                           |                             |    |    |    |       |      |                             |         |         |

| P10-P13  | P10-P13(Input & PullUp) | D04-D07                                           | D04-D07                           | D04-D07                                           | D04-D07                                           |                             |    |    |    |       |      |                             |         |         |

| P20-P23  | P20-P23(Input & PullUp) | $\overline{\text{CS0}}$ – $\overline{\text{CS3}}$ | $\overline{CS0} - \overline{CS3}$ | $\overline{\text{CS0}}$ – $\overline{\text{CS3}}$ | $\overline{\text{CS0}}$ – $\overline{\text{CS3}}$ |                             |    |    |    |       |      |                             |         |         |

| P30      | P30(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    | CL |    |       |      |                             |         |         |

| P31      | P31(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    | FR |       |      |                             |         |         |

| P32      | P32(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    | PTOVF |      |                             |         |         |

| P33      | P33(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    |       | FOUT |                             |         |         |

| P40      | P40(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    |       |      | SIN(I)                      | SIN(I)  | SIN(I)  |

| P41      | P41(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    |       |      | SOUT(O)                     | SOUT(O) | SOUT(O) |

| P42      | P42(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    |       |      | $\overline{\text{SCLK}}(O)$ | SCLK(I) | P42     |

| P43      | P43(Input & PullUp)     |                                                   |                                   |                                                   |                                                   |                             |    |    |    |       |      | P43                         | SRDY(O) | P43     |

Table 2.2.6.1 List of combined terminal settings

Master: Clock synchronous master mode Slave: Clock synchronous slave mode Async.: Asynchronous mode

For setting procedure of the functions, see explanations for each of the peripheral circuits.

## 2.3 Test Terminal (TEST)

This is the terminal that is used at the time of the factory inspection of the IC. During normal operation, connect the  $\overline{\text{TEST}}$  to VDD.

# CHAPTER 3 CPU, ROM, RAM

## 3.1 CPU

The E0C6247 employs the 4-bit core CPU E0C6200A for the CPU, so that register configuration, instructions and so forth are virtually identical to those in other family processors using the E0C6200A. Refer to "E0C6200/6200A Core CPU Manual" for details about the E0C6200A. However, The SLEEP operation is not assumed in the E0C6247, so the SLP instruction cannot be used.

## 3.2 ROM

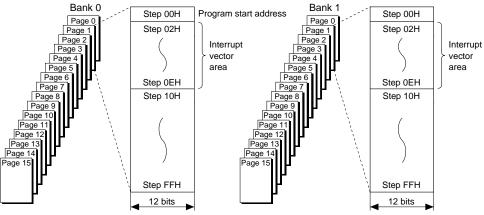

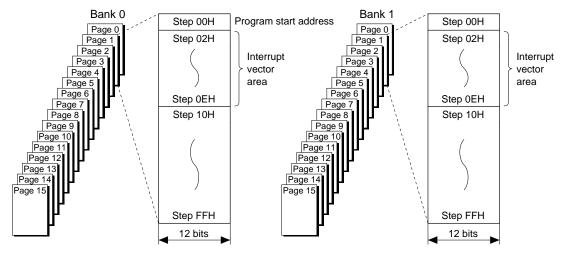

The built-in ROM, a mask ROM for loading the program, has a capacity of 8,192 steps  $\times$  12 bits. The program area is two banks, each of 16 (0–15) pages  $\times$  256 (00H–FFH) steps. After initial reset, the program beginning address is set to bank 0, page 1, step 00H. The interrupt vector is allocated to page 1 of each bank, steps 02H–0EH.

Fig. 3.2.1 ROM configuration

## 3.3 RAM

The RAM, a data memory storing a variety of data, has a capacity of 1,792 words  $\times 4$  bits. When programming, keep the following points in mind.

- (1) Part of the data memory can be used as stack area when subroutine calls and saving registers, so be careful not to overlap the data area and stack area.

- (2) Subroutine calls and interrupts take up three words of the stack area.

- (3) The data memory 000H–00FH is for the register pointers (RP), and is the addressable memory register area.

## 3.4 External Memory

When external memory access function is selected by the software, maximum four 64K-byte (512K-bit) RAM or maximum four 128K-byte (1M-bit) ROM may be expanded externally. See Section 4.13, "External Memory Access", for details of external memory.

# CHAPTER 4 PERIPHERAL CIRCUITS AND OPERATION

Peripheral circuits (timer, I/O, and so on) of the E0C6247 are memory mapped, and interfaced with the CPU. Thus, all the peripheral circuits can be controlled by using the memory operation command to access the I/O memory in the memory map.

The following sections describe how the peripheral circuits operation.

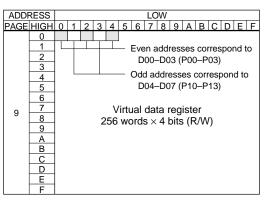

## 4.1 Memory Map

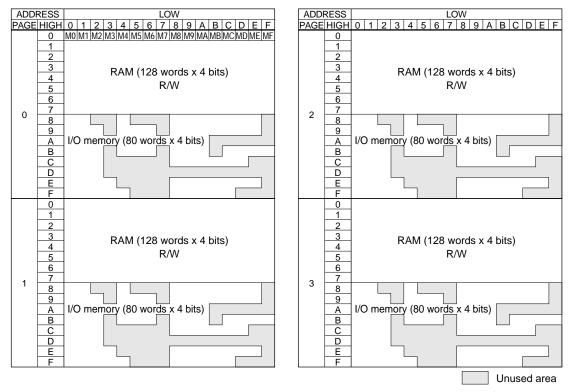

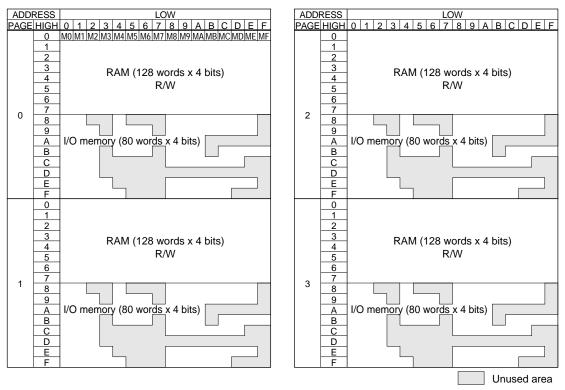

Data memory of the E0C6247 is composed of 1,792-word RAM, 256-word display memory, 80-word I/O memory and 256-word external memory access area

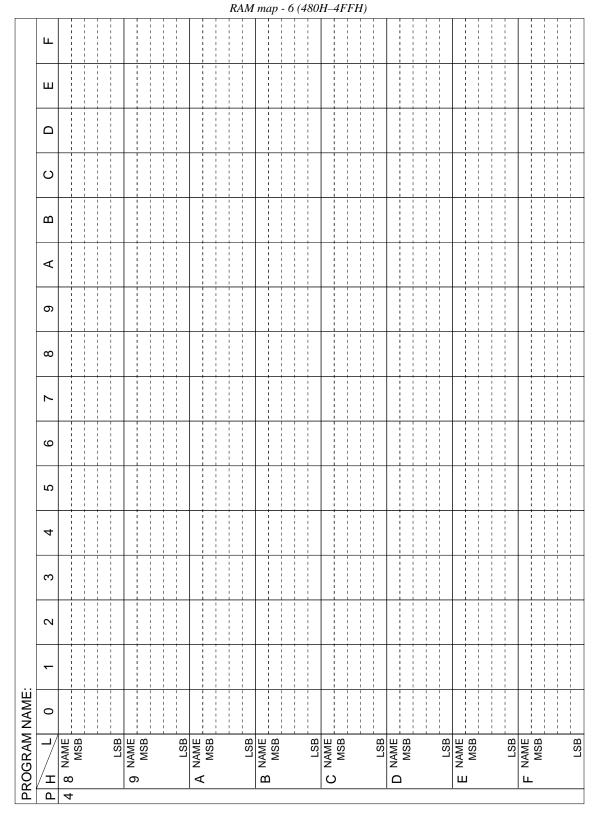

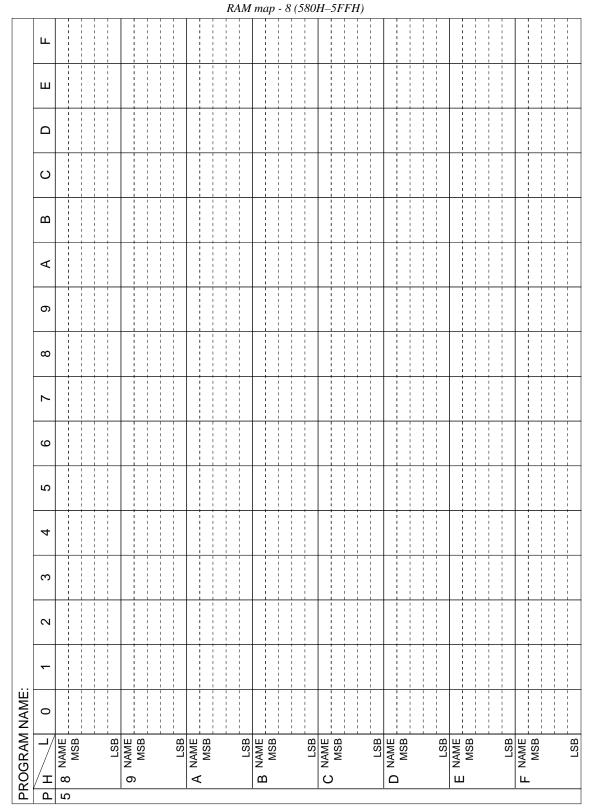

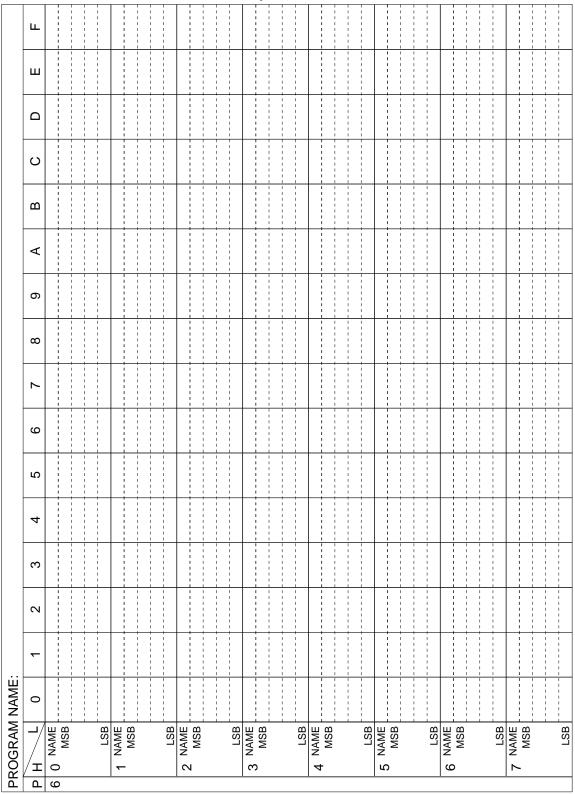

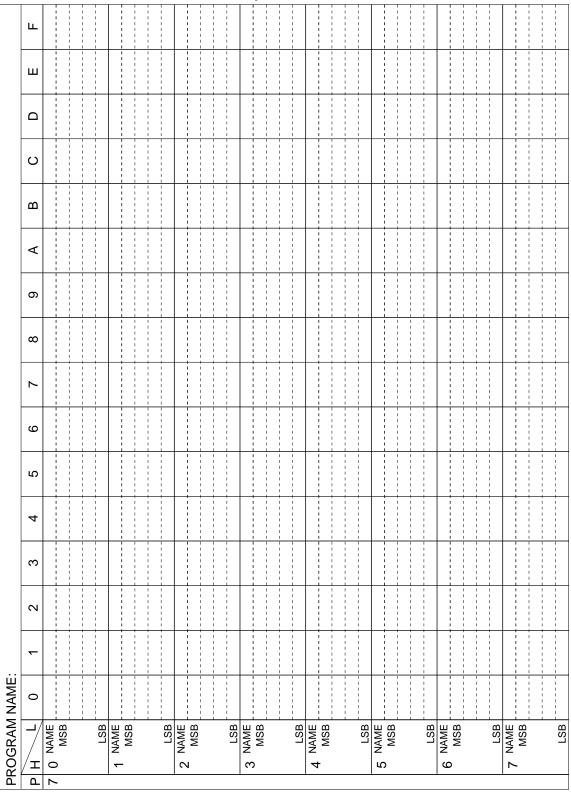

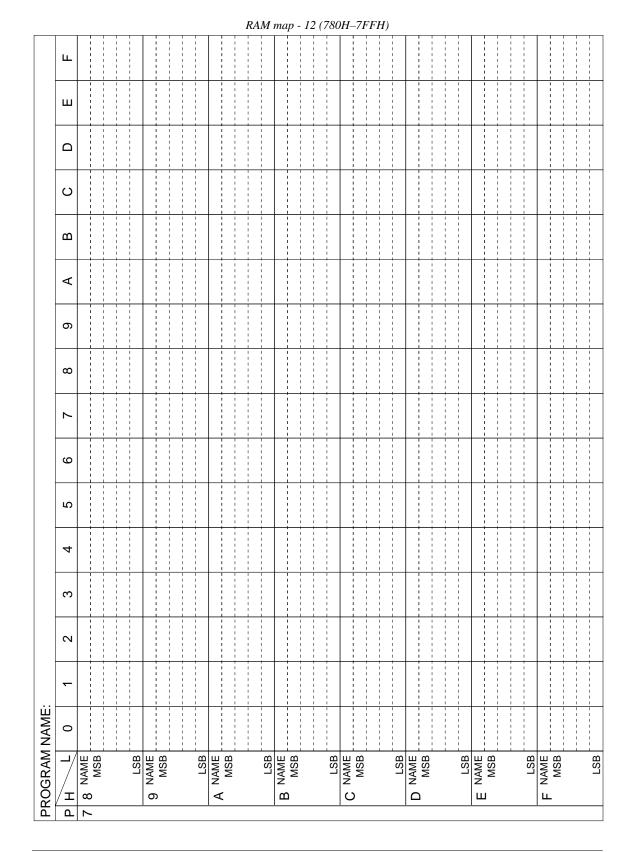

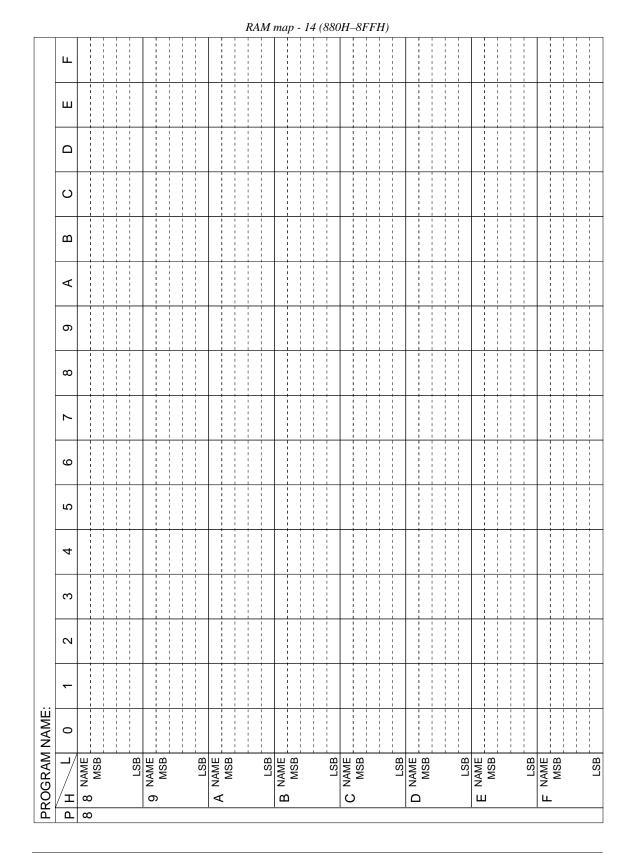

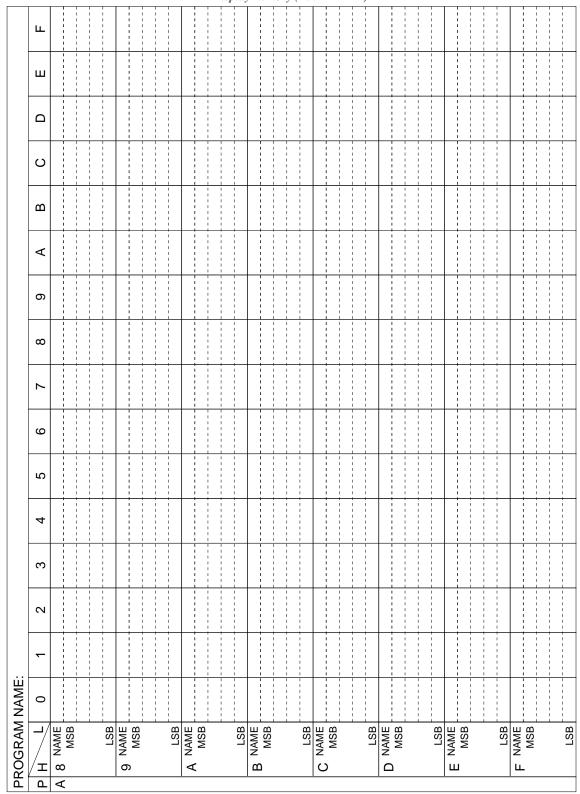

Figures 4.1.1(a) and (b) present the overall memory maps of the E0C6247, and Tables 4.1.1(a)–(h) the peripheral circuits' (I/O space) memory maps.

In the E0C6247 the same I/O memory has been laid out for 80H–FCH from page 0 to 3. As a result, the I/O memory can be accessed without changing over the data memory page if it is in page 0 to 3. The same result is obtained for I/O memory changes and for readable/writable address references, no matter on what page within 0 to 3 it is done.

Fig. 4.1.1(a) Memory map

Note: Memory is not mounted in unused area within the memory map and in memory area not indicated in this chapter. For this reason, normal operation cannot be assured for programs that have been prepared with access to these areas.

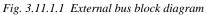

| ADD  | RESS                                                                                        | LOW                             | ADDRESS                                                                                                              |

|------|---------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------|

| PAGE | HIGH                                                                                        | 0 1 2 3 4 5 6 7 8 9 A B C D E F | PAGE HIGH 0 1 2 3 4 5 6 7 8 9 A B C D E F                                                                            |

| 4    | 0<br>1<br>2<br>3<br>4<br>5<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F           | RAM (256 words x 4 bits)<br>R/W | 8<br>0<br>1<br>3<br>4<br>5<br>6<br>7<br>RAM (256 words x 4 bits)<br>8<br>8<br>7<br>R/W<br>A<br>B<br>C<br>D<br>E<br>F |

| 5    | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F                | RAM (256 words x 4 bits)<br>R/W | 9<br>8<br>9<br>7<br>9<br>8<br>7<br>(256 words x 4 bits)<br>9<br>A<br>B<br>C<br>D<br>E<br>F                           |

| 6    | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F | RAM (256 words x 4 bits)<br>R/W | A                                                                                                                    |

| 7    | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>A<br>B<br>C<br>D<br>E<br>F                | RAM (256 words x 4 bits)<br>R/W |                                                                                                                      |

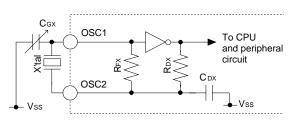

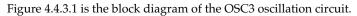

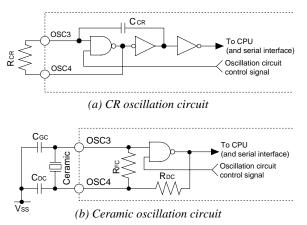

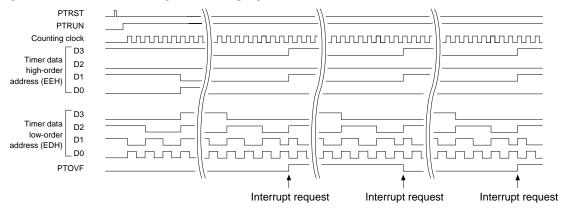

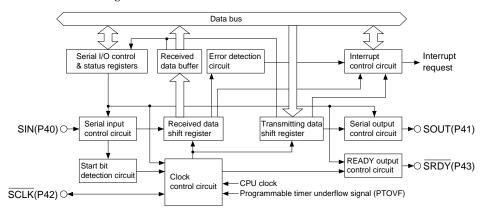

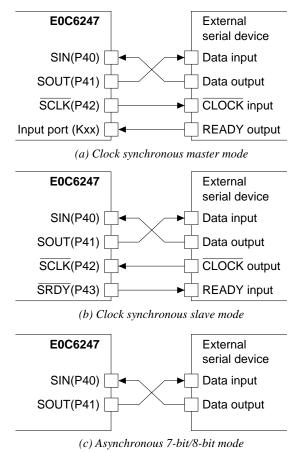

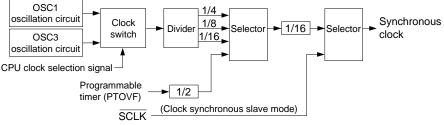

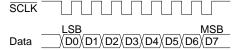

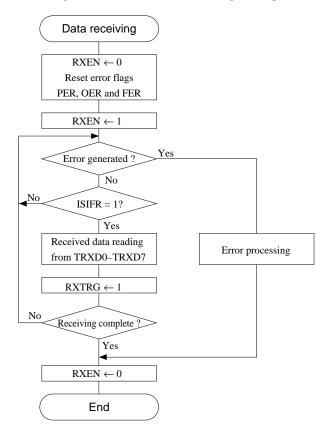

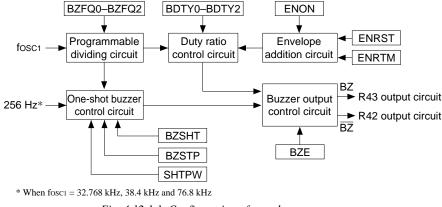

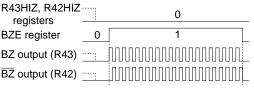

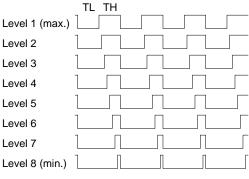

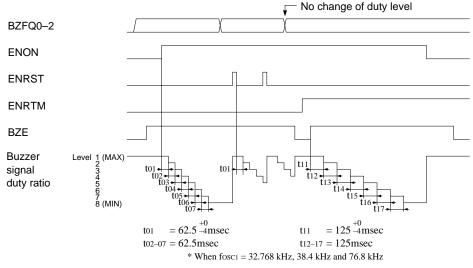

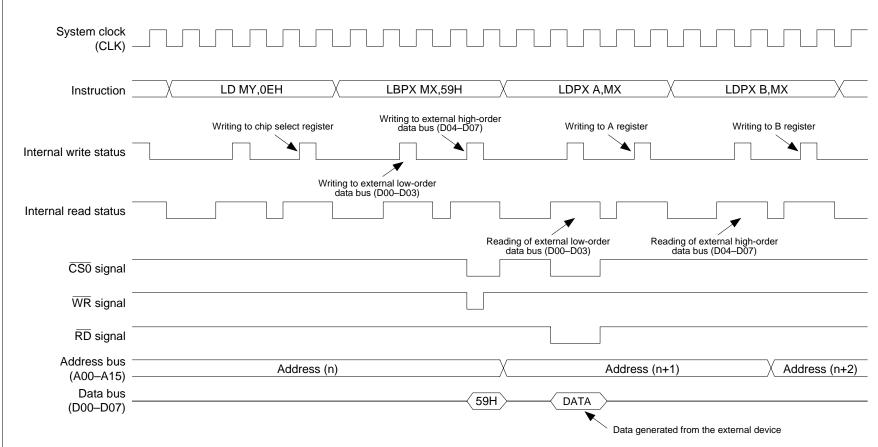

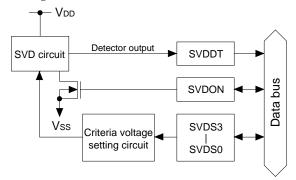

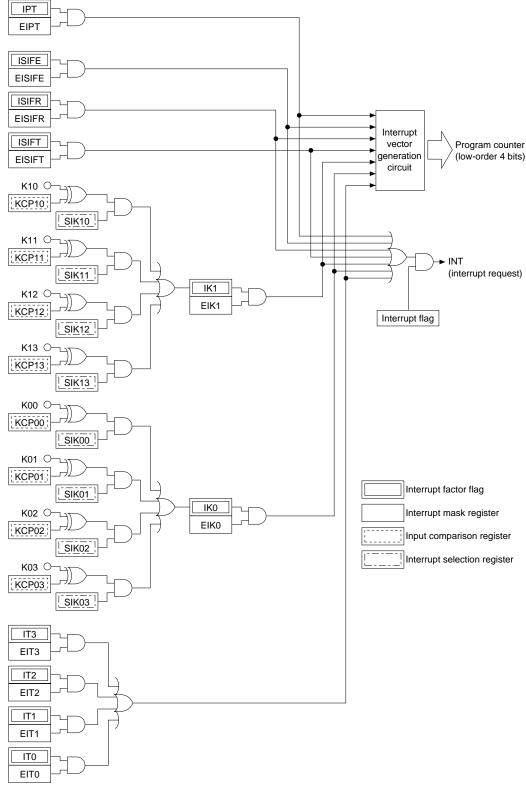

Fig. 4.1.1(b) Memory map