# **EPSON**

SEIKO EPSON CORPORATION

MLS Chipset Chipset Chipset

"Seiko Epson is neither licensed nor authorized to license its customers under one or more patents held by Motif Corporation to use this integrated circuit in the manufacture of liquid crystal display modules. Such license, however, may be obtained directly from MOTIF by writing to: Motif, Inc., c/o In Focus Systems, Inc., 27700A SW Parkway Avenue, Wilsonville, OR 97070-9215, Attention: Vice President Corporate Development."

# NOTICE

No parts of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind aristing out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export licence from teh Ministry of International Trade and Industry or other approval from another government agency.

# CONTENTS

| SED1360  | Seri | es | <br> | • • | <br> | • |     | <br> | • | <br> | • | <br>• • | • | • | • • | 1-1 |

|----------|------|----|------|-----|------|---|-----|------|---|------|---|---------|---|---|-----|-----|

| SED1580  |      |    | <br> |     | <br> |   | • • | <br> |   | <br> |   | <br>    | • |   |     | 2-1 |

| SED1590  |      |    | <br> |     | <br> |   | • • | <br> |   | <br> |   | <br>    | • |   |     | 3-1 |

| SED1750  |      |    | <br> |     | <br> |   |     | <br> |   | <br> |   | <br>    |   |   |     | 4-1 |

| SED1751  |      |    | <br> |     | <br> |   | • • | <br> |   | <br> |   | <br>    | • |   |     | 5-1 |

| SCI7500F | 0A . |    | <br> |     | <br> |   |     | <br> |   | <br> |   | <br>    |   |   |     | 6-1 |

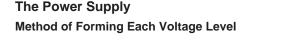

# FEATURE

This chip set works to support the MLS (Multi Line Selection) drive method capable of making high-speed responses consisting of multiple numbers of SED1580, SED1590, SED1751, SED1360 and SCI7500 ICs. Since the indication data are stored in the indication RAM built into the X-driver to issue LCD drive signals, transference of indication data from the controller will be interrupted except for the period when the indications are being revised. Also, the complicated processings necessary for MLS drive are completed between the X-driver and the Y-driver so users need not be concerned about them. Consequently, the existing interface is usable.

Moreover, we are preparing exclusive power ICs to help configure the display systems for handy, high performance equipment.

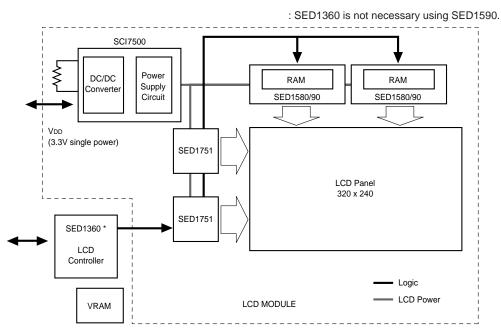

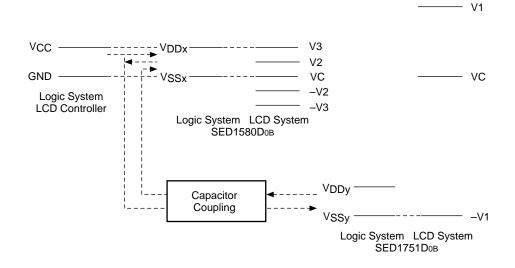

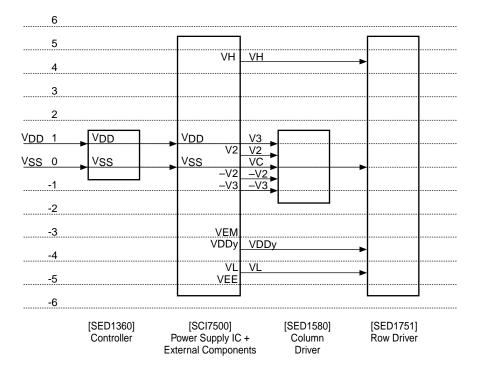

# **CHIP SET CONFIGURATION**

- SED1360F0A LCD controller (applicable to drivers with display RAM)

- SED1580T0A/D0B 160-output, 4-line distributed MLS drive method LCD segment driver

- SED1590T0A/D0B 160-output, 4-line distributed MLS drive method LCD segment driver + controller

- SED1751T0A/D0B 120/100-output, 4-line distributed MLS drive method LCD common driver

- SCI7500F0A 4-line MLS driver with exclusive power supply

# FEATURES OF CHIP SETS

- Ultra-low power consumption with newly power circuits.

- About 5mW with  $320 \times 240$  dots FTN reflection monochrome display.

- Single power supply : 3.3V, on chip DC/DC converter.

- Two types of interface.

- High contrast, High quality with no flicker.

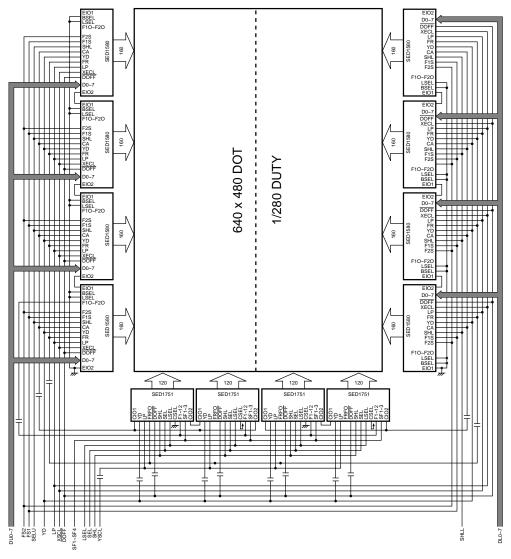

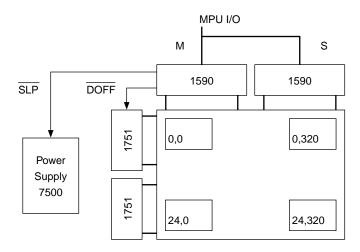

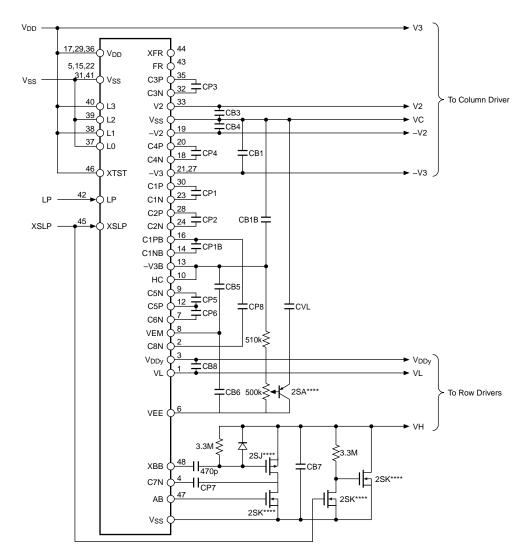

# **BLOCK DIAGRAM**

# SED1360F0A LCD CONTROLLER (applicable to drivers with built-in indication RAM)

| Power supply | : Logic channel 2.7 – 5.5V |

|--------------|----------------------------|

| Package      | : GFP6-60 pin              |

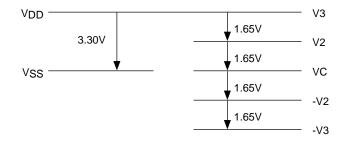

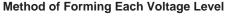

#### SED1580T0A/D0B MLS drive method LCD segment driver

| Number of LCD outputs   | : 160 outputs              |

|-------------------------|----------------------------|

| Driving duty            | : 1/240 duty               |

| Built-in indication RAM | : $160 \times 240$ bits    |

| Power supply            | : Logic channel 3.0 – 3.6V |

|                         | LCD channel $6.0 - 7.2V$   |

| Package                 | : TCP or Au bump chip      |

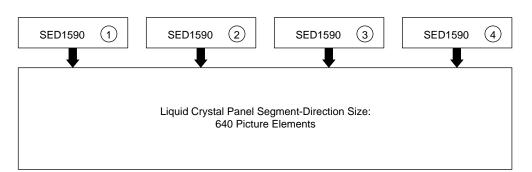

#### SED1590T0A/D0B MLS drive method LCD segment driver + controller

| Number of LCD outputs   | : 160 outputs                                                  |

|-------------------------|----------------------------------------------------------------|

| Driving duty            | : 1/240 duty                                                   |

| Built-in indication RAM | : $160 \times 240$ bits                                        |

| Power supply            | : Logic channel 2.7 – 3.6V                                     |

|                         | LCD channel $5.4 - 7.2V$                                       |

| Package                 | : TCP (under development) or Au bump chip                      |

| Others                  | : Built-in LCD controller function (with 31 types of commands) |

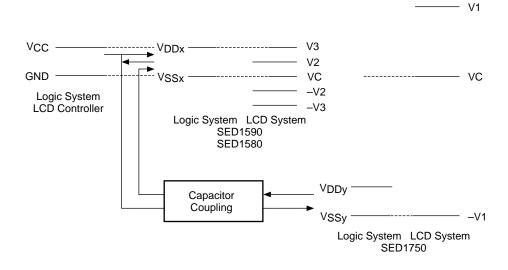

# SED1751T0A/D0B MLS DRIVE METHOD LCD COMMON DRIVER

| Number of LCD outputs   | : 120 outputs/100-output changeover |

|-------------------------|-------------------------------------|

| Driving duty            | : 1/480 duty                        |

| Built-in indication RAM | : $160 \times 240$ bits             |

| Power supply            | : Logic channel 2.7 – 5.5V          |

|                         | LCD channel $14 - 42V$              |

| Package                 | : TCP or Au bump chip               |

# SCI7500F0A 4-line MLS driver with exclusive power supply

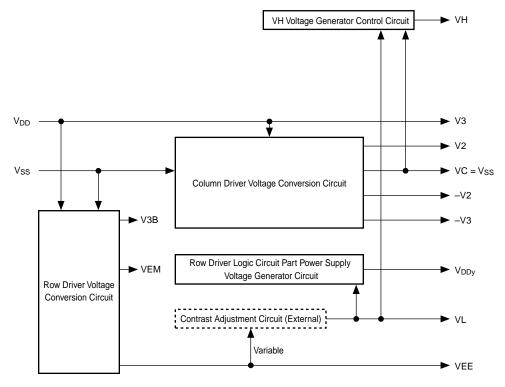

Incorporating a built-in DC/DC converter with a voltage conversion circuit and a bias circuit necessary for quintuple (1/200 duty) and sextuple boosted (1/240 duty) 4-line MLS driving.

| Power supply | : $2.4 - 3.6V$ single power input |

|--------------|-----------------------------------|

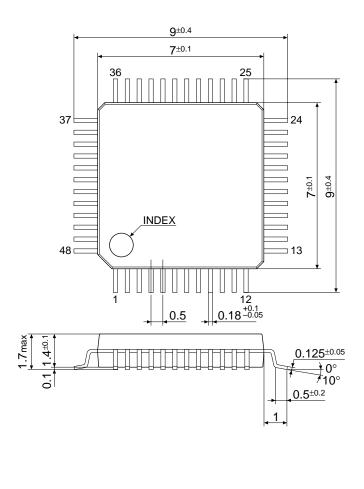

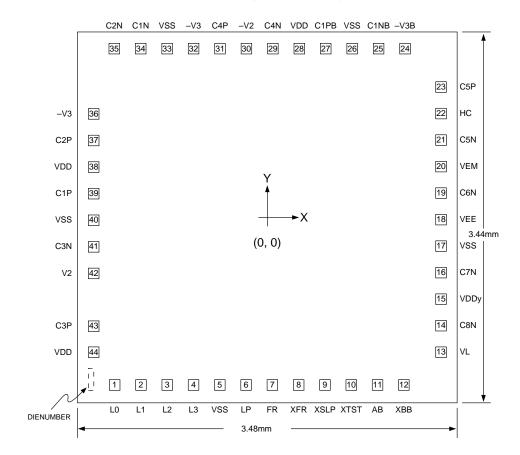

| Package      | : GFP12-48 pin                    |

# **SED1360 Series**

# Contents

| INTRODUCTION            | 1-1  |

|-------------------------|------|

| FEATURES                | 1-1  |

| OVERVIEW DESCRIPTION    | 1-2  |

| PINOUT DIAGRAM          | 1-5  |

| PIN DESCRIPTION         | 1-8  |

| D.C. CHARACTERISTICS    | 1-11 |

| A.C. CHARACTERISTICS    | 1-14 |

| OPERATION DESCRIPTION   | 1-19 |

| OSCILLATION DESCRIPTION | 1-25 |

| COMMAND DESCRIPTION     |      |

| ERRORTA                 | 1-29 |

| NOTICE                  | 1-29 |

# INTRODUCTION

#### Scope

This is the Functional Specification for SED1360 3.3 V Ultra Low Power LCD Controller Chip.

#### Objectives

- (1) To specify functions and interface requirements of the chip.

- (2) To allow review of the functions of the chip, as a preliminary specification.

# FEATURES

## Technology

- ultra low power CMOS process

- 3.3 volt operation

- chip supply with aluminum pad

- 64 pin QFP6 surface mount package

#### System

- Direct connection to the 68 family CPUs.

- minimum CPU Interface pin count.

- no buffers are required in a 3.3 V-System.

- internal oscillator with external Capacitance and Resistance, or external oscillator for a low frequency input source.

- interfaces to 64 kb and, or 256 kb SRAMs.

- controls Seiko Epson's RAM integrated Segment Drivers.

- self-controlled Doze Mode.

- optimized Hardware for low to medium resolution LCDs.

- ultra low power consumption.

# **OVERVIEW DESCRIPTION**

SED1360 is an ultra low power 3.3 V LCD controller which is optimized to drive low to medium resolution LCD panels. SED1360 can interface to the 68 family CPUs in the Port Peripheral Timing.

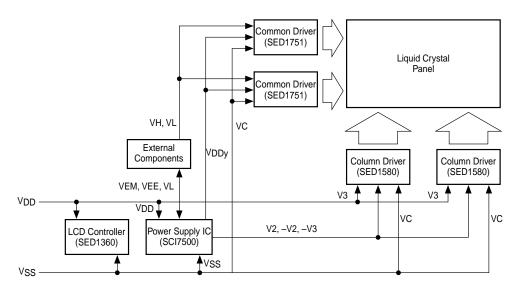

# **Typical System Block Diagram**

The following figure shows typical system implementation with SED1360.

Display Subsystem

Figure 1. Typical System Block Diagram

#### SED1360

- (1) 3.3 V operational low power LCD Controller Chip.

- (2) receives Data from CPU.

- (3) stores the Display Data into SRAM.

- (4) reads the Data written in the SRAM to update LCD Display.

- (5) transfers the read Data to LCD Module automatically.

- (6) controls entering to Doze Mode and returning to Active Mode automatically.

- (7) supports local oscillation or low frequency input to realize the Ultra Low Power LCD Display Subsystem.

- (8) supports Hardware Suspend Mode.

#### LCD Module

- (1) 3.3 V operational low power LCD Module.

- (2) consists of Seiko Epson's RAM integrated Segment Drivers, Common Drivers and an LCD panel.

- (3) The LCD Module enters into Power Save Mode automatically, if "XSCLU" is not provided.

#### SRAM

- (1) SED1360 uses the SRAM to store the Display Data written by CPU in order to arbitrate between CPU access and LCD Display refresh.

- (2) has to be 3.3 V operational.

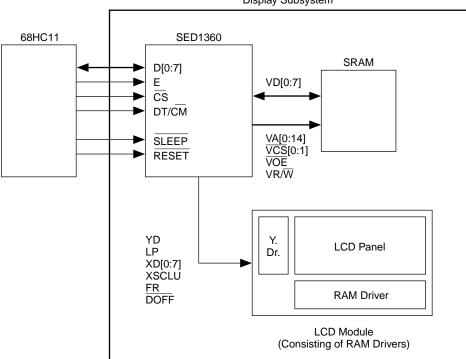

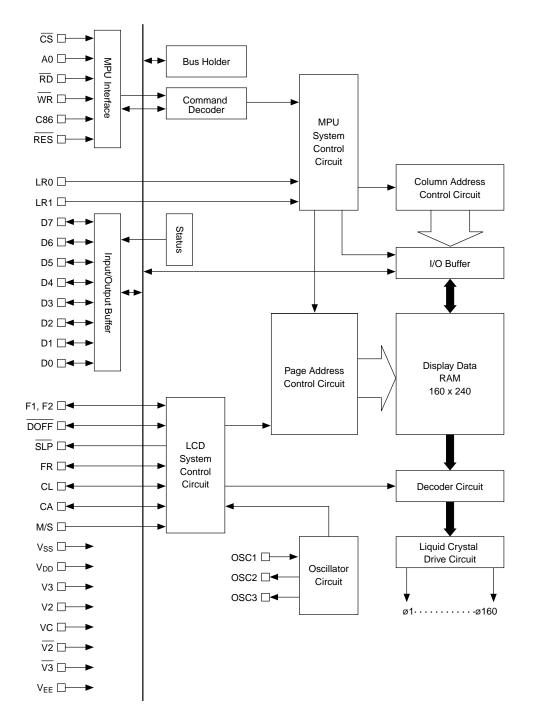

#### SED1360 Internal Block Diagram

The following figure shows an overview of the LCD Controller chip SED1360.

Figure 2. SED1360 Internal Block Diagram

#### **CPU Interface**

- (1) 3.3 V 68XX dedicated CPU Interface.

- (2) 8 bit Data are used to transfer Data or Commands.

- (3) The rising edge of " $\overline{CS}$ " signal is used to execute the Data Transfer.

- (4) "DT/ $\overline{CM}$ " is used for CPU to indicate either Data or Command is on the bus.

- (5) "SLEEP" signal is used to set the chip in Sleep Mode.

- (6) No other signals are required for the normal operation.

- (7) "RESET" is used to initialize the chip.

#### Address Generator for CPU Access

- (1) The internal CPU Write Start Address can be set by the command.

- (2) After every single CPU Display Data Write Access, the internal CPU Write Address Counter is increased by one.

#### Address Generator for Display Refresh

- (1) "E" is used to generate the Display Refresh Address.

- (2) Address Generator begins when the immediate Frame comes after the CPU Display Data Write Access occurs or when CPU sets the "Display Data Transfer" command.

- (3) Address Generation stops if no CPU Display Data Write Access occurs for two LCD Frame period.

#### **Address Selector**

When CPU Display Data Write Access occurs, the internal CPU Write Address is selected to generate the address for SRAM.

#### **Memory Controller**

- (1) When CPU Display Data Write Access occurs, Memory Controller stores the data into SRAM.

- (2) The Memory Controller begins reading the data stored in the SRAM to transfer to the LCD Module when the immediate Frame comes after the CPU Display Data Write Access occurs or when CPU sets the "Display Data Transfer" command.

- (3) The Memory Controller stops reading the data from the SRAM if no CPU Display Data Write Access occurs for two LCD Frame period.

#### LCD Timing Generator

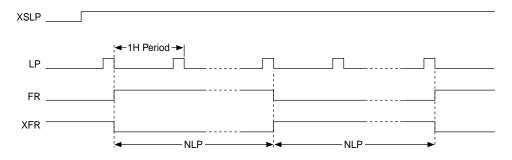

- Local oscillation is directly used to generate "LP" (Horizontal Sync. Pulse), "YD" (Vertical Sync. Pulse) and "FR" (LCD voltage alternation signal).

- (2) The updated data stored in the SRAM is transferred through the Memory Controller and the LCD Timing Generator to the LCD Module, if the CPU Display Data Write Access occurs or when CPU sets the "Display Data Transfer" command.

- (3) The LCD Timing Generator uses "E" to generate "XSCLU".

- (4) "XSCLU" is automatically controlled by the CPU Display Data Write Access or setting the "Display Data Transfer" command.

#### **Power Management Unit**

(1) Power Management Unit monitors the occurrence of CPU Display Data Write Access, the execution of the "Display Data Transfer" command, the internal state of LCD Frame period and the "SLEEP" signal in order to determine entering to Doze Mode and returning to Active Mode. And this unit also controls local oscillation.

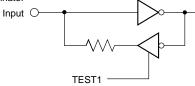

#### Test Unit

Test Unit controls test functions of the chip if the chip is in Test Mode.

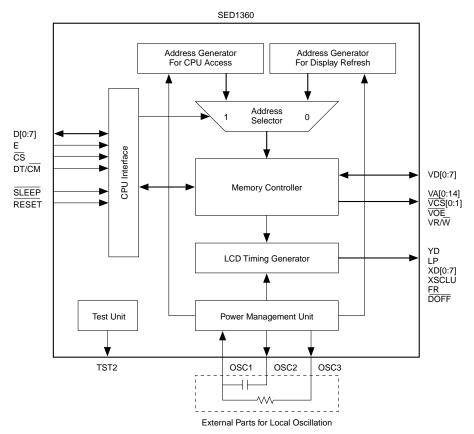

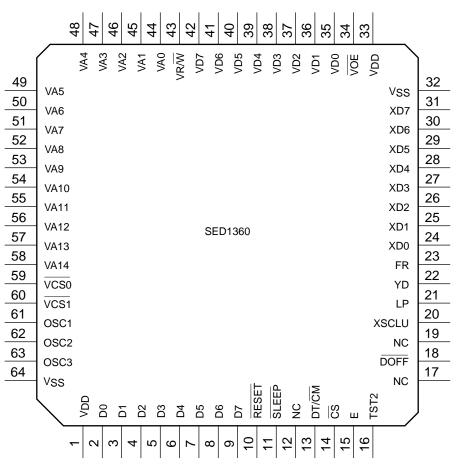

# PINOUT DIAGRAM

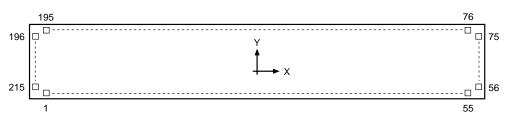

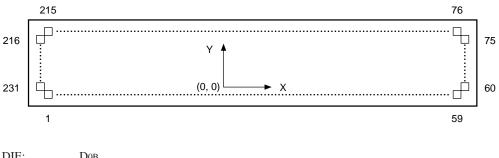

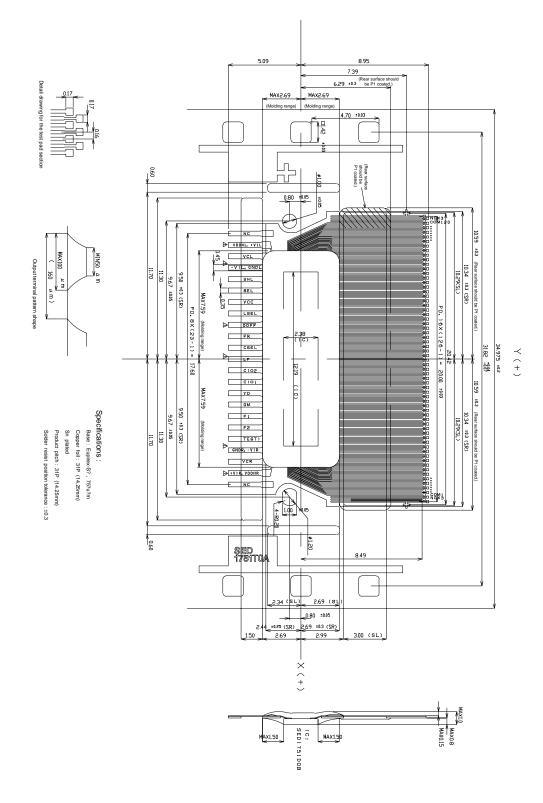

# SED1360D0A

The following figure shows a pinout placement.

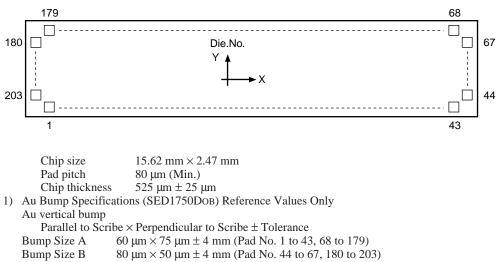

Figure 3. SED1360D0A Pinout Diagram

| chip size       | $4.21 \text{ mm} \times 4.11 \text{ mm}$ |

|-----------------|------------------------------------------|

| chip thickness  | 400 µm                                   |

| pad pich (min.) | 136 µm                                   |

| pad size (min.) | $100 \ \mu m \times 100 \ \mu m$         |

| Pin No. | <b>Χ (μm)</b> | <b>Υ (μm)</b> | Pin No. | <b>Χ (μm)</b> | <b>Υ (μm)</b> |

|---------|---------------|---------------|---------|---------------|---------------|

| 1       | -1425         | -1913         | 44      | 1506          | 1913          |

| 2       | -1221         |               | 45      | 1227          |               |

| 3       | -1085         |               | 46      | 1091          |               |

| 4       | -949          |               | 47      | 955           |               |

| 5       | -813          |               | 48      | 819           |               |

| 6       | -677          |               | 49      | 683           |               |

| 7       | -541          |               | 50      | 547           |               |

| 8       | -405          |               | 51      | 411           |               |

| 9       | -269          |               | 52      | 275           |               |

| 10      | -133          |               | 53      | 139           |               |

| 11      | 3             |               | 54      | 3             |               |

| 12      | 139           |               | 55      | -133          |               |

| 13      | 275           |               | 56      | -269          |               |

| 14      | 411           |               | 57      | -405          |               |

| 15      | 547           |               | 58      | -541          |               |

| 16      | 683           |               | 59      | -677          |               |

| 17      | 819           |               | 60      | -813          |               |

| 18      | 955           |               | 61      | -949          |               |

| 19      | 1091          |               | 62      | -1085         |               |

| 20      | 1227          |               | 63      | -1221         |               |

| 21      | 1506          | <b>↓</b>      | 64      | -1476         | ↓             |

| 22      | 1964          | -1560         | 65      | -1964         | 1547          |

| 23      |               | -1359         | 66      |               | 1350          |

| 24      |               | -1159         | 67      |               | 1153          |

| 25      |               | -1023         | 68      |               | 1017          |

| 26      |               | -887          | 69      |               | 881           |

| 27      |               | -751          | 70      |               | 745           |

| 28      |               | -615          | 71      |               | 609           |

| 29      |               | -479          | 72      |               | 473           |

| 30      |               | -343          | 73      |               | 337           |

| 31      |               | -207          | 74      |               | 201           |

| 32      |               | -71           | 75      |               | 65            |

| 33      |               | 65            | 76      |               | -71           |

| 34      |               | 201           | 77      |               | -207          |

| 35      |               | 337           | 78      |               | -343          |

| 36      |               | 473           | 79      |               | -479          |

| 37      |               | 609           | 80      |               | -615          |

| 38      |               | 745           | 81      |               | -751          |

| 39      |               | 881           | 82      |               | -887          |

| 40      |               | 1017          | 83      |               | -1023         |

| 41      |               | 1153          | 84      |               | -1159         |

| 42      |               | 1359          | 85      |               | -1295         |

| 43      | 🔸             | 1564          | 86      | ▼             | -1499         |

| Table 1. | SED1360D0A | Pin Coordinates |  |

|----------|------------|-----------------|--|

| 10010 11 | 00000000   |                 |  |

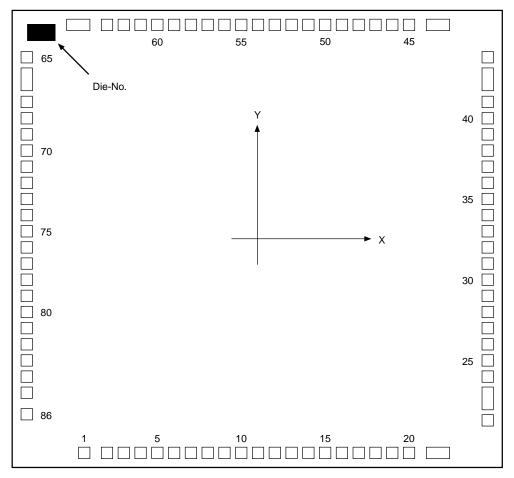

## SED1360F0A

The following figure shows a pinout placement.

Figure 4. SED1360F0A Pinout Diagram

Note: Pinout placement subject to change. Package type: 64 pin surface mount QFP6 NC pins are left unconnected.

# **PIN DESCRIPTION**

Key

- C = CMOS level input

- CS = CMOS level input with hysteresis

- Cosc = CMOS level input for an internal oscillation inverter

- T = TTL level input

- Ox = CMOS output, x denotes output driver type.

- OOSC = CMOS output for an internal oscillation inverter

- PU = integrated pull-up resistor

- PD = integrated pull-down resistor

#### **CPU Interface**

The CPU interface signals are placed on one side of the chip for easy connection to CPU. And the input levels of all CPU Interface pins are unified with CMOS level to allow easy connection to 3.3 V 68 family CPUs.

| Pin Name | Туре | Pin No. | Drv | Description                                                                                                                                                                                                                    |

|----------|------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D [0:7]  | I    | 29      | С   | Data inputs. The data is captured into an SED1360's input data register by the rising edge of "CS".                                                                                                                            |

| E        | I    | 15      | С   | In Active Mode, "E" is used to write or read the CPU data to from SRAM and transfer the data written in the SRAM to the LCD Module.                                                                                            |

| CS       | I    | 14      | С   | The rising edge of this signal is used to capture the state of <u>"D</u> [0:7] and "DT/ $\overline{CM}$ " into SED1360.<br>When " $\overline{CS}$ " is high, no data captures occur.                                           |

| DT/CM    | I    | 13      | С   | If this signal is high, Data is on the bus. If this signal is low, Command is on the bus.                                                                                                                                      |

| SLEEP    | I    | 11      | С   | If this signal is pulled low, the chip enters Sleep<br>Mode. In the Sleep Mode, internal oscillation is<br>disabled, all of the input signals are masked and all<br>of the output signals are controlled to inactive<br>state. |

| RESET    | I    | 10      | CS  | The active low "RESET" signal from the system clears all internal registers.                                                                                                                                                   |

| Table 2. | CPU Interface | Pin Description |

|----------|---------------|-----------------|

|----------|---------------|-----------------|

#### SRAM Interface

The SRAM Interface signals are basically placed on two sides of the chip. The input level of "VD [0:7]" is met with TTL level to connect with generic 3.3 V SRAMs. And also "VD [0:7]" have integrated pullup resistors to eliminate current consumption at the input buffers in Doze Mode.

| Pin Name  | Туре | Pin No. | Drv           | Description                                                                                                                                                                                                                                                                                                                                                |

|-----------|------|---------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VD [0:7]  | I/O  | 3542    | T<br>O2<br>PU | The "VD [0:7]" signals are connected to SRAM's 8 bit data. The captured display data in SED1360 are stored in the SRAM through "VD [0:7]" by the "VR/ $\overline{W}$ " signal.                                                                                                                                                                             |

| VA [0:14] | 0    | 4458    | O2            | The "VA [0:14]" signals are connected to SRAM's address lines. "VA [0:14]" generate either CPU Display Data Write Address or Display Refresh Address depending upon operation modes.                                                                                                                                                                       |

| VCS [0:1] | 0    | 59, 60  | 02            | SED1360 manages up to 64 kb of SRAM as a frame buffer memory. SED1360 is configured to primarily use two 256 kb SRAMs. "VCS0" is active when 1st 32 kb is selected. "VCS1" is active when the rest 32 kb is selected. "VCS [0:1]" are connected to SRAM's chip select inputs (active low). Those signals are inactie (high), if the chip is in Sleep Mode. |

| VOE       | 0    | 34      | 02            | The "VOE" signal is connected to SRAM's data output enable input.                                                                                                                                                                                                                                                                                          |

| VR/W      | 0    | 43      | 02            | The "VR/ $\overline{W}$ " signal is connected to SRAM's write strobe input.                                                                                                                                                                                                                                                                                |

|  | Table 3. | SRAM Interfa | ace Pin Description |

|--|----------|--------------|---------------------|

|--|----------|--------------|---------------------|

# LCD Interface

The LCD interface signals are placed on the rest one side of the chip. The output type of all signals is optimized to drive the Ultra Low Power LCD Module properly.

| Pin Name | Туре | Pin No. | Drv | Description                                                                                                                                                                                                                                                              |

|----------|------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XD [0:7] | 0    | 2431    | O1  | The "XD [0:7]" signals are connected to the display data inputs of the LCD Module. During Doze Mode, the signals are driven low. "XD [0:7] are transferred to the LCD Module by the falling edge of "XSCLU".                                                             |

| XSCLU    | 0    | 20      | O1  | The "XSCLU" signal is connected to the display<br>data shift clock of the LCD Module. During Doze<br>Mode, the signal is driven low to force the RAM<br>integrated Segment Drivers to be in Power Save<br>Mode.                                                          |

| LP       | 0    | 21      | O1  | The "LP" signal is connected to te input, which<br>drives the data latching pulse of the segment<br>drivers and the scanning clock of the common<br>drivers, of the LCD Module. The "LP" period is<br>directly generated by the signal which is input<br>through "OSC1". |

| YD       | 0    | 22      | 01  | The "YD" is connected to the frame start pulse signal of the LCD Module.                                                                                                                                                                                                 |

| FR       | 0    | 23      | 01  | The "FR" signal is connected to the signal which alternates the LCD voltage in the LCD Module.                                                                                                                                                                           |

| DOFF     | 0    | 18      | 01  | This signal outputs low if the chip is in Sleep Mode.                                                                                                                                                                                                                    |

| Table 4. | LCD Interface Pin Description |

|----------|-------------------------------|

|----------|-------------------------------|

# Oscillation

The oscillation pins are used to generate the low frequency which directly generates the "LP" signal.

| Pin Name | Туре | Pin No. | Drv  | Description                                                                                                                                                                        |

|----------|------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSC1     | I    | 61      | Cosc | The pin is connected to the one node of the capacitance and the one node of the resistance. If an external oscillator is used as a clock source, then this pin is the clock input. |

| OSC2     | 0    | 62      | Oosc | This pin is connected to the other node of the capacitance. If an external oscillator is used as a clock source, then this pin should be left unconnected.                         |

| OSC3     | 0    | 63      | Oosc | This pin is connected to the other node of the resistance. If an external oscillator is used as a clock source, then this pin should be left unconnected.                          |

| Table 5. | Oscillation | Pin | Description |

|----------|-------------|-----|-------------|

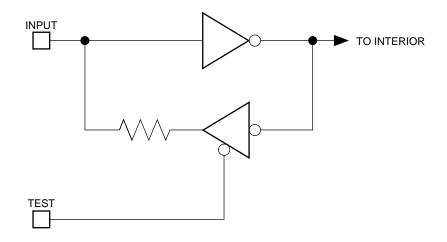

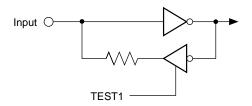

# Test

The test signals are prepared for testing the chip itself.

Table 6. Test Pin Description

| Pin Name | Туре | Pin No.       | Drv | Description                                                                   |  |  |

|----------|------|---------------|-----|-------------------------------------------------------------------------------|--|--|

| NC       | _    | 12, 17,<br>19 |     | NC pins are not connected to the chip. These pins should be left unconnected. |  |  |

| TST2     | 0    | 16            | 01  | This pin should be left unconnected.                                          |  |  |

### **Power Supply**

Table 7. Power Supply Pin Description

| Pin Name | Туре | Pin No. | Drv | Description                                 |  |  |

|----------|------|---------|-----|---------------------------------------------|--|--|

| Vdd      | Р    | 1, 33   |     | VDD supply for the chip. Normally 3.3 volt. |  |  |

| Vss      | Р    | 32, 64  |     | Vss supply for the chip. Normally 0 volt.   |  |  |

Units

V

V

Vdd

Vss

# D.C. CHARACTERISTICS

Conditions:  $VDD = 3.0 \text{ V} \sim 3.6 \text{ V}$ ,  $Ta = -10^{\circ}\text{C}$  to  $70^{\circ}\text{C}$  unless otherwise specified

#### **Absolute Maximum Ratings**

| Parameter                  | Symbol | Rating                      | Units |

|----------------------------|--------|-----------------------------|-------|

| Supply Voltage             | Vdd    | Vss – 0.3 to 5.0            | Volts |

| Input Voltage              | Vin    | Vss - 0.3 to VDD + 0.3      | Volts |

| Output Voltage             | Vout   | Vss to VDD                  |       |

| Operating Temperature      | Topr   | -10 to +70                  | °C    |

| Storage Temperature        | Тѕтс   | -65 to +150                 | °C    |

| Soldering Temperature/Time | Tsol   | 260 for 10 sec max. at lead | °C    |

#### Table 8. Absolute Maximum Ratings

#### **Recommended Operating Conditions**

Input Voltage

|                | 0. 10000111 | nended operating cond |     |     |     |   |

|----------------|-------------|-----------------------|-----|-----|-----|---|

| Parameter      | Symbol      | Condition             | Min | Тур | Max | ĺ |

| Supply Voltage | Vdd         | Vss = 0 V             | 3.0 | 3.3 | 3.6 | ĺ |

Vin

| Table 9. | Recommended | Operating | Conditions |

|----------|-------------|-----------|------------|

# **Input Specification**

| Parameter                                          | Symbol         | Condition                         | Min  | Тур | Max  | Units |

|----------------------------------------------------|----------------|-----------------------------------|------|-----|------|-------|

| Low Level Input Voltage for type C input pins      | VIL1<br>(C)    | Vdd = MIN                         |      |     | 0.6  | V     |

| High Level Input Voltage for type C input pins     | VIH1<br>(C)    | Vdd = MAX                         | 2.5  |     |      | V     |

| High Level Input Voltage for<br>type CS input pins | VIL2<br>(CS)   | VDD = 3.3 V                       |      |     | 0.5  | V     |

| High Level Input Voltage for type CS input pins    | VIH2<br>(CS)   | VDD = 3.3 V                       | 2.9  |     |      | V     |

| Hysteresis Voltage for<br>type CS input pins       | Vнүs<br>(CS)   | VDD = 3.3 V                       |      | 0.1 |      | V     |

| High Level Input Voltage for type T input pins     | VIL3<br>(T)    | Vdd = MIN                         |      |     | 0.5  | V     |

| High Level Input Voltage for type T input pins     | Vінз<br>(T)    | Vdd = MAX                         | 1.7  |     |      | V     |

| Low Level Input Voltage for type Cosc input pins   | VIL4<br>(Cosc) | Vdd = MIN                         |      |     | 0.6  | V     |

| Low Level Input Voltage for type Cosc input pins   | VIH4<br>(Cosc) | Vdd = MAX                         | 2.5  |     |      | V     |

| Input Leakage Current                              | lız            | Vdd = MAX<br>Vil = Vss, Vih = Vdd | -1.0 |     | 1.0  | μA    |

| Input Pin Capacitance                              | CIN            |                                   |      | 10  |      | pF    |

| Pull Down Resistance                               | Rpd<br>(PU)    | VDD = 3.3 V                       | 90   |     | 1100 | kΩ    |

| Pull Up Resistance                                 | Rpu<br>(PU)    | Vdd = 3.3 V                       | 90   |     | 1100 | kΩ    |

Table 10. Input Specifications

# **Output Specifications**

Table 11. Output Specifications

| Parameter                                          | Symbol         | Condition                         | Min         | Тур | Max         | Units |

|----------------------------------------------------|----------------|-----------------------------------|-------------|-----|-------------|-------|

| Low Level Output Voltage for type O1 output pins   | Vol1<br>(O1)   | VDD = MIN<br>IOL = 1.0 mA         | Vss<br>+0.3 |     |             | V     |

| Low Level Output Voltage for type O1 output pins   | Vон1<br>(O1)   | Vdd = MIN<br>Ioh = -0.5 mA        |             |     | Vdd<br>-0.3 | V     |

| Low Level Output Voltage for type O2 output pins   | Vol2<br>(O2)   | VDD = MIN<br>IOL = 3.0 mA         | Vss<br>+0.3 |     |             | V     |

| Low Level Output Voltage for type O2 output pins   | Vон2<br>(O2)   | Vdd = MIN<br>Іон = -1.5 mA        |             |     | Vdd<br>-0.3 | V     |

| Low Level Output Voltage for type Oosc output pins | Vol3<br>(Oosc) | Vdd = MIN<br>Iol = 100 μA         | Vss<br>+0.3 |     |             | V     |

| Low Level Output Voltage for type Oosc output pins | Voнз<br>(Oosc) | Vdd = MIN<br>Ιοη = -100 μΑ        |             |     | Vdd<br>-0.3 | V     |

| Output Leakage Current                             | loz            | Vdd = MAX<br>Voh = Vdd, Vol = Vss | -1.0        |     | 1.0         | μΑ    |

| Output Pin Capacitance                             | Соит           |                                   |             | 10  |             | pF    |

# **Power Consumption**

| Parameter                                                         | Symbol | Condition                                                     | Min | Тур | Max | Units |

|-------------------------------------------------------------------|--------|---------------------------------------------------------------|-----|-----|-----|-------|

| Current Consumption<br>in Active Mode<br>with CPU write access    | IOP1   | VDD = 3.3 V<br>tcyce = 500 ns<br>fosc = 24 kHz                |     | 5   |     | mA    |

| Current Consumption<br>in Active Mode<br>with no CPU write access | IOP2   | VDD = 3.3 V<br>tcyce = 500 ns<br>"CS" = high<br>fosc = 24 kHz |     | 1   |     | mA    |

| Current Consumption<br>in Doze Mode<br>with CPU write access      | ЮРЗ    | VDD = 3.3 V<br>tcyce = 500 ns<br>fosc = 24 kHz                |     | 4   |     | mA    |

| Current Consumption<br>in Doze Mode<br>with no CPU write access   | IOP4   | VDD = 3.3 V<br>tcyce = 500 ns<br>"CS" = high<br>fosc = 24 kHz |     | 150 |     | μΑ    |

| Current Consumption<br>in Sleep Mode                              | IOP5   | VDD = 3.3 V<br>No input signals toggle.                       |     | 1   |     | μΑ    |

Table 12. Power Consumption

Note: The above table shows the target power consumption.

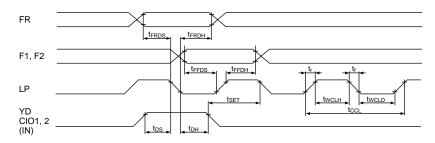

# A.C. CHARACTERISTICS

Conditions: VDD = 3.3 V,  $Ta = 0^{\circ}C$  to  $70^{\circ}C$  unless otherwise specified Tr, Tf for all inputs must be -10 ns (10% to 90%)CL = 10 pF (SRAM Interface)CL = 20 pF (LCD Interface)

A single 1.5 V threshold voltage is used for the A.C. measurements.

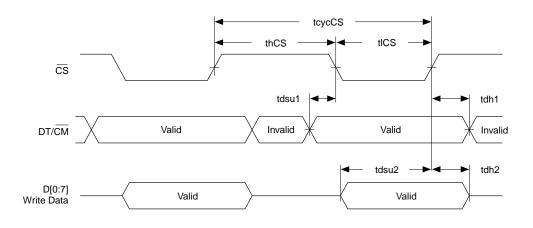

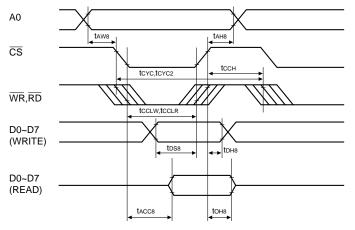

## **CPU Interface Timing**

| Parameter                | Symbol | Min           | Тур | Мах | Units |

|--------------------------|--------|---------------|-----|-----|-------|

| "CS" period              | tcycCS | <b>t</b> cycE |     |     | ns    |

| "CS" low pulse width     | tics   | 170           |     |     | ns    |

| "CS" high pulse width    | thcs   | 100           |     |     | ns    |

| "DT/CM" setup to "CS"    | tdsu1  | 20            |     |     | ns    |

| "DT/CM" hold from "CS"   | tdh1   | 0             |     |     | ns    |

| "D [0:7]" setup to "CS"  | tdsu2  | 70            |     |     | ns    |

| "D [0:7]" hold from "CS" | tdh2   | 0             |     |     | ns    |

Table 13. CPU Interface Timing

Figure 5. CPU Interface Timing

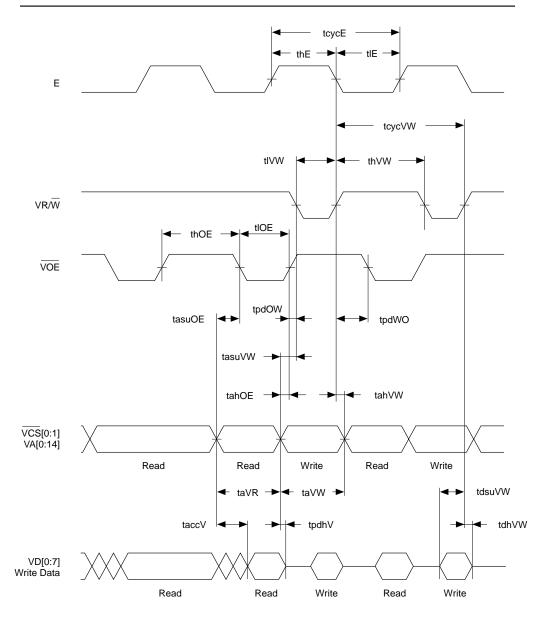

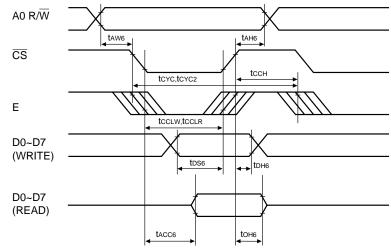

# SRAM Interface Timing

| Parameter                                       | Symbol         | Min             | Тур                     | Мах     | Units |

|-------------------------------------------------|----------------|-----------------|-------------------------|---------|-------|

| "E" period                                      | <b>t</b> cycE  | 333             |                         |         | ns    |

| "E" low pulse width                             | t⊫             | 142             |                         |         | ns    |

| "E" high pulse width                            | thE            | 137             |                         |         | ns    |

| "VR/W" period                                   | <b>t</b> cycVW | <b>t</b> cycE   |                         |         | ns    |

| "VR/W" low pulse width                          | tıvw           |                 | <b>t</b> hE <b>-</b> 40 |         | ns    |

| "VR/W" high pulse width                         | <b>t</b> h∨W   |                 | t⊫                      |         | ns    |

| "VA [0:14]", "VCS [0:1]" setup to "VR/W"        | <b>t</b> asu∨W | 0               |                         |         | ns    |

| "VA [0:14]", "VCS [0:1]" hold from<br>"VR/W"    | tah∨W          | 0               |                         |         | ns    |

| "VD [0:7]" setup to "VR/W"                      | <b>t</b> dsuVW | <b>t</b> ivw-20 | tıvw-10                 |         | ns    |

| "VD [0:7]" hold from "VR/W"                     | <b>t</b> dh∨W  | 0               |                         |         | ns    |

| valid address period for the Display<br>Refresh | <b>t</b> avr   | t⊫-15           | t⊫                      |         | ns    |

| valid address period for the CPU data write     | ta∨w           | the-15          | thE                     |         | ns    |

| SRAM read data access from the valid address    | tacc∨          |                 |                         | tavR-25 | ns    |

| SRAM read data hold time from the valid address | <b>t</b> pdh∨  | 0               |                         |         | ns    |

| "VA [0:14]", "VCS [0:1]" setup to "VOE"         | tasuOE         | 0               |                         |         | ns    |

| "VOE" hold from "VA [0:14]", "VCS [0:1]"        | <b>t</b> ahOE  | 0               |                         |         | ns    |

| "VOE" low pulse width                           | tioe           |                 | t⊫                      |         | ns    |

| "VOE" high pulse width                          | <b>t</b> hOE   |                 | <b>t</b> hE             |         | ns    |

| "VR/W" delay from "VOE"                         | <b>t</b> pdOW  | 0               |                         |         | ns    |

| "VOE" delay from "VR/OW"                        | <b>t</b> pdWO  | 0               |                         |         | ns    |

Figure 6. SRAM Interface Timing

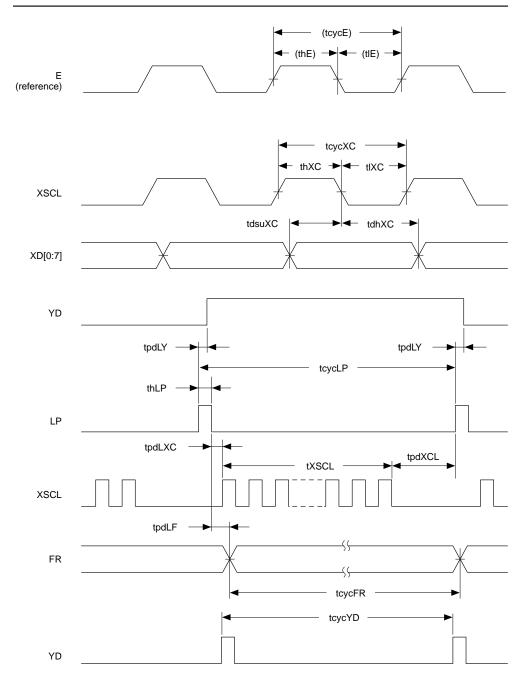

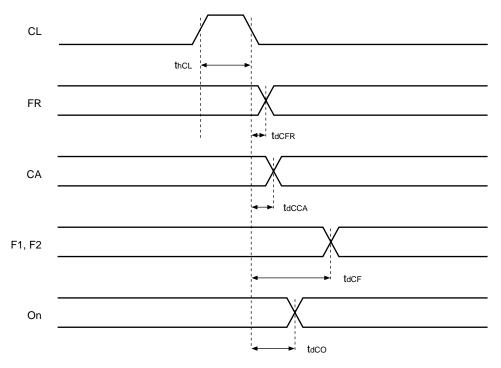

# **LCD Interface Timing**

| Parameter                   | Symbol             | Min               | Тур                                                     | Max                                 | Units |

|-----------------------------|--------------------|-------------------|---------------------------------------------------------|-------------------------------------|-------|

| "XSCLU" period              | <b>t</b> cycXC     | <b>t</b> cycE     |                                                         |                                     | ns    |

| "XSCLU" low pulse width     | tixc               |                   | ti⊨                                                     |                                     | ns    |

| "XSCLU" high pulse width    | <b>t</b> hXC       |                   | thE                                                     |                                     | ns    |

| "XD [0:7]" setup to "XSCL"  | <b>t</b> dsuXC     |                   | thE                                                     |                                     | ns    |

| "XD [0:7]" hold from "XSCL" | <b>t</b> dhXC      |                   | ti⊨                                                     |                                     | ns    |

| "YD" delay from "LP"        | <b>t</b> pdLY      | 0                 |                                                         |                                     | ns    |

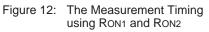

| "LP" period                 | <b>t</b> cycLP     | tcycOSC           | 2tcycOSC                                                | 4tcycOSC                            | ns    |

| "LP" high pulse width       | <b>t</b> hLP       | 500               | 700                                                     | 1200                                | ns    |

| "XSCL" delay from "LP"      | <b>t</b> pdLXC     | 3tcycE<br>+thE-50 | 4tcycE                                                  | 4 <b>t</b> cycE<br>+ <b>t</b> hE+50 | ns    |

| "LP" delay from "XSCL"      | t <sub>pdXCL</sub> |                   |                                                         |                                     | ns    |

| "XSCL" enabled              | txsc∟              |                   | [(Hor.<br>size/8)-1]<br>× t <sub>cyE+thE</sub>          |                                     | ns    |

| "YD" period                 | <b>t</b> cycYD     |                   | $\stackrel{(\text{Ver.size})}{\times t_{\text{cycLP}}}$ |                                     | ns    |

| "FR" high or Low time       | <b>t</b> cycFR     |                   | <b>t</b> cycYD                                          |                                     | ns    |

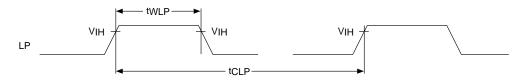

| "FR" delay from "LP"        | tpdLF              | 10                | 0                                                       | 200                                 | ns    |

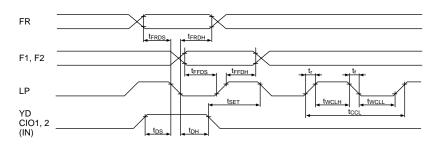

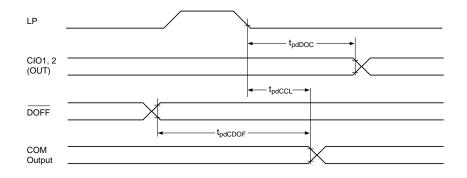

Table 15. LCD Interface Timing

Notes: 1. t<sub>cycOSC</sub> is a period of frequency given to or generated at "OSC1".

2. Hor.size is described in the section Display Size.

3. Ver.size is described in the section Display Size.

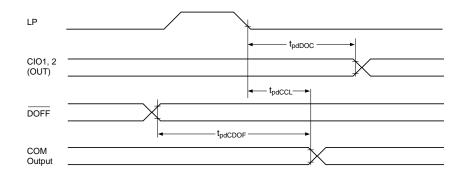

Figure 7. LCD Interface Timing

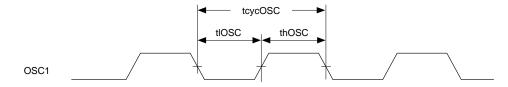

# **Oscillation Timing**

| Parameter                                          | Symbol  | Min                 | Тур                          | Мах                 | Units |

|----------------------------------------------------|---------|---------------------|------------------------------|---------------------|-------|

| "OSC1" period                                      | tcycOSC | 20<br>tosc = 50 kHz | <b>41.7</b><br>fosc = 24 kHz | 50<br>fosc = 20 kHz | μs    |

| "OSC1" low width if external oscillation is used.  | tiosc   |                     | 0.5tcycOSC                   |                     | μs    |

| "OSC1" high width if external oscillation is used. | thosc   |                     | 0.5tcycosc                   |                     | μs    |

Table 16. LCD Interface Timing

Figure 8. LCD Interface Timing

# **OPERATION DESCRIPTION**

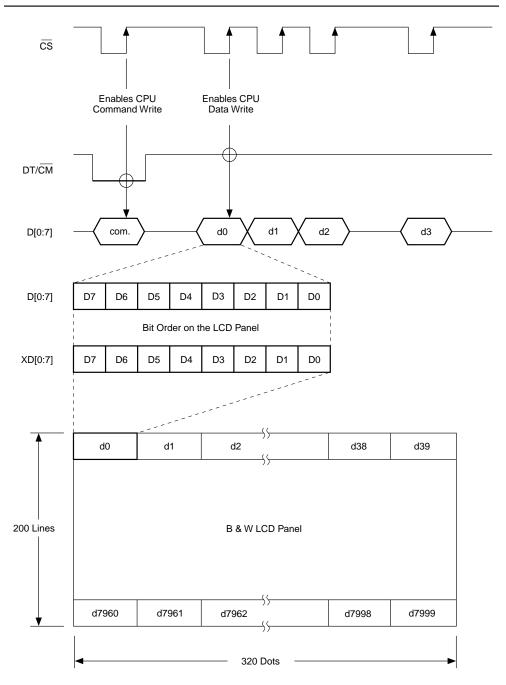

# CPU Write Data Transfer

The following figure gives a basic timing for SED1360 to receive the CPU Write Data and relationship between CPU Data and pixels on the LCD panel. It is assumed that both CPU Write Start Address and Display Refresh Start Address are the same and the  $320 \times 200$  dot LCD is used in the following figure.

- (1) The rising edge of " $\overline{CS}$ " is used for SED1360 to latch the CPU data.

- (2) The CPU Data Write, after the "Display Data Write" command is executed, will be stored in the SRAM according to the internal CPU Write Address.

- (3) The first 40 Byte data will be stored in SRAM and displayed continuously on the same line.

- (4) The data will be displayed at the most left position on the next line on the panel every 40 Byte data.

Figure 9. CPU Write Data Transfer

### **Display Data Transfer Modes**

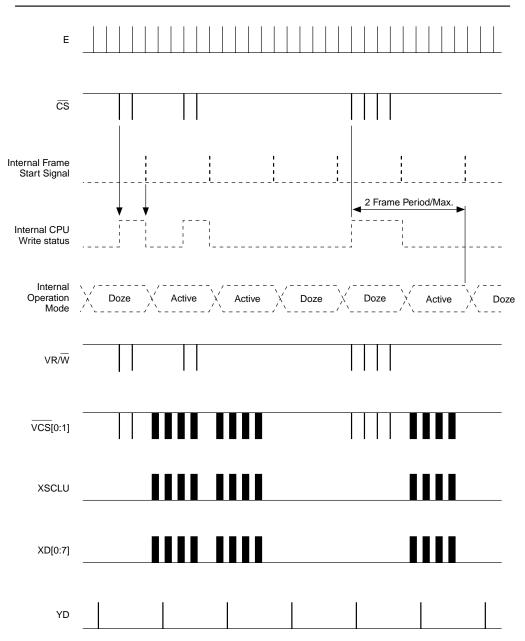

#### **Display Data Auto Transfer Mode**

The following figure gives a basic operation mode which SED1360 switches automatically. The figure assumes that the chip is configured in Display Data Auto Transfer Mode.

- (1) If CPU Display Data Write Access occurs, then the next Frame period will be Active Mode. That is the Active Mode is initiated by the CPU Display Data Write Access, if the chip is configured in Display Data Auto Transfer Mode.

- (2) If no CPU Display Data Write Access occurs in one Frame period, then the next Frame period will be Doze Mode.

- (3) SED1360 switches the whole LCD Display Subsystem between Doze Mode and Active Mode.

- (4) In the Active Mode, SED1360 reads the data from the SRAM, enables "XSCLU" in order to transfer the data stored in the SRAM to the LCD Module, then the RAM integrated Segment Drivers wake up from the power save mode.

- (5) In the Doze Mode, SED1360 stops reading the data from the SRAM, disables "XSCLU" in order for the RAM integrated Segment Drivers to enter into the Power Save Mode.

Figure 10. Display Data Auto Transfer Mode

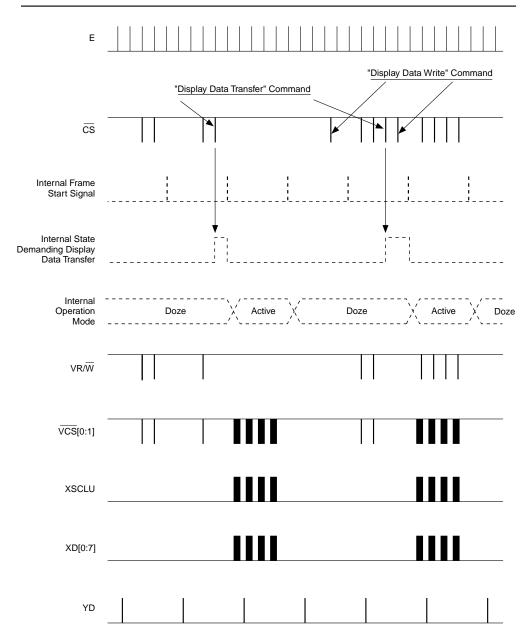

#### **Display Data Manual Transfer Mode**

The following figure gives another basic operation mode which SED1360 controls Active Mode with the "Display Data Transfer" command. The figure assumes that the chip is configured in Display Data Manual Transfer Mode.

- (1) If the "Display Data Transfer" command is set to the chip, then the next Frame period will be Active Mode. That is the Active Mode is initiated by the Display Data Transfer" command, if the chip is configured in Display Data Manual Transfer Mode.

- (2) Once one Frame of display data, which are in the SRAM, are transferred to the LCD Module, the chip switches to Doze Mode and it keeps the Doze Mode until next "Display Data Transfer" command is executed. But if the next "Display Data Transfer" command is set without having any other commands between these two "Display Data Transfer" commands, the next "Display Data Transfer" command is ignored. That is in this case the next "Display Data Transfer" command does not set the chip in the Active Mode.

- (3) SED1360 switches the whole LCD Display Subsystem between Doze Mode and Active Mode.

- (4) In the Active Mode, SED1360 reads the data from the SRAM, enables "XSCLU" in order to transfer the data stored in the SRAM to the LCD Module, then the RAM integrated Segment Drivers wake up from the power save mode.

- (5) In the Doze Mode, SED1360 stops reading the data from the SRAM, disables "XSCLU" in order for the RAM integrated Segment Drivers to enter into the Power Save Mode.

Figure 11. Display Data Manual Transfer Mode

#### Sleep Mode

SED1360 can enter into the Sleep Mode by setting the "SLEEP" signal low. This mode is prepared to shut the whole LCD Display Subsystem off with keeping the data in the SRAM. In the Sleep Mode, the chip will be in the following state.

- (1) The internal oscillation is displayed.

- (2) VA [0:14] output low, VCS [0:1] output high, VD [0:7] will be high impedance (pins are pulled high by the integrated pull-up resisters).

- (3) "FR", "YD", "LP", "XSCLU", "XD [0:7]" and "DOFF" output low. VOE, VR/W output high.

- (4) "D [0:7]", "E" "CS", "DT/CM" and "RESET" are internally masked but they also should be kept in invalid state.

# **OSCILLATION DESCRIPTION**

SED1360's Hardware is optimized to display  $320 \times 200$  LCD panel driven by RAM integrated Segment Drivers as a default chip configuration. This section describes how to determine the frequency which is input to OSC1 and how to generate the frequency by using the internal oscillation function.

## **OSC1 Frequency Determination**

Conditions: 320 × 200 single scan LCD panel assumes 60 Hz as an LCD frame frequency

- (1) "LP" period is obtained by the following calculation.

- $60 \times 200 = 12$  kHz (2) If an external oscillator is used, the OSC1 frequency can be the same as "LP". Then 12 kHz is the required frequency for OSC1.

- (3) If an internal oscillator is used, the oscillation frequency has to be doubled to be 24 kHz. The internal oscillation might be unstable below 24 kHz. So if the required frequency is below 20 kHz, it is recommended to generate doubled frequency. There is a register which divides the internal oscillation frequency by two, four or eight.

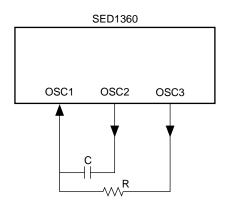

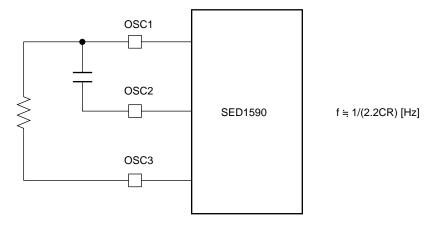

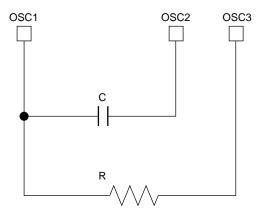

## **Internal Oscillation**

The following figure shows how to connect a capacitance and a resistance to the oscillation pins. The values of C and R have to be determined on the actual system.

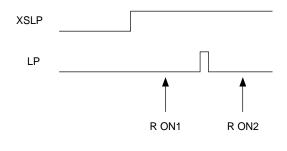

Figure 12. Internal Oscillation Implementation

# **COMMAND DESCRIPTION**

SED1360 has several commands which can manipulate the data transfer procedure between CPU, SRAM, LCD Module and SED1360.

#### **Display Size**

| command; | $DT/\overline{CM} = 0$ |

|----------|------------------------|

|----------|------------------------|

| D7      | D6 | D5  | D4 | D3 | D2 | D1 | D0 |     |

|---------|----|-----|----|----|----|----|----|-----|

| 0       | 0  | 0   | 0  | 0  | 0  | 0  | 1  | 01H |

| data: [ |    | - 1 |    |    |    |    |    |     |

| data; L |     | = 1 | -   | -   | -   | -   |     | _     |

|---------|-----|-----|-----|-----|-----|-----|-----|-------|

| 0       | 0   | HC5 | HC4 | HC3 | HC2 | HC1 | HC0 | data1 |

| VC7     | VC6 | VC5 | VC4 | VC3 | VC2 | VC1 | VC0 | data2 |

(1) This command sets the size of the display.

(2) This command requires two bytes of data which follow this command.

- (3) The first data defines a horizontal size of the display in byte unit, and the second data defines a vertical size of the display in line unit.

- (4) The horizontal size is set 320 dots and the vertical size is set 200 lines when the "RESET" signal is set low.

Table 17. Horizontal Size

| Hor. size | HC [5:0] |

|-----------|----------|

| 8         | 00h      |

| 16        | 01h      |

| 24        | 02h      |

|           |          |

| 240       | 1Dh      |

|           |          |

| 320       | 27h      |

|           |          |

| 512       | 3Fh      |

Table 18. Vertical Size

| VC [7:0] |

|----------|

| 00h      |

| 01h      |

| 02h      |

|          |

| C7h      |

|          |

| Efh      |

|          |

| Ffh      |

|          |

#### **Display Data Auto Transfer Mode**

command;  $DT/\overline{CM} = 0$

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |

|----|----|----|----|----|----|----|----|-----|

| 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 02H |

(1) This command configures the chip in the Display Data Auto Transfer Mode. Detailed functional explanation is described in "Display Data Auto Transfer Mode".

## **Display Data Manual Transfer Mode**

| command; $DT/\overline{CM} = 0$ |    |    |    |    |    |    |    |     |

|---------------------------------|----|----|----|----|----|----|----|-----|

| D7                              | D6 | D5 | D4 | D3 | D2 | D1 | D0 |     |

| 0                               | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03H |

(1) This command configures the chip in the Display Data Manual Transfer Mode. Detailed functional explanation is described in "Display Manual Transfer Mode".

#### **Display Data Transfer**

| comma | and; D1 | Г/СМ = | 0  | -  |    |    |    |    |

|-------|---------|--------|----|----|----|----|----|----|

| D7    | D6      | D5     | D4 | D3 | D2 | D1 | D0 |    |

| 0     | 0       | 0      | 0  | 0  | 1  | 0  | 0  | 04 |

(1) This command force the chip to go into the Active Mode so that the chip can start transferring the display data to the LCD Module. Detailed functional explanation is described in "Display Data Manual Transfer Mode". This command is executable in not only Display Data Manual Transfer Mode but also Display Data Auto Transfer Mode.

#### **Display Data Write**

| command; $DT/\overline{CM} = 0$ |    |    |    |    |    |    |    | _     |

|---------------------------------|----|----|----|----|----|----|----|-------|

| D7                              | D6 | D5 | D4 | D3 | D2 | D1 | D0 |       |

| 0                               | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 05H   |

| data; $DT/\overline{CM} = 1$    |    |    |    |    |    |    | _  |       |

| *                               | *  | *  | *  | *  | *  | *  | *  | data1 |

| *                               | *  | *  | *  | *  | *  | *  | *  | data2 |

|                                 |    |    |    |    |    |    |    |       |

| *                               | *  | *  | *  | *  | *  | *  | *  | datan |

|                                 |    |    |    |    |    |    |    | -     |

- (1) This command enables the chip to receive the data as the display data which are stored in SRAM.

- (2) Data (data1,...datan) which follow this command are stored in SRAM until other commands are executed. If any other command breaks Display Data Write Access to the SRAM through the chip, this command has to be set again before starting Display Data Write Access.

#### **CPU Write Start Address**

| command; $DT/\overline{CM} = 0$ |       |      |      |      |      |     |     |       |

|---------------------------------|-------|------|------|------|------|-----|-----|-------|

| D7                              | D6    | D5   | D4   | D3   | D2   | D1  | D0  |       |

| 0                               | 0     | 0    | 0    | 0    | 1    | 1   | 0   | 06H   |

| data; D                         | DT/CM | = 1  |      |      |      |     |     | _     |

| WA7                             | WA6   | WA5  | WA4  | WA3  | WA2  | WA1 | WA1 | data1 |

| WA15                            | WA14  | WA13 | WA12 | WA11 | WA10 | WA9 | WA8 | data2 |

(1) This command sets the SRAM address which CPU Display Data can be stored.

(2) This command requires two bytes of data which follow this command.

(3) The order of two byte data is that the first data is lower byte and second data is higher byte.

(4) The two bytes of data are temporarily set to the internal CPU Write Address Counter by this command. And the CPU Write Address Counter is increased by one, when CPU Display Data Write Access occurs.

#### **Display Refresh Start Address**

command;  $DT/\overline{CM} = 0$

|       |                 |      |      |      |      |     |     | _     |

|-------|-----------------|------|------|------|------|-----|-----|-------|

| D7    | D6              | D5   | D4   | D3   | D2   | D1  | D0  |       |

| 0     | 0               | 0    | 0    | 0    | 1    | 1   | 1   | 07H   |

| data; | data; DT/CM = 1 |      |      |      |      |     |     |       |

| RA7   | RA6             | RA5  | RA4  | RA3  | RA2  | RA1 | RA1 | data1 |

| RA15  | RA14            | RA13 | RA12 | RA11 | RA10 | RA9 | RA8 | data2 |

(1) This command sets the SRAM address which SED1360 starts reading the data from, to transfer the display data to the LCD Module in Active Mode.

(2) This command requires two bytes of data which follow this command.

(3) The order of two byte data is that the first data is lower byte and second data is higher byte.

(4) The two bytes of data are set to the internal Display Data Refresh Address Counter by this command.

#### Display ON/OFF

command;  $DT/\overline{CM} = 0$

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0         |            |

|----|----|----|----|----|----|----|------------|------------|

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | ON/<br>OFF | 81H<br>80H |

(1) This command controls " $\overline{\text{DOFF}}$ " output.

(2) If the ON/OFF is set to high "DOFF" outputs high. If the ON/OFF is set to low "DOFF" outputs low.

(3) The  $ON/\overline{OFF}$  is set to low at the reset.

# LP Configuration

| command; $DT/\overline{CM} = 0$ |    |    |    |    |    |     |     | _     |

|---------------------------------|----|----|----|----|----|-----|-----|-------|

| D7                              | D6 | D5 | D4 | D3 | D2 | D1  | D0  |       |

| 0                               | 0  | 0  | 0  | 1  | 0  | 0   | 0   | 08H   |

| data; DT/ <del>CM</del> = 1     |    |    |    |    |    |     |     | -     |

| 0                               | 0  | 0  | 0  | 0  | 0  | FS1 | FS0 | data1 |

(1) This command selects "LP" period.

- (2) FS1,0 select the period of the signal "LP". The following table shows how to select the required frequency for the signal "LP".

- (3) FS [1,0] = [0,0] is set when the "RESET" signal is set low.

| FS1 | FS0 | LP frequency |

|-----|-----|--------------|

| 0   | 0   | fosc         |

| 0   | 1   | fosc/2       |

| 1   | 0   | fosc/4       |

| 1   | 1   | fosc/8       |

Table 19. LP Frequency

# ERRORTA

This version has one error. About CPU Write Start Address, Values which CPU wrote is increased by one. So, you should set values which is decreased by one.

# NOTICE

No parts of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind aristing out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty what anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions there of may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

Pay attention to the following point when using a semiconductor device. A semiconductor device will be deteriorated in its characteristic when it is exposed to light. For this reason, this IC might malfunction in some cases when exposed to the light. To avoid causing such malfunction, steps be taken to shield the light in its packaging or enclosure to prevent the surface, rear and side of this IC from being exposed to the light.

# SED1580

# Contents

| INTRODUCTION                    | 2-1  |

|---------------------------------|------|

| FEATURES                        | 2-1  |

| BLOCK DIAGRAM                   | 2-2  |

| PIN CONFIGURATION               | 2-3  |

| ELECTRICAL CHARACTERISTICS      | 2-15 |

| POWER SOURCE                    | 2-19 |

| EXAMPLE OF EXTERNAL CONNECTIONS | 2-20 |

# OVERVIEW

### Description

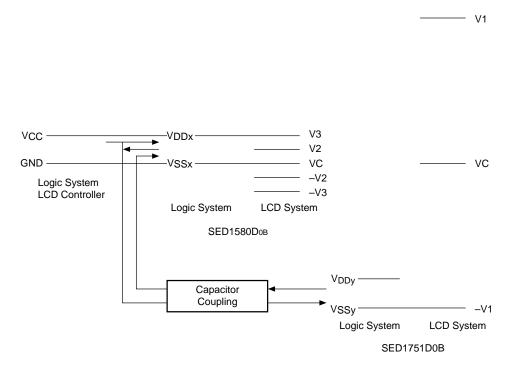

The SED1580 is a 160-output, 5-level segment (column) driver for MLS (Multi-Line Selection) driving, able to drive with both high contrast and high speed. It is used in conjunction with the SED1751. When paired with the SED1751 it can be connected to the SED1360 LCD controller.

Because the SED1580 stores display data in its internal display RAM and generates LC drive signals, display data transmission from the controller can be suspended except for when there are changes to the display, thereby enabling an ultra low power display system.

The SED1580 uses a slim package, facilitating the construction of thinner LCD panels, and the low-voltage operation of its logic power source makes it appropriate to a wide range of applications.

# FEATURES

- Number of simultaneous line selects: 4 Lines

- Drive duty ratio (MAX) 1/240 duty

- LCD driver outputs 160 outputs

- Internal display RAM  $160 \times 240$  bit

- Extremely low consumption current

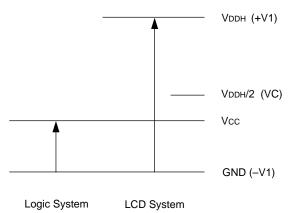

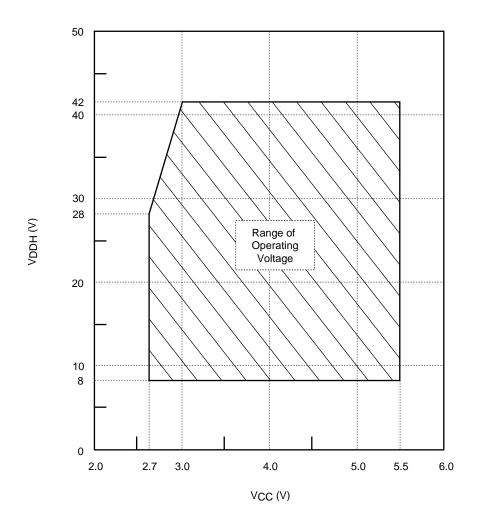

- Power Source Voltages Logic System: 3.0 to 3.6V (Max)

LCD System: 6.0 to 7.2V (Max)

- High speed, low power data transmission possible through the 4-bit/8-bit switchable bus enable chain method

- Non-biased display off function

- Output shift direction pin select supported

- Slim chip shape

•

Shipment status:

In CHIP form ......SED1580D0B In TCP form .....SED1580T0A

This product is not designed for resistance to light or radiation

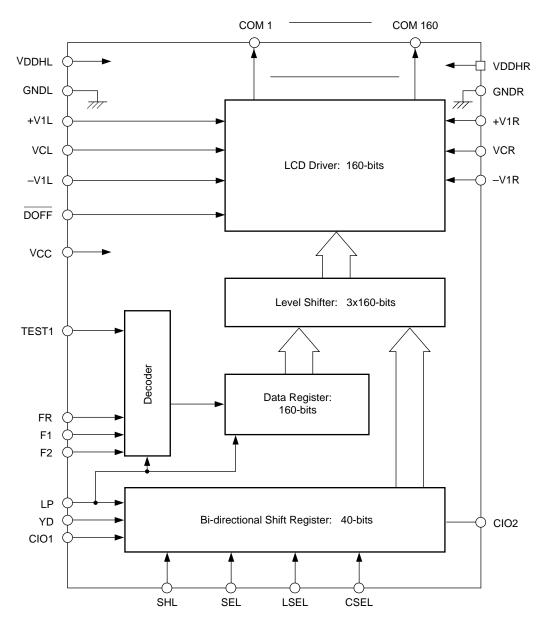

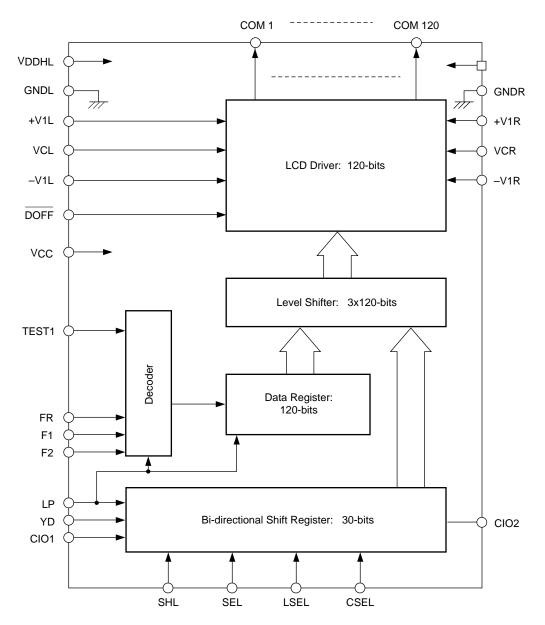

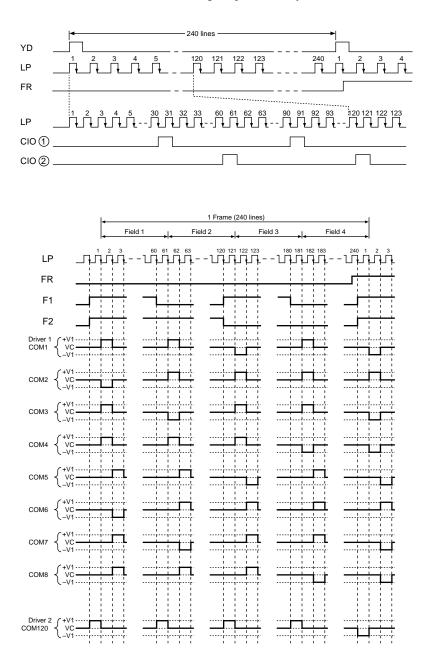

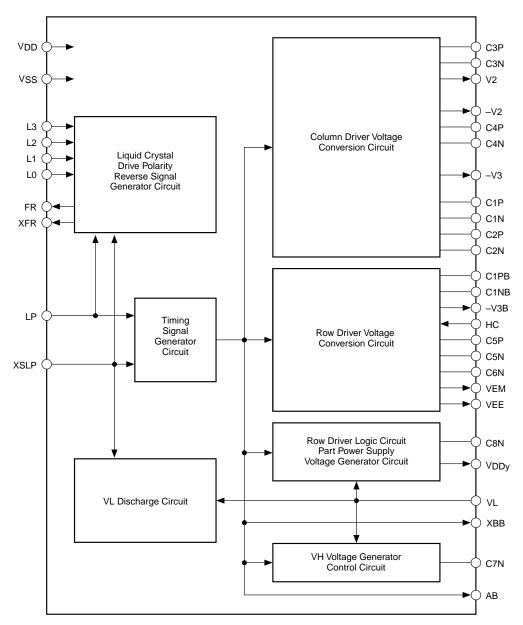

### **BLOCK DIAGRAM**

**Block Diagram**

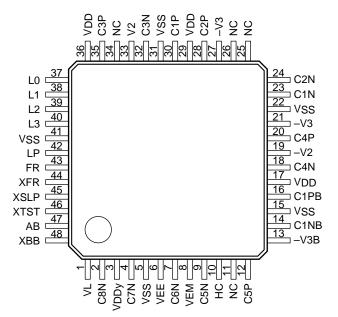

# **PIN CONFIGURATION**

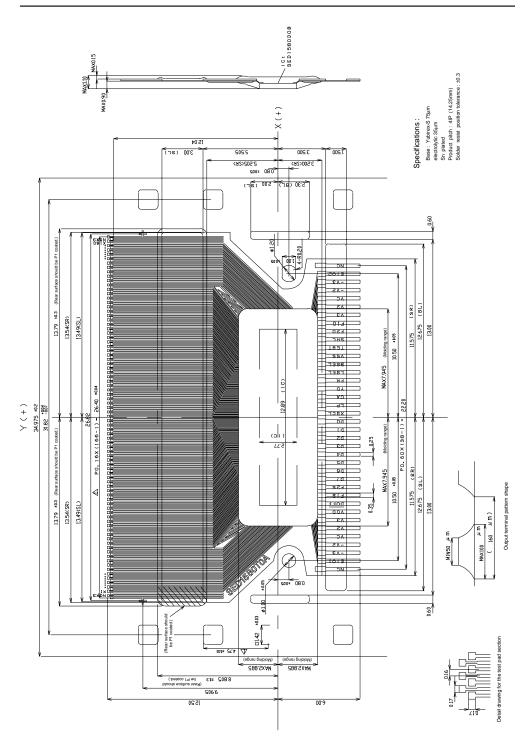

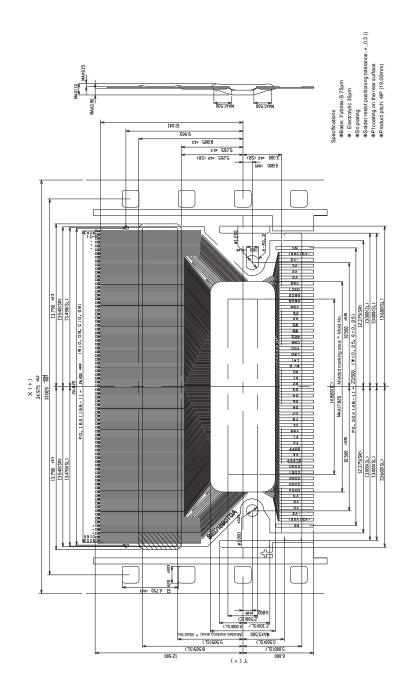

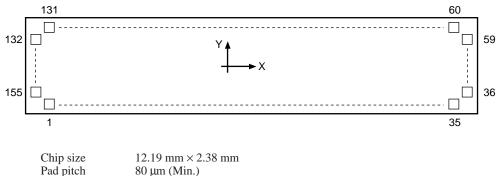

**Pad Layout**

Bump size (Unit: µm)

| Pad number                         |     |    |

|------------------------------------|-----|----|

| i ad number                        | Х   | Y  |

| 56 to 215                          | 67  | 63 |

| 1, 7 to 16, 18 to 36, 38 to 49, 55 | 74  | 74 |

| 2 to 6, 17, 37, 50 to 54           | 110 | 74 |

| 22                                 | 110 | 75 |

Bump specifications (reference values)

| Items                      |         | Specifications |         |

|----------------------------|---------|----------------|---------|

| nems                       | MIN     | TYP            | MAX     |

| Bump size specifications   | -4 μm   | Bump size      | +4 µm   |

| Bump height specifications | –5.5 μm | 22.5 μm        | +5.5 μm |

| Bump strength              | 30g     |                |         |

### **Pin Coordinates**

### SED1580 Bump Center Coordinates

| Pin      | Name | Х     | Y     | Pin | Name       | Х    | Y        | Pin | Name         | X     | Y    |

|----------|------|-------|-------|-----|------------|------|----------|-----|--------------|-------|------|

| 1        | EIO2 | -5378 | -1240 | 63  | X8         | 6303 | -265     | 125 | X70          | 1075  | 1246 |

| 2        | -V3  | -5222 |       | 64  | X9         |      | -159     | 126 | X71          | 972   |      |

| 3        | -V2  | -5044 |       | 65  | X10        |      | -53      | 127 | X72          | 870   |      |

| 4        | VC   | -4866 |       | 66  | X11        |      | 53       | 128 | X73          | 767   |      |

| 5        | V2   | -4688 |       | 67  | X12        |      | 159      | 129 | X74          | 665   |      |

| 6        | V3   | -4510 |       | 68  | X13        |      | 265      | 130 | X75          | 562   |      |

| 7        | NC   | -4322 |       | 69  | X14        |      | 372      | 131 | X76          | 460   |      |

| 8        | NC   | -4144 |       | 70  | X15        |      | 478      | 132 | X77          | 357   |      |

| 9        | NC   | -3966 |       | 71  | X16        |      | 584      | 133 | X78          | 255   |      |

| 10       | NC   | -3789 |       | 72  | X17        |      | 690      | 134 | X79          | 152   |      |

| 11       | NC   | -3611 |       | 73  | X18        |      | 797      | 135 | X80          | 50    |      |

| 12       | F10  | -3449 |       | 74  | X19        |      | 903      | 136 | X81          | -52   |      |

| 13       | F20  | -2915 |       | 75  | X20        | ♥    | 1009     | 137 | X82          | -154  |      |

| 14       | NC   | -2266 |       | 76  | X20        | 6098 | 1246     | 138 | X83          | -257  |      |

| 15       | SHL  | -2086 |       | 77  | X22        | 5995 | 1240     | 139 | X84          | -359  |      |

| 16       | TEST | -1906 |       | 78  | X23        | 5893 |          | 140 | X85          | -462  |      |

| 17       | Vss  | -1726 |       | 79  | X24        | 5790 |          | 140 | X86          | -564  |      |

|          | BSEL | -1546 |       | 80  | X24<br>X25 | 5688 |          | 141 | X87          | -567  |      |

| 18       | LSEL |       |       |     |            |      |          |     | X88          |       |      |

| 19<br>20 |      | -1366 |       | 81  | X26        | 5585 |          | 143 |              | -769  |      |

| 20       | FR   | -1186 |       | 82  | X27        | 5483 |          | 144 | X89          | -872  |      |

| 21       | YD   | -1006 |       | 83  | X28        | 5380 |          | 145 | X90          | -974  |      |

| 22       | NC   | -826  |       | 84  | X29        | 5278 |          | 146 | X91          | -1077 |      |

| 23       | CA   | -546  |       | 85  | X30        | 5175 |          | 147 | X92          | -1179 |      |

| 24       | LP   | -466  |       | 86  | X31        | 5073 |          | 148 | X93          | -1282 |      |

| 25       | XSCL | -286  |       | 87  | X32        | 4970 |          | 149 | X94          | -1385 |      |

| 26       | D0   | 163   |       | 88  | X33        | 4868 |          | 150 | X95          | -1487 |      |

| 27       | D1   | 343   |       | 89  | X34        | 4765 |          | 151 | X96          | -1590 |      |

| 28       | D2   | 523   |       | 90  | X35        | 4663 |          | 152 | X97          | -1692 |      |

| 29       | D3   | 703   |       | 91  | X36        | 4560 |          | 153 | X98          | -1795 |      |

| 30       | D4   | 883   |       | 92  | X37        | 4458 |          | 154 | X99          | -1897 |      |

| 31       | D5   | 1063  |       | 93  | X38        | 4355 |          | 155 | X100         | -2000 |      |

| 32       | D6   | 1243  |       | 94  | X39        | 4253 |          | 156 | X101         | -2102 |      |

| 33       | D7   | 1423  |       | 95  | X40        | 4150 |          | 157 | X102         | -2205 |      |

| 34       | F2S  | 1603  |       | 96  | X41        | 4048 |          | 158 | X103         | -2307 |      |

| 35       | F1S  | 1783  |       | 97  | X42        | 3945 |          | 159 | X104         | -2410 |      |

| 36       | DOFF | 1963  |       | 98  | X43        | 3843 |          | 160 | X105         | -2512 |      |

| 37       | Vdd  | 2143  |       | 99  | X44        | 3740 |          | 161 | X106         | -2615 |      |

| 38       | NC   | 2387  |       | 100 | X45        | 3637 |          | 162 | X107         | -2717 |      |

| 39       | NC   | 2564  |       | 101 | X46        | 3535 |          | 163 | X108         | -2820 |      |

| 40       | NC   | 2742  |       | 102 | X47        | 3432 |          | 164 | X109         | -2922 |      |

| 41       | NC   | 2920  |       | 103 | X48        | 3330 |          | 165 | X110         | -3025 |      |

| 42       | NC   | 3098  |       | 104 | X49        | 3227 |          | 166 | X111         | -3127 |      |

| 43       | NC   | 3275  |       | 105 | X50        | 3125 |          | 167 | X112         | -3230 |      |

| 43<br>44 | NC   | 3453  |       | 105 | X51        | 3022 |          | 168 | X112<br>X113 | -3332 |      |

| 45       | NC   | 3631  |       | 100 | X52        | 2920 |          | 169 | X113         | -3435 |      |

| 40       | NC   | 3809  |       | 107 | X53        | 2920 |          | 170 | X114<br>X115 | -3433 |      |

| 40<br>47 | NC   | 3986  |       | 108 | X54        | 2715 |          | 170 | X115         | -3640 |      |

| 47       | NC   | 4164  |       | 110 | X55        | 2612 |          | 171 | X110<br>X117 | -3640 |      |

|          |      |       |       |     |            |      |          |     |              |       |      |

| 49<br>50 | NC   | 4342  |       | 111 | X56        | 2510 |          | 173 | X118         | -3845 |      |

| 50       | V3   | 4722  |       | 112 | X57        | 2407 |          | 174 | X119         | -3947 |      |

| 51       | V2   | 4900  |       | 113 | X58        | 2305 |          | 175 | X120         | -4050 |      |

| 52       | Vc   | 5077  |       | 114 | X59        | 2202 |          | 176 | X121         | -4152 |      |

| 53       | -V2  | 5255  |       | 115 | X60        | 2100 |          | 177 | X122         | -4255 |      |

| 54       | -V3  | 5433  | 🖌     | 116 | X61        | 1997 |          | 178 | X123         | -4357 |      |

| 55       | EIO1 | 5629  |       | 117 | X62        | 1895 |          | 179 | X124         | -4460 |      |

| 56       | X1   | 6303  | -1009 | 118 | X63        | 1792 |          | 180 | X125         | -4562 |      |

| 57       | X2   |       | -903  | 119 | X64        | 1690 |          | 181 | X126         | -4655 |      |

| 58       | X3   |       | -797  | 120 | X65        | 1587 |          | 182 | X127         | -4767 |      |

| 59       | X4   |       | -690  | 121 | X66        | 1485 |          | 183 | X128         | -4870 |      |

| 60       | X5   |       | -584  | 122 | X67        | 1382 |          | 184 | X129         | -4972 |      |

| 61       | X6   |       | -478  | 123 | X68        | 1280 |          | 185 | X130         | -5075 |      |

| 62       | X7   | V V   | -371  | 124 | X69        | 1177 | <b>V</b> | 186 | X131         | -5177 | I V  |

Units: µm

|     |      |       |      |    |     |      |       |     |   |     |      |       | Units: µm |

|-----|------|-------|------|----|-----|------|-------|-----|---|-----|------|-------|-----------|

| Pin | Name | Х     | Y    |    | Pin | Name | Х     | Y   | [ | Pin | Name | Х     | Y         |

| 187 | X132 | -5280 | 1246 |    | 197 | X142 | -6303 | 903 |   | 207 | X152 | -6303 | -159      |

| 188 | X133 | -5382 |      |    | 198 | X143 |       | 797 |   | 208 | X153 |       | -265      |

| 189 | X134 | -5485 |      |    | 199 | X144 |       | 690 |   | 209 | X154 |       | -371      |

| 190 | X135 | -5587 |      | 2  | 200 | X145 |       | 584 |   | 210 | X155 |       | -478      |

| 191 | X136 | -5690 |      | 2  | 201 | X146 |       | 478 |   | 211 | X156 |       | -584      |

| 192 | X137 | -5792 |      | 2  | 202 | X147 |       | 372 |   | 212 | X157 |       | -690      |

| 193 | X138 | -5895 |      | 2  | 203 | X148 |       | 265 |   | 213 | X158 |       | -797      |

| 194 | X139 | -5997 |      | 12 | 204 | X149 |       | 159 |   | 214 | X159 |       | -903      |

| 195 | X140 | -6100 | ♥    | 1  | 205 | X150 |       | 53  |   | 215 | X160 | ♥     | -1009     |

| 196 | X141 | -6303 | 1009 | 2  | 206 | X151 |       | -53 |   |     |      |       |           |

# **Pin Functions**

Pin Functions Table

| Pin Name      | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # of<br>Pins |

|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| X1 to<br>X160 | 0   | Segment (column) output to drive the LC.<br>Output transition occurs on falling edge of LP.                                                                                                                                                                                                                                                                                                                                                                                                    | 160          |

| BSEL          | I   | Display data input bit number select input. "L": 4 bit input.<br>"H": 8 bit input.                                                                                                                                                                                                                                                                                                                                                                                                             | 1            |

| LSEL          | I   | 1/2 H operation select input. "L": Normal operation.<br>"H": 1/2 H operation.                                                                                                                                                                                                                                                                                                                                                                                                                  | 1            |

| D0 to D7      | I   | Display data input. When 4 bit input is used, D0 to D3 is used, and D4 to D7 can be left NC.                                                                                                                                                                                                                                                                                                                                                                                                   | 8            |

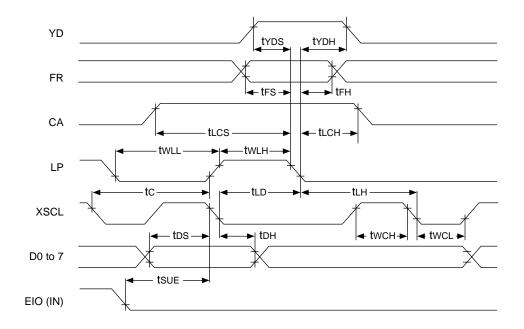

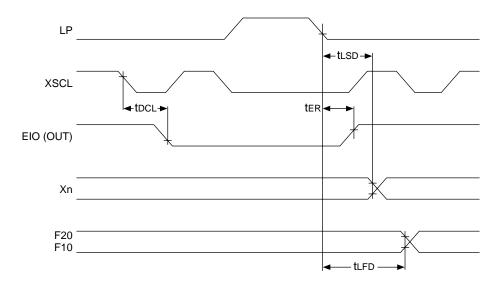

| XSCL          | I   | Display data shift clock input. Display data (D0 to D7) is read sequentially into the data register on the falling edge.                                                                                                                                                                                                                                                                                                                                                                       | 1            |

| LP            | I   | <ul> <li>Display data latch clock input</li> <li>* Accepts into the LCD driver the control signal from the LC driver selected by the MLS decoder, doing so at the falling edge, and outputs the LC driver output.</li> <li>* Writes the contents of the data registers to the frame memory 4 LP at a time for the specified column address.</li> <li>* Resets the enable control circuit.</li> <li>* When 1/2 operation is selected, inputs the LP with twice the normal frequency.</li> </ul> | 1            |

| EIO1<br>EIO2  | I/O | <ul> <li>Enable I/O</li> <li>* Is set to input or output depending on the SHL input level.</li> <li>* When output, the LP input is reset (in an "H" state), and when the 160 bit of display data has been read in, the signal automatically falls to L.</li> <li>* When connected in cascade, is connected to the next stage EIO input.</li> </ul>                                                                                                                                             | 1<br>1       |

| Pin Name                | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | # of<br>Pins |  |  |  |  |  |  |  |

|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| SHL                     |       | Shift direction select and EIO terminal I/O control input.<br><u>WHEN BSEL = "L" (i.e. 4-bit input):</u><br>When the display data has been input to terminals<br>(D3, D2, D1, D0) in the order (a, b, c, d) (e, f, g, h)<br>(w, x, y, z), the relationship between the data and the segment<br>is as shown in the table below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |              |  |  |  |  |  |  |  |