# SED1580

# Contents

| INTRODUCTION                    | 2-1  |

|---------------------------------|------|

| FEATURES                        | 2-1  |

| BLOCK DIAGRAM                   | 2-2  |

| PIN CONFIGURATION               | 2-3  |

| ELECTRICAL CHARACTERISTICS      | 2-15 |

| POWER SOURCE                    | 2-19 |

| EXAMPLE OF EXTERNAL CONNECTIONS | 2-20 |

# OVERVIEW

## Description

The SED1580 is a 160-output, 5-level segment (column) driver for MLS (Multi-Line Selection) driving, able to drive with both high contrast and high speed. It is used in conjunction with the SED1751. When paired with the SED1751 it can be connected to the SED1360 LCD controller.

Because the SED1580 stores display data in its internal display RAM and generates LC drive signals, display data transmission from the controller can be suspended except for when there are changes to the display, thereby enabling an ultra low power display system.

The SED1580 uses a slim package, facilitating the construction of thinner LCD panels, and the low-voltage operation of its logic power source makes it appropriate to a wide range of applications.

# FEATURES

- Number of simultaneous line selects: 4 Lines

- Drive duty ratio (MAX) 1/240 duty

- LCD driver outputs 160 outputs

- Internal display RAM  $160 \times 240$  bit

- Extremely low consumption current

- Power Source Voltages Logic System: 3.0 to 3.6V (Max)

LCD System: 6.0 to 7.2V (Max)

- High speed, low power data transmission possible through the 4-bit/8-bit switchable bus enable chain method

- Non-biased display off function

- Output shift direction pin select supported

- Slim chip shape

•

Shipment status:

In CHIP form ......SED1580D0B In TCP form .....SED1580T0A

This product is not designed for resistance to light or radiation

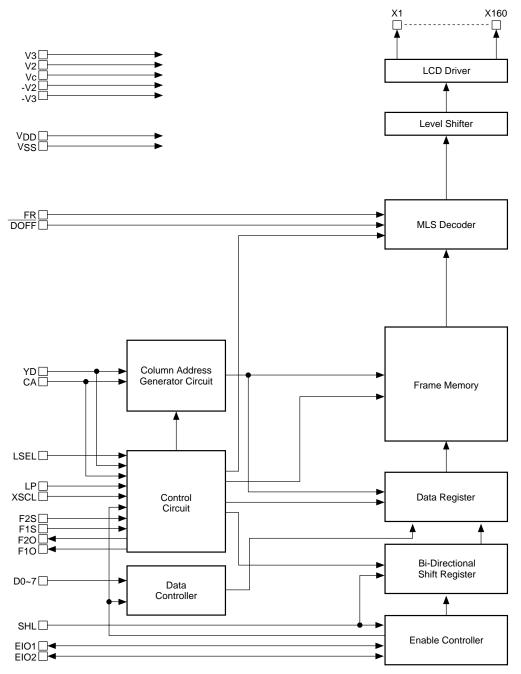

# **BLOCK DIAGRAM**

**Block Diagram**

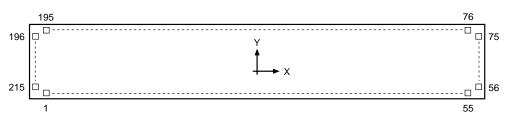

# **PIN CONFIGURATION**

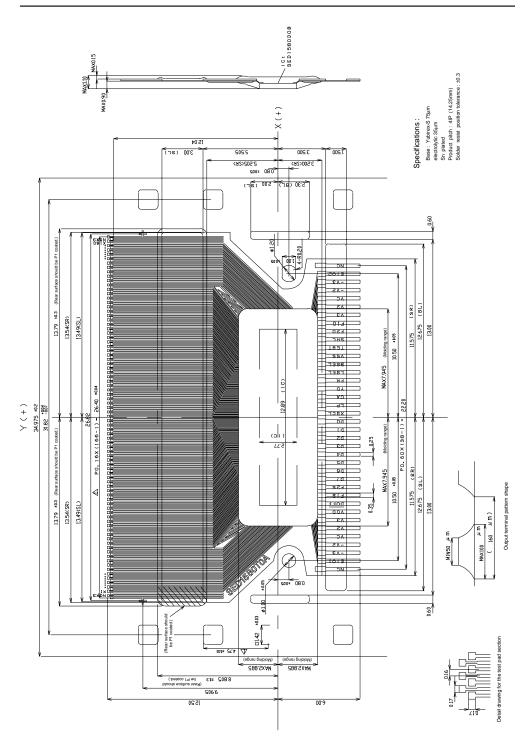

**Pad Layout**

Bump size (Unit: µm)

| Pad number                         |     |    |

|------------------------------------|-----|----|

| i ad number                        | Х   | Y  |

| 56 to 215                          | 67  | 63 |

| 1, 7 to 16, 18 to 36, 38 to 49, 55 | 74  | 74 |

| 2 to 6, 17, 37, 50 to 54           | 110 | 74 |

| 22                                 | 110 | 75 |

Bump specifications (reference values)

| Items                      |         | Specifications |         |

|----------------------------|---------|----------------|---------|

| nems                       | MIN     | TYP            | MAX     |

| Bump size specifications   | -4 μm   | Bump size      | +4 µm   |

| Bump height specifications | –5.5 μm | 22.5 μm        | +5.5 μm |

| Bump strength              | 30g     |                |         |

## **Pin Coordinates**

#### SED1580 Bump Center Coordinates

| Pin      | Name | Х     | Y     | Pin | Name       | Х    | Y        | Pin | Name         | X     | Y    |

|----------|------|-------|-------|-----|------------|------|----------|-----|--------------|-------|------|

| 1        | EIO2 | -5378 | -1240 | 63  | X8         | 6303 | -265     | 125 | X70          | 1075  | 1246 |

| 2        | -V3  | -5222 |       | 64  | X9         |      | -159     | 126 | X71          | 972   |      |

| 3        | -V2  | -5044 |       | 65  | X10        |      | -53      | 127 | X72          | 870   |      |

| 4        | VC   | -4866 |       | 66  | X11        |      | 53       | 128 | X73          | 767   |      |

| 5        | V2   | -4688 |       | 67  | X12        |      | 159      | 129 | X74          | 665   |      |

| 6        | V3   | -4510 |       | 68  | X13        |      | 265      | 130 | X75          | 562   |      |

| 7        | NC   | -4322 |       | 69  | X14        |      | 372      | 131 | X76          | 460   |      |

| 8        | NC   | -4144 |       | 70  | X15        |      | 478      | 132 | X77          | 357   |      |

| 9        | NC   | -3966 |       | 71  | X16        |      | 584      | 133 | X78          | 255   |      |

| 10       | NC   | -3789 |       | 72  | X17        |      | 690      | 134 | X79          | 152   |      |

| 11       | NC   | -3611 |       | 73  | X18        |      | 797      | 135 | X80          | 50    |      |

| 12       | F10  | -3449 |       | 74  | X19        |      | 903      | 136 | X81          | -52   |      |

| 13       | F20  | -2915 |       | 75  | X20        | ♥    | 1009     | 137 | X82          | -154  |      |

| 14       | NC   | -2266 |       | 76  | X20        | 6098 | 1246     | 138 | X83          | -257  |      |

| 15       | SHL  | -2086 |       | 77  | X22        | 5995 | 1240     | 139 | X84          | -359  |      |

| 16       | TEST | -1906 |       | 78  | X23        | 5893 |          | 140 | X85          | -462  |      |

| 17       | Vss  | -1726 |       | 79  | X24        | 5790 |          | 140 | X86          | -564  |      |

|          | BSEL | -1546 |       | 80  | X24<br>X25 | 5688 |          | 141 | X87          | -567  |      |

| 18       | LSEL |       |       |     |            |      |          |     | X88          |       |      |

| 19<br>20 |      | -1366 |       | 81  | X26        | 5585 |          | 143 |              | -769  |      |

| 20       | FR   | -1186 |       | 82  | X27        | 5483 |          | 144 | X89          | -872  |      |

| 21       | YD   | -1006 |       | 83  | X28        | 5380 |          | 145 | X90          | -974  |      |

| 22       | NC   | -826  |       | 84  | X29        | 5278 |          | 146 | X91          | -1077 |      |

| 23       | CA   | -546  |       | 85  | X30        | 5175 |          | 147 | X92          | -1179 |      |

| 24       | LP   | -466  |       | 86  | X31        | 5073 |          | 148 | X93          | -1282 |      |

| 25       | XSCL | -286  |       | 87  | X32        | 4970 |          | 149 | X94          | -1385 |      |

| 26       | D0   | 163   |       | 88  | X33        | 4868 |          | 150 | X95          | -1487 |      |

| 27       | D1   | 343   |       | 89  | X34        | 4765 |          | 151 | X96          | -1590 |      |

| 28       | D2   | 523   |       | 90  | X35        | 4663 |          | 152 | X97          | -1692 |      |

| 29       | D3   | 703   |       | 91  | X36        | 4560 |          | 153 | X98          | -1795 |      |

| 30       | D4   | 883   |       | 92  | X37        | 4458 |          | 154 | X99          | -1897 |      |

| 31       | D5   | 1063  |       | 93  | X38        | 4355 |          | 155 | X100         | -2000 |      |

| 32       | D6   | 1243  |       | 94  | X39        | 4253 |          | 156 | X101         | -2102 |      |

| 33       | D7   | 1423  |       | 95  | X40        | 4150 |          | 157 | X102         | -2205 |      |

| 34       | F2S  | 1603  |       | 96  | X41        | 4048 |          | 158 | X103         | -2307 |      |

| 35       | F1S  | 1783  |       | 97  | X42        | 3945 |          | 159 | X104         | -2410 |      |

| 36       | DOFF | 1963  |       | 98  | X43        | 3843 |          | 160 | X105         | -2512 |      |

| 37       | Vdd  | 2143  |       | 99  | X44        | 3740 |          | 161 | X106         | -2615 |      |

| 38       | NC   | 2387  |       | 100 | X45        | 3637 |          | 162 | X107         | -2717 |      |

| 39       | NC   | 2564  |       | 101 | X46        | 3535 |          | 163 | X108         | -2820 |      |

| 40       | NC   | 2742  |       | 102 | X47        | 3432 |          | 164 | X109         | -2922 |      |

| 41       | NC   | 2920  |       | 103 | X48        | 3330 |          | 165 | X110         | -3025 |      |

| 42       | NC   | 3098  |       | 104 | X49        | 3227 |          | 166 | X111         | -3127 |      |

| 43       | NC   | 3275  |       | 105 | X50        | 3125 |          | 167 | X112         | -3230 |      |

| 43<br>44 | NC   | 3453  |       | 105 | X51        | 3022 |          | 168 | X112<br>X113 | -3332 |      |

| 45       | NC   | 3631  |       | 100 | X52        | 2920 |          | 169 | X113         | -3435 |      |

| 40       | NC   | 3809  |       | 107 | X53        | 2920 |          | 170 | X114<br>X115 | -3433 |      |

| 40<br>47 | NC   | 3986  |       | 108 | X54        | 2715 |          | 170 | X115         | -3640 |      |

| 47       | NC   | 4164  |       | 110 | X55        | 2612 |          | 171 | X110<br>X117 | -3640 |      |

|          |      |       |       |     |            |      |          |     |              |       |      |

| 49<br>50 | NC   | 4342  |       | 111 | X56        | 2510 |          | 173 | X118         | -3845 |      |

| 50       | V3   | 4722  |       | 112 | X57        | 2407 |          | 174 | X119         | -3947 |      |

| 51       | V2   | 4900  |       | 113 | X58        | 2305 |          | 175 | X120         | -4050 |      |

| 52       | Vc   | 5077  |       | 114 | X59        | 2202 |          | 176 | X121         | -4152 |      |

| 53       | -V2  | 5255  |       | 115 | X60        | 2100 |          | 177 | X122         | -4255 |      |

| 54       | -V3  | 5433  | 🖌     | 116 | X61        | 1997 |          | 178 | X123         | -4357 |      |

| 55       | EIO1 | 5629  |       | 117 | X62        | 1895 |          | 179 | X124         | -4460 |      |

| 56       | X1   | 6303  | -1009 | 118 | X63        | 1792 |          | 180 | X125         | -4562 |      |

| 57       | X2   |       | -903  | 119 | X64        | 1690 |          | 181 | X126         | -4655 |      |

| 58       | X3   |       | -797  | 120 | X65        | 1587 |          | 182 | X127         | -4767 |      |

| 59       | X4   |       | -690  | 121 | X66        | 1485 |          | 183 | X128         | -4870 |      |

| 60       | X5   |       | -584  | 122 | X67        | 1382 |          | 184 | X129         | -4972 |      |

| 61       | X6   |       | -478  | 123 | X68        | 1280 |          | 185 | X130         | -5075 |      |

| 62       | X7   | V V   | -371  | 124 | X69        | 1177 | <b>V</b> | 186 | X131         | -5177 | I V  |

Units: µm

|     |      |       |      |    |     |      |       |     |   |     |      |       | Units: µm |

|-----|------|-------|------|----|-----|------|-------|-----|---|-----|------|-------|-----------|

| Pin | Name | Х     | Y    |    | Pin | Name | Х     | Y   | [ | Pin | Name | Х     | Y         |

| 187 | X132 | -5280 | 1246 |    | 197 | X142 | -6303 | 903 |   | 207 | X152 | -6303 | -159      |

| 188 | X133 | -5382 |      |    | 198 | X143 |       | 797 |   | 208 | X153 |       | -265      |

| 189 | X134 | -5485 |      |    | 199 | X144 |       | 690 |   | 209 | X154 |       | -371      |

| 190 | X135 | -5587 |      | 2  | 200 | X145 |       | 584 |   | 210 | X155 |       | -478      |

| 191 | X136 | -5690 |      | 2  | 201 | X146 |       | 478 |   | 211 | X156 |       | -584      |

| 192 | X137 | -5792 |      | 2  | 202 | X147 |       | 372 |   | 212 | X157 |       | -690      |

| 193 | X138 | -5895 |      | 2  | 203 | X148 |       | 265 |   | 213 | X158 |       | -797      |

| 194 | X139 | -5997 |      | 12 | 204 | X149 |       | 159 |   | 214 | X159 |       | -903      |

| 195 | X140 | -6100 | ♥    | 1  | 205 | X150 |       | 53  |   | 215 | X160 | ♥     | -1009     |

| 196 | X141 | -6303 | 1009 | 2  | 206 | X151 |       | -53 |   |     |      |       |           |

# **Pin Functions**

Pin Functions Table

| Pin Name      | I/O | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # of<br>Pins |

|---------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| X1 to<br>X160 | 0   | Segment (column) output to drive the LC.<br>Output transition occurs on falling edge of LP.                                                                                                                                                                                                                                                                                                                                                                                                    | 160          |

| BSEL          | I   | Display data input bit number select input. "L": 4 bit input.<br>"H": 8 bit input.                                                                                                                                                                                                                                                                                                                                                                                                             | 1            |

| LSEL          | I   | 1/2 H operation select input. "L": Normal operation.<br>"H": 1/2 H operation.                                                                                                                                                                                                                                                                                                                                                                                                                  | 1            |

| D0 to D7      | I   | Display data input. When 4 bit input is used, D0 to D3 is used, and D4 to D7 can be left NC.                                                                                                                                                                                                                                                                                                                                                                                                   | 8            |

| XSCL          | I   | Display data shift clock input. Display data (D0 to D7) is read sequentially into the data register on the falling edge.                                                                                                                                                                                                                                                                                                                                                                       | 1            |

| LP            | I   | <ul> <li>Display data latch clock input</li> <li>* Accepts into the LCD driver the control signal from the LC driver selected by the MLS decoder, doing so at the falling edge, and outputs the LC driver output.</li> <li>* Writes the contents of the data registers to the frame memory 4 LP at a time for the specified column address.</li> <li>* Resets the enable control circuit.</li> <li>* When 1/2 operation is selected, inputs the LP with twice the normal frequency.</li> </ul> | 1            |

| EIO1<br>EIO2  | I/O | <ul> <li>Enable I/O</li> <li>* Is set to input or output depending on the SHL input level.</li> <li>* When output, the LP input is reset (in an "H" state), and when the 160 bit of display data has been read in, the signal automatically falls to L.</li> <li>* When connected in cascade, is connected to the next stage EIO input.</li> </ul>                                                                                                                                             | 1<br>1       |

| Pin Name                | I/O   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # of<br>Pins |  |  |  |  |  |  |  |

|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|--|

| SHL                     |       | Shift direction select and EIO terminal I/O control input.<br><u>WHEN BSEL = "L" (i.e. 4-bit input):</u><br>When the display data has been input to terminals<br>(D3, D2, D1, D0) in the order (a, b, c, d) (e, f, g, h)<br>(w, x, y, z), the relationship between the data and the segment<br>is as shown in the table below:                                                                                                                                                                                                                                                                                                                 |              |  |  |  |  |  |  |  |

|                         |       | SHL         EIO           160         159         158         157         156         155         154         15          8         7         6         5         4         3         2         1         1         2           L         a         b         c         d         e         f         g         h          s         t         u         v         w         x         y         z         Output         Input           H         z         y         x         w         u         t         s          h         g         f         e         d         c         b         a         Input         Output                | 1            |  |  |  |  |  |  |  |

|                         |       | <u>WHEN BSEL = "H" (i.e., 8-bit input):</u><br>When the display data has been input to terminals<br>(D7, D6, D5, D4, D3, D2, D1, D0) in the order<br>(a, b, c, d, e, f, g, h) (s, t, u, v, w, x, y, z), the relationship<br>between the data and the segment is as shown in the table<br>below:                                                                                                                                                                                                                                                                                                                                                |              |  |  |  |  |  |  |  |

|                         |       | EIO           SHL         EIO           160         159         158         157         156         155         154         153          8         7         6         5         4         3         2         1         1         2           L         a         b         c         d         e         f         g         h          s         t         u         v         w         x         y         z         Output         Input           H         z         y         x         w         u         t         s          h         g         f         e         d         c         b         a         Input         Output |              |  |  |  |  |  |  |  |

| DOFF                    | I     | Forced blank input.<br>When at "L" level, segment output is forced to Vc. The display<br>RAM data is maintained.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1            |  |  |  |  |  |  |  |

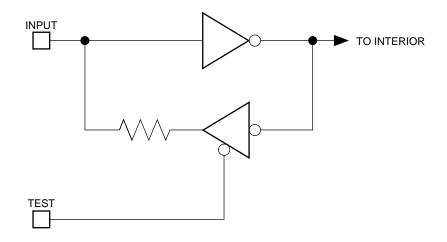

| FR                      | I     | LC drive output AC signal input. With terminator (*1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1            |  |  |  |  |  |  |  |

| YD                      | I     | Frame running start input<br>* Resets the column address for writing or reading.<br>* The number of running lines for writing (column address<br>number) relating to frame memory is determined based on the<br>number of LP pulses input during a single YD cycle.                                                                                                                                                                                                                                                                                                                                                                            | 1            |  |  |  |  |  |  |  |

| СА                      | I     | Field delimiter signal input. With terminator (*1).<br>This signal is input at the start of each new field, and is output<br>by the SED1751.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1            |  |  |  |  |  |  |  |

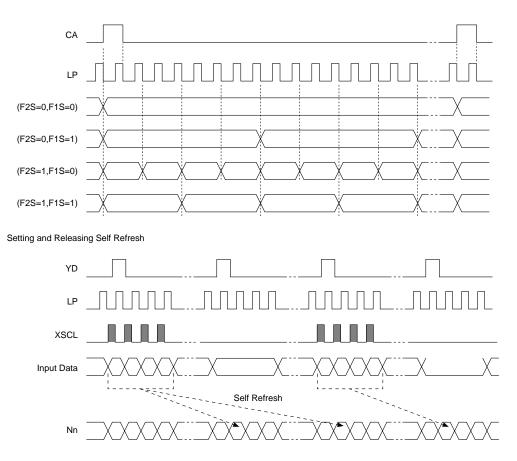

| F1S<br>F2S              | I     | Drive pattern cutover gap set input<br>(F2S, F1S) = $(0,0)$ , $(0,1)$ , $(1,0)$ , $(1,1)$<br>Cutover gap Field, 8H, 2H, 4H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1<br>1       |  |  |  |  |  |  |  |

| F1O<br>F2O              | 0     | Driver pattern select output for the Y driver. Connects to the common (row) driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |  |  |  |  |  |  |  |

| TEST                    | I     | Test input. Normally fixed at "L".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1            |  |  |  |  |  |  |  |

| Vdd, Vss                | Power | Power supply for logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1<br>each    |  |  |  |  |  |  |  |

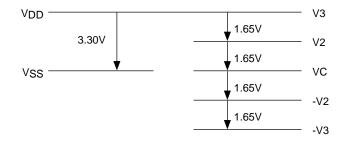

| V3, V2, VC,<br>-V2, -V3 | Power | Power supply for LC driver. $V_3 > V_2 > V_C > -V_2 > -V_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5<br>each    |  |  |  |  |  |  |  |

Note: \*1 Regarding the terminator

#### FUNCTIONS The Functional Blocks Enable Control

When the enable signal is in a disable state (EIO = "H"), the internal clock signal and data bus are fixed at "L", placing the chip in power save mode.

When multiple segment drivers are used, the EIO terminals of the various drivers are cascade connected and the EIO terminal of the first driver is connected to "Vss".

The enable control circuit automatically senses when 160 bits worth of data have been received, and automatically sends the enable signal, thus eliminating the need for a control signal from the control LSI.

#### **Bi-directional Shift Register**

This sends the control signal for writing the display data DO - D7 to the data register. The order in which the display data is latched into the data register by the SHL input is returned (SIC? Reversed?).

#### **Data Register**

This is a 160 dot register which controls writing to the display RAM. It has 4 lines. At each falling edge of the LP signal it accepts display data from one line, and writes to the frame memory after it has stored 4 lines of data.

#### Frame Memory

This is static RAM (with peripheral circuits) that stores LC display data. It has a capacity of 160 segments by 240 lines.

#### **MLS Decoder**

This outputs the drive control signals necessary for the 4 MLS driving. The control signal is set by field information provided by the four lines of display data, FR, DOFF, and the control circuit.

#### LCD Driver

The LCD driver outputs the LC drive voltage. The driver voltage is selected by the control signal from the 5 levels V3, V2, VC, -V2 and -V3, determined by the MLS decoder.

#### **Column Address Generating Circuit**

When writing to or reading from frame memory, this outputs the column address corresponding to the location of the RAM in frame memory.

#### Level Shifter

This is a level interface circuit used to convert signal levels when signals are propagated from low-voltage parts to high-voltage parts.

#### **Data Control**

This accepts display data input when enabled, and sends it to the data register.

#### **Control Circuit**

This determines the self refresh rate, enables the data register to write to the display RAM, controls the output of the column address generator, and performs field control on the MLS decoder.

#### The Self Refresh Function

#### Setting the Self Refresh Mode

"Self refresh mode" refers to a situation where the transmission of display data from the display controller to the SED1580 is suspended when the content of the display does not change, and where the SED1580 automatically senses this and enters a power down display mode.

To place the SED1580 in the self refresh mode maintain the shift clock XSCL at the "L" level during four horizontal display periods (4x the LP signal period) after the completion of the input of the display data of an n + 3 line.

When the XSCL is suspended, the power is reduced, so display data inputs D0 - D7 are suspended, as is transmission from the display controller, being set to "H" or "L". At this time the display controller must send LP, YD, or FR signals periodically to the SED1580 as it does when data is being sent. The SED1580 receives these signals, periodically reads display data from its internal RAM, and refreshes the display. The display off function is operational even when in the self refresh mode.

#### Getting Out of the Self Refresh Mode

In order to get out of the self refresh mode, the display controller inputs the shift clock XSCL to the SED1580 for four or more horizontal display periods with the timing of the data transmission from the falling edge of the LP signal at the time of an n + 3 line. With the falling edge of the LP signal after the fourth horizontal period after getting out of this mode, the display data transmitted during the four horizontal display intervals is written to frame memory.

When SED1580s are cascade connected, if the number of XSCL clocks input does not correspond to the cascade connections, then not all of the SED1580s will be released from self refresh mode.

| n lines     | 1, 5, 9,233, 237 (1 + multiples of 4)  |

|-------------|----------------------------------------|

| n + 1 lines | 2, 6, 10,234, 238 (2 + multiples of 4) |

| n + 2 lines | 3, 7, 11,235, 239 (3 + multiples of 4) |

| n + 3 lines | 4, 8, 12,236, 240 (Multiples of 4)     |

Note: When the number of lines is 240:

#### The Relationship Between Drive Output Voltages and Display Data

F20, F10, and the common drive voltage have the following relationships:

| FR         |     | l          | -   |     | н   |     |     |     |  |  |  |  |

|------------|-----|------------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| F10<br>F20 | 1   | 0 1<br>1 0 |     | 0   | 1   | 0   | 1   | 0   |  |  |  |  |

| n line     | V1  | V1         | -V1 | V1  | -V1 | -V1 | V1  | -V1 |  |  |  |  |

| n + 1 line | -V1 | V1         | V1  | V1  | V1  | -V1 | -V1 | -V1 |  |  |  |  |

| n + 2 line | V1  | -V1        | V1  | V1  | -V1 | V1  | -V1 | -V1 |  |  |  |  |

| n + 3 line | V1  | V1         | V1  | -V1 | -V1 | -V1 | -V1 | V1  |  |  |  |  |

Note: Voltage relationships: V1 > VC > -V1 (VC is the middle voltage level)

The transitions in (F2O, F1O) within each field when the drive pattern changes:

| First field  | In the order $(1,1) \rightarrow (1,0) \rightarrow (0,1) \rightarrow (0,0) \rightarrow (1,1) \rightarrow (1,0) \rightarrow (0,1) \rightarrow (0,0)$ |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Second field | In the order $(1,0) \rightarrow (0,1) \rightarrow (0,0) \rightarrow (1,1) \rightarrow (1,0) \rightarrow (0,1) \rightarrow (0,0) \rightarrow (1,1)$ |

| Third field  | In the order $(0,1) \rightarrow (0,0) \rightarrow (1,1) \rightarrow (1,0) \rightarrow (0,1) \rightarrow (0,0) \rightarrow (1,1) \rightarrow (1,0)$ |

| Fourth field | In the order $(0,0) \rightarrow (1,1) \rightarrow (1,0) \rightarrow (0,1) \rightarrow (0,0) \rightarrow (1,1) \rightarrow (1,0) \rightarrow (0,1)$ |

This is determined by the values of the inputs (F2S, F1S) during the changeover interval. The relationship between F2S and F1S and the changeover interval is as follows:

When the changeover interval is selected for each field, the value stored in the field is the first value shown in the shown in the (F2O, F1O) change table above (the value on the left).

| F2S | F1S | Changeover Interval |

|-----|-----|---------------------|

| 0   | 0   | Field               |

| 0   | 1   | 8-line interval     |

| 1   | 0   | 2-line interval     |

| 1   | 1   | 4-line interval     |

The relationship between the display data, the LC AC signal FR, and the segment output voltage is as shown below. The output voltage changes in conjunction with the F20, F10 values that determine the common drive voltage.

Display data: 0 = not lit, 1 = lit

| When FR = | "L"                   |    |    |    |     |    |     |     |     |    |     |     |     |     |     |     |     |

|-----------|-----------------------|----|----|----|-----|----|-----|-----|-----|----|-----|-----|-----|-----|-----|-----|-----|

|           | n line                | 0  | 0  | 0  | 0   | 0  | 0   | 0   | 0   | 1  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Display   | n + 1 line            | 0  | 0  | 0  | 0   | 1  | 1   | 1   | 1   | 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   |

| Line      | n + 2 line            | 0  | 0  | 1  | 1   | 0  | 0   | 1   | 1   | 0  | 0   | 1   | 1   | 0   | 0   | 1   | 1   |

|           | n + 3 line            | 0  | 1  | 0  | 1   | 0  | 1   | 0   | 1   | 0  | 1   | 0   | 1   | 0   | 1   | 0   | 1   |

|           | (F2O, F1O)<br>= (1,1) | V2 | Vc | Vc | –V2 | V3 | V2  | V2  | Vc  | Vc | -V2 | -V2 | -V3 | V2  | Vc  | Vc  | –V2 |

| Drive     | (F2O, F1O)<br>= (1,0) | V2 | Vc | V3 | V2  | Vc | -V2 | V2  | Vc  | Vc | -V2 | V2  | Vc  | -V2 | -V3 | Vc  | –V2 |

| Voltage   | (F2O, F1O)<br>= (0,1) | V2 | Vc | Vc | -V2 | Vc | -V2 | -V2 | -V3 | V3 | V2  | V2  | Vc  | V2  | Vc  | Vc  | –V2 |

|           | (F2O, F1O)<br>= (0,0) | V2 | Vз | Vc | V2  | Vc | V2  | -V2 | Vc  | Vc | V2  | -V2 | Vc  | -V2 | Vc  | -V3 | -V2 |

When FR = "H"

|         | n line                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1   | 1   | 1   | 1  | 1   | 1  | 1  | 1  |

|---------|-----------------------|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|----|-----|----|----|----|

| Display | n + 1 line            | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 0   | 0   | 0   | 0  | 1   | 1  | 1  | 1  |

| Line    | n + 2 line            | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 1  | 0   | 0   | 1   | 1  | 0   | 0  | 1  | 1  |

|         | n + 3 line            | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1  | 0   | 1   | 0   | 1  | 0   | 1  | 0  | 1  |

|         | (F2O, F1O)<br>= (1,1) | -V2 | Vc  | Vc  | V2  | -V3 | -V2 | -V2 | Vc | Vc  | V2  | V2  | V3 | -V2 | Vc | Vc | V2 |

| Drive   | (F2O, F1O)<br>= (1,0) | –V2 | Vc  | –V3 | -V2 | Vc  | V2  | -V2 | Vc | Vc  | V2  | -V2 | Vc | V2  | V3 | Vc | V2 |

| Voltage | (F2O, F1O)<br>= (0,1) | -V2 | Vc  | Vc  | V2  | Vc  | V2  | V2  | V3 | -V3 | -V2 | -V2 | Vc | -V2 | Vc | Vc | V2 |

|         | (F2O, F1O)<br>= (0,0) | -V2 | -V3 | Vc  | -V2 | Vc  | -V2 | V2  | Vc | Vc  | -V2 | V2  | Vc | V2  | Vc | V3 | V2 |

When  $\overline{\text{DOFF}}$  = "L", all drive outputs are tied to the Vc level.

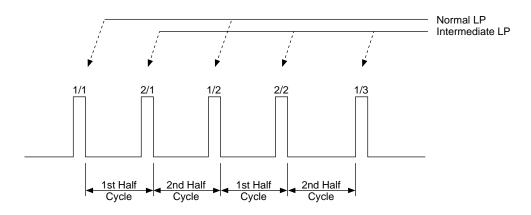

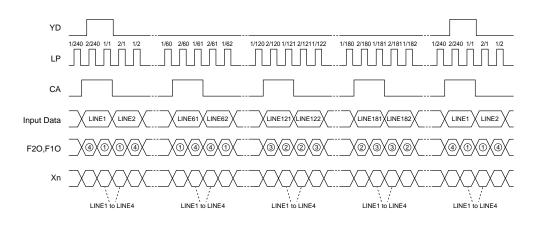

# LC Drive Output Voltages During 1/2 H Operation

When LSEL is set to "H" and twice the normal frequency is applied to the LP input terminal, then the chip functions in 1/2 mode. Each time LP is input the field data changes, thus the output changes at the center point of the 1H interval. However, the input of display data to the D1580, writing of display data to the frame memory, and read in display data from the frame memory is the same as in the normal drive.

The Y driver output changes according to the field data output by the X driver with each LP input, causing a transition at the center point of the 1H interval; however, the transition of the drive line occurs each 1H, just as in the normal drive.

During 1/2 H operation, the changes of the F20, F10 in each field are as shown in the table below. In this table the statuses of the F20 and F10 are represented as given below:

| (F2O, F1O) = (1,1) | (1) |

|--------------------|-----|

| (F2O, F1O) = (1,0) | (2) |

| (F2O, F1O) = (0,1) | (3) |

| (F2O, F1O) = (0,0) | (4) |

|          | First Half<br>Cycle | Second Half<br>Cycle | First Half<br>Cycle | Second Half<br>Cycle |                     |

|----------|---------------------|----------------------|---------------------|----------------------|---------------------|

| Field #1 | (4)                 | (1)                  | (1)                 | (4)                  |                     |

| Field #2 | (1)                 | (4)                  | (4)                 | (1)                  | This pattern is     |

| Field #3 | (3)                 | (2)                  | (2)                 | (3)                  | repeated hereafter. |

| Field #4 | (2)                 | (3)                  | (3)                 | (2)                  |                     |

During 1/2H operation, the values of F2S and F1S are ignored.

The segment output voltage during 1/2 H operation also follows the display data of 4.3 and the diagram showing the relationship between the LC AC signal FR and the segment output voltage. In the signal B/ A that indicates the number of the LP, the "A" in the figure indicates LP during a normal drive, and "B" differentiates between the normal LP and the intermediate LP (where B = 1 is normal and B = 2 is intermediate).

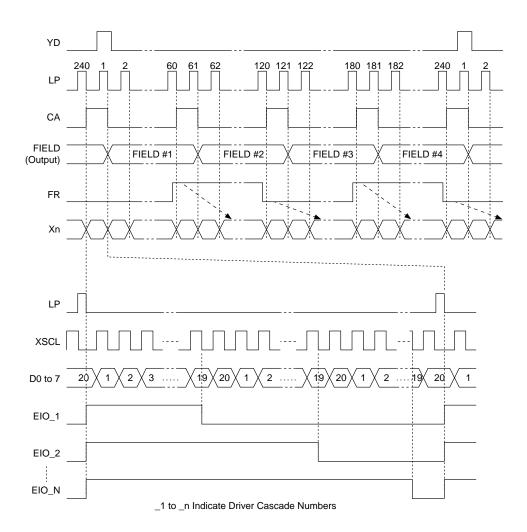

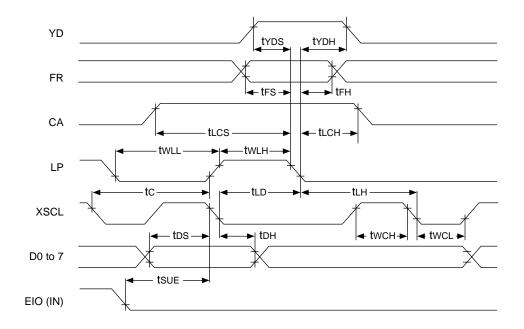

Timing diagram (assuming 1/240 duty)

(This diagram provided only as a reference.) **Normal Drive Timing**

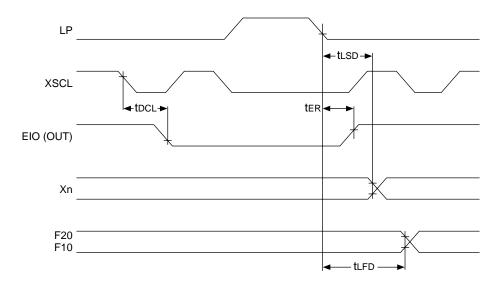

# F2O, F1O Change Timing

#### 1/2 H Drive Timing

# **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

| Parameter             | Symbol | Rating               | Units |

|-----------------------|--------|----------------------|-------|

| Power voltage (1)     | Vss    | -7.0 to +0.3         | V     |

| Power voltage (2)     | -V3    | -8.0 to +0.3         | V     |

| Input voltage         | VI     | Vss -0.3 to VDD +0.3 | V     |

| Output voltage        | Vo     | Vss -0.3 to VDD +0.3 | V     |

| EIO output current    | IO1    | 20                   | mA    |

| Operating temperature | Topr   | -20 to +85           | °C    |

| Storage temperature 1 | Tstg1  | -65 to +150          | °C    |

| Storage temperature 2 | Tstg2  | -55 to +100          | °C    |

Note 1: The voltages are all relative to VDD = 0V.

Storage temperature 1 is the recommendation for the chip itself or for the chip and a plastic package, and storage temperature 2 is the recommendation for the chip mounted on TCP. Ensure that the relationship between V3, V2, VC, -V2 and -V3 is always as follows: Note 2:

Note 3:  $V_{DD} \ge V_3 > V_2 > V_C > -\hat{V_2} > -V_3$

# **DC Characteristics**

| Unless otherwise specified, VDD = V3 = 0V, VSS =   |                                                                                                    |              |                                                                                                                                                                                                                                                                       |                           |                             | 3.3V ± 0.     | 3V, Ta        | = -20 to  | 85°C  |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------------|---------------|---------------|-----------|-------|

| Parame                                             | ter                                                                                                | Symbol       | Conditions                                                                                                                                                                                                                                                            |                           | Applicable terminals        | Min           | Тур           | Max       | Units |

| Power voltage                                      | e (1)                                                                                              | Vss          |                                                                                                                                                                                                                                                                       |                           | Vss                         | -3.6          | -3.3          | -3.0      | V     |

| Power voltage                                      | voltage (2) -V <sub>3</sub> Vss = -3.0V to -3.6V                                                   |              | -V3                                                                                                                                                                                                                                                                   | -7.2                      | -6.4                        | -6.0          | V             |           |       |

| Power voltage                                      | 9 (3)                                                                                              | -V2          | Vss = -3.0V to -3.6V                                                                                                                                                                                                                                                  | /                         | -V2                         |               | (–V3)*<br>3/4 |           | V     |

| Power voltage                                      | e (4)                                                                                              | Vc           | Vss = -3.0V to -3.6V                                                                                                                                                                                                                                                  | /                         | Vc                          |               | (–V3)*<br>2/4 |           | V     |

| Power voltage                                      | e (5)                                                                                              | V2           | Vss = -3.0V to -3.6V                                                                                                                                                                                                                                                  | V2                        |                             | (–V3)*<br>1/4 |               | V         |       |

| High-level inp                                     | ut voltage                                                                                         | Vін          | Vss =                                                                                                                                                                                                                                                                 | EIO1, EIO2<br>LSEL, FR, Y | , SHL, BSEL,<br>/D, CA, LP, | 0.2* Vss      |               |           | V     |

| Low-level inpu                                     | it voltage                                                                                         | VIL          | -3.3V to -3.6V                                                                                                                                                                                                                                                        | XSCL, D0 to<br>F2S, DOFF  |                             |               |               | 0.8* Vss  | V     |

| High-level out voltage                             | put                                                                                                | Vон          | Vss =                                                                                                                                                                                                                                                                 | Іон =<br>–0.6mA           | EIO1, EIO2                  | Vdd - 0.4     |               |           | V     |

| Low-level outp<br>voltage                          | out                                                                                                | Vol          | -3.3V to -3.6V                                                                                                                                                                                                                                                        | lo∟ =<br>0.6mA            | F10, F20                    |               |               | Vss + 0.4 | V     |

| Input leakage                                      | current                                                                                            | L            | $V_{SS} \leq V_{IN} \leq V_{DD} \qquad \begin{array}{c} SHL, BSEL, LS \\ YD, CA, LP, X \\ D0 \text{ to } D7, F1S \\ \overline{DOFF} \end{array}$                                                                                                                      |                           | , XSCL,                     |               |               | 5.0       | μΑ    |

| I/O leakage cu                                     | urrent                                                                                             | Ili/o        | $Vss \leq Vin \leq Vdd$                                                                                                                                                                                                                                               | EIO1, EIO2                |                             |               |               | 5.0       | μΑ    |

| Static current                                     | Static current (1) Issq                                                                            |              | VIN = VDD or VSS VSS                                                                                                                                                                                                                                                  |                           |                             |               |               | 10        | μΑ    |

| Static current                                     | (2)                                                                                                | —I зт        | -V3 = -6.6V                                                                                                                                                                                                                                                           |                           |                             |               | 5             | μA        |       |

| Output resista                                     | nce                                                                                                | Rseg         | $      \Delta VON = 0.5V, VSS = -       V_3 = V_{DD} = 0V, V_2 = -       V_C = -3.30V, -V_2 = -       V_3 = 6.60V                                  $                                                                                                                  | –1.65V,                   | X1 to X160                  |               | 0.8           | 1.5       | KΩ    |

| Average<br>operating<br>consumption<br>current (1) | Data<br>Transfer<br>Mode                                                                           | Isst         | $\begin{array}{l} Vss = -3.30V, V_3 = Vdd = 0V, \\ V_2 = -1.65V, V_c = -3.30V \\ -V_2 = -4.95V, -V_3 = -6.60V \\ V_1N = Vdd or Vss, fxscL = 480 kHz, \\ f_{LP} = 12kHz, f_{FR} = 30Hz, \\ Input Data: checker pattern, \\ 8-bit, 320 \times 200, no load \end{array}$ |                           | Vss                         |               | 70            | 100       | μΑ    |

|                                                    | Self<br>Refresh<br>Mode                                                                            | Isss         | XSCL = Vss Other parameters are the same as for Iss⊤                                                                                                                                                                                                                  |                           |                             |               | 50            | 70        | μΑ    |

|                                                    | verage operating<br>onsumption current (2) -I <sub>3T</sub> Parameters are the same as for<br>Isst |              | -V3                                                                                                                                                                                                                                                                   |                           | 10                          | 20            | μΑ            |           |       |

|                                                    |                                                                                                    | Freq = 1 MHz |                                                                                                                                                                                                                                                                       | , XSCL,                   |                             |               | 8             | pF        |       |

| I/O terminal<br>capacitance                        |                                                                                                    | CI/O         | Ta = 25°C<br>Chip alone                                                                                                                                                                                                                                               | EIO1, EIO2                |                             |               |               | 15        | pF    |

| Output terminal                                    |                                                                                                    | со           |                                                                                                                                                                                                                                                                       | F1O, F2O                  |                             |               |               | 7         | pF    |

Liplose otherwise or contribute 1/2 = 0/1/2 and 1/2 = -3/2/1 = 0.3/1 = -20 to  $85^{\circ}$

# AC Characteristics

**Input Timing Characteristics**

| Parameter                            | Symbol       | Conditions | Min  | Max | Units |

|--------------------------------------|--------------|------------|------|-----|-------|

| XSCL period                          | tc           |            | 150  |     | ns    |

| XSCL high level pulse width          | twcн         |            | 20   |     | ns    |

| XSCL low level pulse width           | twcL         |            | 20   |     | ns    |

| Data setup time                      | tos          |            | 10   |     | ns    |

| Data hold time                       | tон          |            | 10   |     | ns    |

| Time between XSCL and LP fall        | tld          |            | 10   |     | ns    |

| Time between LP and XSCL fall        | t∟н          |            | 150  |     | ns    |

| LP high level pulse width            | twLH         |            | 100  |     | ns    |

| LP low level pulse width             | twll         |            | 100  |     | ns    |

| FR setup time                        | trs          |            | 25   |     | ns    |

| FR hold time                         | tгн          |            | 10   |     | ns    |

| EIO setup time                       | tsue         |            | 30   |     | ns    |

| YD setup time                        | tyds         |            | 50   |     | ns    |

| YD hold time                         | tydh         |            | 50   |     | ns    |

| CA setup time                        | t∟cs         |            | 10   |     | μs    |

| CA hold time                         | <b>t</b> LCH |            | -200 | 200 | ns    |

| Input signal rise time and fall time | tr, tf       |            |      | 30  | ns    |

Note: CA is only effective at the first LP in the field. Assuming 1/N duty, the "first LP" refers to 1 and 1+ (multiples of (N/4).

FR is accepted at the falling edge of LP, and its state is reflected into the output that changes at the falling edge the following 1H.

# **Output Timing Characteristics**

| $VSS = -3.3 V \pm 0.3 V$ , VIH = 0.2 VSS, VIL = 0.8 VSS, $-V3 = -6.6 V \pm 0.6 V$ |              |                  |     |      |       |  |

|-----------------------------------------------------------------------------------|--------------|------------------|-----|------|-------|--|

| Parameter                                                                         | Symbol       | Conditions       | Min | Max  | Units |  |

| EIO reset time                                                                    | <b>t</b> er  |                  |     | 80   | ns    |  |

| EIO output delay time                                                             | <b>t</b> DCL | C∟ = 15 pF (EI0) |     | 90   | ns    |  |

| $LP \rightarrow Xn$ output delay time                                             | tlsd         | CL 100 pF        |     | 400  | ns    |  |

| $LP \rightarrow F2O$ , F1O output delay time                                      | <b>t</b> lfd | CL = 100 pF      |     | 3000 | ns    |  |

Vss =  $-3.3V \pm 0.3V$ , Vih = 0.2 Vss, Vil = 0.8 Vss,  $-V_3 = -6.6V \pm 0.6V$

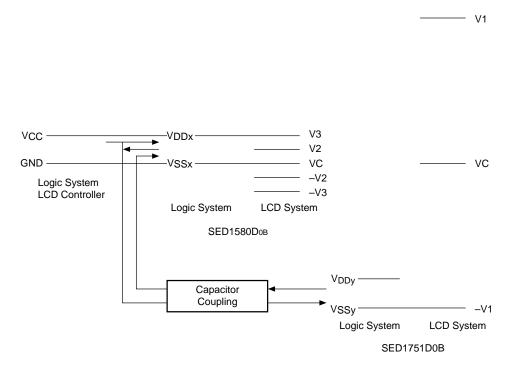

# POWER SOURCE

#### The Relationship Between Voltage Levels

When the SED1580 and SED1751 are used to structure an extremely low-power module system, the power supplies for the SED1580 logic systems and LCD systems, and the power supplies for the LCD controller should have the voltage relationships shown in the figure above.

In this case, caution is required when sending signals to the logic system. Specifically, use caution with the following:

| LCD Controller | $\rightarrow$ | SED1580 | Direct connection             |

|----------------|---------------|---------|-------------------------------|

| LCD Controller | $\rightarrow$ | SED1751 | Requires a capacitor coupling |

| SED1580        | $\rightarrow$ | SED1751 | Requires a capacitor coupling |

| SED1751        | $\rightarrow$ | SED1580 | Requires a capacitor coupling |

#### **Cautions During Power Up and Power Down**

This LSI requires special attention to be paid to the sequence in which the power supplies are turned on. Ensure that the power supply ON sequence is always one of the sequences below:

Logic system ON  $\rightarrow$  First LP cycle  $\rightarrow$  LCD system ON or Logic system ON  $\rightarrow \overline{\text{DOFF}} = \text{"L"} \rightarrow \text{LCD}$  system ON  $\rightarrow \text{First}$  LP cycle (\*2)  $\rightarrow \overline{\text{DOFF}} = \text{"H"}$

After applying power to the SED1580, the 2 frame interval is not displayed correctly because the number of LP cycles input in the first frame is counted and used to determine an address in the frame memory. This requires the use of DOFF. Consequently, display data should be transmitted at the point marked with (\*2). For power down, use the LCD system OFF  $\rightarrow$  Logic system OFF sequence, or power both down at the same time.

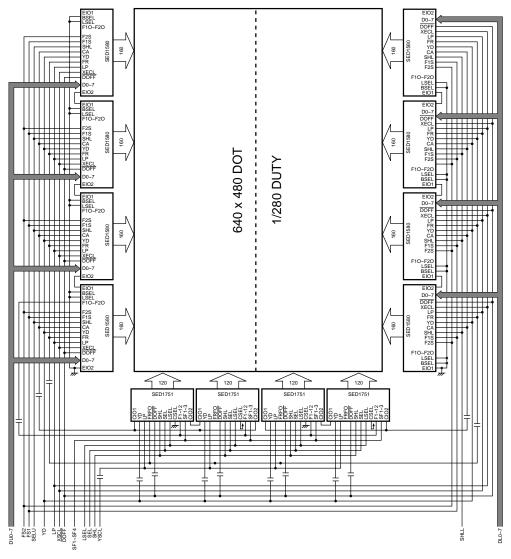

# **EXAMPLE OF EXTERNAL CONNECTIONS**

Controller

**EPSON**

#### Notes

Regarding this development specification, take the followings into consideration.

- The contents of this development specification may be revised without prior notice.

This development specification does not guarantee or grant the industrial property rights or any other rights.

The application examples contained in this development manual are given in order to help customers understand the product. Note that we shall not take any responsibility regarding problems on circuits. Regarding the use of semiconductor elements, take the followings into consideration.

#### [Precautions on Handling Optical Parts]

Following the solar cell theory, the characteristics of a semiconductor element changes as it is exposed to the light. Therefore, if this IC is exposed to the light, malfunction may occur.

- Design and mount the IC so that it won't be exposed to the light when in use.

Design and mount the IC so that it won't be exposed to the light in the inspection process.

- (3) Be concerned about shading of all the surfaces (front, back and side) of the IC.