# SED1590

# Contents

| OVERVIEW                   | 3-1  |

|----------------------------|------|

| TERMINAL FUNCTIONS         | 3-3  |

| EXPLANATION OF FUNCTIONS   | 3-9  |

| COMMANDS                   | 3-18 |

| ELECTRICAL CHARACTERISTICS | 3-26 |

| EXAMPLE OF USE             | 3-31 |

# OVERVIEW

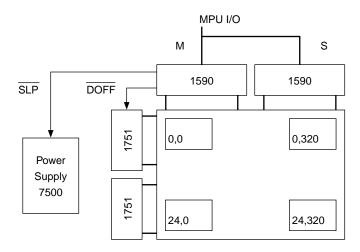

# Description

The SED 1590 is a high image quality mid-display-size-compatible RAM-integrated segment (column) driver that boasts the low power consumption required by portable devices. It is used in a set with the SED 1751 common (row) driver and the SCI 7500 power supply IC.

The SED 1590 can be connected directly to the MPU bus. It stores in its internal display RAM memory the 8-bit parallel display data sent to it from the MPU and then issues the LCD drive signals independent of the MPU. The chip has 160 LCD drive outputs and is equipped with 160 out  $\times$  240 line internal display RAM. Furthermore, because there is a one-to-one correspondence between picture elements on the LCD display and internal RAM dots, displays can be created with a high degree of flexibility.

Because it is not necessary to supply an external clock when writing to the SED 1590 internal RAM from the MPU side, these operations can be performed with an absolute minimum power consumption. Moreover, even when multiple SED 1590 chips are used, single chip select is supported; thus it is not necessary for the MPU to distinguish between the multiple chips.

The SED 1590 has a slim form that is useful in creating thinner LCD panels. It can operate using a low-voltage logic power supply system, and is thus suited to a broad range of applications.

#### Features

| <ul> <li>Number of LCD drive outputs: 1 0 out</li> <li>Drive duty ratio (MAX):</li></ul> |

|------------------------------------------------------------------------------------------|

| • RAM data displayed directly using the display data RAM.                                |

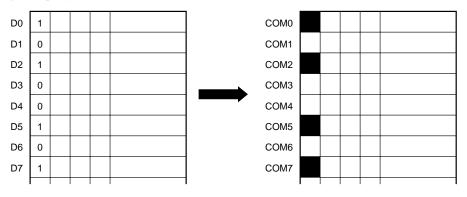

| • RAM bit data (when in normal display mode):                                            |

| "1" - On                                                                                 |

| • Internal RAM capacity:                                                                 |

| • High speed 8-bit MPU interface                                                         |

| • Compatible with both 80x86 series and 68000 series MPUs.                               |

| • Single chip select when multiple chips are used.                                       |

| Rich command functions.                                                                  |

| Extremely low consumption current.                                                       |

| • Power supply                                                                           |

| • Logic system: 2.7 to 3.6 V                                                             |

| • LCD system: 5.4 to 7.2 V                                                               |

| <ul> <li>Non-biased display off function</li> </ul>                                      |

| Slim chip shape                                                                          |

| • Package: DIE                                                                           |

| ТСР ТХХ                                                                                  |

| • This product is not designed for resistance to rediction or exposure to l              |

• This product is not designed for resistance to radiation or exposure to light.

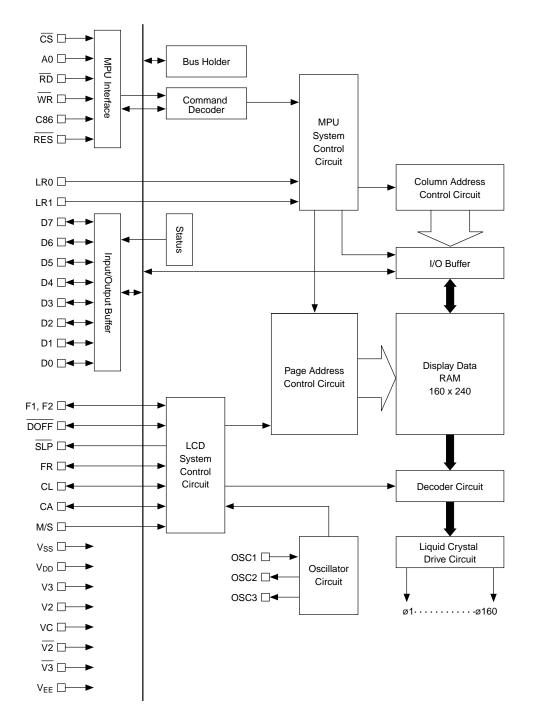

## **Block Diagram**

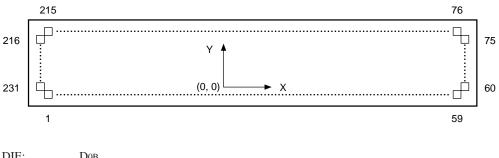

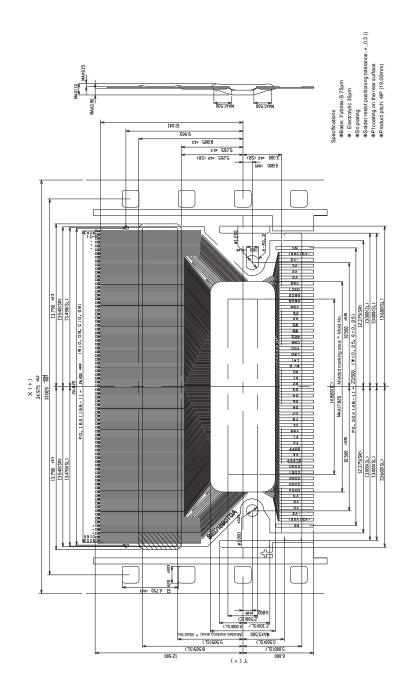

# TERMINAL FUNCTIONS Terminal Layout Diagram Dob

| DIE.         | DOB                                       |

|--------------|-------------------------------------------|

| Chip size:   | $14.82 \text{ mm} \times 2.50 \text{ mm}$ |

| Bump size:   | 67 μm × 80 μm (min.)                      |

| Bump pitch:  | 100 μm (min.)                             |

| Bump height: | $22.5 \pm 5.5 \ \mu m$                    |

|              |                                           |

# **Terminal Coordinates D0B**

| Pin      | Name         | X            | Y     | Pin      | Name         | Х            | Y       |

|----------|--------------|--------------|-------|----------|--------------|--------------|---------|

| 1        | V2           | -6692        | -1130 | 59       | V2           | 6692         | -1130   |

| 2        | VC           | -6548        |       | 60       | V3           | 7290         | -837    |

| 3        | V2           | -6404        |       | 61       | VEE          |              | -693    |

| 4        | V3           | -6260        |       | 62       | NC           |              | -549    |

| 5        | Vss          | -6025        |       | 63       | NC           |              | -369    |

| 6        | OSC1         | -5846        |       | 64       | O160         |              | -268    |

| 7        | OSC2         | -5588        |       | 65       | O159         |              | -167    |

| 8        | OSC3         | -5292        |       | 66       | O158         |              | -66     |

| 9        | Vss          | -5016        |       | 67       | O157         |              | 33      |

| 10       | NC           | -4847        |       | 68       | O156         |              | 134     |

| 11       | NC           | -4703        |       | 69       | O155         |              | 235     |

| 12       | CS           | -4507        |       | 70       | O154         |              | 336     |

| 13       | A0           | -4344        |       | 71       | O153         |              | 437     |

| 14       | RD           | -4181        |       | 72       | O152         |              | 537     |

| 15       | WR           | -4019        |       | 73       | O151         |              | 638     |

| 16       | RES          | -3856        |       | 74       | O150         |              | 739     |

| 17       | Vss          | -3703        |       | 75       | NC           | V            | 840     |

| 18       | C86          | -3508        |       | 76       | NC           | 7007         | 1130    |

| 19       | Vdd          | -3355        |       | 77       | O149         | 6904         |         |

| 20       | LR0          | -3160        |       | 78       | O148         | 6804         |         |

| 21       | Vss          | -3001        |       | 79       | O147         | 6703         |         |

| 22       | LR1          | -2805        |       | 80       | O146         | 6602         |         |

| 23       | Vdd          | -2652        |       | 81       | O145         | 6501         |         |

| 24       | MS           | -2453        |       | 82       | O144         | 6400         |         |

| 25       | Vss          | -2295        |       | 83       | O143         | 6300         |         |

| 26       | D0           | -1926        |       | 84       | O142         | 6199         |         |

| 27       | D1           | -1609        |       | 85       | O141         | 6098         |         |

| 28       | Vdd          | -1309        |       | 86       | O140         | 5997         |         |

| 29       | D2           | -1055        |       | 87       | O139         | 5896         |         |

| 30       | D3           | -728         |       | 88       | O138         | 5796         |         |

| 31       | D4           | -432         |       | 89       | O137         | 5695         |         |

| 32       | D5           | -104         |       | 90       | O136         | 5594         |         |

| 33       | D6           | 191          |       | 91       | O135         | 5493         |         |

| 34       | D7           | 518          |       | 92       | O134         | 5392         |         |

| 35       | FR           | 858          |       | 93       | O133         | 5292         |         |

| 36       | CL           | 1154         |       | 94       | O132         | 5191         |         |

| 37       | Vss          | 1413         |       | 95       | O131         | 5090         |         |

| 38       | F1<br>F2     | 1882         |       | 96       | O130         | 4989         |         |

| 39       | DOF          | 2178         |       | 97       | O129         | 4888         |         |

| 40<br>41 | CA           | 2506<br>2802 |       | 98<br>99 | O128<br>O127 | 4788<br>4687 |         |

| 41       |              | 3191         |       | 100      | 0127         | 4687<br>4586 |         |

| 42       | COD0         | 3519         |       | 100      | 0120         | 4380         |         |

| 43       | COD0<br>COD1 | 3815         |       | 101      | 0123         | 4483         |         |

| 44       | COD1<br>COD2 | 4142         |       | 102      | 0124         | 4384         |         |

| 46       | COD2         | 4438         |       | 103      | 0122         | 4183         |         |

| 40       | COD4         | 4766         |       | 105      | 0122         | 4082         |         |

| 48       | NC           | 5002         |       | 106      | O120         | 3981         |         |

| 49       | NC           | 5146         |       | 107      | O120<br>O119 | 3880         |         |

| 50       | NC           | 5290         |       | 107      | O118         | 3780         |         |

| 51       | NC           | 5434         |       | 109      | 0117         | 3679         |         |

| 52       | NC           | 5578         |       | 110      | O116         | 3578         |         |

| 53       | NC           | 5722         |       | 111      | O115         | 3477         |         |

| 54       | NC           | 5866         |       | 112      | 0114         | 3376         |         |

| 55       | NC           | 6010         |       | 113      | O113         | 3276         |         |

| 56       | V3           | 6260         |       | 114      | 0112         | 3175         |         |

| 57       | V2           | 6404         |       | 115      | 0111         | 3074         |         |

| 58       | VC           | 6548         | 🖌     | 116      | O110         | 2973         | ▼       |

|          |              |              | · · · |          | 0.10         | _0,0         | <b></b> |

| Pin | Name       | Х              | Y    | Pin        | Name       | X              | Y          |

|-----|------------|----------------|------|------------|------------|----------------|------------|

| 117 | O109       | 2872           | 1130 | 175        | O51        | -2973          | 1130       |

| 118 | O108       | 2772           |      | 176        | O50        | -3074          | 1          |

| 119 | O107       | 2671           |      | 177        | O49        | -3175          |            |

| 120 | O106       | 2570           |      | 178        | O48        | -3276          |            |

| 121 | O105       | 2469           |      | 179        | 047        | -3376          |            |

| 122 | O104       | 2368           |      | 180        | O46        | -3477          |            |

| 123 | O103       | 2268           |      | 181        | O45        | -3578          |            |

| 124 | O102       | 2167           |      | 182        | O44        | -3679          |            |

| 125 | O101       | 2066           |      | 183        | O43        | -3780          |            |

| 126 | O100       | 1965           |      | 184        | O42        | -3880          |            |

| 127 | O99        | 1864           |      | 185        | O41        | -3981          |            |

| 128 | O98        | 1764           |      | 186        | O40        | -4082          |            |

| 129 | 097        | 1663           |      | 187        | O39        | -4183          |            |

| 130 | O96        | 1562           |      | 188        | O38        | -4284          |            |

| 131 | O95        | 1461           |      | 189        | 037        | -4384          |            |

| 132 | O94        | 1360           |      | 190        | O36        | -4485          |            |

| 133 | O93        | 1260           |      | 191        | O35        | -4586          |            |

| 134 | O93<br>O92 | 1159           |      | 192        | 033<br>034 | -4687          |            |

| 134 | O92<br>O91 | 1058           |      | 192        | O34<br>O33 | -4007          |            |

| 135 | O91<br>O90 | 957            |      | 193        | 033<br>032 | -4788          |            |

| 130 | O90<br>O89 | 856            |      | 194        | 032        | -4989          |            |

| 137 | O88        | 756            |      | 195        | O30        | -5090          |            |

| 139 | 087        | 655            |      | 190        | O30<br>O29 | -5191          |            |

| 139 | 087<br>086 | 554            |      | 197        | O29<br>O28 | -5292          |            |

|     |            |                |      |            |            |                |            |

| 141 | O85        | 453            |      | 199        | 027        | -5392          |            |

| 142 | O84        | 352            |      | 200        | O26        | -5493          |            |

| 143 | O83        | 252            |      | 201        | O25        | -5594<br>-5695 |            |

| 144 | O82        | 151            |      | 202        | 024        | 1              |            |

| 145 | O81        | 50             |      | 203        | 023        | -5796          |            |

| 146 | O80        | -50            |      | 204        | 022        | -5896          |            |

| 147 | 079        | -151           |      | 205        | O21        | -5997          |            |

| 148 | 078        | -252           |      | 206        | O20        | -6098          |            |

| 149 | 077        | -352           |      | 207        | O19        | -6199          |            |

| 150 | 076<br>075 | -453           |      | 208        | 018        | -6300          |            |

| 151 | 075        | -554           |      | 209        | 017        | -6400          |            |

| 152 | 074        | -655           |      | 210        | O16        | -6501          |            |

| 153 | 073        | -756           |      | 211        | O15        | -6602          |            |

| 154 | 072        | -856           |      | 212        | 014        | -6703          |            |

| 155 | 071        | -957           |      | 213        | 013        | -6804          |            |

| 156 | O70<br>O69 | -1058          |      | 214<br>215 | O12<br>NC  | -6904<br>-7007 | <b>↓</b>   |

| 157 |            | -1159          |      | 215        | NC         | -7007          | 840        |

| 158 | O68        | -1260          |      |            |            | -7290          |            |

| 159 | O67        | -1360          |      | 217        | 011        |                | 739        |

| 160 | O66        | -1461          |      | 218        | 010        |                | 638<br>527 |

| 161 | O65        | -1562          |      | 219        | 09         |                | 537        |

| 162 | O64        | -1663          |      | 220        | 08         |                | 437        |

| 163 | O63        | -1764          |      | 221        | 07         |                | 336        |

| 164 | O62        | -1864          |      | 222        | 06         |                | 235        |

| 165 | O61        | -1965          |      | 223        | 05         |                | 134        |

| 166 | O60        | -2066<br>-2167 |      | 224        | 04         |                | 33         |

| 167 | O59        | -2167<br>-2268 |      | 225        | 03         |                | -66<br>167 |

| 168 | O58        |                |      | 226        | 02         |                | -167       |

| 169 | 057        | -2368          |      | 227        | 01         |                | -268       |

| 170 | O56        | -2469          |      | 228        | NC         |                | -369       |

| 171 | O55        | -2570          |      | 229        | NC         |                | -549       |

| 172 | O54        | -2671          |      | 230        | VEE        | 🖌              | -693       |

| 173 | O53        | -2772          | 🖌    | 231        | V3         |                | -837       |

| 174 | O52        | -2872          | ▼    |            |            |                |            |

# **Explanation of Terminals**

# **Power Supply Terminals**

| Terminal<br>Name        | I/O          | Explanation                                                                                                                                                         | No. of<br>Terminals |

|-------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Vdd                     | Power Supply | These are connected to Vcc (the system power supply).                                                                                                               | 3                   |

| Vss                     | Power Supply | These are connected to the system GND.                                                                                                                              | 6                   |

| Vee                     | Power Supply | These are the liquid crystal drive system load-side power supplies. VDD–VEE.                                                                                        | 2                   |

| V3, V2, VC,<br>-V2, -V3 | Power Supply | These are the liquid crystal drive multi-level power supplies. The relationships between the various levels must be: $VDD \ge V3 \ge V2 \ge VC > -V2 > -V3 \ge VEE$ | 2 Each              |

# Terminals Pertaining to the MPU

| Terminal<br>Name | I/O | Explanation                                                                                                                                                                                                                                                                                                                                                               | No. of<br>Terminals |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| D7 to D0         | I   | These comprise the 8–bit bi-directional data bus, and are connected to a standard 8–bit or 16–bit MPU data bus.                                                                                                                                                                                                                                                           | 8                   |

| A0               | Ι   | The least significant bit of the address bus of a normal MPU is connected to discern between data and commands.<br>H: Inidcates that D7 to D0 are control data.<br>L: Indicates that D7 to D0 are display data.                                                                                                                                                           | 1                   |

| RES              | I   | When initial settings are restored by placing $\overline{\text{RES}}$ to "L".<br>The reset operation is performed based on the $\overline{\text{RES}}$ level.<br>Schmidt trigger.                                                                                                                                                                                         | 1                   |

| CS               | I   | This is the chip select signal. In the SED 1590, even if multiple chips are used, the $\overline{CS}$ is a shared line. When $\overline{CS}$ is in a non-active state, D7 to D0 enter a high-impedance state.                                                                                                                                                             | 1                   |

| RD (E)           | I   | <ul> <li>When connected to an 80x86 series MPU<br/>Active "L"<br/>This terminal connects to the RD signal of the 80x86 MPU,<br/>and while this signal is low, the data bus is in an output state.</li> <li>When connected to a 68000 series MPU<br/>Active "H"<br/>This serves as the 68000 MPU-enabled clock input terminal.</li> </ul>                                  | 1                   |

| WR<br>(R/W)      | I   | <ul> <li>When connected to an 80x86 system MPU<br/>Active "L"<br/>This terminal is connected to the WR signal of the 80x86 series<br/>MPU. The data bus signals are latched on the rising edge of<br/>the WR signal.</li> <li>When connected to a 68000 series MPU<br/>This is the read/write control input terminal.<br/>R/W = "H": Read<br/>R/W = "L": Write</li> </ul> | 1                   |

| C86              | I   | This is the MPU interface switch terminal.<br>C86 = "H": The 68000 MPU interface.<br>C86 = "L": The 80x86 series MPU interface.                                                                                                                                                                                                                                           | 1                   |

# Liquid Crystal Drive Circuit Signals

| Terminal<br>Name | I/O | Explanation                                                                                                                                                                                                                                                                                                                                                 | No. of<br>Terminals |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| OSC1             | I   | This is for the oscillator circuit. When an external input is used, it is input to this terminal. Connect to "H" or "L" in case of slave operations.                                                                                                                                                                                                        | 1                   |

| OSC2             | 0   | This is a terminal for the oscillator circuit. When the internal oscillator circuit is used, connect to OSC1 through a capacitor. Make this terminal open in case of slave operations.                                                                                                                                                                      | 1                   |

| OSC3             | 0   | This is a terminal for the oscillator circuit. When the internal oscillator circuit is used, connect to OSC1 through a resistor. Make this terminal open in case of slave operations.                                                                                                                                                                       | 1                   |

| M/S              | I/O | This terminal selects master/slave operation. In master mode,<br>signals required for the liquid crystal display are output, while during<br>slave operation signals that are required to the liquid crystal<br>display are input, thereby synchronizing the liquid crystal display<br>system.<br>M/S = "H": Master operation<br>M/S = "L": Slave operation | 1                   |

| CL               | I/O | This is the display clock input/output terminal. When using master/slave mode, this is connected to the various CL terminals. This is also connected to the common driver YSCL terminals. When M/S = "H": Output When M/S = "L": Input                                                                                                                      | 1                   |

| FR               | I/O | This is the liquid crystal alternating current input/output terminal.<br>When using master/slave mode, this is connected to the various<br>FR terminals. This is also connected to the common driver FR<br>terminals.<br>When M/S = "H": Output<br>When M/S = "L": Input                                                                                    | 1                   |

| CA               | I/O | This is the field start signal. When using master/slave mode, this is connected to the various CA terminals. This is also connected to the common driver CA terminals. When M/S = "H": Output When M/S = "L": Input                                                                                                                                         | 1                   |

| DOF              | I/O | This is the liquid crystal display blanking control terminal.<br>When using master/slave mode, this is connected to the various<br>DOFF terminals. This is also connected to the common driver<br>DOFF terminals.<br>When M/S = "H": Output<br>When M/S = "L": Input                                                                                        | 1                   |

| SLP              | 0   | This is the sleep control terminal. When set to a sleep status by the MCU, both the master and the slave circuits enter the sleep mode. This terminal is not connected between the master and the slave. Connect to the SCI 7500 $\overline{\text{SLP}}$ terminal for the master only.                                                                      | 1                   |

| F1, F2           | I/O | These are the drive pattern signal input/output terminals.<br>When in master/slave mode, these are connected to the F1<br>and F2 terminals respectively. These are connected to the<br>common driver F1 and F2 terminals.<br>When M/S = "H": Output<br>When M/S = "L": Input                                                                                | 1 each              |

|                  |     |                                                                                                                                                                                                                                                                                                                                                             | 1                   |

# **Control Terminals**

| Terminal<br>Name                     | I/O | Explanation                                                                                                                                                                                                                                | No. of<br>Terminals |

|--------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| LR0, LR1                             | I   | When multiple SED1590 chips are used, these terminals specify the various segment driver layout positions. Using this information, the SED1590 determines the relationships between the various segments and the position in internal RAM. | 1 each              |

| COD0<br>COD1<br>COD2<br>COD3<br>COD4 | 0   | These comprise the 5-bit output port. The status of this port can be controlled by commands from the MPU. They can be used for controls of the electronic volume control knobs and other applications.                                     | 1 each              |

# **EXPLANATION OF FUNCTIONS**

#### The MPU Interface

The SED1590 exchanges data with the MPU through an 8-bit bi-directional data bus (D7 to D0). By setting the C86 terminal to "H" or "L" the SED1590 can be connected directly to the MPU bus for either the 80x86 system MPUs or the 68000 system MPUs, as shown in Table 1.

#### Table 1

| C86 | Туре          | CS | A0 | RD | WR  | D0 to D7 |

|-----|---------------|----|----|----|-----|----------|

| Н   | 68000 MPU bus | CS | A0 | E  | R/W | D0 to D7 |

| L   | 80×86 MPU bus | CS | A0 | RD | WR  | D0 to D7 |

The SED1590 identifies data bus signals using combinations of the A0, E, R/W and  $(\overline{RD}, \overline{WR})$  signals as shown in Table 2.

#### Table 2

| Common | 68 System | 80 System |   |                                      |

|--------|-----------|-----------|---|--------------------------------------|

| A0     | R/W       | RD WR     |   | Function                             |

| 1      | 0         | 1 0       |   | Write display data                   |

| 0      | 1         | 0         | 1 | Read status                          |

| 0      | 0         | 1 0       |   | Write to internal register (command) |

The SED1590 possesses a function that automatically identifies the segment driver position by the LR0 and LR1 terminals even when multiple SED1590 chips are used, so from the perspective of the MPU, there is no need for the MPU to identify the individual segment drivers. As a result, the  $\overline{CS}$  chip select terminals can share a common line from the outside. The LR will be discussed below.

When the chips are not selected, D0 to D7 enter a high impedance state and terminals A0,  $\overline{RD}$ , and  $\overline{WR}$  inputs are disabled.

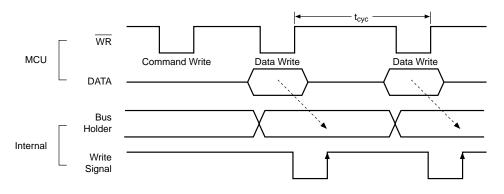

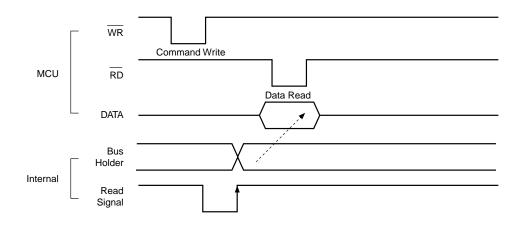

#### Accessing the Display Data RAM and the Internal Registers.

The SED1590 uses a type of pipeline process between LSIs through the bus holders in the internal data bus in order to match the operating frequencies between the MPU and the display data RAM and internal registers. Consequently, when viewed from the MPU side, there are no constraints on accessing the SED1590 in terms of the display data RAM access time (tACC), but rather the cycle time is dominant. When the cycle time is not adequate, then the MPU may insert an NOP command, which is equivalent to executing a dummy wait.

#### SED1590

#### • Writing

• Reading

#### **Busy Flag**

When the busy flag is "L", the SED1569 is making internal operations. The busy flag is being output through the terminal D7 by the status read command. Although commands from the MPU are being accepted even while the busy flag is appearing, it is necessary to secure due cycle time (tcyc) in order to make proper writing of the indication data. Meanwhile, in case the cycle time is being satisfied, it is not necessary to check this flag.

#### Page Address Control Circuit

Page direction address control is performed when the display RAM is accessed by the MPU and when contents of the display data RAM are read for the liquid crystal display.

When the page direction scan is designated by the scan direction select command, the page address will increment each time the MPU makes the writing operation. While the internal RAM contains 240 lines worth of data, because the MPU access processes in 8 dot units in the common direction, the number of pages is 240/8 = 30 pages.

Consequently, the count is locked when address value 29 is reached, and there is no incrementation beyond this level. The count lock is cleared next time the page address is set. Moreover, the counter within the page address control circuit is independent of the column address control circuit counter. When there is a read operation for the liquid crystal display, incrementation is synchronized with the CL

When there is a read operation for the liquid crystal display, incrementation is synchronized with the CL signal, and the count is reset when the display line that is set by a control command from the MPU has been reached.

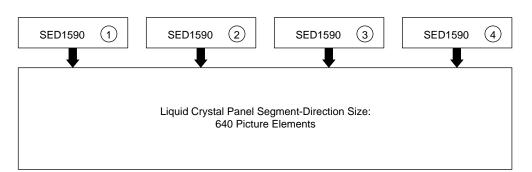

#### The Column Address Control Circuit

Address control in the column direction is performed when the display RAM is accessed from the MPU. The SED1590 unit has only 160 columns; however, using multiple chips the SED1590 can handle continuous column addressing even when using four chips in the column direction (640 columns). Consequently, from the MPU perspective, the MPU need not be aware of the multiple chips.

The address value is incremented or decremented when a write or read operation is performed by the MPU. In the increment mode, the count is locked at 279H (639), while in the decrement mode the count is locked at 000H (0). Incrementing/decrementing will not proceed past that count. The count lock is cleared the next time that a column address set is performed. Moreover, the counter within the column address control circuit operates independently of the page address control circuit counter.

# The I/O Buffer

The I/O buffer is a bi-directional buffer for cases where the MPU accesses the display data RAM via the SED1590 internal bus.

#### The Display Data RAM

The display data RAM is RAM in which is stored the dot data for the display. It has a  $160 \times 240$  bit structure. The data can be selected by specifying the page address and the column address. The display data D0 to D7 from the MPU corresponds to 8 dots in the common direction of the liquid crystal display, and thus when multiple SED1590 chips are used, there are few constraints when the display data is sent, allowing the display to be structured freely.

MPU-side display RAM reading and writing is done through the I/O buffer, which operates to prevent timing overlaps with the display RAM reads for driving the liquid crystal. Consequently, there is absolutely no negative effect on the display such as flickering even if operations that write data to the RAM or read data from the RAM are performed completely asynchronously with the liquid crystal drive timing during the dipslay.

# The Oscillator Circuit

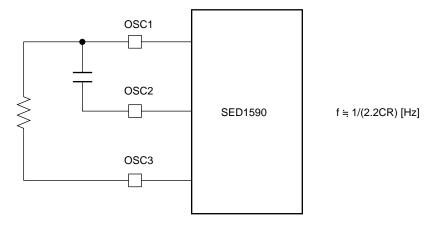

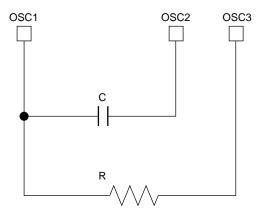

The oscillator circuit generates the synch circuit for the liquid crystal drive. When the internal oscillator circuit of the SED1590 is used, then a capacitor must be placed between OSC1 and OSC2, and a resistor must be placed between OSC1 and OSC3, as shown in the figure below. Determine the C and R values based on the oscillation frequency formula given below.

When the internal oscillator circuit is not used (i.e. when an external clock input is used instead), input the external clock into OSC1. Leave OSC2 and OSC3 open.

| M/S |                                                       | OSC1                         | OSC2        | OSC3 |  |

|-----|-------------------------------------------------------|------------------------------|-------------|------|--|

| "H" | Master operation                                      | Re                           | fer to Fig. | . 3  |  |

|     | (using the internal oscillation circuit)              | indicated above.             |             |      |  |

| "H" | Master operation<br>(using external signal<br>inputs) | Input<br>terminal.           | Open        | Open |  |

| "L" | Slave operation                                       | Connect<br>to<br>"H" or "L". | Open        | Open |  |

#### The Decoder

The decoder outputs the segment driver control signal that is required for the liquid crystal drive. This control signal is determined by the display data, the drive pattern signals F1 and F2, and by the liquid crystal alternating current signal FR.

#### The Liquid Crystal Drive Circuit

This outputs the liquid crystal drive voltage. The liquid crystal drive voltage can be of one of five values: V3, V2, VC,  $\overline{V2}$ ,  $\overline{V3}$ . These values are selected by the drive control signal determined by the decoder.

#### The Internal Timing Generator Circuit

The internal timing generator circuit controls the internal write operations when the display data RAM is accessed by the MPU. Moreover, in this case the column address counter and page address counter incrementation/decrementation is also controlled by the internal timing generator circuit.

When a module is structured from multiple chips, the SED1590 automatically determines from LR0 and LR1 which chip corresponds to which segments on the panel so that only the address relating to the corresponding segment responds. Consequently, from the perspective of the MPU, there is no need to identify each individual SED1590 chip, but rather when accessing in the column direction, continuous addresses can be handled in so far as the addresses are in the same page. As a result, the CS line can be shared. In this case, the relationship between the actual segment output and the column address is as shown in the following figure.

When there is an access race where both the MPU system and the display system are attempting to access the display data RAM simultaneously, the conflict between both accesses is mediated by the display control circuit. Consequently, there is no need for the MPU to perform a busy check in so far as the accesses ensure the cycle time that is set by the AC timing.

#### Table 3

|           | LR1 | LR0 | Corresponding Picture Elements | Column Address (10-bit binary display) |

|-----------|-----|-----|--------------------------------|----------------------------------------|

| SED1590 1 | "L" | "L" | 1 to 160                       | 000000000B to 0010011111B              |

| SED1590 2 | "L" | "H" | 161 to 320                     | 0010100000B to 0100111111B             |

| SED1590 3 | "H" | "L" | 321 to 480                     | 0101000000B to 0111011111B             |

| SED1590 4 | "H" | "H" | 481 to 640                     | 0111100000B to 1001111111B             |

#### The Display Control Circuit

The display control circuit generates the timing signals CL, CA, FR, along with the drive pattern signals F1 and F2, for the display based on the oscillator output from the oscillator circuit. Moreover, depending on the commands from the MPU, this circuit generates the  $\overrightarrow{\text{DOFF}}$  display On/Off control signal and the  $\overrightarrow{\text{SLP}}$  sleep signal as well.

When multiple SED1590 chips are used, the input and output statuses of these signals are as given in Table 4.

Table 4

| Operating Mode | CL     | СА     | F1, F2 | FR     | DOFF   | SLP    |

|----------------|--------|--------|--------|--------|--------|--------|

| Master         | Output | Output | Output | Output | Output | Output |

| Slave          | Input  | Input  | Input  | Input  | Input  | Output |

# The Relationship Between the Display Drive Output Voltage and the Display Data

Table 5 shows the relationships between F1, F2 and the common drive voltage.

Table 5

| FR          | L   |     |     |     | н   |     |     |     |

|-------------|-----|-----|-----|-----|-----|-----|-----|-----|

| F1          | Н   | L   | Н   | L   | Н   | L   | Н   | L   |

| F2          | Н   | Н   | L   | L   | Н   | Н   | L   | L   |

| n Line      | V1  | V1  | -V1 | V1  | -V1 | -V1 | V1  | -V1 |

| n + 1 Line  | -V1 | V1  | V1  | V1  | V1  | -V1 | -V1 | -V1 |

| n + 2 Lines | V1  | -V1 | V1  | V1  | -V1 | V1  | -V1 | -V1 |

| n + 3 Lines | V1  | V1  | V1  | -V1 | -V1 | -V1 | -V1 | V1  |

Note: The voltage relationships are as follows: V1 > VC > -V1 (where VC is the central voltage).

The values of F1 and F2 change for each horizontal interval (as described below) and for each CA set by the commands. The changes are as shown below. Moreover, in this display the numbers are described as (F2, F2).

| $(1,1) \longrightarrow (1,0) \longrightarrow (0,1) \longrightarrow (0,0) \longrightarrow (0,0) \longrightarrow (0,1) \longrightarrow (1,0)$ |                |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| $(1,0) \longrightarrow (0,1) \longrightarrow (0,0) \longrightarrow (0,0) \longrightarrow (0,1) \longrightarrow (1,0) \longrightarrow (1,1)$ |                |

| $(0,1) \longrightarrow (0,0) \longrightarrow (0,0) \longrightarrow (0,1) \longrightarrow (1,0) \longrightarrow (1,1) \longrightarrow (1,0)$ | <b>→</b> (0,1) |

| $(0,0) \longrightarrow (0,0) \longrightarrow (0,1) \longrightarrow (1,0) \longrightarrow (1,1) \longrightarrow (1,0) \longrightarrow (0,1)$ | → (0,0)        |

Changes in the horizontal direction indicate changes that happen each horizontal interval, where the horizontal interval was set by using commands. The changes in the vertical direction, shown on the column on the left, show the value change that starts with each CA.

The relationships between the display data, the liquid crystal alternating current signal FR, and the segment drive voltage are as shown in Table 6. These drive voltages change according to the combination of F1 and F2. In this table, "0" indicates "Off" and "1" indicates "On".

# Table 6

FR = "L"

|                    | n     | 0  | 0  | 0  | 0   | 0  | 0   | 0   | 0   | 1  | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

|--------------------|-------|----|----|----|-----|----|-----|-----|-----|----|-----|-----|-----|-----|-----|-----|-----|

| Display<br>Picture | n + 1 | 0  | 0  | 0  | 0   | 1  | 1   | 1   | 1   | 0  | 0   | 0   | 0   | 1   | 1   | 1   | 1   |

| Element            | n + 2 | 0  | 0  | 1  | 1   | 0  | 0   | 1   | 1   | 0  | 0   | 1   | 1   | 0   | 0   | 1   | 1   |

|                    | n + 3 | 0  | 1  | 0  | 1   | 0  | 1   | 0   | 1   | 0  | 1   | 0   | 1   | 0   | 1   | 0   | 1   |

|                    | 1     | V2 | VC | VC | -V2 | V3 | V2  | V2  | VC  | VC | V2  | -V2 | -V3 | V2  | VC  | VC  | -V2 |

| Drive              | 2     | V2 | VC | V3 | V2  | VC | -V2 | V2  | VC  | VC | -V2 | V2  | VC  | -V2 | -V3 | VC  | -V2 |

| Voltage            | 3     | V2 | VC | VC | -V2 | VC | -V2 | -V2 | -V3 | V3 | V2  | V2  | VC  | V2  | VC  | VC  | -V2 |

|                    | 4     | V2 | V3 | VC | V2  | VC | V2  | -V2 | VC  | VC | V2  | -V2 | VC  | -V2 | VC  | -V3 | -V2 |

#### FR = "H"

|                    | n     | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 1   | 1   | 1   | 1  | 1   | 1  | 1  | 1  |

|--------------------|-------|-----|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|----|-----|----|----|----|

| Display<br>Picture | n + 1 | 0   | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 0   | 0   | 0   | 0  | 1   | 1  | 1  | 1  |

| Element            | n + 2 | 0   | 0   | 1   | 1   | 0   | 0   | 1   | 1  | 0   | 0   | 1   | 1  | 0   | 0  | 1  | 1  |

|                    | n + 3 | 0   | 1   | 0   | 1   | 0   | 1   | 0   | 1  | 0   | 1   | 0   | 1  | 0   | 1  | 0  | 1  |

|                    | 1     | -V2 | VC  | VC  | V2  | -V3 | -V2 | -V2 | VC | VC  | V2  | V2  | V3 | -V2 | VC | VC | V2 |

| Drive              | 2     | -V2 | VC  | -V3 | -V2 | VC  | V2  | -V2 | VC | VC  | V2  | -V2 | VC | V2  | V3 | VC | V2 |

| Voltage            | 3     | -V2 | VC  | VC  | V2  | VC  | V2  | V2  | V3 | -V3 | -V2 | -V2 | VC | -V2 | VC | VC | V2 |

|                    | 4     | -V2 | -V3 | VC  | -V2 | VC  | -V2 | V2  | VC | VC  | -V2 | V2  | VC | V2  | VC | V3 | V2 |

Notes: (1), (2), (3) and (4) correspond to the following drive pattern:

(1): (F2, F1) = (H, H)

(2): (F2, F1) = (H, L) (3): (F2, F1) = (L, H)

(3): (F2, F1) = (L, T1)(4): (F2, F1) = (L, L)

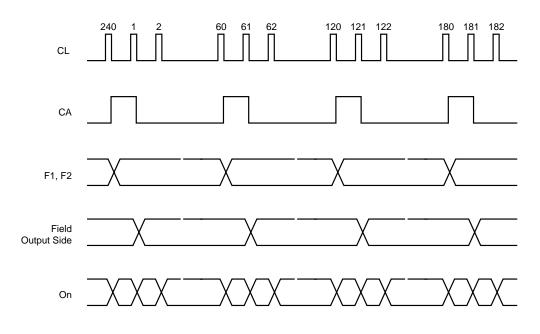

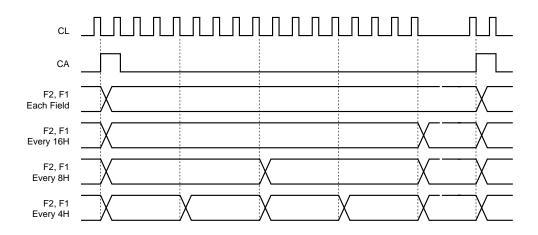

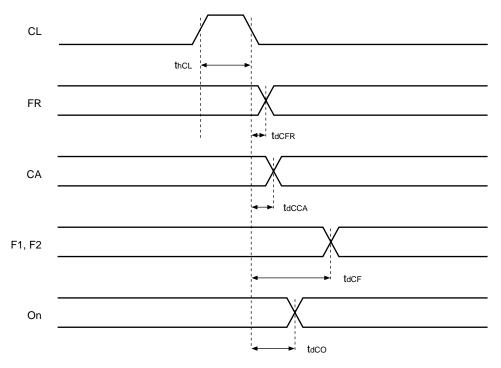

#### **Timing Diagram**

The timing diagram for the liquid crystal display is as shown in the following figure. Example: The example shows the fields used in a 1/240 duty, where the liquid crystal drive pattern (F2, F1) switches for each field.

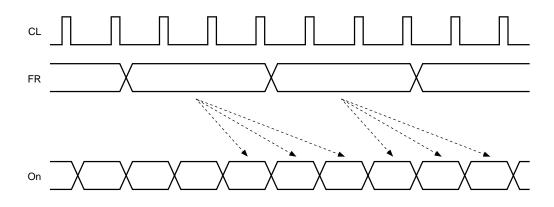

The figure below shows an example where the drive pattern (F2, F1) is different. The drive pattern is changed with the falling edge of CL and the status is reflected to the driver output that changes at the next falling edge of CL.

The figure below shows the timing with which FR changes. FR changes on the falling edge of CL, and the changes are reflected to the driver which changes on the next falling edge of CL (master mode). Moreover, in the case of slave mode, the FR status is accepted with the falling edge of CL, and is reflected to the driver output that changes on the next falling edge of CL.

# COMMANDS

# Table of Commands

Table 7 shows a table of SED1590 commands

Table 7

| Com | mand Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                    | Parameters |

|-----|-----------|----|----|----|----|----|----|----|----|----|----|----|-----------------------------|------------|

| 1   | DON       | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | Display ON                  | None       |

| 2   | DOFF      | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  | Display OFF                 | None       |

| 3   | DISNOR    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | Normal display              | None       |

| 4   | DISINV    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | Inverse display             | None       |

| 5   | DTYSET    | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | Duty set                    | 1 byte     |

| 6   | LINSET    | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | FR interval set             | 1 byte     |

| 7   | PATSET    | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | Drive pattern set           | 1 byte     |

| 8   | VOLCTL    | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | Output port control         | 1 byte     |

| 9   | SLPON     | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | Sleep on                    | None       |

| 10  | SLPOFF    | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | Sleep off                   | None       |

| 11  | DVDSET    | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  | Divide offset               | 1 byte     |

| 12  | PASET     | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 1  | Page address set            | 1 byte     |

| 13  | PDNOR     | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | Page direction normal       | None       |

| 14  | PDINV     | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | Page direction inverse      | None       |

| 15  | CASET     | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | Column address set          | 2 byte     |

| 16  | CAINC     | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | Column address<br>increment | None       |

| 17  | CADEC     | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | Column address<br>decrement | None       |

| 18  | PDIR      | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | Page direction scan         | None       |

| 19  | CDIR      | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | Column direction scan       | None       |

| 20  | MWRITE    | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | Memory write                | Data       |

| 21  | CNTCLR    | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | Counter clear               | None       |

| 22  | PCCLR     | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | Page counter clear          | None       |

| 23  | CCCLR     | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | Column counter clear        | None       |

| 24  | CKSET     | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | Clock divide set            | 1 byte     |

| 25  | RETURN    | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | Return                      | None       |

| 26  | VOLRD     | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | Output port set read        | 1 byte     |

| 27  | STREAD    | 0  | 0  | 1  |    |    |    |    |    |    |    |    | Status read                 |            |

# **Command Details**

The SED1590 identifies the data bus signals by a combination of A0,  $\overline{RD}$  (E),  $\overline{WR}$  (R/ $\overline{W}$ ). The command interpretation and execution is performed based entirely on internal timing without relying on any external clock.

In the 80×86 MPU interface, a low pulse is sent to the  $\overline{WR}$  terminal to launch the command when writing. In the 68000 series MPU interface, a "L" input to the  $R/\overline{W}$  terminal causes a write state, and then the commands are launched when a high pulse input is sent to the E terminal. Consequently, the 68000 series MPU interface is different from the 80x86 MPU interface in the command details and command tables, and in that the  $\overline{RD}$  (E) terminal is "1" ("H") when performing status reads and when reading display data. The commands will be explained below using the 80×86 MPU interface in the examples.

#### Display ON/OFF Command: 1, Parameter:0

This command forces the entire display ON or OFF. When the display is OFF, all outputs are fixed at VC. Because the display is not possible when in sleep mode, make sure that this command is used after the sleep mode is turned OFF.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function    |

|--------------|----|----|----|----|----|----|----|----|----|----|----|-------------|

| DON          | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | Display ON  |

| DOFF         | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  | Display OFF |

#### Page Address Set Command: 1, Parameter: 1

This command and its following parameters makes it possible to set the page address corresponding to the low address when accessing the display data RAM from the MPU side. The desired bit of the display data RAM can be accessed by specifying the page address and the column address. The page addresses are 5 bits, corresponding to 30 pages (pages 0 to 29). Even if the page address changes, there is no change to the display status.

This command is input into the registers and loaded in the counters). That which is input is stored within the register, and can be reloaded by the PACLR command.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function         |

|--------------|----|----|----|----|----|----|----|----|----|----|----|------------------|

| PASET        | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 0  | 1  | Page address set |

| Parameter    | 1  | 1  | 0  |    |    |    | D  | D  | D  | D  | D  |                  |

#### Page Address Direction Command: 1, Parameter: 0

This command makes it possible to reverse the position of page 0 in the page address of the display RAM data. Consequently, it is possible to reverse the page address scan direction when the MPU uses the display data in the page direction. The relationship between the physical position in internal RAM and the page address is inverted:

Normal:  $0 \rightarrow 29$

Reversed:  $24 \leftarrow 0$

When reversed, the final page address becomes 24. Consequently, the number of lines which can be indicated becomes upto 200.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                |

|--------------|----|----|----|----|----|----|----|----|----|----|----|-------------------------|

| PDNOR        | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 0  | Page direction normal   |

| PDINV        | 0  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | 1  | 1  | Page direction inverted |

#### Column Address Set Command: 1, Parameter: 2

This command and its following parameters make it possible to specify the column address when the MPU accesses display data RAM in the column direction. The desired bit of display data RAM can be accessed by specifying the page address and the column address. The column address has 10 bits, and when four of the chips are used in the column direction, up to 640 dots (pixels) are supported. Even when the address changes, the state of the display does not change. There are 640 columns (columns 0 to 639).

The address value is input with the less significant address 5 bit first and then the more significant 5 bit. With the less significant alone, when another command is entered, only the less significant is entered into the register, however, the counter is not loaded. When the less significant is followed by the more significant, they are loaded into the counter and the input is stored in the register. When the less significant address is followed by some other command, the counter will not be loaded and the command will be cancelled. With this command, the set values can be reloaded by the CCCLR command.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function           |

|--------------|----|----|----|----|----|----|----|----|----|----|----|--------------------|

| CASET        | 0  | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | Column address set |

| Parameter 1  | 1  | 1  | 0  |    |    |    | D  | D  | D  | D  | D  | Lower 5 bits       |

| Parameter 2  | 1  | 1  | 0  |    |    |    | D  | D  | D  | D  | D  | Upper 5 bits       |

#### Column Address Direction Command: 1, Parameters: 0

This command specifies the behavior of the column address counter (increment vs. decrement). The address increments or decrements each time RAM accesses the display data. In the increment mode, the count operation stops when the value reaches 279H (639), or when the value reaches 000H (0) in the decrement mode.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                 |

|--------------|----|----|----|----|----|----|----|----|----|----|----|--------------------------|

| CAINC        | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | Column address increment |

| CADEC        | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | Column address decrement |

#### Scan Direction Select Command: 1, Parameter: 0

When the MPU continuously accesses display memory, this determines whether the scanning will be done in the page direction or in the column direction.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function              |

|--------------|----|----|----|----|----|----|----|----|----|----|----|-----------------------|

| PDIR         | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | Page direction scan   |

| CDIR         | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | Column direction scan |

#### Display Data Write Command: 1, Parameter: Number of data to be written

When the MPU writes data to the memory, this command places the chip in a data entry mode. By writing data again after this command, the display data RAM contents can be changed. The data write mode is cleared automatically when another command is entered.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function     |

|--------------|----|----|----|----|----|----|----|----|----|----|----|--------------|

| MWRITE       | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | Memory write |

| Parameter    | 1  | 1  | 0  | D  | D  | D  | D  | D  | D  | D  | D  | Write data   |

#### Status Read

This read operation makes it possible to monitor the internal operating status of the SED1590. No other command except for the status read command will be accepted with a RAM busy state (1). If the cycle time is followed, then there is no need to check for the RAM busy state under normal use.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------|

| STREAD       | 0  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Status   |

| D7: | Busy/Ready               | Busy: 1, Ready: 0                    |

|-----|--------------------------|--------------------------------------|

| D6: | Page Address Direction   | Normal: 1, Inverted: 0               |

| D5: | Column Address Direction | Normal: 1, Inverted:0                |

| D4: | Increment Direction      | Column: 0, Page: 1                   |

| D3: | Display ON/OFF           | Off: 1, On: 0                        |

| D2: | SLEEP ON/OFF             | Off: 0, On: 1                        |

| D1: | INVERT                   | Normal Display: 1, Invert Display: 0 |

| D0: | Reserved terminal        |                                      |

#### Display Normal/Inverted Command: 1, Parameter:0

This command makes it possible to inert the ON/OFF status of each point on the display without having to rewrite the contents of the display data RAM. Because all points in the display are either set to the normal display or reverse, partial inversions are not supported.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function         |

|--------------|----|----|----|----|----|----|----|----|----|----|----|------------------|

| DISNOR       | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0  | Display normal   |

| DISINV       | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 1  | Display inverted |

#### Duty Set Command: 1, Parameter: 1

This command combined with the following paramenter sets the duty.

| Command Name           | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                          |

|------------------------|----|----|----|----|----|----|----|----|----|----|----|-----------------------------------|

| DTYSET                 | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | Duty set                          |

| Parameter              | 1  | 1  | 0  |    |    | D  | D  | D  | D  | D  | D  | (Number of display<br>lines)/ 4/1 |

| Example:<br>1/200 duty | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | 1  |                                   |

| Example:<br>1/240 duty | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 1  |                                   |

#### Sleep Mode On/Off Command: 1, Parameter:0

This command controls the sleep mode of the LCD module. Before launching this command, be sure that the Display OFF command has been entered and that the display is in an OFF state. Moreover, after issuing the Sleep OFF command, be sure to maintain the logic power supply for 40 ms to discharge the load of the power supply IC.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function  |

|--------------|----|----|----|----|----|----|----|----|----|----|----|-----------|

| SLPON        | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | Sleep ON  |

| SLPOFF       | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | Sleep OFF |

#### Line Inverse Number Set Tab Command: 1, Parameter: 1

This command controls the number of lines inverted in the LCD module.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function             |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------------------|

| LINSET       | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | FR inverse set       |

| Parameter    | 1  | 1  | 0  |    |    |    |    | D  | D  | D  | D  | FR inverse set value |

The default value is being set to 11H inverse. (D3 to D0 = 1010)

#### Pattern Set Command: 1, Parameter: 1

This command controls the MLS pattern switching interval.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                |

|--------------|----|----|----|----|----|----|----|----|----|----|----|-------------------------|

| PATSET       | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | Drive pattern set       |

| Parameter    | 1  | 1  | 0  |    |    |    |    |    |    | D  | D  | Drive pattern set value |

The correspondence between the input data and the switching interval is as follows:

(The default value will be set to 8H.)

|     | 8H | 4H | 16H | Field |

|-----|----|----|-----|-------|

| D0: | 0  | 1  | 0   | 1     |

| D1: | 0  | 0  | 1   | 1     |

#### **Output Port Control Command: 1, Parameter: 1**

This command sets 5 bit data to control the LCD power supply.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0    | F               | unction      |

|--------------|----|----|----|----|----|----|----|----|----|----|-------|-----------------|--------------|

| VOLCTL       | 0  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  | 1  | 0     | Output          | port control |

| Parameter    | 1  | 1  | 0  |    |    |    | D  | D  | D  | D  | D     | Output<br>value | port control |

|              |    |    |    |    |    |    |    |    |    |    | D0: 0 | COD 0           | D1: COD 1    |

|              |    |    |    |    |    |    |    |    |    |    | D2: ( | COD 2           | D3: COD 3    |

D4: COD 4

#### Partition DOFF Set Command: 1, Parameter: 1

This command controls the LCD module display on/off for each driver.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                   |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------------------------|

| DVDSET       | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  | Partition offset           |

| Parameter    | 1  | 1  | 0  |    |    |    |    | D  | D  | D  | D  | Partition offset set value |

D= "1": Display ON D = "0": Display OFF

(LR1, LR0): (0, 0)  $\rightarrow$  D0; (0,1)  $\rightarrow$  D1; (1, 0)  $\rightarrow$  D2; (1,1)  $\rightarrow$  D3

#### Initialize Command: 1, Parameter: 0

These commands clear the contents of the page counter, the page register, the column counter, and the column register to 0.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function             |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------------------|

| CNTCLR       | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | Counter clear        |

| PCCLR        | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | Page counter clear   |

| CCCLR        | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | Column counter clear |

CNTCLR: Resets the page counter and register to 0, and the column counter and register to 0.

PACLR: Loads the register value to the page counter.

CACLR: Loads the register value to the column counter.

#### Clock Divide Set Command: 1, Parameter: 1

This command sets the CL division ratio that serves as the basis for the timing signal for the liquid crystal display.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function                 |

|--------------|----|----|----|----|----|----|----|----|----|----|----|--------------------------|

| CKSET        | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | Clock division set       |

| Parameter    | 1  | 1  | 0  |    |    |    |    |    |    | D  | D  | Clock division set value |

Correspondence of Divider Ratios

|      |     | 2 | 1 | 4 | 8 |

|------|-----|---|---|---|---|

| Data | D1: | 0 | 0 | 1 | 1 |

|      | D0: | 0 | 1 | 0 | 1 |

#### Return Command: 1, Parameter: 0

This command sets the scan direction counter to the set value, and increments (+1) the counter in the fixed direction.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function       |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------------|

| RETURN       | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  | Address return |

#### **Output Port Setting Read Command: 1**

This command reads the output port set bit to the data bus. Perform a read operation after this command is input. Only the master chip gives an output.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function             |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------------------|

| VOLRD        | 0  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0  | Output port set read |

| Parameter    | 1  | 0  | 1  |    |    |    | 0  | 0  | 0  | 0  | 0  |                      |

#### NOP (Non-operating) Command: 1, Parameter: 0

This command has no effect on operations.

| Command Name | A0 | RD | WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | Function |

|--------------|----|----|----|----|----|----|----|----|----|----|----|----------|

| NOP1         | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | NOP      |

| NOP2         | 0  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | 0  | 0  | NOP      |

# ELECTRICAL CHARACTERISTICS Absolute Maximum Ratings

| ltem                     | Signal               | Rated Value      | Units |

|--------------------------|----------------------|------------------|-------|

| Power supply voltage (1) | Vss                  | -7.0 to +0.3     | V     |

| Power supply voltage (2) | VEE                  | -8.0 to +0.3     | V     |

| Power supply voltage (3) | V3, V2, VC, -V2, -V3 | VEE to +0.3      | V     |

| Input voltage            | Vin                  | Vss -0.3 to +0.3 | V     |

| Output voltage           | Vout                 | Vss -0.3 to +0.3 | V     |

| Operating temperature    | Topr                 | -20 to +85       | °C    |

| Storage temperature 1    | Tstg1                | -65 to +150      | °C    |

| Storage temperature 2    | Tstg2                | -55 to +100      | °C    |

Note 1: The voltages are all relative to VDD = 0V.

Note 2: Storage temperature 1 is the storage temperature for the bare chip or the plastic chip package products, and storage temperature 2 is the specification for the TCP packaged product.

Note 3: Be sure that the relationships between voltages V3, V2, VC, -V2, -V3 are always such that  $VDD \ge V3 > V2 > VC > -V3 \ge VEE$ .

Note 4: This LSI chip may be permanently damaged if the LSI chip is used in conditions exceeding the absolute maximum ratings. Furthermore, it is desirable to always operate the LSI chip within these electrical characteristic conditions, not only may the LSI chip malfunction if these conditions are exceeded, but there will be adverse effects on the reliability of the LSI chip.

# **DC Characteristics**

Unless otherwise stated, VDD = V3 = 0V, VSS = -3.0V, VEE = -V3 = -6.0V, V2 = -1.5V, VC = -3.0, -V2 = -4.5V

| Item                                 | Symbol | Parameter                                                                                                               | Min     | Тур         | Мах     | Units | Corresponding<br>Terminal |

|--------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------|---------|-------------|---------|-------|---------------------------|

| Power supply voltage (1)             | Vss    |                                                                                                                         | -3.6    | -3.0        | -2.7    | V     | Vss                       |

| Power supply voltage (2)             | VEE    |                                                                                                                         | -7.2    | -6.0        | -5.4    | V     | Vee                       |

| Power supply voltage (3)             | V3     |                                                                                                                         |         |             | Vdd     | V     | V3                        |

| Power supply voltage (4)             | V2     |                                                                                                                         |         | 0.25<br>Vee |         | V     | V2                        |

| Power supply voltage (5)             | VC     |                                                                                                                         |         | 0.50<br>Vee |         | V     | VC                        |

| Power supply voltage (6)             | -V2    |                                                                                                                         |         | 0.75<br>Vee |         | V     | -V2                       |

| Power supply voltage (7)             | -V3    |                                                                                                                         | Vee     |             |         | V     | -V3                       |

| High-level input voltage             | VIHC   |                                                                                                                         | 0.3Vss  | _           | Vdd     | V     | *1                        |

| Low-level input voltage              | VILC   |                                                                                                                         | Vss     | _           | 0.7 Vss | V     | *1                        |

| High-level output voltage            | Vон    | Iон = -0.6mA                                                                                                            | Vdd-0.4 | _           | Vdd     | V     | *2                        |

| Low-level output voltage             | Vol    | IoL = +0.6mA                                                                                                            | Vss     | _           | Vss+0.4 | V     | *2                        |

| Schmidt high-level input voltage     | Vihs   |                                                                                                                         | 0.3Vss  | _           | Vdd     | V     | RES                       |

| Schmidt low-level input voltage      | Vils   |                                                                                                                         | Vss     | _           | 0.7Vss  | V     | RES                       |

| Input leakage current                | LI     | Vss ≤Vin≤Vdd                                                                                                            | —       | _           | 5.0     | μΑ    | *3                        |

| Input/output leakage<br>current      | Ili/o  | VIN=VDD, VSS                                                                                                            | _       | _           | 5.0     | μΑ    | *4                        |

| Driver output<br>resistance          | Ron    | $Vss = -3.0V, \\ VEE = -6.0V \\ V3 = 0V, \\ V2 = -1.5V \\ VC = -3.0V \\ -V2 = -4.5V \\ -V3 = -6.0V, \\ \Delta V = 0.5V$ | _       | 0.6         | 1.0     | kΩ    | 01~<br>0160               |

| Static consumption<br>current        | Issq   | VIN = VDD<br>or Vss                                                                                                     | _       | —           | 5       | μΑ    | Vss                       |

| Static consumption<br>current        | IEEQ   | VEE = -6.0V                                                                                                             | _       | _           | 5       | μΑ    | VEE                       |

| Dynamic consumption<br>current       | ISSOP1 | MPU access *6                                                                                                           | _       | 1.5         | 2.0     | μΑ    | Vss                       |

| Dynamic consumption<br>current       | ISSOP2 | MPU no access *6                                                                                                        | _       | 90          | 130     | μΑ    | Vss                       |

| Dynamic consumption<br>current       | IEEOP  | VEE = -6.0V                                                                                                             | _       | 12          | 20      | μΑ    | VEE                       |

| Input terminal<br>capacitance        | CI     |                                                                                                                         |         | _           | 8       | pF    | *3                        |

| Input/output terminal<br>capacitance | CI/O   | Freq. = 1MHz<br>Ta = 25°C<br>IC alone                                                                                   |         |             | 15      | pF    | *4                        |

| Output terminal<br>capacitance       | со     |                                                                                                                         | _       | _           | 7       | pF    | SLP                       |

| Oscillator frequency                 | lfosc  | Ta = 25°C                                                                                                               |         | 24          | -       | kHz   | *5                        |

DC Characteristics: Supplemental Explanation for Corresponding Terminals

- \*1 •Input terminals: A0, RES, CS, RD, WR, C86, OSC1, M/S, LR0, and LR1.

•Input/output terminals (Input mode): D[0:7], CL, FR, CA, DOFF, SLP, F1 and F2.

- \*2 •Input/output terminals (Output mode): D[0:7], CL, FR, CA, DOFF, F1, and F2.

•Output terminals: OSC2, OSC3, and SLP

- \*3 •Input terminals: A0, RES, CS, RD, WR, C86, OSC1, M/S, LR0, and LR1.

- \*4 •Input/Output terminals (Input mode): D[0:7], CL, FR, CA, DOFF, SLP, F1, and F2.

- \*5 •Local oscillator circuit depending on CR.

- \*6 •Frame frequency = 60 Hz, Duty = 1/200 and CR oscillation 24 kHz should be split into twodivisions when used.

- •Adjust the "C" to C = 100 pF and adjust the R to 24 kHz, using a variable resistor.

- •Access of the MPU will be made by continuous writing of the indicated data within the cycle time of 1,333 ns (750 kHz).

- •The indicated data will appear in black or white in units of 4 lines each, repetitively.

Oscillating frequency: f = 1/(2.2 CR)

#### **AC Characteristics**

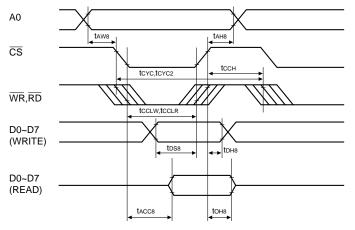

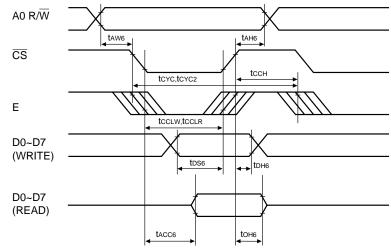

#### The System Bus

Read/Write Characteristics I (80×86 Series MPUs)

$[Ta = -20 \text{ to } 85^{\circ}C, Vss = -3.0 \text{ to } -3.6V]$

| Signal   | Symbol        | Parameter                                  | Min  | Мах | Units | Measurement<br>Conditions |

|----------|---------------|--------------------------------------------|------|-----|-------|---------------------------|

| AO       | tah8          | Address hold time                          | 5    | _   | ns    |                           |

| AU       | taw8          | Address setup time                         | 5    | —   | ns    |                           |

|          | tcyc          | Write cycle                                | 1300 | —   | ns    |                           |

|          | tcyc2         | Read cycle (Status read, output port read) | 300  | —   | ns    |                           |

| WR, RD   | tссн          | Duration of the control pulse "H"          | 600  | —   | ns    |                           |

|          | tcclw         | Duration of the control pulse "L" (WR)     | 50   | —   | ns    |                           |

|          | <b>t</b> CCLR | Duration of the control pulse "L" (RD)     | 140  | —   | ns    |                           |

|          | tDS8          | Data setup time                            | 35   | —   | ns    |                           |

| D0 to D7 | tdh8          | Data hold time                             | 5    | _   | ns    |                           |

| D0 10 D7 | tACC8         | Read access time                           | —    | 140 | ns    | CL = 100 pF               |

|          | tонв          | Output disable time                        | 30   | 90  | ns    |                           |

| $[Ta = -20 \text{ to } 85^{\circ}C]$ | Vss = -2.7  to  -3.0 V |

|--------------------------------------|------------------------|

|--------------------------------------|------------------------|

|          |               |                                            |      |     | ,     | 2.1 10 0.01               |

|----------|---------------|--------------------------------------------|------|-----|-------|---------------------------|

| Signal   | Symbol        | Parameter                                  | Min  | Мах | Units | Measurement<br>Conditions |

| A0       | tans          | Address hold time                          | 5    | _   | ns    |                           |

|          | taw8          | Address setup time                         | 5    | _   | ns    |                           |

|          | tcyc          | Write cycle                                | 1600 | _   | ns    |                           |

|          | tcyc2         | Read cycle (Status read, output port read) | 350  | —   | ns    |                           |

| WR, RD   | tссн          | Duration of the control pulse "H"          | 900  | —   | ns    |                           |

|          | tcclw         | Duration of the control pulse "L" (WR)     | 70   | —   | ns    |                           |