# DESCRIPTION

The SCI7654 COA/MOA is a CMOS process, chargepumping DC/DC converter and voltage regulator featuring the very high efficiency but low power consumption. An addition of four, three, or two external capacitors can generate four-, three- or two-time output voltage in negative direction than the input voltage. Also, the built-in voltage regulator can set any output voltage of DC/DC converter and can output the regulated voltage using two external resistances. As the regulator output can have a negative temperature gradient that is required for LCD panels, it is optimum for the LCD panel power supply.

# **FEATURES**

- · Charge-pumping, DC-to-DC converter (four-, threeor two-time negative boosting)

- Built-in voltage regulator (regulated voltage output circuit)

- High power conversion efficiency

• High output capacity

- : 95% • Low current consumption :  $130 \,\mu\text{A}$  (VI =  $-5.0 \,\text{V}$

- during four-time boosting, Typ.) : 20 mA (Max.)

- · Input voltages

- : -2.4 to -5.5 V (during four-time boosting) : 2.4 to -7.3 V (during three-time boosting) : 2.4 to -11 V (during two-time boosting) • DC/DC converter output : |Input voltage|  $\times 4$ (Max.)

- · Built-in reference voltage for high-precision regulator : 1.5 + -0.05 V (at CT0)

- · Temperature gradient function of regulator output voltages

- · Low standby current (during power-off)

- : 5.0 µA Power-off by the external signal

- · Full built-in oscillator circuit

- Lineup

voltage

: SCI7654M0A, 16-pin SSOP : SCI7654C0A, 16-pin DIP

: -0.04, -0.15, -0.35, -0.55 (%/°C)

# APPLICATIONS

- · Power supply of medium- and small-capacity LCD panels

- Regulated power supply of battery driven devices

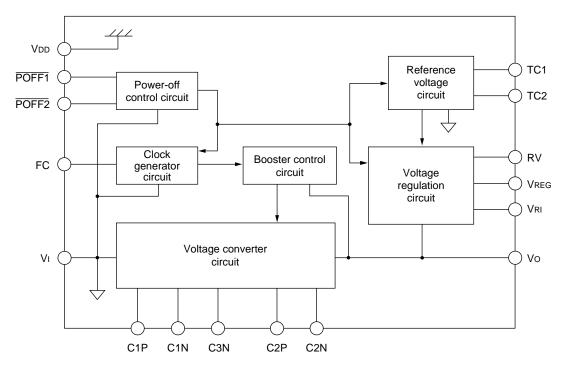

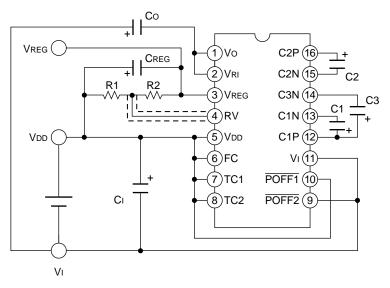

# **BLOCK DIAGRAM**

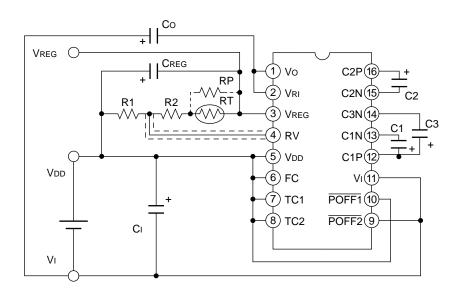

Figure 2.1 Block diagram

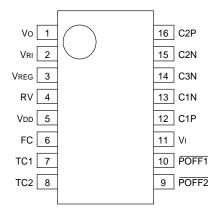

# **PIN DESCRIPTION**

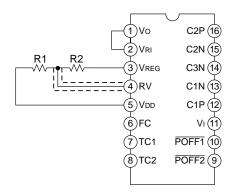

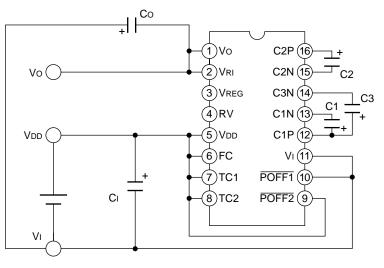

Figure 2.2 SCI7654MoA/CoA pin assignment

| Pin name | Pin No. | PAD No. | Function                                                                      |

|----------|---------|---------|-------------------------------------------------------------------------------|

| Vo       | 1       | 18      | Four-time booster output                                                      |

| Vri      | 2       | 19      | Regulator input                                                               |

| Vreg     | 3       | 20      | Regulator output                                                              |

| Rv       | 4       | 21      | Regulator output voltage adjustment input                                     |

| Vdd      | 5       | 22, 23  | Power pin (positive)                                                          |

| FC       | 6       | 24      | Internal clock frequency input, and clock input in serial/parallel connection |

| TC1      | 7       | 3       | Regulator output temperature gradient setup input (1)                         |

| TC2      | 8       | 4       | Regulator output temperature gradient setup input (2)                         |

| POFF2    | 9       | 5       | Power-off control input (2)                                                   |

| POFF1    | 10      | 6       | Power-off control input (1)                                                   |

| VI       | 11      | 11, 12  | Power voltage (negative)                                                      |

| C1P      | 12      | 13      | Two- or four-time booster capacitor positive pin                              |

| C1N      | 13      | 14      | Two-time booster capacitor negative pin                                       |

| C3N      | 14      | 15      | Four-time booster capacitor negative pin                                      |

| C2N      | 15      | 16      | Three-time booster capacitor negative pin                                     |

| C2P      | 16      | 17      | Three-time booster capacitor positive pin                                     |

### Table 2.1 Functions of the terminal

| Deveneter                      | Question        | Rat                  | ing                      | l lasit | Domorko                             |

|--------------------------------|-----------------|----------------------|--------------------------|---------|-------------------------------------|

| Parameter                      | Symbol          | Min.                 | Max.                     | Unit    | Remarks                             |

| Input power voltage            | VI              | -26.0/N              | V <sub>DD</sub> + 0.3    | V       | N = Boost time<br>Vı pin            |

| Input pin voltage              | V <sub>1</sub>  | V <sub>I</sub> – 0.3 | V <sub>DD</sub> + 0.3    | V       | POFF1, POFF2, TC1, TC2 and FC pins  |

| Output pin voltage 1           | Voc1            | Vı – 0.3             | Vdd + 0.3                | V       | C1P and C2P pins                    |

| Output pin voltage 2           | Voc2            | 2 × VI – 0.3         | VI + 0.3                 | V       | C1N pin                             |

| Output pin voltage 3           | Vосз            | 3 × VI – 0.3         | 2 × VI + 0.3             | V       | C2N pin                             |

| Output pin voltage 4           | Voc4            | $4 \times VI - 0.3$  | 3 × VI + 0.3             | V       | C3N pin                             |

| Regulator input power voltage  | V <sub>RI</sub> | $N 	imes V_I - 0.3$  | V <sub>DD</sub> + 0.3    | V       | N = Boost time, V <sub>RI</sub> pin |

| Regulator input pin voltage    | Vrv             | N 	imes VI - 0.3     | Vdd + 0.3                | V       | N = Boost time, RV pin              |

| Output voltage                 | Vo              | $N 	imes V_I - 0.3$  | V <sub>DD</sub> + 0.3    | V       | N = Boost time<br>Vo and VREG pins  |

| Input current                  | li              |                      | 80                       | mA      | Vı pin                              |

| Output current                 | lo              |                      | N ≤ 4: 20<br>N > 4: 80/N | mA      | N = Boost time<br>Vo and VREG pins  |

| Allowable loss                 | Pd              |                      | 210                      | mW      | Ta ≤ 25°C                           |

| Operating temperature          | Topr            | -30                  | 85                       | °C      |                                     |

| Storage temperature            | Tstg            | -55                  | 150                      | °C      |                                     |

| Soldering temperature and time | Tsol            |                      | 260 • 10                 | °C•S    | At leads                            |

Notes: 1. An operation exceeding the above absolute maximum ratings may cause a malfunction or permanent damage of devices. The device reliability may drop excessively even if the devices temporarily operate normally.

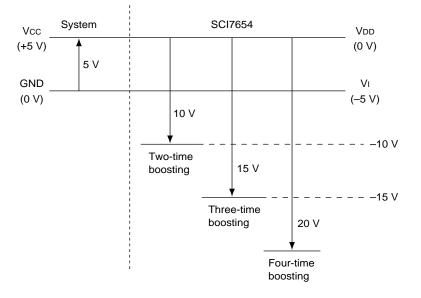

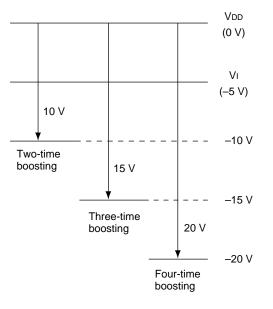

Electrical potential to peripheral systems: The SCI7654 common power supply has the highest potential (VDD). The electrical potential given by this specification is based on VDD = 0 V. Take care to avoid a potential problem during connection to a peripheral system.

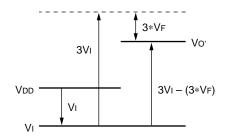

### Figure 2.3 Potential relationship

# ELECTRICAL CHARACTERISTICS

### Table 2.3 DC characteristics (1)

| Та | $= -30^{\circ}Ct$ | to +85°C, | VDD = 0 | ) V, | VI = - | -5.0 | V   |

|----|-------------------|-----------|---------|------|--------|------|-----|

|    |                   |           | 11000   | oth  |        | mot  | a d |

| Parameter                       | Symbol | Characteristics                             | Min.                                                                                            | Тур. | Max. | Unit |

|---------------------------------|--------|---------------------------------------------|-------------------------------------------------------------------------------------------------|------|------|------|

|                                 |        | N = Boost time if CT0 is selected           | -22/N                                                                                           |      | -2.4 | V    |

| Input power voltage             | VI     | N = Boost time if CT1 is selected           | -22/N                                                                                           |      | -2.4 | V    |

|                                 | VI     | N = Boost time if CT2 is selected           | -22/N                                                                                           |      | -2.4 | V    |

|                                 |        | N = Boost time if CT3 is selected           | CT2 is selected $-22/N$ $-2.4$ VCT3 is selected $-22/N$ $-2.4$ VC = VDD during $-22/N$ $-2.4$ V |      |      |      |

| Boost start input power voltage | Vsta   | N = Boost time, FC = VDD during no loading  | -22/N                                                                                           |      | -2.4 | V    |

| Boost output voltage            | Vo     |                                             | -22                                                                                             |      |      | V    |

| Regulator input voltage         | Vri    |                                             | -22                                                                                             |      | -2.4 | V    |

| Regulator output voltage        | Vreg   | Ireg = 0, Vri = $-22$ V<br>Rrv = $1M\Omega$ |                                                                                                 |      | -2.4 | V    |

# Table 2.3 DC characteristics (2)

| $Ta = -30^{\circ}C$ to $+85^{\circ}C$ , $VDD = 0$ V, $VI = -5.0$ V |

|--------------------------------------------------------------------|

| unless otherwise noted                                             |

| Parameter                                                                                                                                                    | Symbol    | Characteristics                                                                                                                                                                                                                      | Min. | Тур. | Max. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Boost output impedance                                                                                                                                       | Ro        | IO = 10 mA, VI = $-5.0$ V during<br>4-time boosting<br>C1, C2, C3, CO = 10 $\mu$ F (tantalum)                                                                                                                                        |      | 200  | 300  | Ω    |

| Boost output impedance Boost power conversion efficiency Booster operation current consumption 1 Booster operation current consumption 2 Regulator operation | K         | Io = 10 mA, VI = $-3.0$ V,<br>Ta = 25°C during 4-time boosting<br>C1, C2, C3, Co = 10 $\mu$ F (tantalum)                                                                                                                             |      | 250  | 300  | Ω    |

| Boost power conversion                                                                                                                                       | Peff      | IO = 2 mA, VI = $-5.0$ V during<br>4-time boosting<br>C1, C2, C3, CO = 10 $\mu$ F (tantalum)                                                                                                                                         |      | 95   |      | %    |

|                                                                                                                                                              | T GI      | Io = 2 mA, VI = $-3.0$ V, Ta = $25^{\circ}$ C<br>during 4-time boosting<br>C1, C2, C3, Co = $10 \mu$ F (tantalum)                                                                                                                    |      | 94   |      | %    |

| Booster operation current                                                                                                                                    | lopr1     | $\label{eq:FC} \begin{array}{l} FC = V_{DD}, \ \overline{POFF1} = V_{I}, \ \overline{POFF2} = V_{DD}, \\ V_{I} = -5.0 \ V \ during \ no \ loading \\ C1, \ C2, \ C3, \ Co = 10 \ \mu F \ (tantalum) \end{array}$                     |      | 130  | 220  | μΑ   |

|                                                                                                                                                              | торгт     | $\label{eq:FC} \begin{array}{l} FC = V_{DD}, \ \overline{POFF1} = V_{I}, \ \overline{POFF2} = V_{DD}, \\ V_{I} = -3.0 \ V, \ Ta = 25^{\circ}C \ during \ no \ loading \\ C1, \ C2, \ C3, \ Co = 10 \ \mu F \ (tantalum) \end{array}$ |      | 90   | 150  | μA   |

| Booster operation current                                                                                                                                    | lopr2     | $\label{eq:FC} \begin{array}{l} FC = VI, \ \overline{POFF1} = VI, \ \overline{POFF2} = VDD, \\ VI = -5.0 \ V \ during \ no \ loading \\ C1, \ C2, \ C3, \ Co = 10 \ \muF \ (tantalum) \end{array}$                                   |      | 520  | 880  | μA   |

| consumption 2                                                                                                                                                | lopr2     | $\label{eq:FC} \begin{array}{l} FC = VI, \ \overline{POFF1} = VI, \ \overline{POFF2} = VDD, \\ VI = -3.0 \ V, \ Ta = 25^\circ C \ during \ no \ loading \\ C1, \ C2, \ C3, \ Co = 10 \ \muF \ (tantalum) \end{array}$                |      | 360  | 600  | μA   |

| Regulator operation<br>current consumption                                                                                                                   | Iopvr     | $V_{RI} = -20 V$ , $R_{RV} = 1 M\Omega$ during no loading                                                                                                                                                                            |      | 10   | 15   | μA   |

| Static current                                                                                                                                               | lq        | $\overline{POFF1} = VI, \overline{POFF2} = VI$<br>FC = VDD                                                                                                                                                                           |      |      | 5.0  | μΑ   |

| Input leakage current                                                                                                                                        | ILI       | Pins used: POFF1, POFF2, FC, TC1, TC2                                                                                                                                                                                                |      |      | 0.5  | μA   |

| Regulated output saturation resistance                                                                                                                       | RSAT (*1) | 0 < IREG < 20 mA<br>Rv = VDD<br>Ta = 25°C                                                                                                                                                                                            |      | 10   | 20   | Ω    |

| Regulated output voltage stability                                                                                                                           | ΔVR (*2)  | -20 V < VRI < -10 V, IREG = 1 mA<br>VREG = -9 V<br>Ta = 25°C                                                                                                                                                                         |      |      | 0.2  | %/V  |

### Table 2.3DC characteristics (3)

$Ta = -30^{\circ}C$  to  $+85^{\circ}C$ , VDD = 0 V, VI = -5.0 V unless otherwise noted

| Parameter                                    | Symbol   | Characteristics                                                     | Min.   | Тур.  | Max.   | Unit |

|----------------------------------------------|----------|---------------------------------------------------------------------|--------|-------|--------|------|

| Regulated output load variation              | ΔVo (*3) | VRI = -20 V, VREG = -15 V,<br>Ta = 25°C setup<br>0 < IREG < 20 mA   |        | 30    | 50     | mV   |

|                                              | VREF0    | TC1 = VDD, TC2 = VDD                                                | -1.55  | -1.50 | -1.45  | V    |

| Reference voltage                            | VREF1    | TC1 = VDD, TC2 = VI                                                 | -1.70  | -1.50 | -1.30  | V    |

| (Ta = 25°C)                                  | VREF2    | TC1 = VI, TC2 = VDD                                                 | -1.90  | -1.50 | -1.10  | V    |

|                                              | VREF3    | TC1 = VI, TC2 = VI                                                  | -2.15  | -1.50 | -0.85  | V    |

|                                              | CT0      | TC1 = VDD, TC2 = VDD, SSOP product                                  | -0.07  | -0.04 | 0      | %/°C |

| Reference voltage<br>temperature coefficient | CT1      | TC1 = VDD, TC2 = VI, SSOP product                                   | -0.25  | -0.15 | -0.07  | %/°C |

| (*4, *5)                                     | CT2      | TC1 = VI, TC2 = VDD, SSOP product                                   | -0.45  | -0.35 | -0.20  | %/°C |

|                                              | CT3      | TC1 = VI, TC2 = VI, SSOP product                                    | -0.75  | -0.55 | -0.30  | %/°C |

| Input voltage level                          | VI       | VI = $-2.4$ to $-5.5$ V<br>Pins used: POFF1, POFF2, FC,<br>TC1, TC2 | 0.2 Vi |       |        | V    |

| input voltage level                          | VIL      | VI = $-2.4$ to $-5.5$ V<br>Pins used: POFF1, POFF2, FC,<br>TC1, TC2 |        |       | 0.8 Vi | V    |

| Booster capacitance                          | CMAX     | Capacitors used: C1, C2 and C3                                      |        |       | 47     | μF   |

\*1 RSAT =  $\frac{\Delta (VREG - VRI)}{\Delta IREG}$

\*2

$$\Delta V_{R} = \frac{V_{REG} (V_{RI} = -20 \text{ V}) - V_{REG} (V_{RI} = -10 \text{ V})}{\Delta V_{RI} \bullet V_{REG} (V_{RI} = -10 \text{ V})}$$

\*3

$$\Delta Vo = \frac{VREG (IREG = 20 \text{ mA}) - VREG (IREG = 0 \text{ mA})}{\Delta IREG}$$

\*4 CT =

$$\frac{|V_{\text{REF}}(50^{\circ}\text{C})| - |V_{\text{REF}}(0^{\circ}\text{C})|}{50^{\circ}\text{C} - 0^{\circ}\text{C}} \times \frac{100}{|V_{\text{REF}}(25^{\circ}\text{C})|}$$

\*5 The reference voltage and temperature coefficient of the chip products may vary depending on the moldings used on each chip. Use these chips only after the temperature test.

### Table 2.4 AC characteristics

| Parameter                  | Symbol | Characteristics                     |                        |      | Тур. | Max. | Unit |

|----------------------------|--------|-------------------------------------|------------------------|------|------|------|------|

| Internal clock frequency 1 | fCL1   | $\frac{FC = VDD,}{POFF1} = VI$      | Ta = 25°C              | 3.0  | 4.0  | 6.0  | kHz  |

|                            |        | POFF2 = VDD<br>Pin used: C1P        | Ta = -30°C<br>to +85°C | 2.0  | 4.0  | 7.0  | kHz  |

| Internal clock frequency 2 | fCL2   | FC = VI,<br>$\overline{POFF1} = VI$ | Ta = 25°C              | 12.0 | 16.0 | 24.0 | kHz  |

|                            |        | POFF2 = VDD<br>Pin used: C1P        | Ta = −30°C<br>to +85°C | 8.0  | 16.0 | 28.0 | kHz  |

VDD = 0 V and VI = -5.0 Vunless otherwise noted

# **EXPLANATION OF FUNCTIONS**

### **Clock Generator Circuit**

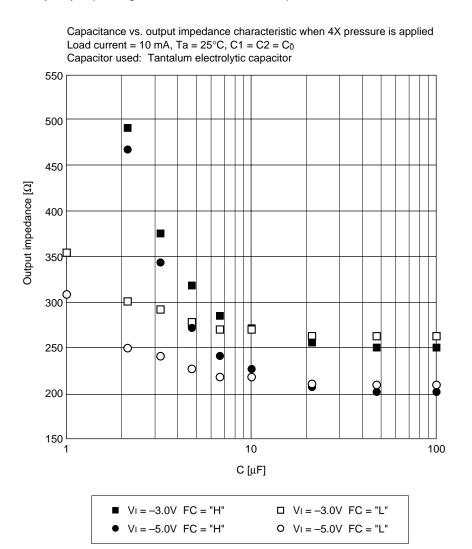

As the SCI7654 has a built-in clock generator circuit, no more parts are required for voltage boost control. The clock frequency changes according to the FC pin voltage level as defined on Table 2.5. Low Output mode or High Output mode is selectable. This allows frequency selection according to the used capacitance and load current as the boost output impedance changes depending on the clock frequency and external booster capacitance. However, the High Output mode has the current consumption approximately four times larger than the Low Output mode.

Table 2.5 FC pin setup

|         |             |                 |                     | Charao            | teristics           |                |  |

|---------|-------------|-----------------|---------------------|-------------------|---------------------|----------------|--|

| FC pin  | Mode        | Clock frequency | Current consumption | Output ripple     | Output<br>impedance | Capacitance    |  |

| H (Vdd) | Low Output  | 4.0 kHz (Typ.)  | IOP (*1)            | Vrr (*2)          | See Figure A1.      | See Figure A1. |  |

| L (VI)  | High Output | 16.0 kHz (Typ.) | IOP × Approx. 4     | VRI × Approx. 1/4 | See Figure A1.      | See Figure A1. |  |

\*1 See the DC characteristics table for current consumption.

\*2 See Section Page 2-32 for the output ripple definition and calculation.

Figure A1 Characteristic chart: Capacitance vs. output impedance when 4X pressure is applied NOTE: This characteristic chart simply indicates an approximate trend in the characteristics, which may vary depending on evaluation environment, parts used, and other factors.

### Voltage Converter

The voltage converter, consisting of a boost control circuit and a voltage converter circuit, receives clocks from the clock generator circuit and boosts the input power voltage (VI) four, three or two times. During four-time boosting, however, the three-time and twotime boost outputs cannot be obtained simultaneously. Figure 2.4 gives the potential relationship during four-, three- and two-time boosting. The C2P pin is also used as the master clock output during parallel connection.

Figure 2.4 Electrical potentials during boosting (at -5V input)

Caution:

• When connecting a capacitor to the C1P, C2P, C1N, C2N, C3N, or Vo pin for voltage conversion, close the capacitor to the IC package as much as possible to minimize the wiring length.

### **Reference Voltage Circuit**

The SCI7654 has a built-in reference voltage circuit for voltage regulation. The regulated voltage (explained in the next "voltage regulator circuit" section) is set depending on the division ratio between this reference voltage and the external resistance. The reference voltage can be used to change the temperature coefficient at pins TC1 and TC2. One of four states can be selected as listed on Table 2.6.

Table 2.6 Setup of reference voltage and temperature coefficient

|      | TC1<br>(H = V <sub>DD</sub> ) | TC2<br>(H = V <sub>DD</sub> ) | Refe  | erence volt<br>VREF (V) | age,  |       | rature coe<br>CT (%/°C) | ,     |

|------|-------------------------------|-------------------------------|-------|-------------------------|-------|-------|-------------------------|-------|

| Mode | (L = VI)                      | (L = VI)                      | Min.  | Тур.                    | Max.  | Min.  | Тур.                    | Max.  |

| CT0  | Н                             | Н                             | -1.55 | -1.5                    | -1.45 | -0.07 | -0.04                   | 0     |

| CT1  | Н                             | L                             | -1.70 | -1.5                    | -1.30 | -0.25 | -0.15                   | -0.07 |

| CT2  | L                             | Н                             | -1.90 | -1.5                    | -1.10 | -0.45 | -0.35                   | -0.20 |

| CT3  | L                             | L                             | -2.15 | -1.5                    | -0.85 | -0.75 | -0.55                   | -0.30 |

Notes: 1. The reference voltage is given at  $Ta = 25^{\circ}C$ .

2. The reference voltage and temperature coefficient of the chip products may vary depending on the moldings used on each chip. Use these chips only after the temperature test.

The temperature coefficient (CT) is defined by the following equation. The negative sign of the temperature coefficient (CT) means that the |VREF| value decreases when the temperature rises.

$$CT = \frac{|V_{REF} (50^{\circ}C)| - |V_{REF} (0^{\circ}C)|}{50^{\circ}C - 0^{\circ}C} \times \frac{100}{|V_{REF} (25^{\circ}C)|}$$

Notes on TC1 and TC2 pin replacement:

• When replacing the TC1 and TC2 pins after power-on, always select the power-off mode ( $\overline{POFF1} = \overline{POFF2} = VI$ ) and replace them by each other.

### Voltage Regulator Circuit

The voltage regulator circuit regulates a voltage entered in the VRI pin and can output any voltage. It uses the series voltage regulation. As shown in Figure 2.5, the VRI and VO pins must be short-circuited by a jumper as short as possible except for larger time boosting by using external diodes.

As shown by equation (1), any output voltage can be set by the ratio of external division resistors R1 and R2. The sum of division resistance is recommended to be small as possible to avoid an external noise interference. As the current consumed by division resistors (equation (2)) flows, the 100 ohms to 1M ohms are recommended to use.

The temperature coefficient of the regulated voltage is equal to the temperature coefficient of the reference voltage that is explained in the "reference voltage circuit" section.

### Figure 2.5 VREG setup and mounting notes

Setup:

• Relationship between VREG and reference voltage

$$V_{REG} = \frac{R1 + R2}{R1} \times (\text{Reference voltage}) \qquad \qquad \bullet \bullet \bullet \bullet \text{Equation (1)}$$

• Current consumption of division resistors

$$I_{REG} = \frac{|V_{REG}|}{R1 + R2} \qquad \qquad \bullet \bullet \bullet \bullet \text{Equation (2)}$$

Setup example:

• To output VREG = -18 V by four-time boosting if VI = -5 V and VO = -20 V

First, determine the total resistance of division resistors R1 and R2. If the current consumption is assumed to be 20  $\mu$ A, the total resistance can be obtained from equation (2) as follows:

$R1+R2=12V\div 20~\mu A=900~k\Omega$

If the reference voltage is -1.5 V, the division resistance ratio can be obtained from equation (1) as follows:

$(R1 + R2) / R2 = (-18 \text{ V}) \div (-1.5 \text{ V}) = 12$

Therefore, R1 and R2 are:

$\begin{array}{l} R1=75 \ k\Omega \\ R2=825 \ k\Omega \end{array}$

Changing the temperature coefficient:

• The temperature coefficient of the regulated voltage depends on the temperature coefficient of the reference voltage (if the division ratio of setup resistors does not depend on the temperature). It is necessary to change the temperature coefficient using thermistors, resistors or others to set any other temperature coefficient of the regulated voltage. The following explains how to calculate the VREG voltage in temperature T.

$$V_{REG}(T) = \left\{ 1 + \frac{C_{TR2} \times R2 (T0)}{C_{TR1} \times R1 (T0)} \right\} \times C_{TREF} \times (T - T0) \times V_{REF} (T0) \qquad \bullet \bullet \bullet \bullet \text{ Equation (3)}$$

| T0        | : 25°C                                                                |

|-----------|-----------------------------------------------------------------------|

| CTR1      | : Temperature coefficient of resistor R1 (Ratio to the value at 25°C) |

| CTR2      | : Temperature coefficient of resistor R2 (Ratio to the value at 25°C) |

| CTREF     | : Temperature coefficient of internal reference voltage (%/°C)        |

| R1 (T0)   | : R1 value ( $\Omega$ ) at 25°C                                       |

| R2 (T0)   | : R2 value ( $\Omega$ ) at 25°C                                       |

| VREF (T0) | : Internal reference voltage (V) at 25°C                              |

If the temperature coefficient of R1 and R2 is identical in equation (3), the VREG voltage depends on the temperature coefficient of internal reference voltage only.

Application notes on voltage regulator circuit:

- To satisfy the absolute maximum ratings of the SCI7654, the setup resistor(s) must be inserted between VDD and VREG pins of the SCI7654 that uses the voltage regulator. The SCI7654 IC itself may be degraded or destroyed if the R1 resistor is connected to pin VDD of SCI7654 that does not use the regulator during serial connection.

- The regulation voltage adjustment input (pin RV) has the very high input impedance, and its noise insertion can drop the regulator stability. As shown in Figure 2.5, shield the cable between the division resistor and RV pin or use a cable as short as possible between them.

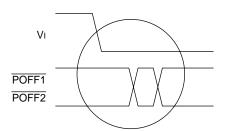

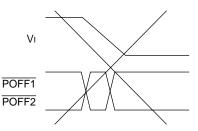

### **Power-off Control Function**

The SCI7654 has the power-off function and turns on or off each circuit function when control signals are entered in the POFF1 and POFF2 pins from an external system (such as microprocessor) as defined on Table 2.7. This power-off function can also cut the reactive

current in parallel connection and other application circuits.

To use the dual-state, power-off control (all ON and all OFF states) only, connect pin POFF2 to pin VI and use only pin POFF1 for power-off control.

| $\square$ | POFF1<br>(H = V <sub>DD</sub> )<br>(L = V <sub>I</sub> ) | POFF2<br>(H = V <sub>DD</sub> )<br>(L = V <sub>I</sub> ) | Functions  |                    |                      |                                                                |

|-----------|----------------------------------------------------------|----------------------------------------------------------|------------|--------------------|----------------------|----------------------------------------------------------------|

| Mode      |                                                          |                                                          | Oscillator | Booster<br>circuit | Regulator<br>circuit | Applications                                                   |

| PS1       | Н                                                        | L                                                        | On         | On                 | On                   | All circuits are turned on.                                    |

| PS2       | L                                                        | L                                                        | Off        | Off (*1)           | Off (*2)             | All circuits are turned off.                                   |

| PS3       | н                                                        | Н                                                        | Off        | On                 | On                   | Slave unit side of parallel connection (Booster and regulator) |

| PS4       | L                                                        | Н                                                        | On         | On                 | Off                  | Master unit side of parallel connection (Booster only)         |

Table 2.7 Available combination of power-off control

\*1 When the booster circuit is off, approximately VI + 0.6 V voltage appears at Vo pin.

\*2 When the regulator is off, the VREG pin becomes high-impedance state.

Application notes on power-off function:

• When using external system signals for power-on control, start to control the power only when VI voltage becomes stable after power-on. Unstable VI voltage may destroy the IC permanently during on/off control.

### Figure 2.6 Start timing of power-off control

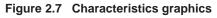

# **CHARACTERISTICS GRAPHICS**

# **APPLICATION CIRCUIT EXAMPLES**

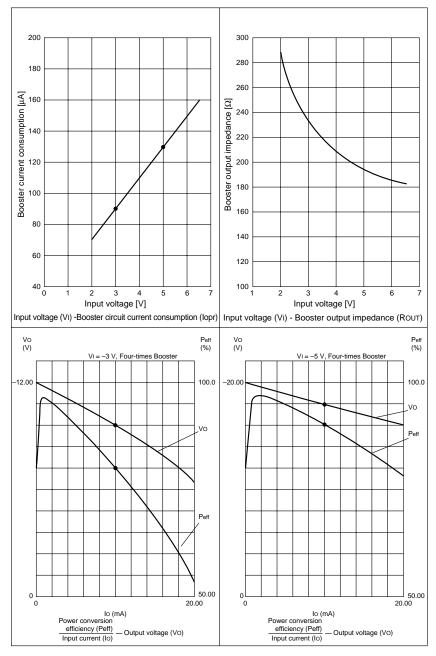

### Four-time Booster and Regulator

Figure 2.8 gives a wiring example of four-time booster and regulator that is the typical SCI7654 application. This example boosts the input voltage (VI) four times in negative direction, and outputs the regulated voltage at  $\ensuremath{\mathsf{VREG}}$  pin.

Setup conditions of Figure 2.8

- Internal clock : On (Low Output mode)

- Booster circuit : On

- Regulator : On (if  $CT = -0.04\%/^{\circ}C$ )

- ♦ Power-off procedure

- Set the  $\overline{POFF1}$  pin to logical low (VI) to turn off all circuits.

- ♦ Regulator

• For the regulator setup and notes, see the "voltage regulator circuit" section.

♦ Application in other setup conditions

- (1) When used in the High Output mode

- Connect the FC pin to the VI pin.

- (2) When changing the temperature coefficient (CT)

- Change the TC1 and TC2 pin setup by following the definition of Table 2.7.

appearing at the Vo pin may contain ripple components.

Figure 2.9 gives a wiring example.

### 4-time Booster

Only the booster circuit operates, and it boosts the input voltage (VI) four times in negative direction and outputs it at the Vo pin. As the regulator is not used, the voltage

Figure 2.9 Wiring example of 4-time booster

♦ Setup conditions of Figure 2.9

- Internal clock : On (Low Output mode)

- Booster circuit : On

- Regulator : Off

### ♦ Power-off procedure

• Set the  $\overline{POFF2}$  pin to low (VI) to turn off all circuits.

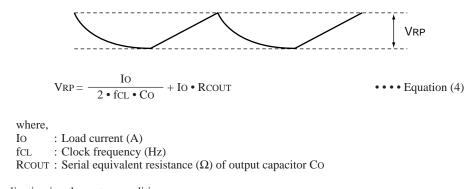

◊ Ripple voltage

• As the output at Vo pin is unstable, it can contain ripple components as shown in Figure 2.10. The ripple voltage (VRP) increases according to the load current, and it can roughly be calculated by equation (4).

### Figure 2.10 Ripple waveforms

♦ Application in other setup conditions

(1) When used in the High Output mode

• Connect the FC pin to the VI pin.

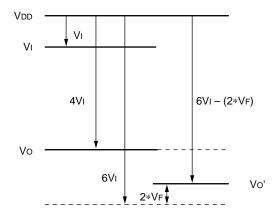

### Parallel Connection (for Increased Boosting)

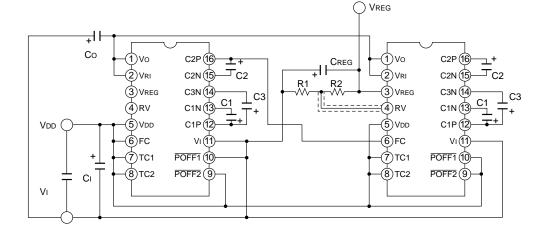

The parallel connection is useful for reduction of booster output impedance or reduction of ripple voltage. In the parallel connection of "n" lines, the booster output impedance can be reduced to approximately "1/ n". Only the smoothing capacitor (CO) for booster output can be used commonly in the parallel connection. When using the regulator, use only one of "n" SCI7654 chips which are in parallel connection. (If multiple regulators are operated in parallel mode, the reactive current consumption occurs.) Figure 2.11 gives a wiring example of 4-time booster and regulator where two SCI7654's are parallelly connected.

### Figure 2.11 Parallel connection example

Setup conditions of Figure 2.11

- First stage

- Internal clock : On (Low Output mode)

- Booster circuit : On : Off

- Regulator

- Second stage

- Internal clock : Off • Booster circuit : On

- - Regulator : On (if  $CT = -0.04\%/^{\circ}C$ )

- ♦ Power-off procedure

- In Figure 2.11, when the POFF2 pin of the first-stage SCI7654 is set to low (VI), voltage boosting is stopped at the first and second stages. However, the regulator at the second stage does not stop. Therefore, the voltage that is approximately VI appears at VREG pin during |VREG| > |VI| setup.

- To set the VREG pin to high-impedance state, set both POFF1 and POFF2 pins to low at the first and second stages.

- ♦ Application in other setup conditions

- (1) When used in the High Output mode

- Connect the FC pin of the first-stage SCI7654 to the VI pin.

- (2) When changing the temperature coefficient (CT)

- Change the TC1 and TC2 pin setup by following the definition of Table 2.7.

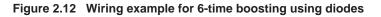

### Larger Time Boosting Using Diodes

The SCI7654 can be configured to have the five-time or larger voltage boosting and regulation by adding external diodes. As the booster output impedance increases due to the diode forward voltage drop (VF), the diodes having a smaller VF are recommended to use.

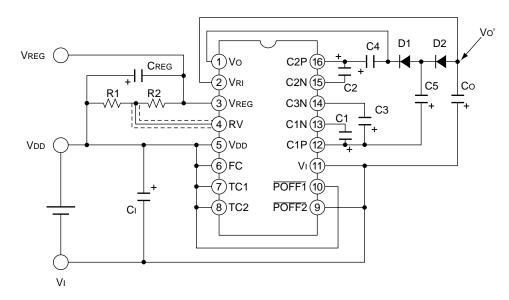

Figure 2.12 gives a wiring example of 6-time booster and regulator that use two diodes. The wiring between Vo and VRI must be minimal. Figure 2.13 provides the potential relationship.

Setup conditions of Figure 2.12

- Internal clock : On (Low Output mode)

- Booster circuit : On

- Regulator : On (if  $CT = -0.04\%/^{\circ}C$ )

### Figure 2.13 Potential relationship during 6-time boosting using diodes

♦ Power-off procedure

• Set the POFF1 pin to low (VI) to turn off all circuits.

♦ Output voltages

• When diodes are used for voltage boosting, the characteristics of diodes directly affect on the voltage boosting characteristics. The forward voltage drop (VF) of diodes can reduce the booster output voltage. As the example of Figure 2.12 uses two diodes, the drop of "VF" voltage multiplied by two occurs as shown in Figure 2.13. The booster output voltage is expressed by equation (5).

To increase the |VO'| value, use the diodes having a smaller VF.

$$|$$

Vo'  $|$  = 6 ×  $|$  VI  $|$  - 2 × VF

•••• Equation (5)

### ♦ Notes

① Input and output current conditions

To satisfy the input and output current ratings, limit the total current does not exceed the rated input current. The total current means the total boost time multiplied by the output load current. The example of Figure 2.12 has the maximum load current of 13.3 mA (= 80 mA divided by 6).

(2) Input and output voltage conditions

To satisfy the input and output voltage ratings, take care not to violate the electric potential relationship of higher time boosting using diodes. The example of Figure 2.12 must have the "VI" that can satisfy the input voltage conditions during 6-time boosting (see Table 2.3).

- ♦ Application in other setup conditions

- (1) When used in the High Output mode

- Connect the FC pin to the  $\hat{VI}$  pin.

- When changing the temperature coefficient (CT) Change the TC1 and TC2 pin setup by following the definition of Table 2.7.

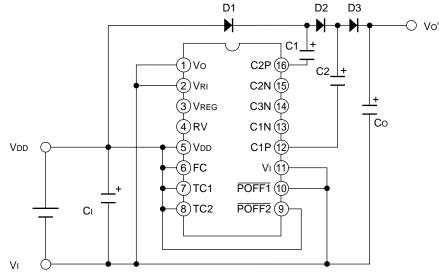

### **Positive Voltage Conversion**

The SCI7654 can also boost up a voltage to the positive potential using external diodes. In such case, however, the regulator function is unavailable. Figure 2.14 gives

a wiring example for three-time positive boosting, and Figure 2.15 provides its electrical potential relationship.

### Figure 2.14 Wiring example of positive voltage conversion (3-time boosting)

### ♦ Setup conditions of Figure 2.14

- Internal clock : On (Low Output mode)

- Booster circuit : On

- Regulator : Off

### Figure 2.15 Potential relationship during positive voltage conversion (3-time boosting)

♦ Power-off procedure

• Set the  $\overline{POFF2}$  pin to low (VI) to turn off all circuits.

### ♦ Two-time boosting

• To boost up a voltage two times, remove capacitor C1 and diode D1 of Figure 2.14, and connect the anode of diode D2 to the VDD pin.

♦ Output voltages

• When diodes are used for voltage boosting, the characteristics of diodes directly affect on the voltage boosting characteristics. The forward voltage drop (VF) of diodes can reduce the booster output voltage. As the example of Figure 2.14 uses three diodes, the drop of "VF" voltage multiplied by three occurs. The booster output voltage is expressed by equation (5).

To increase the |Vo'| value, use the diodes having a smaller VF.

$$|VO'| = 3 \times |VI| - (3 \times VF)$$

•••• Equation (6)

♦ Notes

① Input and output current conditions

To satisfy the input and output current ratings, take care to limit the input current below the ratings.

- (2) Input and output voltage conditions

- During forward voltage conversion, the input voltage ratings are the same as two-time negative voltage boosting (see Table 2.3).

- ♦ Application in other setup conditions

When used in the High Output mode, connect the FC pin to the VI pin.

# Wiring Example When Changing the Regulator Temperature Coefficient

The temperature coefficient of the regulator depends on the temperature coefficient of the internal reference voltage. To set another temperature coefficient, use a thermistor resistor or others as shown in Figure 2.16.

### Figure 2.16 Wiring example when changing the regulator temperature coefficient

- ♦ Setup conditions of Figure 2.16

- Internal clock : On (Low Output mode)

- Booster circuit : On

- Regulator : On

- Thermistor resistor : RT

♦ Power-off procedure

• Set the  $\overline{POFF1}$  pin to low (VI) to turn off all circuits.

♦ Regulator temperature coefficient

- For the regulator setup and notes, see the "voltage regulator circuit" section of the function.

- The thermistor resistor (RT) has the non-linear temperature characteristics. To correct them to the linear characteristics, insert the RP as shown Figure 2.16.

♦ Application in other setup conditions

• When used in the High Output mode, connect the FC pin to the VI pin.