# SED1225 Series LCD Controller/Drivers

**Technical Manual**

## Contents

| OUTLINE                                  |

|------------------------------------------|

| FEATURES                                 |

| BLOCK DIAGRAM                            |

| PIN ASSIGNMENT                           |

| PIN DESCRIPTION                          |

| FUNCTION DESCRIPTION                     |

| COMMAND                                  |

| COMMAND LIST                             |

| BUILT-IN MEMORIES                        |

| MAXIMUM ABSOLUTE RATINGS                 |

| DC CHARACTERISTICS                       |

| SIGNAL TIMING CHARACTERISTICS            |

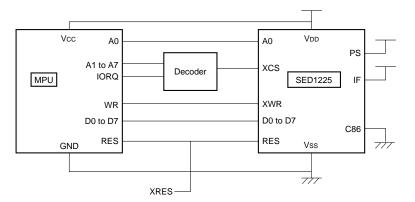

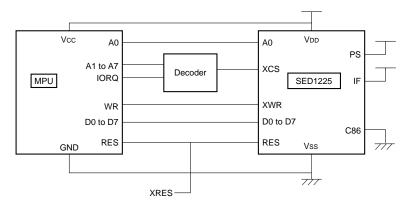

| MPU INTERFACES (REFERENCE)               |

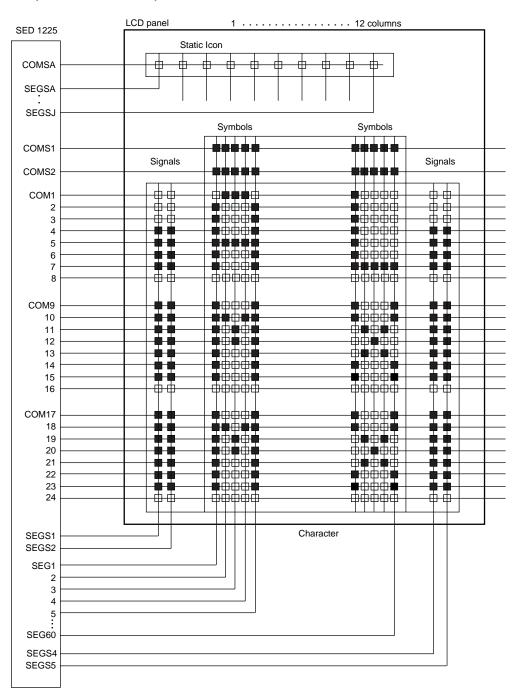

| LCD CELL INTERFACE                       |

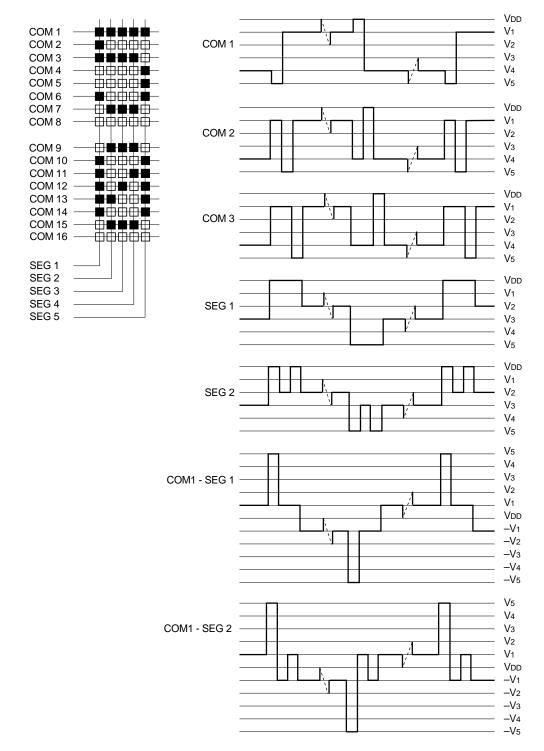

| LCD DRIVE WAVEFORMS (B WAVEFORMS)        |

| EXAMPLE OF INSTRUCTION SETUP (REFERENCE) |

| OPTION LIST                              |

| CAUTIONS                                 |

## OUTLINE

The SED1225 dot-matrix LCD Controller Driver receives 4-bit, 8-bit, or serial data from the microprocessor and displays up to 36 characters, four user-defined characters, and up to 120 symbols.

Up to 256 types of built-in character generator ROMs are provided. Each character font has a 5×8-dot structure. Also, the user-defined character RAM contains four 5×8-dot characters. In addition, a symbolic register can be used for flexible symbol display. The Driver featuring the very low power consumption can drive a handy terminal unit in either Sleep or Standby mode with the minimum power consumption.

## **FEATURES**

- Built-in display data RAM Can display up to 36 characters, 4 user-defined characters, and 120 symbols.

- Built-in CGROM (for 256-character display), CGRAM (for 4-character display), and symbol register (for 120 symbol display)

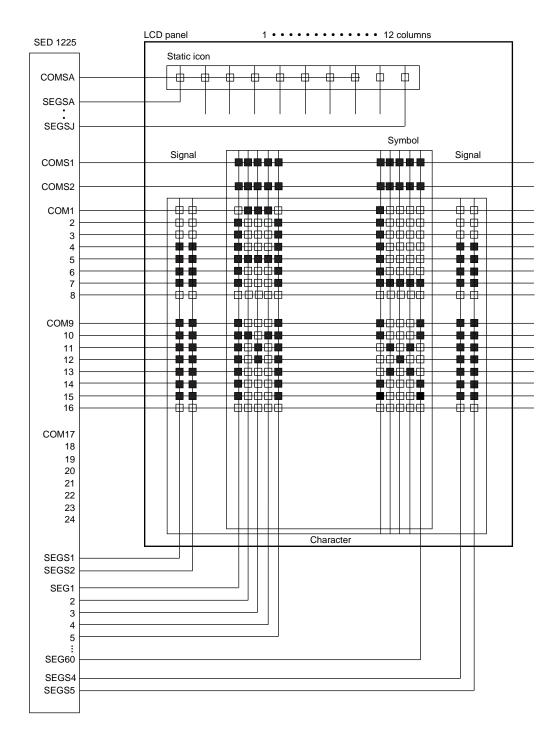

- No. of display columns by lines Normal mode: (12 columns plus 4 signal segments) × 3 line + 120 symbols + 10 static symbols Standby mode: 10 static symbols

- Built-in C&R oscillators

- Available external clock input

- High-speed MPU interfaces Interface to both 68- and 80-series MPUs Support of 4/8-bit interface

- Support of serial interface

- Character font: 5x8 dots

- Duty ratio: 1/18, 1/26

- Simple command setup

- Built-in LCD drive power circuit: Power amp and regulator

- Built-in electronic controls

- Very low power consumption 30 μA (including the operating current of the built-in power supply during normal operation) 10 μA (Static icon display during Standby operation 5 μA (Display off during Sleep operation)

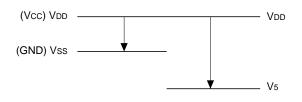

- Power supplies

VDD Vss: -1.7 to -3.6 V

VDD V5: -3.0 to -6.0 V

- Wide operating temperature range: Ta=-30 to +85°C

- CMOS process

- Package design

Chip (with gold bump): SED1225D\*B

TCP: SED1225T\*\*

- This IC package is not designed to have a radiation or strong light resistance.

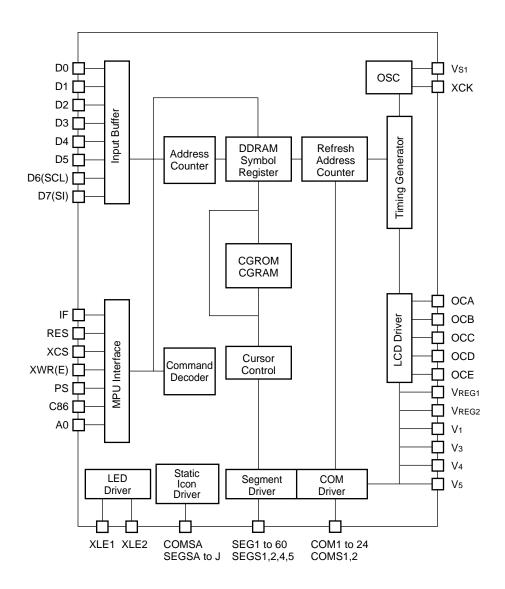

## **BLOCK DIAGRAM**

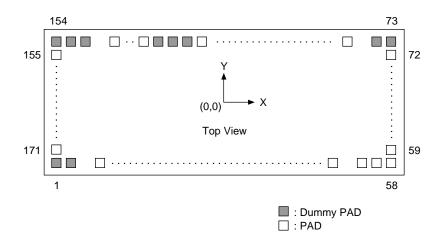

## **PIN ASSIGNMENT**

#### SED1225D\*\*\*

CGROM pattern version number

| Chip size:                  | $7.85 \times 1.97 \text{ mm}$ |

|-----------------------------|-------------------------------|

| Pad pitch:                  | 90 µm (min)                   |

| Chip thickness (Reference): | 625 µm                        |

Au bump specifications

Bump size: Pad Nos. 59 to 72, and 155 to 171: 78 μm × 59 μm Pad Nos. 1 to 58, and 73 to 154: 59 μm × 78 μm Bump height (Reference): 22.5 μm Pad coordinates (1/2)

| PAD |         | Coordinate |      | ] |     | PAD   | Coordinate |      |

|-----|---------|------------|------|---|-----|-------|------------|------|

| No. | Name    | Х          | Y    |   | No. | Name  | Х          | Y    |

| 1   | Dummy   | -3768      | -822 |   | 44  | Vss   | 1718       | -822 |

| 2   | Dummy   | -3678      | -822 |   | 45  | Vss   | 1808       | -822 |

| 3   | A0      | -3349      | -822 |   | 46  | C86   | 1973       | -822 |

| 4   | XWR(E)  | -3200      | -822 |   | 47  | PS    | 2122       | -822 |

| 5   | XCS     | -3050      | -822 |   | 48  | IF    | 2272       | -822 |

| 6   | D7(SI)  | -2901      | -822 |   | 49  | RES   | 2421       | -822 |

| 7   | D6(SCL) | -2751      | -822 |   | 50  | ХСК   | 2571       | -822 |

| 8   | D5      | -2602      | -822 |   | 51  | VS1   | 2720       | -822 |

| 9   | D4      | -2452      | -822 |   | 52  | (FSA) | 2893       | -822 |

| 10  | D3      | -2303      | -822 |   | 53  | (FSB) | 3065       | -822 |

| 11  | D2      | -2153      | -822 |   | 54  | (FSC) | 3237       | -822 |

| 12  | D1      | -2004      | -822 |   | 55  | (FS3) | 3409       | -822 |

| 13  | D0      | -1854      | -822 |   | 56  | (Vdd) | 3589       | -822 |

| 14  | XLE1    | -1705      | -822 |   | 57  | (Vdd) | 3678       | -822 |

| 15  | XLE1    | -1615      | -822 |   | 58  | (Vdd) | 3768       | -822 |

| 16  | XLE2    | -1466      | -822 |   | 59  | (FS2) | 3758       | -628 |

| 17  | XLE2    | -1376      | -822 |   | 60  | (FS1) | 3758       | -456 |

| 18  | Vdd     | -1286      | -822 |   | 61  | (FS0) | 3758       | -283 |

| 19  | Vdd     | -1197      | -822 |   | 62  | COMSA | 3758       | -179 |

| 20  | Vss     | -1107      | -822 |   | 63  | COMS1 | 3758       | -90  |

| 21  | Vss     | -1017      | -822 |   | 64  | COM1  | 3758       | 0    |

| 22  | V5      | -868       | -822 |   | 65  | COM2  | 3758       | 90   |

| 23  | V5      | -778       | -822 |   | 66  | COM3  | 3758       | 179  |

| 24  | V4      | -629       | -822 |   | 67  | COM4  | 3758       | 269  |

| 25  | V4      | -539       | -822 |   | 68  | COM5  | 3758       | 359  |

| 26  | V3      | -389       | -822 |   | 69  | COM6  | 3758       | 449  |

| 27  | V3      | -300       | -822 |   | 70  | COM7  | 3758       | 538  |

| 28  | V1      | -150       | -822 |   | 71  | COM8  | 3758       | 628  |

| 29  | V1      | -60        | -822 |   | 72  | COMS1 | 3758       | 718  |

| 30  | (Vreg1) | 89         | -822 |   | 73  | Dummy | 3768       | 822  |

| 31  | (Vreg1) | 179        | -822 |   | 74  | Dummy | 3678       | 822  |

| 32  | Vreg2   | 328        | -822 |   | 75  | SEGS1 | 3409       | 822  |

| 33  | Vreg2   | 418        | -822 |   | 76  | SEGS2 | 3320       | 822  |

| 34  | OCA     | 567        | -822 |   | 77  | SEG1  | 3230       | 822  |

| 35  | OCA     | 657        | -822 |   | 78  | SEG2  | 3140       | 822  |

| 36  | OCB     | 807        | -822 |   | 79  | SEG3  | 3050       | 822  |

| 37  | OCB     | 896        | -822 |   | 80  | SEG4  | 2961       | 822  |

| 38  | OCC     | 1046       | -822 |   | 81  | SEG5  | 2871       | 822  |

| 39  | OCC     | 1136       | -822 |   | 82  | SEG6  | 2781       | 822  |

| 40  | OCD     | 1285       | -822 |   | 83  | SEG7  | 2692       | 822  |

| 41  | OCD     | 1375       | -822 |   | 84  | SEG8  | 2602       | 822  |

| 42  | OCE     | 1524       | -822 |   | 85  | SEG9  | 2512       | 822  |

| 43  | OCE     | 1614       | -822 |   | 86  | SEG10 | 2423       | 822  |

Note 1: Set the pins VDD of Nos. 56 to 58 and the pins VRBG1 of Nos. 30 and 31 to the floating state.

2: Since the pins FS\* of Nos. 52 to 55 and 59 to 61 are for fuse adjustment, set them to the floating state.

Pad coordinates (2/2)

|     | PAD   | Coord | linate |     | PAD   | Coordinate |      |  |

|-----|-------|-------|--------|-----|-------|------------|------|--|

| No. | Name  | Х     | Y      | No. | Name  | Х          | Y    |  |

| 87  | SEG11 | 2333  | 822    | 130 | SEG54 | -1524      | 822  |  |

| 88  | SEG12 | 2243  | 822    | 131 | SEG55 | -1614      | 822  |  |

| 89  | SEG13 | 2153  | 822    | 132 | SEG56 | -1704      | 822  |  |

| 90  | SEG14 | 2064  | 822    | 133 | SEG57 | -1793      | 822  |  |

| 91  | SEG15 | 1974  | 822    | 134 | SEG58 | -1883      | 822  |  |

| 92  | SEG16 | 1884  | 822    | 135 | SEG59 | -1973      | 822  |  |

| 93  | SEG17 | 1795  | 822    | 136 | SEG60 | -2062      | 822  |  |

| 94  | SEG18 | 1705  | 822    | 137 | SEGS4 | -2152      | 822  |  |

| 95  | SEG19 | 1615  | 822    | 138 | SEGS5 | -2242      | 822  |  |

| 96  | SEG20 | 1526  | 822    | 139 | Dummy | -2332      | 822  |  |

| 97  | SEG21 | 1436  | 822    | 140 | Dummy | -2422      | 822  |  |

| 98  | SEG22 | 1346  | 822    | 141 | Dummy | -2512      | 822  |  |

| 99  | SEG23 | 1256  | 822    | 142 | COM24 | -2602      | 822  |  |

| 100 | SEG24 | 1167  | 822    | 143 | COM23 | -2692      | 822  |  |

| 101 | SEG25 | 1077  | 822    | 144 | COM22 | -2781      | 822  |  |

| 102 | SEG26 | 987   | 822    | 145 | COM21 | -2871      | 822  |  |

| 103 | SEG27 | 898   | 822    | 146 | COM20 | -2961      | 822  |  |

| 104 | SEG28 | 808   | 822    | 147 | COM19 | -3050      | 822  |  |

| 105 | SEG29 | 718   | 822    | 148 | COM18 | -3140      | 822  |  |

| 106 | SEG30 | 629   | 822    | 149 | COM17 | -3230      | 822  |  |

| 107 | SEG31 | 539   | 822    | 150 | COM16 | -3320      | 822  |  |

| 108 | SEG32 | 449   | 822    | 151 | COM15 | -3409      | 822  |  |

| 109 | SEG33 | 359   | 822    | 152 | Dummy | -3589      | 822  |  |

| 110 | SEG34 | 270   | 822    | 153 | Dummy | -3678      | 822  |  |

| 111 | SEG35 | 180   | 822    | 154 | Dummy | -3768      | 822  |  |

| 112 | SEG36 | 90    | 822    | 155 | COM14 | -3758      | 718  |  |

| 113 | SEG37 | 1     | 822    | 156 | COM13 | -3758      | 628  |  |

| 114 | SEG38 | -89   | 822    | 157 | COM12 | -3758      | 538  |  |

| 115 | SEG39 | -179  | 822    | 158 | COM11 | -3758      | 449  |  |

| 116 | SEG40 | -268  | 822    | 159 | COM10 | -3758      | 359  |  |

| 117 | SEG41 | -358  | 822    | 160 | COM9  | -3758      | 269  |  |

| 118 | SEG42 | -448  | 822    | 161 | COMS2 | -3758      | 179  |  |

| 119 | SEG43 | -538  | 822    | 162 | SEGSA | -3758      | 90   |  |

| 120 | SEG44 | -627  | 822    | 163 | SEGSB | -3758      | 0    |  |

| 121 | SEG45 | -717  | 822    | 164 | SEGSC | -3758      | -90  |  |

| 122 | SEG46 | -807  | 822    | 165 | SEGSD | -3758      | -179 |  |

| 123 | SEG47 | -896  | 822    | 166 | SEGSE | -3758      | -269 |  |

| 124 | SEG48 | -986  | 822    | 167 | SEGSF | -3758      | -359 |  |

| 125 | SEG49 | -1076 | 822    | 168 | SEGSG | -3758      | -449 |  |

| 126 | SEG50 | -1165 | 822    | 169 | SEGSH | -3758      | -538 |  |

| 127 | SEG51 | -1255 | 822    | 170 | SEGSI | -3758      | -628 |  |

| 128 | SEG52 | -1345 | 822    | 171 | SEGSJ | -3758      | -718 |  |

| 129 | SEG53 | -1435 | 822    |     |       |            |      |  |

## PIN DESCRIPTION

## **Power Supply Pins**

| Pin Name         | I/O          | Description                                                                                 |   |  |  |  |  |  |  |

|------------------|--------------|---------------------------------------------------------------------------------------------|---|--|--|--|--|--|--|

| Vdd              | Power supply | Connects to the logic power supply. This is common to the Vcc power pin of the MPU.         | 1 |  |  |  |  |  |  |

| Vss              | Power supply | 0V power pin connected to system ground (GND)                                               |   |  |  |  |  |  |  |

| V1, V3<br>V4, V5 | Power supply | Multi-level LCD drive power supplies. A capacitor is required for external stabilization.   | 4 |  |  |  |  |  |  |

| Vs1              | 0            | Output pin of oscillator (OSC) power voltage. Do not connect any external load to this pin. | 1 |  |  |  |  |  |  |

Notes: Two Vss pins are provided. As they are commonly connected inside the IC, an input into any Vss can be used if power impedance is low. To have the enough noise resistance, however, the Vss power input from each pin is recommended.

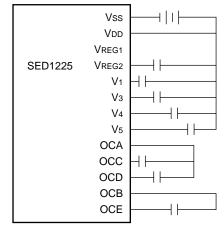

#### **LCD Power Pins**

| Pin Name                        | I/O | Description                                                                                             | No. of Pins |

|---------------------------------|-----|---------------------------------------------------------------------------------------------------------|-------------|

| Vreg2                           | 0   | Output pins of LCD voltage and amp source power supplies.<br>A capacitor is required for stabilization. | 1           |

| OCA<br>OCB<br>OCC<br>OCD<br>OCE | 0   | A voltage capacitor pin. A capacitor is required for amplification.                                     | 5           |

## **LED Drive Terminal**

| Pin Name     | I/O | Description                                                                         | No. of Pins |

|--------------|-----|-------------------------------------------------------------------------------------|-------------|

| XLE1<br>XLE2 |     | An Nch open drain output terminal to drive the LED.<br>Connects to the LED cathode. | 2           |

## System Bus Connector Pins

| Pin Name                      | I/O | Descrition                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               |                            |                             |                              |                                    |                                        |                   |                            | No. of Pins          |   |

|-------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------|------------------------------|------------------------------------|----------------------------------------|-------------------|----------------------------|----------------------|---|

|                               |     | An 8-bit inp<br>Pins D7 an<br>logical low.                                                                                                                                                 | nd D6 funct                                                                                                                                                                                                                                                                                                                                   |                            |                             |                              |                                    |                                        |                   |                            |                      |   |

|                               |     | PS C                                                                                                                                                                                       | C86 IF                                                                                                                                                                                                                                                                                                                                        | D7                         | D6                          | D5                           | D4                                 | D3 to D0                               | XCS               | A0                         | XWR                  |   |

| D7(SI)<br>D6(SCL)<br>D5 to D0 | I   | "H" "<br>"H" '                                                                                                                                                                             | — —<br>'H" "H"<br>'H" "L"<br>"L" "H"<br>"L" "L"                                                                                                                                                                                                                                                                                               | SI<br>D7<br>D7<br>D7<br>D7 | SCL<br>D6<br>D6<br>D6<br>D6 | OPEN<br>D5<br>D5<br>D5<br>D5 | OPEN<br>D4<br>D4<br>D4<br>D4<br>D4 | OPEN<br>D3-D0<br>OPEN<br>D3-D0<br>OPEN | XCS<br>XCS<br>XCS | A0<br>A0<br>A0<br>A0<br>A0 | E<br>E<br>XWR<br>XWR | 8 |

|                               |     |                                                                                                                                                                                            | y be open.<br>ter noise-re<br>y be high c                                                                                                                                                                                                                                                                                                     | esistance                  | e charac                    | teristics                    | i.                                 |                                        |                   | x to hav                   | /e                   |   |

| A0                            | I   | or commar<br>0: Indicate                                                                                                                                                                   | Usually, the most significant bit of MPU address bus is connected to identify data<br>or command.<br>0: Indicates D0 to D7 are command.<br>1: Indicates D0 to D7 are display data.                                                                                                                                                            |                            |                             |                              |                                    |                                        |                   |                            | 1                    |   |

| RES                           | I   | Initializes v                                                                                                                                                                              | vhen RES                                                                                                                                                                                                                                                                                                                                      | is set to                  | low. Th                     | ne syste                     | m is re                            | set at R                               | ES sigr           | al leve                    | Ι.                   | 1 |

| XCS                           | I   | A Chip Sel<br>This is vali                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                               |                            | dress bu                    | us signa                     | l is dec                           | oded ar                                | nd ente           | red.                       |                      | 1 |

| XWR                           | I   | Active lo<br>The WR<br>at the ris<br>- When a 6<br>Active hi                                                                                                                               | <ul> <li>When an 80-series MPU is connected<br/>Active low.</li> <li>The WR signal of 80-series MPU is connected. The data bus signal is fetched<br/>at the rising edge of XWR signal.</li> <li>When a 68-series MPU is connected<br/>Active high.</li> <li>Used as an Enable Clock input of 68-series MPU. The data bus signal is</li> </ul> |                            |                             |                              |                                    |                                        |                   |                            | 1                    |   |

|                               |     | A switching                                                                                                                                                                                | g pin betwe                                                                                                                                                                                                                                                                                                                                   | en seria                   | I data ir                   | nput and                     | paralle                            | el data i                              | nput.             |                            |                      |   |

|                               |     | P/S                                                                                                                                                                                        | Chip s                                                                                                                                                                                                                                                                                                                                        | select                     | Data/C                      | ommar                        | d D                                | Data                                   | Se                | rial Clo                   | ock                  |   |

| PS                            | I   | "H"                                                                                                                                                                                        | XC                                                                                                                                                                                                                                                                                                                                            | S                          |                             | A0                           | D0                                 | to D7                                  |                   | _                          |                      | 1 |

|                               |     | "L"                                                                                                                                                                                        | XC                                                                                                                                                                                                                                                                                                                                            | S                          |                             | A0                           |                                    | SI                                     |                   | SCL                        |                      |   |

| IF                            | I   | An interface data length select pin during parallel data input.<br>- 8-bit parallel input if IF=high<br>- 4-bit parallel input if IF=low<br>This pin is connected to Vbp or Vss if PS=low. |                                                                                                                                                                                                                                                                                                                                               |                            |                             |                              |                                    |                                        |                   | 1                          |                      |   |

| C86                           | I   | An MPU interface switch pin.<br>- 68-series MPU interface if C86=high<br>- 80-series MPU interface if C86=low<br>This pin is connected to VDD or Vss if PS=low.                            |                                                                                                                                                                                                                                                                                                                                               |                            |                             |                              |                                    |                                        |                   | 1                          |                      |   |

| хск                           | I   | It must be f                                                                                                                                                                               | An external clock input pin.<br>It must be fixed to high to use the internal oscillator.<br>To use an external clock input, turn the internal oscillator OFF by issuing the                                                                                                                                                                   |                            |                             |                              |                                    |                                        |                   |                            | he                   | 1 |

## **LCD Driver Signals**

Dynamic drive pins

| Pin<br>Name      | I/O | Description                                                                                                 | No. of<br>Pins |  |  |

|------------------|-----|-------------------------------------------------------------------------------------------------------------|----------------|--|--|

| COM1 to<br>COM24 | 0   | Common signal output pins (for character display)                                                           | 24             |  |  |

| COMS1,<br>COMS2  |     |                                                                                                             |                |  |  |

| SEG1 to<br>SEG60 | 0   | Segment signal output pins (for character display)                                                          | 60             |  |  |

| SEGS1, 2<br>4, 5 | 0   | Segment signal output pins (for non-character display)<br>SEGS1, 2, 4, 5: Segment outputs for signal output | 4              |  |  |

Note: As the same COMS1 signal is output at two pins, one of them must be used.

#### Static drive pins

| Pin<br>Name                          | I/O | Description                                  | No. of<br>Pins |

|--------------------------------------|-----|----------------------------------------------|----------------|

| COMSA                                | 0   | Common signal output pin (for icon display)  | 1              |

| SEGSA, B<br>C, D, E, F<br>G, H, I, J | 0   | Segment signal output pin (for icon display) | 10             |

Notes: We recommend to separate LCD panel electrodes of static drive pins from those of dynamic drive pins. If these patterns are closely located, the LCD and its electrodes may be deteriorated.

## FUNCTION DESCRIPTION

#### **MPU Interfaces**

#### Interface type selection

#### Table 1

| PS | Туре           | XCS | A0 | XWR  | SI | SCL | D0 to D7 |

|----|----------------|-----|----|------|----|-----|----------|

| н  | Parallel input | XCS | A0 | XWR  | -  | -   | D0 to D7 |

| L  | Serial input   | XCS | A0 | H, L | SI | SCL | _        |

The SED1225 has the C86 pin for MPU selection. If the parallel input is selected (PS=high), if can be connected directly to the 80-series or 68-series MPU by setting the

4-bit data bus can be selected by the IF pin signal.

#### Table 2

| C86 pin signal | Туре      | A0 | XWR | XCS | D0 to D7 |

|----------------|-----------|----|-----|-----|----------|

| "L"            | 80 series | A0 | XWR | XCS | D0 to D7 |

| "H"            | 68 series | A0 | E   | XCS | D0 to D7 |

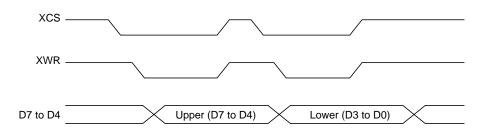

#### Interface to 4-bit MPU

If the 4-bit interface is selected (IF=low), the 8-bit command and data, and its address are transferred in two times.

Note: During continuous writing, the write time greater than the system cycle time (tcyc) must be set before the subsequent write operation.

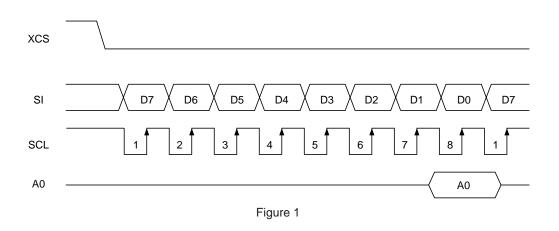

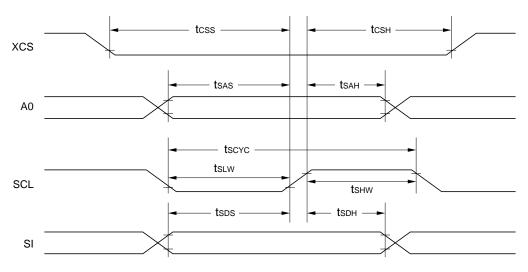

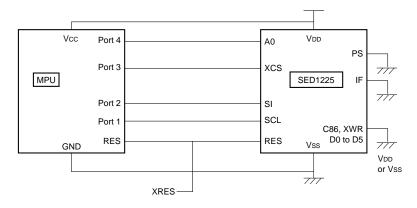

#### Serial interface

The serial interface consists of an 8-bit shift register and a 3-bit counter. During chip select (XCS=low), an SI input and an SCL input can be accepted. During no chip select (XCS=high), the shift register and counter is initialized (reset).

Serial data of D7 to D0 are fetched in this order from the serial data input pin (SI) at the rising edge of serial clock. The data is converted into 8-bit parallel data at the rising edge of the eighth serial clock.

The serial data input (SI) is identified to have the display data or command by the A0 input. It is display data if A0=high, and it is command if A0=low.

The A0 input is fetched and identified at the rising edge of " $8 \times n$ -th" serial clock (SCL). Figure 1 shows a serial interface timing chart.

The SCL signals must be well protected from the far-end reflection and ambient noise due to increased line length. The operation checkout on the actual machine is recommended.

Also, we recommend to repeat periodical command writing and status refreshing to avoid a malfunction due to noise.

## C86 pin to high or low (see Table 2). Also, the 8-bit or

The SED1225 can transfer data via the 4- or 8-bit data bus or via the serial data input (SI). The parallel or serial data

input can be selected by setting the PS pin to high or low

(see Table 1).

#### Data bus signal identification

The SED1225 identifies the data bus based on a combination of A0, AWR and E signals as defined on Table 3.

#### Table 3

| Common | 68 Series | 80 Series | Function                                    |

|--------|-----------|-----------|---------------------------------------------|

| A0     | Е         | XWR       | Function                                    |

| 1      | 1         | 0         | Writes in the RAM and symbol register.      |

| 0      | 1         | 0         | Writes (commands) in the internal register. |

#### **Chip Select**

The SED1225 has an Chip Select pin (XCS) to allow an MPU interface input only if XCS=low.

During no chip select status, all of D0 to D7, A0, XWR, SI and SCL inputs are made invalid. If the serial input interface is selected, the shift register and counter are reset.

However, the Reset signal is entered independent from the XCS status.

#### **Power Circuit**

The built-in power circuit featuring the low power

consumption generates the required LCD drive voltages. The power circuit consists of an amp and a voltage regulator.

#### Amp

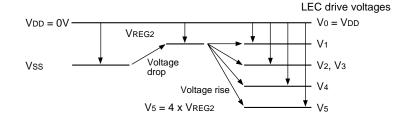

When the capacitors are connected to the OCA, OCB, OCC, OCD, OCE, VREG2 pins, the LCD drive voltages are generated.

As the amp uses the signals from the oscillator, the oscillator or an external clock must be operating. The following provides the potential relationship.

#### Voltage regulator

Voltage regulator using the electronic control function Use the electronic control function and set the voltages appropriate to the LCD panel driving.

When a 5-bit data is set in the electronic control register, one of 32-state voltages can be set for LCD driving. Before using the electronic control function, turn ON the power circuit by issuing the power control command.

The following explains how to calculate the voltages using the electronic control function.

$V_5 = 4 \times V_{\rm EV}$

Conditions: Vev = VREG2 - Xwhere,  $X = n\alpha$  (n=0, 1, ..., 31)  $\alpha = VREG2/95$

| No. | Electronic control register | Х    | V5    |

|-----|-----------------------------|------|-------|

| 0   | (0, 0, 0, 0, 0)             | 0    | Large |

| 1   | (0, 0, 0, 0, 1)             | 1α   | •     |

| 2   | (0, 0, 0, 1, 0)             | 2α   | •     |

| 3   | (0, 0, 0, 1, 1)             | 3α   | •     |

| •   | •                           | •    | •     |

| •   | •                           | •    | •     |

| 30  | (1, 1, 1, 1, 0)             | n-1α | •     |

| 31  | (1, 1, 1, 1, 1)             | nα   | Small |

This is reference voltage for the liquid crystal drive power circuit. The VREGZ has a temperature characteristics of about -0.05%/deg.

#### External unit connection examples

An external voltage regulation capacitor must be connected to the LCD power pin. The LCD drive voltages are fixed to 1/4 biasing.

1/4 bias example

Note: We recommend to display the capacitance appropriate to the LCD panel size and set up the capacitance by observing the drive signal waveforms.

Reference set value: (0.1~1.0 µF)

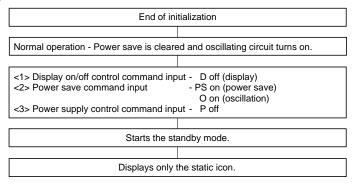

#### **Power Save mode**

The SED1225 supports the Standby and Sleep modes to save the power consumption during system idling.

Standby mode

The Standby mode is selected or released by the Power Save command. During Standby mode, only the static icon is displayed.

1. LCD display outputs

COM1 to COM16, COMS1, COMS2: VDD level

SEG1 to SEG60, SEGS1, 2, 4, 5:

VDD level

SEGSA, B, C, D, E, F, G, H, I, J, COMSA: Can light by static drive Use the Static Icon RAM to display the static icon with SEGSA, B, C, D, E, F, G, H, I, J and COMSA.

- DDRAM, CGRAM and symbol register Their write contents do not change. The contents are kept regardless of Standby mode selection or release.

- 3. The operation mode before selection of Standby mode is kept.

The internal circuits for dynamic display are stopped.

4. Oscillator

The oscillator must be turned ON for static display.

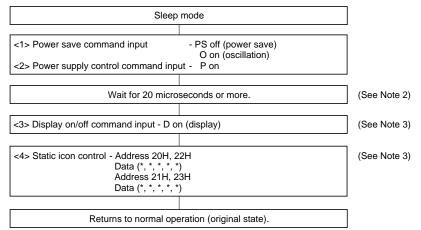

Sleep mode

To select the Sleep mode, turn OFF the power circuit and oscillator by issuing the command, and clear all data of Static Icon register to zero. Then, issue the Power Save command. The system power consumption will be minimized to almost the stopped status.

1. LCD display outputs

COM1 to COM16, COMS1, COMS2: VDD level

SEG1 to SEG60, SEGS1, 2, 4, 5: VDD level

SEGSA, B, C, D, E, F, G, H, I, J, COMSA: Clear all data of Static Icon register to zero.

- 2. DDRAM, CGRAM and symbol register Their write contents do not change. The contents are kept regardless of Standby mode selection or release.

- 3. The operation mode before selection of Standby mode is kept.

All internal circuits are stopped.

4. Oscillator

Turn OFF the built-in power supply and oscillator by issuing the Power Save and power control commands.

### **Reset Circuit**

When the RES input is made active, this LSI is initialized.

| vhen the RES inpu  | it is made active, this LSI is initi |

|--------------------|--------------------------------------|

| Initialization sta | atus                                 |

| (1) Display ON     | /OFF control                         |

| C=0:               | Cursor off                           |

| B=0:               | Blink off                            |

| DC=0:              | Normal display                       |

| D=0:               | Display off                          |

| (2) Power save     |                                      |

| O=0:               | Oscillating circuit off              |

| PS=0:              | Power save off                       |

| (3) Power control  | ol                                   |

| P=0:               | Power circuit off                    |

| (4) System set     |                                      |

| N=0:               | 3 lines                              |

| S2, S1=0:          | Direction of normal display          |

| CG=0:              | CGRAM unused                         |

| (5)Electronic co   | ontrol                               |

| Address:           | 28H                                  |

| Data:              | (0,0,0,0,0)                          |

| (6) Static icon    |                                      |

| Address:           | 20H to 23H                           |

| Data:              | (0,0,0,0,0)                          |

|                    |                                      |

| (7)LED registe | r                                |

|----------------|----------------------------------|

| Address:       | 2AH                              |

| Data:          | (0,0,0,0,0)                      |

| (8)CG RAM, I   | DD RAM and symbol register       |

| Address:       | 00H to 1FH, 30H to 7CH           |

| Data:          | Must be initialized by MPU after |

|                | reset input because of being     |

|                | indefinite.                      |

|                |                                  |

Connect the RES terminal to the MPU reset terminal as described in "6-1 MPU Interface", and execute initialization simultaneously with the MPU. However, if the MPU bus and port are put into high impedance for a certain time period by resetting, perform reset input to the SED1225 after the input to the SED1225 has been determined. When the RES terminal becomes "L", each register is cleared and the above setup is established. If initialization by the RES terminal is not performed when power voltage is applied, resetting may be disabled.

## COMMAND

Table 4 lists the supported commands. The SED1225 identifies a data bus by a combination of A0, XWR and E signals. It features high-speed processing as the

#### Command outline

| Table 4                        |                        |    |     |

|--------------------------------|------------------------|----|-----|

| Command type                   | Command name           | A0 | XWR |

| Display control                | Cursor Home            | 0  | 0   |

| instruction                    | Display On/Off Control | 0  | 0   |

| Power control                  | Power Save             | 0  | 0   |

| I Ower control                 | Power Control          | 0  | 0   |

| System setup                   | System Setup           | 0  | 0   |

| Address control<br>instruction | Address Setup          | 0  | 0   |

| Data input instruction         | Data Write             | 1  | 0   |

timing only.

As the execution time of each instruction depends on the internal processing time of the SED1225, an enough time greater than the system cycle time (tcyc) must be assigned for continuous instruction execution.

- Explanation of commands

- (1) Cursor Home

The Cursor Home command presets the Address counter to 30H, and shifts the cursor to column 1 of line 1 if Cursor Display is ON.

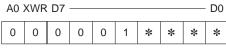

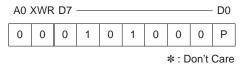

(2) Display On/Off Control

The Display On/Off Control command sets the LCD character and cursor display.

| A0 2 | XWR | D7 |   |   |   |   |   |    | D0 |

|------|-----|----|---|---|---|---|---|----|----|

| 0    | 0   | 0  | 0 | 1 | 1 | С | В | DC | D  |

|      |     |    |   |   |   |   | _ |    | -  |

\* : Don't Care

- D=0: Turns the display off.

- D=1: Turns the display on.

- DC=0: Selects the standard size display.

- DC=1: Selects the double-height vertical display.

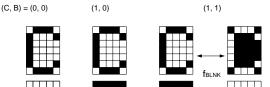

- B=0: Turns cursor blinking off.

- B=1: Turns cursor blinking on.

During blinking, the cursor character is alternately displayed normally and reversely. The normal and reverse display is repeated approximately every one second.

- C=0: Does not display the cursor.

- C=1: Displays the cursor.

The following provides the relationship between the C and B registers and cursor display.

commands are analyzed and executed in the internal

| С | В | Cursor display                                        |

|---|---|-------------------------------------------------------|

| 0 | 0 | Not displayed                                         |

| 0 | 1 | Not displayed                                         |

| 1 | 0 | Underbar cursor                                       |

| 1 | 1 | Alternate character display<br>normally and reversely |

The cursor display position is indicated by the address counter. Accordingly, to move the cursor, change the address counter value by automatic increment by writing the RAM address set command or RAM data.

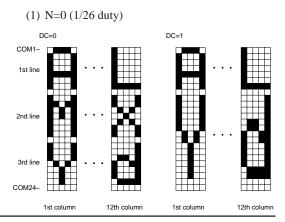

The following shows the relationship between the DC resistor and display:

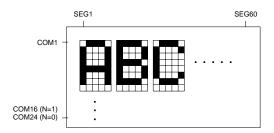

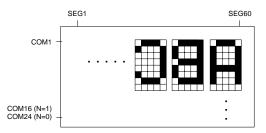

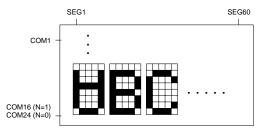

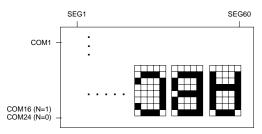

The character on the 3rd line will be displayed in double size on the second and third lines by setting DC=1.

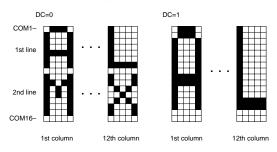

(2) N=1 (1/18 duty)

The character on the 1st line will be displayed in double size on the first and second lines by setting DC=1.

(3) Power Save

The Power Save command controls the oscillator and sets or releases the Sleep mode.

| A0 2 | XWR | D7 |   |   |   |   |   |   | D0 |

|------|-----|----|---|---|---|---|---|---|----|

| 0    | 0   | 0  | 1 | 0 | 0 | * | * | 0 | PS |

\* : Don't Care

- PS=0: Turns the Power Save on. (Release)

- PS=1: Turns the Power Save off. (Select)

- O=0: Turn the oscillator off. (Stop oscillation)

- O=1: Turns the oscillator on. (Oscillation)

- (4) Power Control

The Power Control command controls the builtin power circuit operations.

- P=0: Turns the power circuit off.

- P=1: Turns the power circuit on.

- Note: The oscillator must be operating to operate the voltage amp.

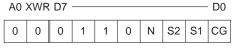

(5) System Reset

The System Reset command sets the display direction, the display line, and the use or no use of CGRAM. This command must first be executed after the power-on or reset.

| * | : | Don't | Care |

|---|---|-------|------|

|---|---|-------|------|

| N=0:    | Displays 3 lines. (1/26 duty)  |

|---------|--------------------------------|

| N=1:    | Displays 2 lines. (1/18 duty)  |

| S2=0:   | Normal display                 |

| S2=1:   | Right and left reverse display |

| S1=0:   | Normal display                 |

| S1=1:   | Top and bottom reverse display |

| CG=0:   | Does not use the CGRAM.        |

| CG=1:   | Uses the CGRAM.                |

|         |                                |

| (1) Nor | mal display                    |

#### (2) Horizontal flipping

#### (3) Vertical flipping

#### (4) Horizontal vertical flipping

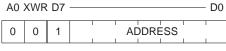

(6) RAM Address Setup

The RAM Address Setup command sets an address into the Address counter to write data into DDRAM, CGRAM and Symbol register.

When the cursor display is ON, the cursor is located at a position corresponding to the DDRAM address set by this command.

\* : Don't Care

(1) The 00H to 7FH address length can be set. To write data in the RAM, set the data write address by this command. When the subsequent data is written continuously, the address is automatically incremented.

#### RAM map

|     | 0   | 1    | 2                             | 3     | 4       | 5    | 6        | 7      | 8  | 9                      | А      | В   | С                        | D      | Е     | F  |

|-----|-----|------|-------------------------------|-------|---------|------|----------|--------|----|------------------------|--------|-----|--------------------------|--------|-------|----|

| 00H |     |      | CC                            | GRAN  | / (00H  | I)   |          |        |    |                        | С      | GRA | M (01                    | H)     |       |    |

| 10H |     |      | CC                            | GRAN  | /I (02H | I)   |          |        |    |                        | С      | GRA | M (03                    | H)     |       |    |

| 20H | SI1 |      | SI2                           | 2     |         | Unu  | ised     |        | EV | TEST                   | LED    |     | ι                        | Jnuse  | d     |    |

| 30H |     |      |                               |       | D       | DRAM | 1 line   | 1      |    | For                    | signal | s – | -                        |        | Unuse | ed |

| 40H |     |      |                               |       | D       | DRAM | 1 line 2 | 2      |    |                        |        |     | +•                       |        | Unuse | ed |

| 50H |     |      |                               |       | D       | DRAN | 1 line 3 | 3      |    |                        |        |     |                          |        | Unuse | ed |

| 60H |     |      |                               |       |         | Sym  | nbol re  | gister |    |                        |        |     |                          |        | Unuse | ed |

| 70H |     |      |                               |       |         | Sym  | nbol re  | gister |    |                        |        |     |                          |        | Unuse | ed |

| I   |     | Elec | c Icon<br>tronic C<br>registe | Contr |         | ster |          |        |    | LED<br>For sig<br>Symb |        |     | : LED<br>: SEG:<br>: COM | S1, 2, | 4, 5  | 2  |

(Do not use in normal operations.)

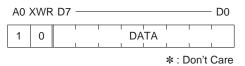

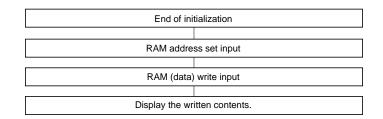

(7) Data Write

- (1) This command writes data in the DDRAM, CGRAM or Symbol register.

- (2) When this command is executed, the Address counter is incremented by 1 automatically. This allows continuous data writing.

Data write example: The following gives an example to write a single line of data continuously.

Note: Assign an enough time greater than "tcyc" before executing the next instruction.

|                            |    |        |    |              | Code         | de   |         |    |    |    | E undition                                                                                                                                                                                                                                                                                                               |

|----------------------------|----|--------|----|--------------|--------------|------|---------|----|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CONTINUARIO                | AO | A0 XWR | D7 | D6           | D5           | D4   | D3      | D2 | Б  | 8  | LAUGUOI                                                                                                                                                                                                                                                                                                                  |

| (1) Cursor Home            | 0  | 0      | 0  | 0            | 0            | -    | *       | *  | *  | *  | Shifts the cursor to its home position.                                                                                                                                                                                                                                                                                  |

| (2) Display On/Off Control | 0  | 0      | 0  | 0            | -            | -    | U       | ۵  | DC | ۵  | Turns on or off the cursor, cursor blinking, double-size display, and data display.<br>C=1: Cursor ON; C=0: Cursor OFF<br>B=1: Blinking ON; B=0: Blinking OFF<br>DC=1: Double-size display; DC=0: Normal display<br>D=1: Display ON; D=0: Display OFF                                                                    |

| (3) Power Save             | 0  | 0      | 0  | ~            | 0            | 0    | *       | *  | 0  | PS | Turns on or off the Power Save mode and oscillator.<br>PS=1: Power Save ON; PS=0: Power Save OFF<br>O=1: OSC ON; O=0: OSC OFF                                                                                                                                                                                            |

| (4) Power Control          | 0  | 0      | 0  | ~            | 0            | -    | 0       | 0  | 0  | ٩  | Turns on or off the built-in power circuit and voltage follower capacity, and sets the amp frequency.<br>P=1: Power circuit ON; P=0: Power circuit OFF                                                                                                                                                                   |

| (5) System Reset           | 0  | 0      | 0  | <del>.</del> | <del>.</del> | 0    | z       | S2 | S. | CG | Sets the use or no use of CGRAM and the display direction.<br>N=1: 3-line display; N=0: 2-line display<br>CG=1: Use of CGRAM; CG=0: No use of CGRAM<br>S2=0, S1=0: Normal display<br>S2=0, S1=1: Top and bottom reverse display<br>S2=1, S1=0: Right and left reverse display<br>S2=1, S1=1: 180-degree rotation display |

| (6) RAM Address Setup      | 0  | 0      | 1  |              |              | AD   | ADDRESS | SS |    |    | Sets an address of DDRAM, CGRAM or Symbol register.                                                                                                                                                                                                                                                                      |

| (7) RAM Write              | -  | 0      |    |              |              | DATA | τA      |    |    |    | Writes data in the DDRAM, CGRAM or Symbol register.                                                                                                                                                                                                                                                                      |

| (8) NOP                    | 0  | 0      | 0  | 0            | 0            | 0    | 0       | 0  | 0  | 0  | This is a non-operation command.                                                                                                                                                                                                                                                                                         |

| (9) Test Mode              | 0  | 0      | 0  | 0            | 0            | 0    | *       | *  | *  | *  | This is an IC chip test command. Do not use in normal operations.                                                                                                                                                                                                                                                        |

Table 4 SED1225 command list

## SED1225 Series

## **BUILT-IN MEMORIES**

#### **Character Generator ROM (CGROM)**

The SED1225 contains up to 126 types of CGROMs. Each character has a  $5\times8$ -dot structure.

Tables 5 to 8 defines the SED1225D\*\* character codes. Four characters (00H to 03H) of character codes are used for the CGROM or CGRAM by the System Setup command. The SED1225's CGROM is a mask ROM and it can be used as a custom CGROM. Consult to our sales agency for details.

The CGROM versions are identified as follows: Example: SED1225D0B ↑

CGROM pattern ID

|                      |   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | ower 4 E. | Bit of Coc | le<br>9 | A | В | С | D | E | F |

|----------------------|---|---|---|---|---|---|---|---|-----------|------------|---------|---|---|---|---|---|---|

|                      | 0 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 1 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 2 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 3 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 4 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 5 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 6 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

| t of Cord            | 7 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

| Higher 4 Bit of Cord | 8 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | 9 |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | А |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | в |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | с |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | D |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | E |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

|                      | F |   |   |   |   |   |   |   |           |            |         |   |   |   |   |   |   |

Table 5 SED1225DAB

Table 6 SED1225DBB

|                      | [ | 0 | 1 | 2 | 3 | 4   | 5 | 6 | ower 4 E.<br>7 | Bit of Coc | le<br>9 | A | В | С | D | E | F |

|----------------------|---|---|---|---|---|-----|---|---|----------------|------------|---------|---|---|---|---|---|---|

|                      |   | - |   |   |   | · · |   |   |                |            |         |   |   |   |   |   |   |

|                      | 0 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 1 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 2 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 3 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 4 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 5 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 6 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

| of Cord              | 7 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

| Higher 4 Bit of Cord | 8 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | 9 |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | A |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | в |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | с |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | D |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | E |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | F |   |   |   |   |     |   |   |                |            |         |   |   |   |   |   |   |

|                      | [ |   |   |   |   |   |   |   |   | Bit of Cod |   |   |   |   |          |   |   |

|----------------------|---|---|---|---|---|---|---|---|---|------------|---|---|---|---|----------|---|---|

|                      |   | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8          | 9 | A | В | С | D        | E | F |

|                      | 0 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 1 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 2 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 3 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 4 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 5 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 6 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

| of Cord              | 7 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

| Higher 4 Bit of Cord | 8 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | 9 |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | А |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | в |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | с |   |   |   |   |   |   |   |   |            |   |   |   |   | ┍╼┲╴╀╶┼╴ |   |   |

|                      | D |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   |   |

|                      | E |   |   |   |   |   |   |   |   |            |   |   |   |   |          |   | I |

|                      | F |   |   |   |   |   |   |   |   |            |   |   |   |   |          | * |   |

Table 7 SED1225DGB

## Character Generator RAM (CGRAM)

The SED1225 has a built-in CGRAM to program userdefined character patterns for highly flexible signal and character display.

Issue the System Setup command to use the CGRAM. The CGRAM has the 160-bit storage capacity, and it can store up to four 5×8-dot character patterns.

The following provides the relationship between CGRAM character patterns and CGRAM addresses and character codes.

| Character | RAM        |   |    |   | С | GRA | M Da | ita |   |    | Character Display | Signal D | Display |

|-----------|------------|---|----|---|---|-----|------|-----|---|----|-------------------|----------|---------|

| Code      | Address    |   | D7 |   |   |     |      |     |   | D0 | SEG               | SEGS     | 4 5     |

| 00H       | 00H to 07H | 0 | *  | * | * | 0   | 1    | 1   | 1 | 1  |                   |          | 4 5     |

|           |            | 1 | *  | * | * | 1   | 0    | 0   | 0 | 0  |                   |          |         |

|           |            | 2 | *  | * | * | 1   | 0    | 0   | 0 | 0  |                   |          |         |

|           |            | 3 | *  | * | * | 0   | 1    | 1   | 1 | 1  |                   |          |         |

|           |            | 4 | *  | * | * | 0   | 0    | 0   | 0 | 1  |                   |          |         |

|           |            | 5 | *  | * | * | 0   | 0    | 0   | 0 | 1  |                   |          |         |

|           |            | 6 | *  | * | * | 1   | 1    | 1   | 1 | 0  |                   |          |         |

|           |            | 7 | *  | * | * | 0   | 0    | 0   | 0 | 0  |                   |          |         |

| 01H       | 08H to 0FH | 8 | *  | * | * | 0   | 0    | 1   | 0 | 0  |                   |          |         |

|           |            | 9 | *  | * | * | 0   | 0    | 1   | 0 | 0  |                   |          |         |

|           |            | Α | *  | * | * | 0   | 1    | 1   | 1 | 0  |                   |          |         |

|           |            | В | *  | * | * | 0   | 1    | 1   | 1 | 0  |                   |          |         |

|           |            | С | *  | * | * | 0   | 1    | 1   | 1 | 0  |                   |          |         |

|           |            | D | *  | * | * | 1   | 1    | 1   | 1 | 1  |                   |          |         |

|           |            | E | *  | * | * | 1   | 1    | 1   | 1 | 1  |                   |          |         |

|           |            | F | *  | * | * | 0   | 0    | 0   | 0 | 0  |                   |          |         |

D7 to D5: Un used

D4 to D0: Character data (1 for display; 0 for no display)

The  $5\times8$ -dot character size can also be set. To do so, use the \*7H and \*FH RAM addresses. However, the \*7H and \*FH data is reversed if the underbar cursor is used.

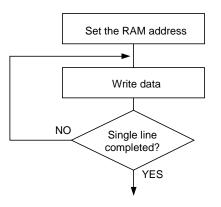

#### Symbol Register

The SED1225 has a built-in Symbol register to allow separate symbol setup on the display panel.

The Symbol register has the 120-bit storage capacity, and it can display 120 symbols. Also, the SED1225 contains a Blink register for every 5-dot blinking. The following provides the relationship between the Symbol register display patterns, RAM addresses and write data.

BL1 to BL24: Blinking setup (0 for no blinking; 1 for blinking)

Note: If the symbol size is 1.5 times greater than other dots, we recommend to divide and drive the SEG\* and COMS1 and COMS2 separately.

### Static Icon RAM

The SED1225 has a built-in Static Icon RAM to display a static icon separately from the dynamic icon. The Static Icon RAM has the 20-bit storage capacity, and

#### (SEGSA, B, C, D, E)

it can display 10 icons. The following provides the relationship between the static icon functions and the static icon, RAM address and write data.

| Function          | DAMAddagag  |    |   | Sta | atic Ic | on D | ata |   |      | Display       |

|-------------------|-------------|----|---|-----|---------|------|-----|---|------|---------------|

| Function          | RAM Address | D7 |   |     |         |      |     |   | - D0 | SEGSA B C D E |

| Display<br>ON/OFF | 20H         | *  | * | *   | 0       | 0    | 1   | 1 | 1    |               |

| Blink<br>ON/OFF   | 21H         | *  | * | *   | 1       | 0    | 0   | 0 | 1    |               |

(SEGSF, G, H, I, J)

| Function          |             |    |   | Sta | atic Ic | on D | ata |   |    | Display       |

|-------------------|-------------|----|---|-----|---------|------|-----|---|----|---------------|

| Function          | RAM Address | D7 |   |     |         |      |     |   | D0 | SEGSA B C D E |

| Display<br>ON/OFF | 22H         | *  | * | *   | 0       | 0    | 1   | 1 | 1  |               |

| Blink<br>ON/OFF   | 23Н         | *  | * | *   | 1       | 0    | 0   | 0 | 1  |               |

\* : Unused

1 : Display or blinking

0 : No display or no blinking

f BLINK : 1 to 2Hz

#### **Electronic Control RAM (Register)**

The SED1225 has the electronic control functions to control LCD drive voltages and to adjust the LCD display density. One of 32-state LCD voltages can be selected when the 5-bit data is written in the Electronic

Control RAM.

The following provides the relationship between the RAM address and write data by electronic control setup.

| Function   |             |    | E | lectro | onic C | Contro | ol Dat | a |    | Chatura |                  |

|------------|-------------|----|---|--------|--------|--------|--------|---|----|---------|------------------|

| Function   | RAM Address | D7 |   |        |        |        |        |   | D0 | Status  | Vev              |

| Electronic | 28H         | *  | * | *      | 0      | 0      | 0      | 0 | 0  | 0       | Vreg-0           |

| Control    |             | *  | * | *      | 0      | 0      | 0      | 0 | 1  | 1       | $VREG-\alpha$    |

|            |             | *  | * | *      | 0      | 0      | 0      | 1 | 0  | 2       | Vreg-2α          |

|            |             |    |   |        |        | •      |        |   |    | •       |                  |

|            |             |    |   |        |        | :      |        |   |    | :       |                  |

|            |             |    |   |        |        | •      |        |   |    | :       | :                |

|            |             | *  | * | *      | 1      | 1      | 1      | 0 | 1  | 29      | Vreg-29α         |

|            |             | *  | * | *      | 1      | 1      | 1      | 1 | 0  | 30      | Vreg-30 $\alpha$ |

|            |             | *  | * | *      | 1      | 1      | 1      | 1 | 1  | 31      | Vreg-31α         |

|            | 29H         | *  | * | *      | *      | *      |        |   |    |         | For test         |

\* : Unused

$\alpha$  :  $\alpha$ =VREG/95 (1/4biased)

Note: Do not use address 29H as it can be used for IC chip test only.

#### LED RAM (Register)

The SED1225 has the LED drive functions to drive the LCD by controlling the XLE1 and XLE2 pins.

The following provides the relationship between the RAM address and write data by LED register setup.

| Europhian.          |             |    |   | LEI | D Regis | ster Dat | a    |      |      |

|---------------------|-------------|----|---|-----|---------|----------|------|------|------|

| Function            | RAM Address | D7 |   |     |         | D3       | D2   | D1   | D0   |

| LED ON/OFF<br>Timer | 2AH         | *  | * | *   | *       | TIM2     | TIM1 | LED2 | LED1 |

\*: Unused

The following defines the XLE1 and XLE2 pin state depending on the TIM1, TIM2, LED1 and LED2 set values.

| LED Registe  | er Set Value |                                                                       |

|--------------|--------------|-----------------------------------------------------------------------|

| TIM2<br>TIM1 | LED2<br>LED1 | Output Status (XLE1, XLE2)                                            |

| 0            | 0            | XLE = High impedance                                                  |

| 0            | 1            | XLE = Low                                                             |

| 1            | 0            | Keeps XLE low approximately 15 sec after input of Display ON command. |

| 1            | 1            | XLE = Low                                                             |

Note: When this function is used, minimize power supply and power cable impedance to avoid IC misoperation due to large current.

## MAXIMUM ABSOLUTE RATINGS

| lte           | em        | Symbol         | Rating          | Unit |

|---------------|-----------|----------------|-----------------|------|

| Power voltag  | je (1)    | Vss            | -0.6 to +0.3    | V    |

| Power voltag  | je (2)    | V5             | -7.0 to +0.3    | V    |

| Power voltag  | je (3)    | V1, V2, V3, V4 | V5 to +0.3      | V    |

| Input voltage | •         | Vin            | Vss-0.3 to +0.3 | V    |

| Output voltag | ge        | Vo             | Vss-0.3 to +0.3 | V    |

| Operating ter | mperature | Topr           | -30 to +85      | °C   |

| Storage       | ТСР       | Tatr           | -55 to +100     |      |

| temperature   | Bare chip | Tstr           | -65 to +125     | °C   |

- Notes: 1. All voltages are referenced to VDD=0 V.

- 2. The following voltage levels must always be satisfied:  $V_{DD} \ge V_1 \ge V_2 \ge V_3 \ge V_4$ , and  $V_{DD} \ge V_{SS} \ge V_5$

- 3. If the LSI is used beyond the maximum absolute rating, the LSI may be destroyed permanently. The LSI should meet the electric characteristics during normal operations. If not, the LSI may be malfunction or the LSI reliability may be lost.

## **DC CHARACTERISTICS**

| lte                      | m                                                           | Symbol            | ,                     | onditions $-3.010 - 1.1$   | Min.             | Тур. | Max.                       | Unit | Pin            |

|--------------------------|-------------------------------------------------------------|-------------------|-----------------------|----------------------------|------------------|------|----------------------------|------|----------------|

| 10                       |                                                             | Cymbol            | 1/4 bias              |                            | -3.6             | -3.0 | -1.7                       | Onit |                |

| Power                    | Operable                                                    |                   | 1/5 bias              |                            | -3.6             | -3.0 | -2.7                       |      |                |

| voltage<br>(1)           | Data hold<br>voltage                                        | Vss               |                       |                            | -3.6             |      | -1.5                       | V    | Vss            |

| Power                    | Operable                                                    | V5                |                       |                            | -6.0             |      | -3.0                       | V    | V5             |

| voltage                  | Operable                                                    | V1, V2            |                       |                            | $0.5 \times V_5$ |      | Vdd                        | V    | V1, V2         |

| (2)                      | Operable                                                    | V3, V4            |                       |                            | V5               |      | $0.5 \times V_5$           | V    | V3, V4         |

| "Hi" input v             | /oltage                                                     | VIHC              |                       |                            | $0.2 \times Vss$ |      | Vdd                        | V    | *2             |

| "Lo" input               | voltage                                                     | VILC              |                       |                            | Vss              |      | $0.8 \times V_{\text{DD}}$ | V    | *2             |

| Input leaka              | age current                                                 | L                 | Vin = Vdd c           | r Vss                      | -1.0             |      | 1.0                        | μΑ   | *2             |

| LCD drive<br>ON resista  |                                                             | Ron<br>(LCD)      | Ta=25°C<br>∆V=0.1V    | V5=-5.0V                   |                  | 10   | 20                         | kΩ   | COM, SEG<br>*3 |

| LED driver<br>ON resista |                                                             | Ron<br>(LED)      | Vss=-3.0V<br>loL=10mA |                            |                  | 100  |                            | Ω    | XLE1, XLE2     |

| Static curr<br>consumpti |                                                             | Iddq              |                       |                            |                  | 0.1  | 5.0                        | μΑ   | Vdd            |

|                          |                                                             | During<br>display | V5 = -5               | /; No loading<br>Vss=–1.8V |                  | 20   | 30                         | μΑ   | Vdd *4         |

| Dynamic                  |                                                             | During<br>display | V5 = -5               | /; No loading<br>Vss=–3.0V |                  | 30   | 45                         | μΑ   | Vdd *4         |

| current<br>consump-      | current Inp During OSC On; PWR off                          |                   |                       |                            | 10               | 15   | μΑ                         | Vdd  |                |

| tion                     | tion During OSC Off; PWR off<br>sleep No loading; Vss=-3.0V |                   |                       |                            | 0.1              | 5    | μΑ                         | Vdd  |                |

|                          |                                                             | During<br>access  | fcyc=20               | 0KHz<br>Vss=–3.0V          |                  | 150  | 300                        | μΑ   | Vdd *5         |

| Input pin c              | apacity                                                     | CIN               | Ta=25°C, f            | =1MHz                      |                  | 8.0  | 10.0                       | pF   | *3             |

| Frame frequency             | <b>f</b> FR | Ta = 25°C, Vss = −3.0V | 70 | 100  | 130 | Hz  | *8     |

|-----------------------------|-------------|------------------------|----|------|-----|-----|--------|

| External clock<br>frequency | fск         |                        |    | 33.8 |     | kHz | *8, *9 |

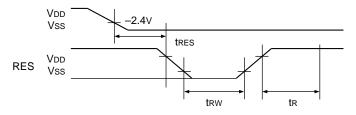

| Reset time        | t <sub>R</sub>  | 1.0 |  | μs | *6 |

|-------------------|-----------------|-----|--|----|----|

| Reset pulse width | t <sub>RW</sub> | 10  |  | μs | *6 |

| Reset start time  | tres            | 50  |  | ns | *7 |

Dynamic system:

| t-in<br>supply    | Amp output voltage   | V5    | Ta = 25°C (during 1/4 bias) | 4 ×<br>Vreg2 |      |       | V |  |

|-------------------|----------------------|-------|-----------------------------|--------------|------|-------|---|--|

| Built-<br>power s | Reference<br>voltage | Vreg2 | Ta = 25°C (during 1/4 bias) | -1.55        | -1.5 | -1.45 | V |  |

- \*1 Although the wide operating character range is guaranteed, a quick and excessive voltage variation may not be guaranteed during access by the MPU. The low-voltage data hold characteristics are valid during Sleep mode. No access by the MPU is allowed during this time.

- \*2 D0 to D5, D6 (SCL), D7 (SI), A0, RES, XCS, XWR (E), PS, IF, C86

- \*3 The resistance if a 0.1-volt voltage is supplied between the SEGn, SEGSn, COMn or COMSn output pin and each power pin (V1, V2, V3 or V4). It is defined within power voltage (2). Ron =  $0.1V/\Delta I$

- where,  $\Delta I$  is current that flows when the 0.1-volt voltage is supplied between the power supply and output.

- \*4 Applied if not accessed by the MPU during character display and if the built-in power circuit and oscillator are operating.

- \*5 Current consumption if always written in "fcyc". The current consumption during access is roughly proportional to the access frequency (fcyc).

- \*6 The "tR" (reset time) indicates a time period from the rising edge of RES signal to the completion of internal circuit reset. Therefore, the SED1225 enters the normal operation status after "tR".

- \*7 Defines the minimum pulse width of RES signal. A pulse width greater than "trw" must be entered for reset.

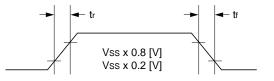

All signal timings are based on 20% and 80% of Vss.

\*8 The following provides the relationship between the oscillator frequency (fosc) for built-in circuit driving and the frame frequency (fFR).

$fosc = 13 \times 26 \times fFR$  (3-line display)

$= 13 \times 18 \times \text{fFR}$  (2-line display)

<Reference>

```

fBLK = (1/128) \times fFR

```

\*9 Enter the waveforms in 40% to 60% duty to use an external clock instead of the built-in oscillator. If no external clock is entered, fix it to high. (Normal high)

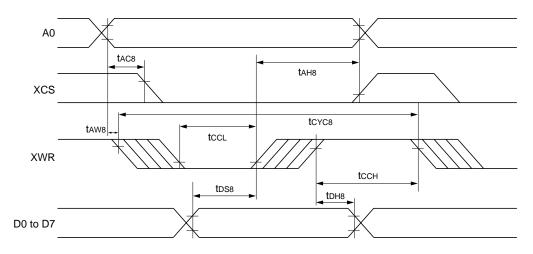

## SIGNAL TIMING CHARACTERISTICS

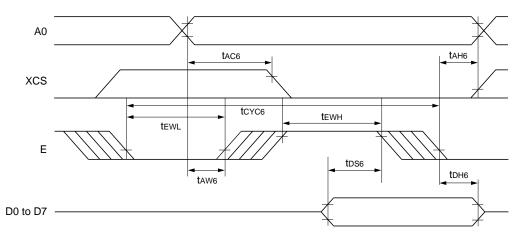

(1) MPU bus write timing (80 series)

|                                                           |           |                                      | (Ta = -30 to +8             | 85°C, Vss     | = -3.6V | to –1.7V) |

|-----------------------------------------------------------|-----------|--------------------------------------|-----------------------------|---------------|---------|-----------|

| Item                                                      | Signal    | Symbol                               | Conditions                  | Min.          | Max.    | Unit      |

| Address setup time<br>Address hold time<br>XCS setup time | A0<br>XCS | taws<br>tahs<br>tacs                 |                             | 60<br>30<br>0 |         | ns        |

| System cycle time                                         |           | t <sub>CYC8</sub>                    | All timing must be based on | 1850          | —       | ns        |