# 12. SED15A6 Series

# Contents

| 1. DESCRIPTION                                 | 12-1 |

|------------------------------------------------|------|

| 2. FEATURES                                    | 12-1 |

| 3. BLOCK DIAGRAM                               | 12-2 |

| 4. PIN DIMENSIONS                              | 12-3 |

| 5. PIN DESCRIPTION                             |      |

| 6. FUNCTIONAL DESCRIPTION                      |      |

| 7. COMMANDS                                    |      |

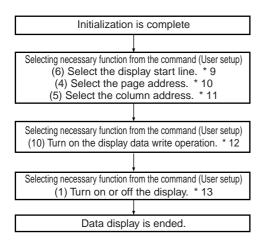

| 8. AN EXAMPLE OF FUNCTION SETUP USING COMMANDS |      |

| 9. ABSOLUTE MAXIMUM RATING                     |      |

| 10. DC CHARACTERISTICS                         |      |

| 11. AC CHARACTERISTICS                         |      |

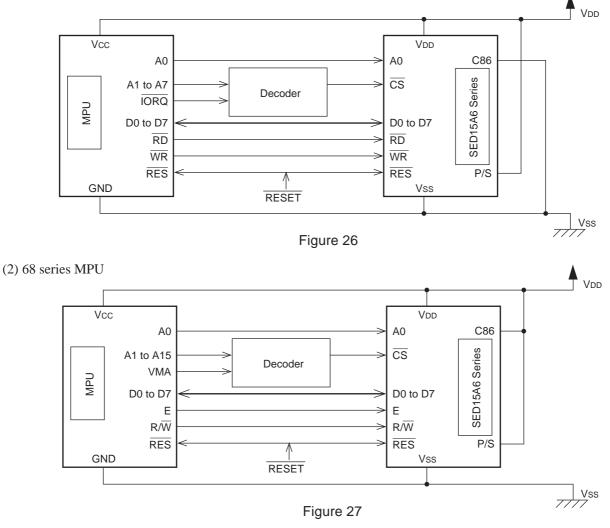

| 12. MPU INTERFACE (EXAMPLES)                   |      |

# **1. DESCRIPTION**

The SED15A6 series is a single-chip liquid crystal display (=LCD) driver for dot-matrix LCDs that can be connected directly to a microprocessor (=MPU) bus. It accepts 8-bit parallel or serial display data from a MPU, stores it in an on-chip display data RAM (=DDRAM), and generates a LCD drive signal independent of the MPU clock.

The use of the on-chip DDRAM of  $65 \times 102$  bits and a one-to-one correspondence between LCD panel pixel dots and on-chip DDRAM bits offer high flexibility in graphic display.

The SED15A6 series does not need external operation clock for DDRAM read/write operations, and has a onchip LCD power supply circuit featuring very low current consumption with few external components, and moreover has a on-chip CR oscillator circuit.

And the SED15A6 does not need smoothing capacitor on the LCD power supply.

Consequently, the SED15A6 series can be realize a high-performance handy display system with a minimum current consumption and the fewest components.

# 2. FEATURES

- Direct display of RAM data through the display data RAM.

- RAM bit data : "1" Non-illuminated "0" Illuminated (during normal display)

RAM capacity 65×102 = 6630 bits

- Display driver circuits

- SED15A6\*\*\* : 55 common output and 102 segment outputs

- High-speed 8-bit MPU interface(The chip can be connected directly to the 8080 series MPUs and the 6800 series MPUs)

- High-speed Serial interface are supported.

- Abundant command functions

Display data Read/Write, display ON/OFF, Normal/ Reverse display mode, page address set,

display start line set, column address set, display all points ON/OFF, LCD bias set, electronic

volume, read/modify/write, segment driver direction select, power saver, common driver

direction select, V<sub>0</sub> voltage regulation internal resistor ratio set.

• Low-power liquid crystal display power supply circuit equipped internally.

Booster circuit(with Boost ratios of Double/Triple/ Quad, where the step-up voltage reference power supply can be input externally)

- High-accuracy voltage adjustment circuit (Thermal gradient –0.1%/°C)

- V<sub>0</sub> voltage divider resistors equipped internally, V<sub>1</sub> to V<sub>4</sub> voltage divider resistors equipped internally, electronic volume function equipped internally, voltage follower.

- Component that can be omitted (you may omit the smoothing capacitor on the voltage follower).

- CR oscillator circuit equipped internally(external clock can also be input)

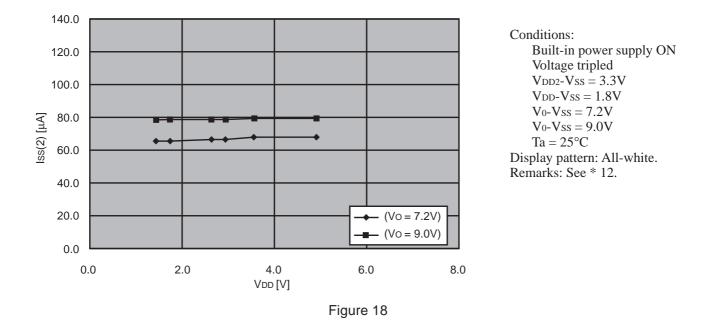

- Extremely low power consumption

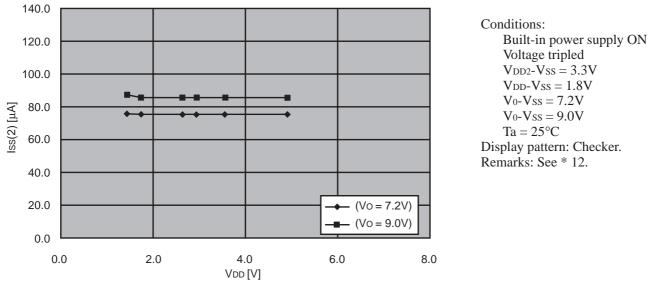

Operating power when the built-in power supply is used(an example) SED15A6DoB (79uA)

Condition : VDD–Vss = 1.8V, VDD2–Vss = 3.3V,V0– Vss = 9.0V, triple boosting, all white is displayed, Ta = 25°C

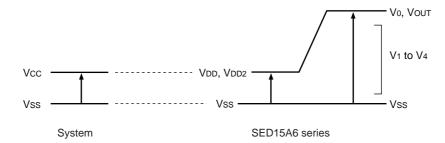

• Power supply

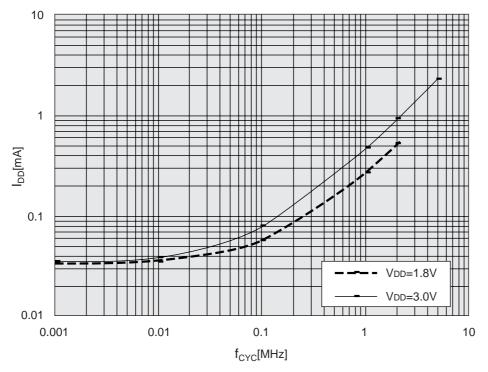

Operable on the low 1.8 voltage Logic power supply : VDD–Vss = 1.8V to 3.6V Boost reference voltage : VDD2–Vss = 1.8V to 5.0V Liquid crystal drive power supply : V0–Vss = 4.5V to 9.0V

- Wide range of operating temperatures : -40 to +85°C

- CMOS process

- Shipping forms include bare chip and TCP.

- There chip not designed for resistance to light or resistance to radiation.

#### **Series Specifications**

| Product<br>Name         | Duty | Bias    | SEG Dr | COM Dr | VREG Temperature<br>Gradient | Power supply specification                          | Shipping<br>Forms |

|-------------------------|------|---------|--------|--------|------------------------------|-----------------------------------------------------|-------------------|

| SED15A6DOB              | 1/55 | 1/6,1/8 | 102    | 55     | −0.1%/°C                     | Built-in power supply is only used                  | Bare Chip         |

| *SED15A6D1B             | 1/55 | 1/6,1/8 | 102    | 55     | −0.1%/°C                     | Vo or Vout External supply voltage follower is used | Bare Chip         |

| *SED15A6D <sub>2B</sub> | 1/55 | 1/6,1/8 | 102    | 55     | −0.1%/°C                     | External power supply is only used                  | Bare Chip         |

| *SED15A6T0*             | 1/55 | 1/6,1/8 | 102    | 55     | −0.1%/°C                     |                                                     | TCP               |

\* : Being planned

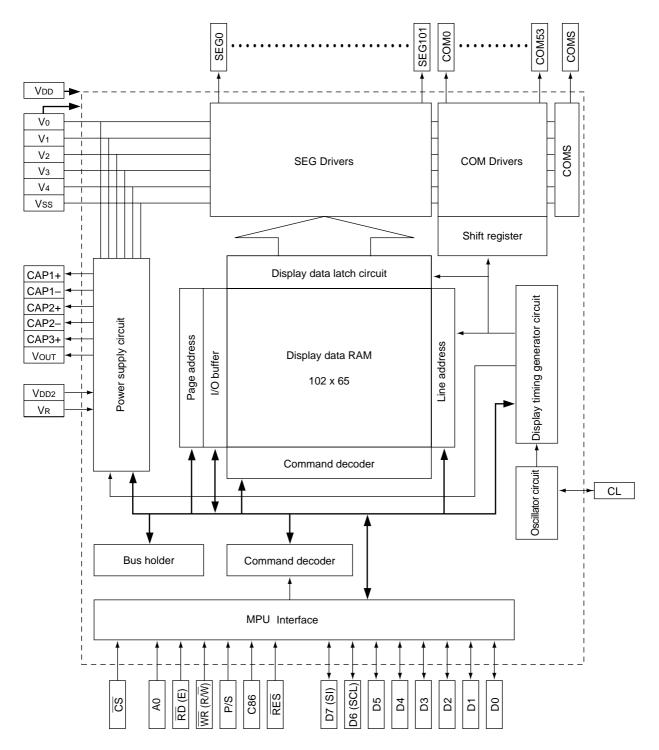

# **3. BLOCK DIAGRAM**

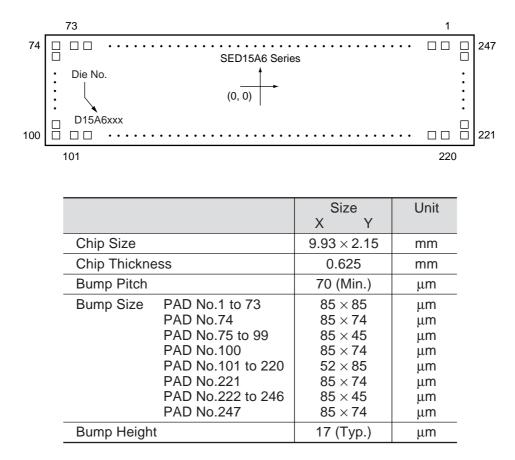

# **4. PIN DIMENSIONS**

# SED15A6\*\*\*\* Pad Center Coordinates

Units: µm

| PAD<br>No. | Pin<br>Name          | X              | Y   | PAD<br>No. | Pin<br>Name     | x              | Y            | PAD<br>No. | Pin<br>Name    | X              | Y    |

|------------|----------------------|----------------|-----|------------|-----------------|----------------|--------------|------------|----------------|----------------|------|

| 1          | (NC)                 | 4570           | 921 | 51         | V3              | -1915          | 921          | 101        | (NC)           | -4623          | -921 |

| 2          | TESTO                | 4449           |     | 52         | V4              | -2035          |              | 102        | (NC)           | -4545          |      |

| 3          | TEST1                | 4300           |     | 53         | CAP2+           | -2156          |              | 103        | COM2           | -4467          |      |

| 4          | Vss                  | 4151           |     | 54         | CAP2+           | -2277          |              | 104        | COM1           | -4389          |      |

| 5          | TEST2                | 4030           |     | 55         | (NC)            | -2397          |              | 105        | COM0           | -4312          |      |

| 6          | TEST3                | 3910           |     | 56         | (NC)            | -2518          |              | 106        | (NC)           | -4234          |      |

| 7          | RES                  | 3789           |     | 57         | (NC)            | -2639          |              | 107        | (NC)           | -4156          |      |

| 8          | CS                   | 3668           |     | 58         | (NC)            | -2760          |              | 108        | (NC)           | -4079          |      |

| 9          | Vss_                 | 3547           |     | 59         | (NC)            | -2880          |              | 109        | (NC)           | -4001          |      |

| 10         | $\overline{WR}(R/W)$ | 3427           |     | 60         | CAP2-           | -3001          |              | 110        | SEG0           | -3923          |      |

| 11         | RD(E)                | 3306           |     | 61         | CAP2-           | -3122          |              | 111        | SEG1           | -3846          |      |

| 12         |                      | 3185           |     | 62         | (NC)            | -3242          |              | 112        | SEG2           | -3768<br>-3690 |      |

| 13<br>14   | CL<br>A0             | 3065<br>2944   |     | 63<br>64   | (NC)<br>(NC)    | -3363<br>-3484 |              | 113<br>114 | SEG3<br>SEG4   | -3690          |      |

| 15         | D7(SI)               | 2823           |     | 65         | (NC)            | -3604          |              | 115        | SEG5           | -3535          |      |

| 16         | D6(SCL)              | 2703           |     | 66         | CAP1+           | -3725          |              | 116        | SEG6           | -3457          |      |

| 17         | D5                   | 2582           |     | 67         | CAP1+           | -3864          |              | 117        | SEG7           | -3380          |      |

| 18         | D4                   | 2461           |     | 68         | CAP1-           | -3967          |              | 118        | SEG8           | -3302          |      |

| 19         | D3                   | 2340           |     | 69         | CAP1-           | -4087          |              | 119        | SEG9           | -3224          |      |

| 20         | D2                   | 2220           |     | 70         | CAP3+           | -4208          |              | 120        | SEG10          | -3146          |      |

| 21         | D1                   | 2099           |     | 71         | CAP3+           | -4329          |              | 121        | SEG11          | -3069          |      |

| 22         | D0                   | 1978           |     | 72         | Vout            | -4449          |              | 122        | SEG12          | -2991          |      |

| 23         | Vdd                  | 1858           |     | 73         | (NC)            | -4570          | +            | 123        | SEG13          | -2913          |      |

| 24         | Vdd                  | 1737           |     | 74         | (NC)            | -4808          | 926          | 124        | SEG14          | -2836          |      |

| 25         | Vdd                  | 1616           |     | 75         | COMS            |                | 842          | 125        | SEG15          | -2758          |      |

| 26         | Vdd2                 | 1496           |     | 76         | COM26           |                | 771          | 126        | SEG16          | -2680          |      |

| 27         | Vdd2                 | 1375           |     | 77         | COM25           |                | 701          | 127        | SEG17          | -2603          |      |

| 28         | VDD2                 | 1254           |     | 78         | COM24           |                | 631          | 128        | SEG18          | -2525          |      |

| 29<br>30   | Vdd<br>P/S           | 1133           |     | 79<br>80   | COM23<br>COM22  |                | 561<br>491   | 129<br>130 | SEG19<br>SEG20 | -2447<br>-2370 |      |

| 30         | C86                  | 1013<br>892    |     | 81         | COM22<br>COM21  |                | 491          | 130        | SEG20<br>SEG21 | -2292          |      |

| 32         | Vss                  | 771            |     | 82         | COM21<br>COM20  |                | 351          | 131        | SEG21<br>SEG22 | -2292          |      |

| 33         | TEST4                | 651            |     | 83         | COM120<br>COM19 |                | 281          | 132        | SEG23          | -2136          |      |

| 34         | TEST5                | 474            |     | 84         | COM18           |                | 210          | 134        | SEG24          | -2059          |      |

| 35         | TEST6                | 297            |     | 85         | COM17           |                | 140          | 135        | SEG25          | -1981          |      |

| 36         | Vss                  | 120            |     | 86         | COM16           |                | 70           | 136        | SEG26          | -1903          |      |

| 37         | Vss                  | 0              |     | 87         | COM15           |                | 0            | 137        | SEG27          | -1826          |      |

| 38         | Vss                  | -121           |     | 88         | COM14           |                | -70          | 138        | SEG28          | -1748          |      |

| 39         | TEST7                | -298           |     | 89         | COM13           |                | -140         | 139        | SEG29          | -1670          |      |

| 40         | TEST8                | -475           |     | 90         | COM12           |                | -210         | 140        | SEG30          | -1593          |      |

| 41         | TEST9                | -652           |     | 91         | COM11           |                | -281         | 141        | SEG31          | -1515          |      |

| 42         | TEST10               | -828           |     | 92         | COM10           |                | -351         | 142        | SEG32          | -1437          |      |

| 43         | Vout                 | -949           |     | 93         | COM9            |                | -421         | 143        | SEG33          | -1360          |      |

| 44         | Vout                 | -1070          |     | 94         | COM8            |                | -491         | 144        | SEG34          | -1282          |      |

| 45         | Vout                 | -1190          |     | 95         | COM7            |                | -561         | 145        | SEG35          | -1204          |      |

| 46         | Vss                  | -1311          |     | 96         | COM6            |                | -631         | 146        | SEG36          | -1127          |      |

| 47<br>48   | Vr<br>Vo             | -1432<br>-1553 |     | 97<br>98   | COM5<br>COM4    |                | -701<br>-771 | 147<br>148 | SEG37<br>SEG38 | -1049<br>-971  |      |

| 40         | V0<br>V1             | -1673          |     | 90         | COM4<br>COM3    |                | -842         | 140        | SEG38          | -893           |      |

| 50         | V1<br>V2             | -1794          |     | 100        | (NC)            |                | -926         | 149        | SEG40          | -816           |      |

|            |                      |                | ♥   |            |                 | ▼              |              |            | 01010          |                | V    |

|            |             |                                                                                                                                                                                                                                                                                                                                                                                                    |                  |            |             |                                                                                                                                                                   | ·                                                                                                                                                                                                                                                                                                                                                                   |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PAD<br>No. | Pin<br>Name | X                                                                                                                                                                                                                                                                                                                                                                                                  | Y                | PAD<br>No. | Pin<br>Name | Х                                                                                                                                                                 | Y                                                                                                                                                                                                                                                                                                                                                                   |

|            |             | X<br>-738<br>-660<br>-583<br>-505<br>-427<br>-350<br>-272<br>-194<br>-117<br>-39<br>39<br>117<br>194<br>272<br>350<br>427<br>505<br>583<br>660<br>738<br>816<br>893<br>971<br>1049<br>1127<br>1204<br>1282<br>1360<br>1437<br>1515<br>1593<br>1670<br>1748<br>1826<br>1903<br>1981<br>2059<br>2136<br>2214<br>2292<br>2370<br>2447<br>2525<br>2603<br>2680<br>2758<br>2836<br>2913<br>2991<br>3069 | <b>Y</b><br>-921 |            |             | X<br>3146<br>3224<br>3380<br>3457<br>3535<br>3613<br>3690<br>3768<br>3846<br>3923<br>4001<br>4079<br>4156<br>4234<br>4312<br>4389<br>4467<br>4545<br>4623<br>4808 | Y         -921         -926         -842         -771         -631         -561         -491         -351         -210         -140         -70         0         70         140         210         281         351         421         -351         -281         -70         0         70         140         210         281         351         421         926 |

Units: µm

# **5. PIN DESCRIPTION**

# Power supply pins

| Name                 | I/O    | Description                                                                                                                                                                                                                                                                                                                                                                             | Number of pins |

|----------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Vdd                  | Supply | Power supply. Connect to MPU power pin Vcc.                                                                                                                                                                                                                                                                                                                                             | 5              |

| Vdd2                 | Supply | Externally-input reference power supply for booster circuit.                                                                                                                                                                                                                                                                                                                            | 3              |

| Vss                  | Supply | This is a 0V terminal connected to the system GND.                                                                                                                                                                                                                                                                                                                                      | 7              |

| V0, V1, V2<br>V3, V4 | Supply | Multi-level power supply for LCD drive. The voltages are determined by LCD cell. The voltages should maintain the following relationship : $V_0 \ge V_1 \ge V_2 \ge V_3 \ge V_4 \ge V_{SS}$ .<br>When on-chip power supply circuit turns on, V0 voltage are generated, and the following voltages are generated to V1 to V4.<br>Either voltage can be selected by LCD bias set command. | 5              |

|                      |        | SED15A6***           V1         5/6 • V0, 7/8 • V0           V2         4/6 • V0, 6/8 • V0           V3         2/6 • V0, 2/8 • V0           V4         1/6 • V0, 1/8 • V0                                                                                                                                                                                                              |                |

## LCD power supply circuit pins

| Name  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                  | Number of<br>pins |

|-------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| CAP1+ | 0   | Boosting capacitor positive connection pin.<br>Capacitor is connected across CAP1- pins.                                                                                                                                                                                                                                                                                                     | 2                 |

| CAP1- | 0   | Boosting capacitor negative connection pin.<br>Capacitor is connected across CAP1+ pins.                                                                                                                                                                                                                                                                                                     | 2                 |

| CAP2+ | 0   | Boosting capacitor positive connection pin.<br>Capacitor is connected across CAP2- pins.                                                                                                                                                                                                                                                                                                     | 2                 |

| CAP2- | 0   | Boosting capacitor negative connection pin.<br>Capacitor is connected across CAP2+ pins.                                                                                                                                                                                                                                                                                                     | 2                 |

| CAP3+ | 0   | Boosting capacitor positive connection pin.<br>Capacitor is connected across CAP1- pins.                                                                                                                                                                                                                                                                                                     | 2                 |

| Vout  | 0   | Booster output. Capacitor is connected across Vss or VDD2.                                                                                                                                                                                                                                                                                                                                   | 4                 |

| VR    | I   | Voltage adjustment pin. Provides Vo voltage using external<br>resistors. When internal resistors are used, this pin cannot be used.<br>Operable only when the built-in resistor for<br>Vo adjustment is not used.<br>[Vo resistance ratio is (D2, D1, D0) = (1.1.1)]<br>This pin is disabled when the built-in resistor for<br>Vo adjustment is used.<br>This pin must be open in this case. | 1                 |

# System bus connection pins

| Pin name                  | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Number of<br>pins |

|---------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| D7 to D0<br>(SL)<br>(SCL) | I/O | <ul> <li>8-bit bi-directional data bus to be connected to the standard 8-bit or 16-bit MPU data bus.</li> <li>When the serial interface is selected (P/S=LOW);</li> <li>D7 : Serial data input (SI)</li> <li>D6 : Serial clock input (SCL)</li> <li>At this time, D0 through D5 will go under the Hz mode.</li> <li>When the chip selects are in non-active state, D0 through D7 will go under the Hz mode.</li> </ul>                                                                                                                                                                 | 8                 |

| A0                        | Ι   | Control/data flag input.<br>A0=HIGH : The data on D7 to D0 is display data.<br>A0=LOW : The data on D7 to D0 is control data.                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                 |

| CS                        | I   | Chip select input. Data input is enable when $\overline{CS}$ is low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                 |

| RES                       | Ι   | When RES is caused to go low, initialization is executed.<br>A reset operation is performed at the signal level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                 |

| RD<br>(E)                 | I   | <ul> <li>When connected to an 8080-series MPU;<br/>This is active-LOW. This pin is connected to the RD signal of the 8080-series MPU. While this signal is low, SED15A6 series data bus in an output status.</li> <li>When connected to an 6800-series MPU;<br/>This is active-HIGH. This is used as an enable clock input pin of the 6800-series MPU.</li> </ul>                                                                                                                                                                                                                      | 1                 |

| WR<br>(R/W)               | Ι   | <ul> <li>When connected to an 8080-series MPU ;<br/>This is active-LOW. This pin is connected to the WR signal of the 8080-series MPU. The signals on the data bus are latched at the rising edge of the WR signal.</li> <li>When connected to an 6800-series MPU ;<br/>This is the read/write control signal input .<br/>R/W=HIGH : Read.<br/>R/W=LOW : Write.</li> </ul>                                                                                                                                                                                                             | 1                 |

| C86                       | Ι   | MPU interface selection pin.<br>C86=HIGH : 6800-series MPU interface<br>C86=LOW : 8080-series MPU interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                 |

| P/S                       | Ι   | Serial data input/parallel data input selection pin.         P/S=HIGH : Parallel data input         P/S=LOW : Serial data input         The following applies depending on the P/S status :         P/S       Data/Command       Data       Read/Write       Serial Clock         HIGH       A0       D7 to D0       RD, WR       –         LOW       A0       SI (D7)       Write only       SCL (D6)         In serial mode, no data can be read from DDRAM.       When P/S=LOW,D5 to D0 are HZ. D5 to D0 may be HIGH, LOW or Open, and moreover A0, RD, WR, C86 may be HIGH or LOW. | 1                 |

#### LCD driver pins

| Name              | I/O              |                                                                                                                   | Descriptio                                                                                                                                                                                                                                                                                                                 | on                          |                 |                      |  | Number of<br>pins |  |

|-------------------|------------------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------|----------------------|--|-------------------|--|

| CL                | I                | circuit for the di<br>CL = HIGH: Bu<br>CL = LOW: Bui<br>Select CL = LO                                            | in is used for enabling or disabling the built-in oscillation<br>for the display clock.<br>HGH: Built-in oscillation circuit is enabled.<br>.OW: Built-in oscillation circuit (external input) is disabled.<br>CL = LOW to turn the external clock off.<br>using the built-in oscillation circuit, select CL = HIGH (VDD). |                             |                 |                      |  |                   |  |

| SEG0<br>to SEG101 | 0                | These pins out<br>One of V <sub>0</sub> , V <sub>2</sub> , V<br>a given combin                                    | /₃ and Vss le                                                                                                                                                                                                                                                                                                              | vels is sele                | cted c          |                      |  | 102               |  |

|                   |                  | RAM data                                                                                                          | Internal FR                                                                                                                                                                                                                                                                                                                | 0                           | Dutput          | t voltage            |  |                   |  |

|                   |                  | RAIVI Uala                                                                                                        | signal                                                                                                                                                                                                                                                                                                                     | Normal dis                  | splay           | Reversing display    |  |                   |  |

|                   |                  | HIGH                                                                                                              | HIGH                                                                                                                                                                                                                                                                                                                       | V <sub>0</sub>              |                 | V2                   |  |                   |  |

|                   |                  | HIGH                                                                                                              | LOW                                                                                                                                                                                                                                                                                                                        | Vss                         |                 | V3                   |  |                   |  |

|                   |                  | LOW                                                                                                               | HIGH                                                                                                                                                                                                                                                                                                                       | V2                          |                 | Vo                   |  |                   |  |

|                   |                  | LOW                                                                                                               | LOW                                                                                                                                                                                                                                                                                                                        | V3                          |                 | Vss                  |  |                   |  |

|                   |                  | Power save                                                                                                        | _                                                                                                                                                                                                                                                                                                                          |                             | V               | lss                  |  |                   |  |

| COM0<br>to COM53  | 0                | These pins output the signal for the common drive of LCD.<br>Following number of pins are assigned to SED15A6***. |                                                                                                                                                                                                                                                                                                                            |                             |                 |                      |  |                   |  |

|                   |                  | Model                                                                                                             | C                                                                                                                                                                                                                                                                                                                          | OM                          | Nur             | nber of COM pins     |  |                   |  |

|                   |                  | SED15A6**                                                                                                         | * COM0                                                                                                                                                                                                                                                                                                                     | ~COM53                      |                 | 54                   |  |                   |  |

|                   |                  | One of V <sub>0</sub> , V <sub>1</sub> , V<br>a given combin                                                      | /4 and Vss le<br>ation of scar                                                                                                                                                                                                                                                                                             | evels is sele<br>data and F | cted c<br>R sig | lepending on<br>nal. |  |                   |  |

|                   |                  | Scar                                                                                                              | n data                                                                                                                                                                                                                                                                                                                     | FR                          | (               | Dutput voltage       |  |                   |  |

|                   |                  | HI                                                                                                                | GH                                                                                                                                                                                                                                                                                                                         | HIGH                        |                 | Vss                  |  |                   |  |

|                   |                  | HI                                                                                                                | GH                                                                                                                                                                                                                                                                                                                         | LOW                         |                 | Vo                   |  |                   |  |

|                   |                  | LC                                                                                                                | W                                                                                                                                                                                                                                                                                                                          | HIGH                        |                 | V1                   |  |                   |  |

|                   |                  | LC                                                                                                                | W                                                                                                                                                                                                                                                                                                                          | LOW                         |                 | V4                   |  |                   |  |

|                   | Power save – Vss |                                                                                                                   |                                                                                                                                                                                                                                                                                                                            |                             |                 |                      |  |                   |  |

| COMS              | 0                | They are COM                                                                                                      |                                                                                                                                                                                                                                                                                                                            |                             | or the i        | indicator.           |  | 2                 |  |

|                   |                  | Both pins outpu<br>They must be r                                                                                 |                                                                                                                                                                                                                                                                                                                            |                             | əd.             |                      |  |                   |  |

#### **Test pins**

| Name           | I/O | Description                                                    | Number of<br>pins |

|----------------|-----|----------------------------------------------------------------|-------------------|

| TEST0<br>to 10 | I/O | These are terminals for IC chip testing. They are set to OPEN. | 11                |

|                |     | Total : 220 pins for the                                       | SED15A6***.       |

Note and caution

• If control signal from MPU is Hz, an over-current may flow through the IC. A protection is required to prevent the Hz signal at the input pins.

# **6. FUNCTIONAL DESCRIPTION**

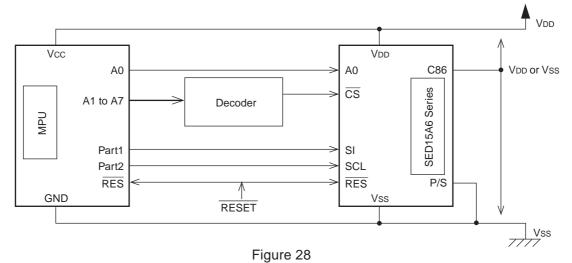

#### **Microprocessor Interface**

#### Interface type selection

The SED15A6 series can transfer data via 8-bit bidirectional data buses (D7 to D0) or via serial data input (SI). Through selecting the P/S pin polarity to the HIGH

#### Table 1

| P/S                 | CS | <b>A0</b> | RD | WR | C86 | D7 | D6  | D5 to D0 |

|---------------------|----|-----------|----|----|-----|----|-----|----------|

| HIGH:Parallel Input | CS | A0        | RD | WR | C86 | D7 | D6  | D5 to D0 |

| LOW:Serial Input    | CS | A0        | I  | -  | -   | SI | SCL | -        |

- : Must always be HIGH or LOW

#### **Parallel interface**

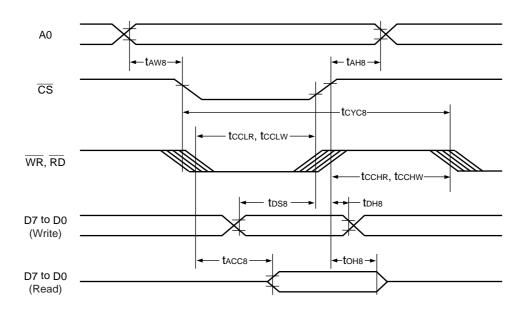

When the parallel interface has been selected (P/S =HIGH), then it is possible to connect directly to either

an 8080-series MPU or a 6800-series MPU (as shown in Table 2) by selecting C86 pin to either HIGH or LOW.

or LOW, it is possible to select either 8-bit parallel data

input or serial data input as shown in Table 1.

#### Table 2

| C86                      | CS | A0 | RD | WR  | D7 to D0 |

|--------------------------|----|----|----|-----|----------|

| HIGH:6800-series MPU bus | CS | A0 | Е  | R/W | D7 to D0 |

| LOW:8080-series MPU bus  | CS | A0 | RD | WR  | D7 to D0 |

Moreover, the SED15A6 series identifies the data bus signal according to A0,  $\overline{\text{RD}}(\text{E})$ ,  $\overline{\text{WR}}(\text{R}/\overline{\text{W}})$ signals, as

shown in Table 3.

#### Table 3

| Common | 6800-series | 8080- | series |                               |  |

|--------|-------------|-------|--------|-------------------------------|--|

| A0     | R/W         | RD    | WR     | Function                      |  |

| 1      | 1           | 0 1   |        | Reads the display data        |  |

| 1      | 0           | 1     | 0      | Writes the display data       |  |

| 0      | 1           | 1     | 0      | Writes control data (command) |  |

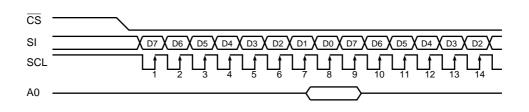

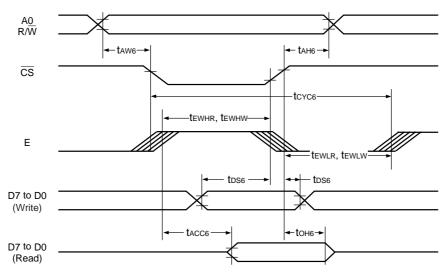

#### Serial interface

When the serial interface has been selected (P/S=LOW) then when the chip is in active state( $\overline{CS}=LOW$ ) the serial data input (SI) and the serial clock input (SCL) can be received.

The serial data is read from the serial data input pin in the rising edge of the serial clocks D7, D6 through D0, in this order. This data is converted to 8 bits parallel data in the rising edge of the eighth serial clock for the processing. The A0 input is used to determine whether the serial data input is display data or command data; when A0=HIGH, the data is display data, and when A0=LOW then the data is command data.

The A0 input is read and used for detection every 8th rising edge of the serial clock after the chip becomes active.

Figure 1 is a serial interface signal chart.

Figure 1

- \* When the chip is inactive, the shift register and the counter is reset to the initial state.

- \* Data read is not available as long as the serial interface is selected.

- \* Reasonable care must be exercised so that SCL signal may not be exposed undesirable effects resulting from, for instance, terminal reflection of wiring or external noises. Before using the signal, it is recommended to test the signal in actual system.

#### **Chip select input**

The MPU interface (either papallel or serial) is enabled only when  $\overline{CS}$ =LOW.

When the chip select is inactive, D7 to D0 enter a high impedance state, and A0,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$  inputs are disabled. When the serial interface is selected, the shift register and the counter are reset.

#### Access to DDRAM and internal registers

In accessing the DDRAM and the internal registers of the SED15A6 series, the MPU is required to satisfy the only cycle time (tcvc), and is not needed to consider the wait time. Accordingly, it is possible to transfer data at higher speed.

In order to realize the higher speed accessing, the

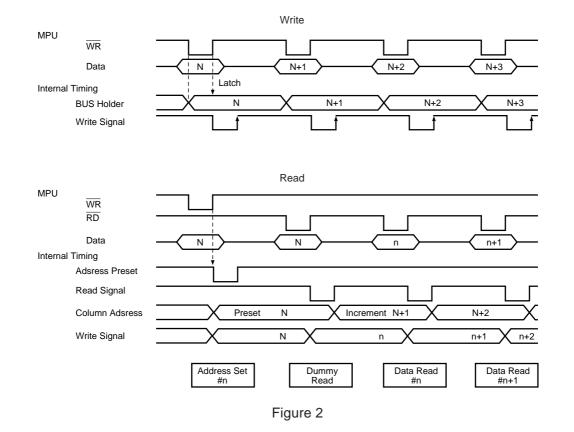

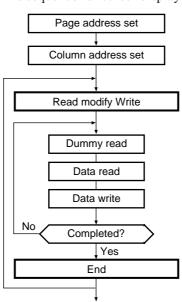

SED15A6 series can perform a type of pipeline processing between LSIs using bus holder of internal data bus when data is sent from/to the MPU. For example, when the MPU writes data to the DDRAM. once the data is stored in the bus holder, then it is written to the DDRAM before the next data write cycle. And when the MPU reads the contents of the DDRAM, the first data read cycle (dummy read cycle) stores the read data in the bus holder, and then the data is read from the bus holder to the system bus at the next data read cycle. Thus, there is a certain restriction in the DDRAM read sequence. When an address is set, the specified address data is NOT output at the immediately following read instruction. The address data is output during second data read. A single dummy read must be inserted after address setup and after write cycle (refer to Figure 2).

#### DDRAM

#### DDRAM and page/column address circuit

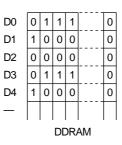

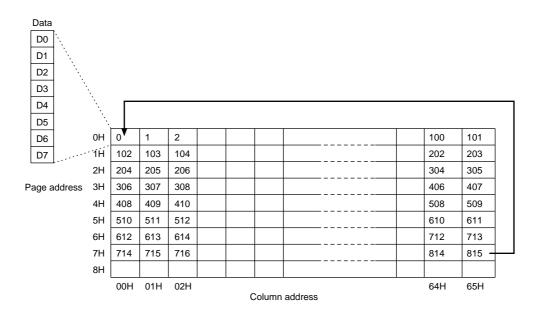

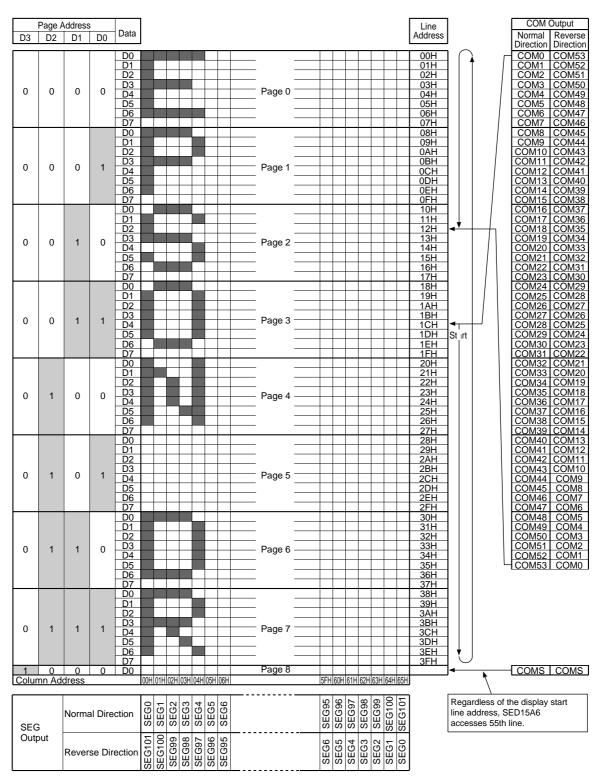

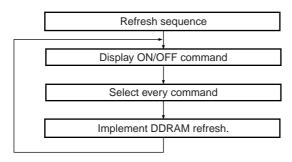

The DDRAM stores pixel data for LCD. It is a 65-row (8 page by 8 bit + 1) by 102-column addressable array. As is shown in Figure 3, the D7 to D0 display data from the MPU corresponds to the LCD common direction. Moreover, reading from and writing to the display RAM from the MPU side is performed through the I/O

buffer, which is an independent operation from signal reading for the liquid crystal driver. Consequently, even if the display data RAM is accessed asynchronously during liquid crystal display, it will not cause adverse effects on the display (such as flickering).

#### Page address circuit

Each pixel can be selected when page address and column address are specified(refer to Figure 5). The MPU issues Page address set command to change the page and access to another page. Page address 8 (D3,D2,D1,D0 = 1,0,0,0) is DDRAM area dedicate to the indicator, and display data D0 is only valid. The DDRAM column address is specified by Column

address set command. The specified column address is

automatically incremented by +1 when a Display data read/write command is entered. After the last column address (65H) ,column address returns to 00H and page address incremented by +1 (refer to Figure 4). After the very last address (column = 65H,page = 7H),both column address and page address return to 00H (column address = 00H, page address = 0H).

Figure 4

#### Column address circuit

Designate the column side address of the indication data RAM as shown in Fig. 5, using the column address setting command. Since the designated column address increments (+1) each time an indication data•read/write command is input, the MPU can make access to the indication data in succession.

Also, as shown in Fig. 4, after an access has been made to the final column address (65H), the column address will return to (00H) and the page address will be automatically incremented (by +1). Thanks to this feature, it is possible to write continuous data being divided between adjoining pages. Furthermore, after accesses have been made to the final addresses of both of the page and column (column = 65H and page = 7H), both of the column address and the page address returns to (00H).

(The page will not increment to "8H". Therefore, be careful when executing "read•modify•write" processes.) Also, as shown in Table 4, the correlation between the column address of the indication data RAM and the segment output can be reversed by use of the ADC command (segment driver direction select command). Thanks to this feature, IC layout limitations when constituting an LCD module can be lessened.

#### Table 4

| Column Address    | 00H    | 01H    | 02H   | 63H   | 64H    | 65H    |

|-------------------|--------|--------|-------|-------|--------|--------|

| Normal Direction  | SEG0   | SEG1   | SEG2  | SEG99 | SEG100 | SEG101 |

| Reverse Direction | SEG101 | SEG100 | SEG99 | SEG2  | SEG1   | SEG0   |

#### Line address circuit

The line address circuit specifies the line address (as shown Figure 5) relating to the COM output when the contents of the DDRAM are displayed. The display start line address, what is normally the top line of the display, can be specified by Display start line address set command. And Common driver direction select command can be used to reverse the relationship between the DDRAM line address and common output. For example, as is shown in Table 5, the display start line address corresponds to the COM0 output when the common driver direction is normal, or the COM53 output when common driver direction is reversed.And the display area is followed by the higher number line addresses in ascending order from the display start line address, corresponding to the duty cycle. This allows flexible IC layout during LCD module assembly. If the display start line address is changed dynamically using the Display start line address set command,then screen scrolling and page swapping can be performed.

#### Table 5 (at display start line address=1CH)

| Line Address      | 1CH   | 1DH   | 3FH   | 00H   | 11H      | 12H   |

|-------------------|-------|-------|-------|-------|----------|-------|

| Normal Direction  | COM0  | COM1  | COM35 | COM36 | COM52    | COM53 |

| Reverse Direction | COM53 | COM52 | COM18 | COM17 | <br>COM1 | COM0  |

#### Display data latch circuit

The display data latch circuit is a latch temporarily stored the display data that is output to the LCD driver circuit from the DDRAM.

Display ON/OFF command, Display normal/reverse

command, and Displayd all points ON/OFF command control only the data within the latch, and do not change the data within the DDRAM.

#### **Display data RAM**

The display data RAM stores pixel data for the LCD. It is a 102-column  $\times$  65-row addressable array as shown in Figure 5.

Figure 5

#### **Oscillation circuit**

The SED15A6 series generates display clocks using its built-in CR oscillation circuit. The built-in oscillation circuit is enabled when CL = HIGH is selected and the power save mode is turned off.

You can stop operation of the CR oscillation circuit by selecting CL = LOW. Display clock can be externally entered via CL pin (when external clock is turned off, CL pin must be placed in LOW).

#### Table 6

| CL          | Operation                                                                    |

|-------------|------------------------------------------------------------------------------|

| HIGH        | Built-in CR oscillation circuit is enabled.                                  |

| LOW         | Built-in CR oscillation circuit is turned off [display clock is turned off]. |

| Clock input | External clock input mode                                                    |

Table 7 shows relationship between frequency of external clock (fcL), frequency of built-in clock circuit (fosc) and fFR. Since CL pin is used for resetting the built-in CR clock circuit, it must satisfy the fcL requirements given in the "DC Characteristics".

#### Table 7

|            | ltem                                      | ffr computation formula |

|------------|-------------------------------------------|-------------------------|

| SED15A6*** | When built-in oscillation circuit is used | frr=fosc / (55×8) [Hz]  |

|            | When external clock input is used         | ffr=fcl/ (55×16) [Hz]   |

#### **Display timing generator circuit**

The display timing generator circuit generates the timing signal to the line address circuit and the display data latch circuit, and generates COM scan signal and the LCD AC signal (dual-frame AC driver waveform).

#### LCD driver circuits

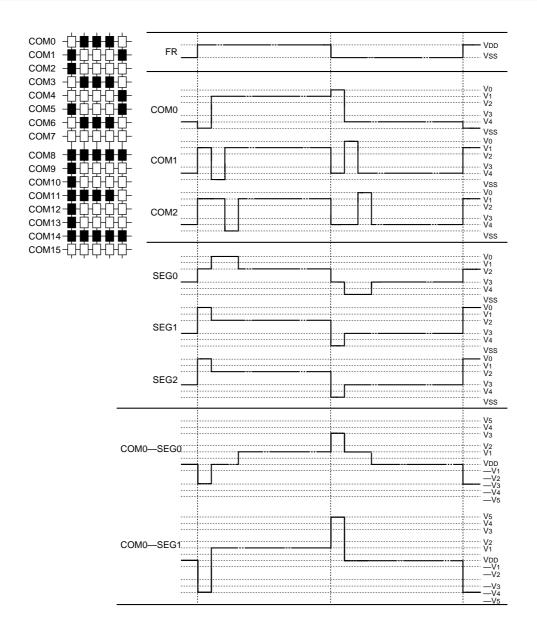

These are multiplexers outputting the LCD panel driving 4-level signal which level is determined by a combination of display data, COM scan signal, and LCD AC signal (FR). Figure 6 shows an example of SEG and COM output waveforms.

Figure 6

#### Power supply circuit

The power supply circuit generates the voltage to drive the LCD panel at low power consumption.

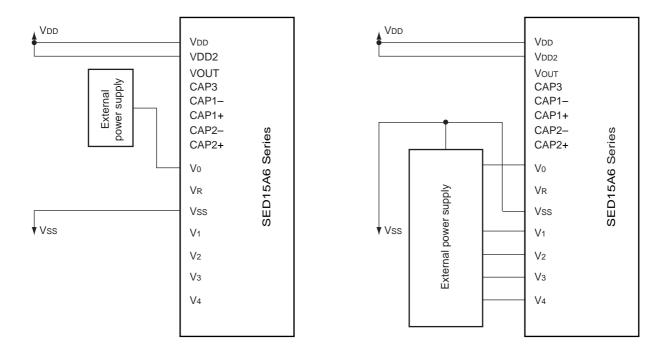

The power supply circuit consists of a booster circuit, voltage regulator circuit, and voltage follower circuit, and is controlled by Power control set command. Using this command, the booster circuit, the voltage regulator circuit, and the voltage follower circuit can be independently turned ON or OFF. Consequently, the external power supply and part of internal power supply circuit functions can be used simultaneously. Table 8 shows reference combinations.

Table 8 lists the functions controllable from 3 bits data of the power control set command. And, Table 9 shows sample combinations of the bits.

Select the models depending on the state of use.

#### Table 8

| ltem                                                           | State |     |  |  |

|----------------------------------------------------------------|-------|-----|--|--|

| Item                                                           | "1"   | "0" |  |  |

| D2 Booster circuit control bit                                 | ON    | OFF |  |  |

| D1 Voltage adjusting circuit (V adjusting circuit) control bit | ON    | OFF |  |  |

| D0 Voltage follower circuit (V/F circuit) control bit          | ON    | OFF |  |  |

#### Table 9

| Usage                                                    | Model | D2 | D1 | D0 | Booster<br>circuit. | V adjusting circuit. | V/F<br>circuit. | External voltage entered. | Pins on<br>booster<br>circuit |

|----------------------------------------------------------|-------|----|----|----|---------------------|----------------------|-----------------|---------------------------|-------------------------------|

| Built-in power supply alone is used                      | *1    | 1  | 1  | 1  | ON                  | ON                   | ON              | Vdd2                      | Used                          |

| V adjusting and                                          | *2    | 0  | 1  | 1  | OFF                 | ON                   | ON              | Vоит *4                   | OPEN                          |

| V/F circuits alone are used<br>V/F circuit alone is used | *2    | 0  | 0  | 1  | OFF                 | OFF                  | ON              | Vo *4                     | OPEN                          |

| External power supply alone is used                      | *3    | 0  | 0  | 0  | OFF                 | OFF                  | OFF             | Vo to V4 *4               | OPEN                          |

\* Pins on the booster circuits denote CAP1+, CAP1-, CAP2+, CAP2- and CAP3+ pins.

\* Although other combinations than the above are available, they are not pragmatic and thus not recommendable.

\*1: SED15A6D0B \*2: SED15A6D1B \*3: SED15A6D2B

\*4: VDD2 is recommended to short-circuit to VDD

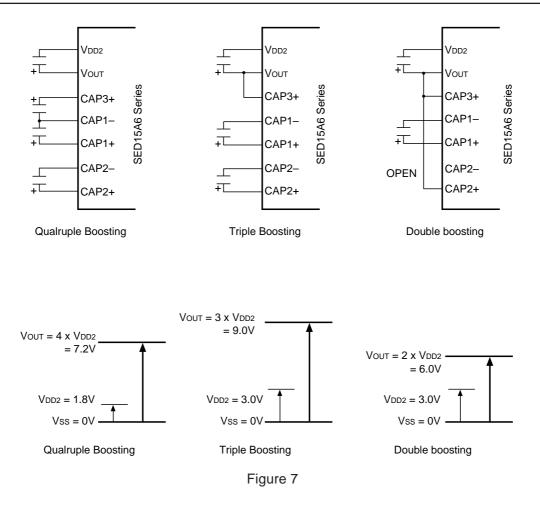

#### **Booster circuit**

Using the booster circuit, it is possible to produce Quad/ Triple/Double boosting of the VDD2–Vss voltage level. Quad boosting : If capacitor are inserted between CAP1+ and CAP1-, between CAP2+ and CAP2-, between CAP3+ and CAP1-, between Vout and VDD2, the potential between VDD2 and Vss is boosted to quadruple toward the positive side and it is output at Vout pin.

Triple boosting : If capacitor are inserted between CAP1+ and CAP1-, between CAP2+ and CAP2-,

between Vout and VDD2, and jumper between CAP3+ and Vout, the triple boosted voltage appears at Vout pin.

Double boosting : If capacitor are inserted between CAP1+ and CAP1-, between Vout and VDD2, open CAP2-, and jumper between CAP2+, CAP3+ and Vout, the double boosted voltage appears at Vout pin. The boosted voltage relationships are shown in Figure

The boosted voltage relationships are shown in Figure 7.

\*VDD2 voltage must be set so that VOUT voltage does not exceed the absolute maximun rated value.

\*The Capacitance depend on the load of the LCD panel to be driven. Set a value that LCD driver voltage may be stable (reference value = 1.0 to  $4.7\mu$ F).

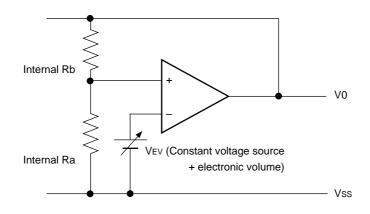

#### Voltage regulator circuit

The boosting voltage occurring at the Vout pin is sent to the voltage regulator, and the V<sub>0</sub> voltage (LCD driver voltage) is output.

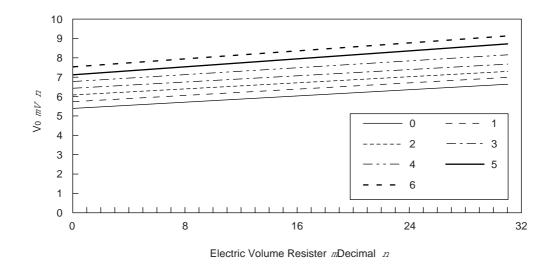

Because the SED15A6 series has the high-accuracy constant voltage source, the 32-level electronic volume function and the internal resistor for the V<sub>0</sub> voltage regulator (= V<sub>0</sub>-resistor), it is possible to construct a high-accuracy voltage regulator circuit without external component. And V<sub>0</sub> voltage can be adjusted by commands only to adjust the LCD contrast.

The  $V_0$  voltage can be calculated using the following equation within the range of  $V_0 < V_{\rm OUT}.$

$V_0 = (1+Rb/Ra) \bullet V_{EV}$

=  $(1+Rb/Ra) \cdot (1-\alpha/200)$  Vreg (Expression A-1) Vev =  $(1-\alpha/200) \cdot$ Vreg

VREG is the on-chip constant voltage as shown in Table 10 at Ta= $25^{\circ}$ C.

#### Table 10

| Model      | Vreg | Thermal Gradient |

|------------|------|------------------|

| SED15A6D** | 1.2V | −0.1%/°C         |

$\alpha$  is a value of the electronic volume, and can be set to one of 32-states by Electronic volume command setting

Table 11

| D4 | D3 | D2 | D1 | D0 | α  |

|----|----|----|----|----|----|

| 0  | 0  | 0  | 0  | 0  | 31 |

| 0  | 0  | 0  | 0  | 1  | 30 |

| 0  | 0  | 0  | 1  | 0  | 29 |

|    |    | :  |    |    | :  |

|    |    | :  |    |    | :  |

| 1  | 1  | 1  | 0  | 0  | 3  |

| 1  | 1  | 1  | 0  | 1  | 2  |

| 1  | 1  | 1  | 1  | 0  | 1  |

| 1  | 1  | 1  | 1  | 1  | 0  |

Rb/Ra is the Vo-resistor ratio, and can be set to one of 7states by Vo-resistor ratio set command setting the 3-bit the 5-bit data in the electronic volume register. Table 11 shows the value of  $\alpha$ .

|    |    |    | 1+Rb/Ra                        |

|----|----|----|--------------------------------|

| D3 | D2 | D1 | SED15A6 (Typ.)                 |

| 0  | 0  | 0  | 5.45                           |

| 0  | 0  | 1  | 5.71                           |

| 0  | 1  | 0  | 6.00                           |

| 0  | 1  | 1  | 6.32                           |

| 1  | 0  | 0  | 6.67                           |

| 1  | 0  | 1  | 7.06                           |

| 1  | 1  | 0  | 7.50                           |

| 1  | 1  | 1  | External resistor can be used. |

data in the V<sub>0</sub>-resistor ratio register. Table 12 shows the value of (1+Rb/Ra) ratio (reference value).

Figure 9 The V<sub>0</sub> voltage as a function of the V<sub>0</sub> voltage regulator internal resister internal resistor and the electronic volume register [Ta=25°C]

<Setup example : When setting Ta = 25C and V\_0 = 7V on an SED15A6\*\*\* model with temperature gradient of -0.1% /°C>

From Figure 9 and expression A-1, the following setting will be employed.

#### Table 13

| Content                                             | Resistors |    |    |    |    |    |    |    |  |

|-----------------------------------------------------|-----------|----|----|----|----|----|----|----|--|

| Content                                             | D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

| Resistance ratio of Vo adjusting built-in resistors | 0         | 0  | 1  | 0  | 0  | 0  | 1  | 1  |  |

| Electronic volume                                   | 1         | 0  | 0  | 1  | 0  | 0  | 0  | 0  |  |

Table 14 shows  $V_0$  voltage variable range and its variable step available from the electronic volume function

when the above setting is employed.

#### Table 14

| Vo             | Min.      |    | Тур.     |    | Max.      | Unit |

|----------------|-----------|----|----------|----|-----------|------|

| Variable range | 6.41[80H] | to | 7.0[90H] | to | 7.58[9FH] | [V]  |

| Variable step  |           |    | 37.92    |    |           | [mV] |

[]: Commands selected from the electronic volume.

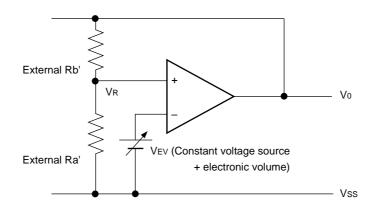

#### When external resistor is used (when the builtin resistor for Vo adjustment is not used)

It is also possible to select a supply voltage V<sub>0</sub> for LCD without using the built-in V<sub>0</sub> voltage adjusting resistors (resistance ratio select command [27H] for the built-in V<sub>0</sub> voltage adjusting resistors) by adding a resistor across Vss and V<sub>R</sub> as well as V<sub>R</sub> and V<sub>0</sub>. In this case too, using the electronic volume allows you to control LCD V<sub>0</sub> through the command and, thus, adjust contrast of LCD

display.

Voltage V<sub>0</sub> is given by the following expression when external resistance values Ra' and Rb' are specified in the range of V<sub>0</sub> < V<sub>OUT</sub>:

$V_0 = (1 + Rb/Ra) \cdot V_{EV}$

=  $(1+Rb/Ra) \cdot (1-\alpha/200) V_{REG}$  (Expression B-1) Vev =  $(1-\alpha/200) \cdot V_{REG}$

VREG represents the constant voltage source on the IC. Its value at Ta = 25 °C is constant as shown in Table 10.

Figure 10

<A setting example: When setting Ta = 25C and V<sub>0</sub> = 7V on an SED15A6\*\*\* model with temperature gradient =-0.1% C>

When the intermediate resistor values (D4, D3, D2, D1, D0) = (1, 0, 0, 0) are selected from the electronic volume, the following is given by expression B-1 since  $\alpha$  = 15 and V REG = 1.2V (Expression B-2).

$V_0 = (1+Rb'/Ra') \bullet (1-\alpha/200) \bullet V_{REG}$

$7V = (1+Rb'/Ra') \cdot (1-15/200) \cdot 1.2$

(Expression B-2)

If you select 5  $\mu$ A for the current conducted to Ra' and

#### Table 15

Rb', the following expression is derived:

$Ra' + Rb' = 1.4M\Omega \qquad (Expression B-3)$  Thus, the following is derived from expressions B-2 and B-3:

$\therefore$  Ra' = 220k $\Omega$ , Rb' = 1180k $\Omega$

Table 14 shows the command selected from the electronic volume. Table 16 lists V<sub>0</sub> voltage variable range and variable steps available from the electronic volume function.

| Content                                                     |    |    |    | Re | esiste | ors |    |    |

|-------------------------------------------------------------|----|----|----|----|--------|-----|----|----|

| Content                                                     | D7 | D6 | D5 | D4 | D3     | D2  | D1 | D0 |

| Resistance ratio of built-in Vo voltage adjusting resistors | 0  | 0  | 1  | 0  | 0      | 1   | 1  | 1  |

| Electronic volume                                           | 1  | 0  | 0  | 1  | 0      | 0   | 0  | 0  |

#### Table 16

| Vo             | Min.      |    | Тур.     |    | Max.      | Unit |

|----------------|-----------|----|----------|----|-----------|------|

| Variable range | 6.45[80H] | to | 7.0[90H] | to | 7.64[9FH] | [V]  |

| Variable step  |           |    | 38.4     |    |           | [mV] |

[]: Commands selected from the electronic volume.

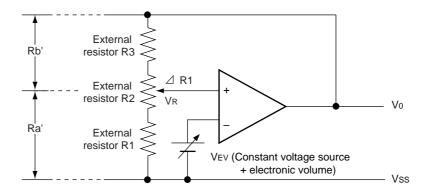

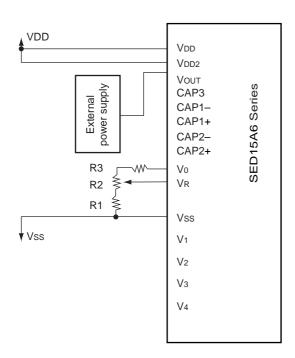

# When using external resistors (When using variable resistors in stead of the built-in V<sub>0</sub> voltage adjusting resistors)

Adding external variable resistors to the above mentioned external resistors allows you to select an LCD drive voltage  $V_0$  through fine tuning of Ra' and Rb'. In this case too, using the electronic volume function permits you to control an LCD voltage through the command and, thus, adjust contrast of the LCD display.

You can determine the V<sub>0</sub> voltage from the following expression when fine adjustment of Ra' and Rb' is done

by specifying resistance values of external resistors R1 and R2 (variable resistors) and R3 within the range of  $|V_0| < |V_{OUT}|$ :

$$V_{0} = \{1+(R3+R2-\Delta R2) / (R1+\Delta R2)\} \bullet V_{EV} \\ = \{1+(R3+R2-\Delta R2) / (R1+\Delta R2)\} \bullet \\ (1-\alpha/200) \bullet V_{REG} \qquad (Expression C-1) \\ [V_{EV} = (1-\alpha/200) \bullet V_{REG}]$$

Where, VREG is the constant voltage source in the IC and its value remains at a constant level as shown in Table 10.

Figure 11

<A setting example: When setting Ta = 25C and V\_0 = 5 to 9V on an SED15A6\*\*\* model with Temperature gradient = -0.1% C>

$\alpha = 15$  and  $V_{REG} = 1.2V$  when intermediate resistor values (D4, D3, D2, D1, D0) = (1, 0, 0, 0, 0) are selected from the electronic volume. Thus, using expression C-1, you can select  $V_0 = 9V$  when  $\Delta R2 = 0\Omega$  in the following manner:

$9V = \{1+(R3+R2) / R1\} \bullet (1-15/200) \bullet 1.2$

$R3 + R2 = 7.11 \cdot R1$  (Expression C-2) If you select 5 uA for the current to be conducted across V<sub>0</sub> and Vss when V<sub>0</sub> = 7V, sum of resistance of R1, R2 and R3 can be derived as shown below:

```

\begin{array}{ll} R1+R2+R3=1.4M\Omega & (Expression C-3).\\ From expressions C-2 and C-3, R1=1.4M\Omega / \\ 8.11=173K\Omega.\\ And, you can select V = 5V when $\Delta R2 = R2$ through the following computation: \\ 5V = = {1+R3/(R1+R2) } \bullet (1-15/200) \bullet 1.2\\ R3/(R1+R2) = 3.5 & (Expression C-4).\\ R2 = 137@ and R3 = 1.09 M\Omega are derived from expressions C-2, C-3 and C-4.\\ Table 15 lists the commands used, and Table 17 shows \\ \end{array}

```

Table 15 lists the commands used, and Table 17 shows V<sub>0</sub> voltage variable voltage range and variable steps available from the electronic volume.

#### Table 17

| Vo             | Min.      |    | Тур.     |    | Max.      | Unit |

|----------------|-----------|----|----------|----|-----------|------|

| Variable range | 6.39[80H] | to | 7.0[90H] | to | 7.57[9FH] | [V]  |

| Variable step  |           |    | 38.1     |    |           | [mV] |

[]: Commands selected from the electronic volume.

- \* When using the built-in V<sub>0</sub> voltage adjusting resistors or the electronic volume function, both of the voltage adjustment circuit and the voltage follower circuit must be activated, as a minimum requirement, by the power control set command. When the booster is circuit is turned off, necessary voltage must be supplied from Vout.

- \* VR pin is enabled only when the built-in Vo voltage adjusting resistors are not used. VR pin must be made open when these resistors are used.

- \* Since VR pin has a higher input impedance, appropriate noise protection measures must provided including cutting the wiring distance shorter or using shielded wire.

#### **Voltage Follower Circuit**

The V<sub>0</sub> voltage is divided to generate the V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub> voltages by on-chip resistor circuit. And the V<sub>1</sub>, V<sub>2</sub>, V<sub>3</sub> and V<sub>4</sub> voltages are impedance-converted by voltage follower, and provide to LCD driver circuit.

LCD bias ratio can be selected by LCD bias set command which is 1/6 bias or 1/8 bias for SED15A6 series.

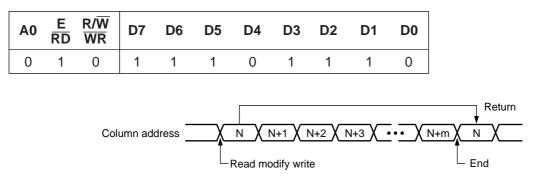

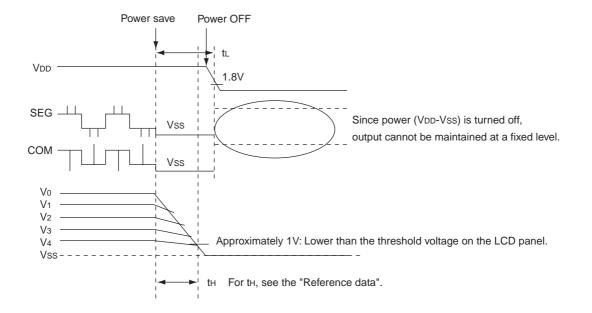

#### **On-chip Power Supply Turn Off Sequence**

Before turning the built-in power supply off, to discharge the remaining electric charge of LCD panel and power supply PIN etc., it is recommended to turn on the power save mode employing the following command sequence. You can also turn the built-in power supply off by initializing it using RES pin or the reset command. Here, of SED15A6D0B with built-in power supply being only used, LOW level signal entering RES pin discharges Vout, thereby introducing shorting across Vout–VDD2 and Vo–Vss. Of SED15A6D1B/SED15A6D2B with external power supply being used, discharge the electric charge by short-circuiting the external power supply to Vss when the power supply is off or power is being saved. (VOUT and V0 electric charge discharging functions are not in the IC)

| Comuchan | Contents              |    | _  | Со | mmar | nd ad | dress |    |    |

|----------|-----------------------|----|----|----|------|-------|-------|----|----|

| Sequence | (command and state)   | D7 | D6 | D5 | D4   | D3    | D2    | D1 | D0 |

| Step1    | Display OFF           | 1  | 0  | 1  | 0    | 1     | 1     | 1  | 0  |

|          | $\downarrow$          |    |    |    |      |       |       |    |    |

| Step2    | Display all points on | 1  | 0  | 1  | 0    | 0     | 1     | 0  | 1  |

|          | $\downarrow$          |    |    |    |      |       |       |    |    |

| End      | Built-in power OFF    | 0  | 0  | 1  | 0    | 1     | 0     | 0  | 0  |

#### Table 18

Power save command (composite command)

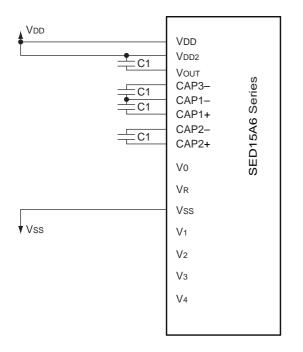

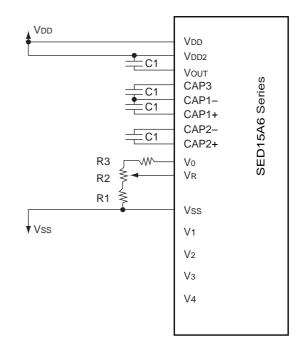

#### Sample Circuits

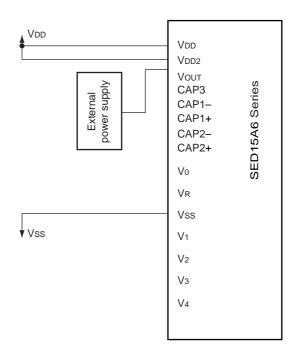

1. When the booster, voltage adjustment and V/F circuits are all used [SED15A6D0B]  $\,$

(1) When built-in V<sub>0</sub> voltage adjusting resistors are used (When V<sub>DD2</sub> = V<sub>DD</sub> is boosted 4 times)

(2) When built-in V<sub>0</sub> voltage adjusting resistors are not used (When V<sub>DD2</sub> = V<sub>DD</sub> boosted 4 times)

- 2. When the voltage adjustment and V/F circuits alone are used

- (1) When built-in V $_0$  voltage adjusting resistors are not used [SED15A6D1B]

(2) When built-in V<sub>0</sub> voltage adjusting resistors are used Voltage Follower Circuit [SED15A6D1B]

4. When built-in power supply is not used[SED15A6D2B]

3. When V/F circuit alone is used [SED15A6D1B]

\* Since VR pin has a higher impedance, wiring distance must be minimized or shielded wire must be used.

.

|                                                 | Sample setting |  |  |  |  |  |  |  |  |

|-------------------------------------------------|----------------|--|--|--|--|--|--|--|--|

| When V <sub>0</sub> is varied between 8 and 9V. |                |  |  |  |  |  |  |  |  |

| ltem                                            | Setting Unit   |  |  |  |  |  |  |  |  |

|                                                 |                |  |  |  |  |  |  |  |  |

Figure 12

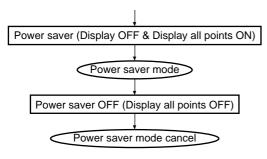

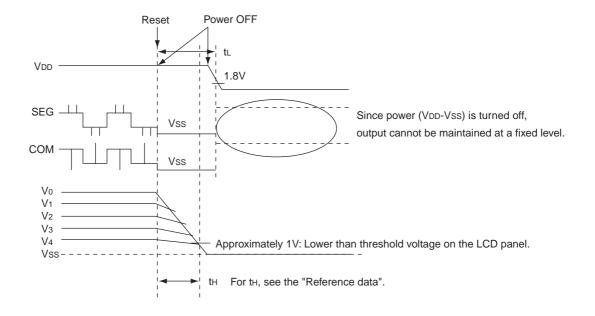

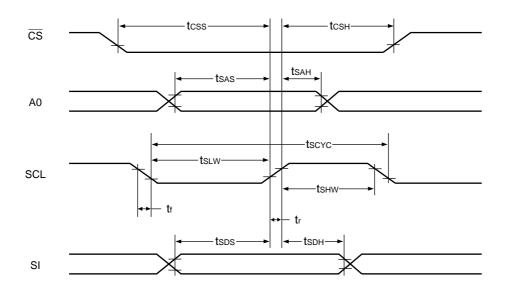

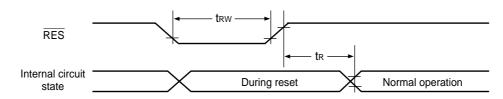

#### **Reset Circuit**

When pin goes low,  $\overline{\text{RES}}$  or when Reset command is used, this LSI is initialized.

Initialized states

- Serial interface internal shift register and counter clear

- Power saver mode is entered.

- Oscillation circuit is stopped.

- The LCD power supply circuit is stopped.

- Display OFF

- Display all points ON (Display all points ON ON/ OFF command D0 = "1")

- Segment/common driver outputs go to the Vss level.

- Display normal

- Page address=0H

- Column address=0H

- Display start line address=set at the first line

- Segment driver direction=normal

- Common driver direction=normal

- Read modify write OFF

- Power control register (D2, D1, D0) = (0, 0, 0)

- V0-resistor ratio register (D2, D1, D0) = (0, 0, 0)

- Electronic volume register (D4, D3, D2, D1, D0) = (1, 0, 0, 0, 0)

- LCD power supply bias ratio = 1/6 bias (SED15A6)

- Test mode is released.

#### \* Voltage short-circuit across Vout and VDD2 as well as Vo and Vss [allowed only when RES pin = LOW level].

When reset is detected, this LSI is set to above initialized states. However it has no effect on contents of DDRAM. As seen in "Microprocessor Interface (Reference Example)", connect  $\overline{\text{RES}}$  pin to the reset pin of the MPU and initialize the MPU at the same time. The initialization by  $\overline{\text{RES}}$  pin is always required during power-on.

If the control signal from MPU is HZ, an overcurrent may flow through the LSI. A protection is required to prevent the HZ signal at the input pin during power-on. In case the SED15A6 series does not use the on-chip LCD power supply circuit, after RES pin is turnd LOW to HIGH, the external LCD power supply must be turned on.

# 7. COMMANDS

The SED15A6 series identifies the data bus by a combination of A0,  $\overline{\text{RD}}$  (E),  $\overline{\text{WD}}(R/\overline{W})$  signals.

In the 8080-series MPU interface, the command is activated when a low pulse is input to  $\overline{\text{RD}}$  pin for reading and when a low pulse is input to  $\overline{\text{WD}}$  pin for writing. In the 6800-series MPU interface, the SED15A6 series enters a read mode when a high level is input to  $\overline{\text{R/W}}$  pin and a write mode when a low level is input to  $\overline{\text{R/W}}$  pin, and the command is activated when a high pulse is input to  $\overline{\text{E}}$  pin. Therefore, in the command explanation and command table, the 6800-series MPU interface is different from the 8080-series MPU interface in that  $\overline{\text{RD}}(\text{E})$  becomes "1 (H)" in Display data read command. And when the serial interface is selected, the data is input in sequence starting with D7.

Taking the 8080-series MPU interface as an example, commands will be explained below.

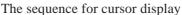

#### **Explanation of commands**

#### **Display ON/OFF**

This command turns the display ON and OFF.

| A0 | E<br>RD | R/₩<br>WR | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0     | Setting                   |

|----|---------|-----------|----|----|----|----|----|----|----|--------|---------------------------|

| 0  | 1       | 0         | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0<br>1 | Display OFF<br>Display ON |

When the Display OFF command is executed when in the Display all points ON mode, Power saver mode is entered. See the section on the Power saver for details.

#### **Display normal/reverse**

This command can reverse the lit and unlit display without overwriting the contents of the DDRAM.