# **EPSON**

CARD-686

Hardware Manual

## **NOTICE**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

©Seiko Epson Corporation 2000 All rights reserved.

PC/AT,PS/2,VGA and Monochrome are trademarks and/or registered trademarks of International Business Machines Corporation. MS-DOS is registered trademark of Microsoft. AMD and AMD-K6 are trademarks and/or registered trademarks of Advanced Micro Devices, Inc.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

# Contents

| 1. BASIC SPECIFICATIONS                          |          |

|--------------------------------------------------|----------|

| 1.1 Block Diagram                                |          |

| 2. PHISYCAL SPECIFICATIONS                       | 4        |

| 2.1 Dimensions                                   | 4        |

| 2.2 Weight                                       |          |

| 2.3 Installation Method                          |          |

| 3 . PIN CONFIGURATION                            |          |

| 4 . PIN FUNCTIONS                                |          |

| 4.1 ISA Bus                                      |          |

| 4.2 LCD Interface                                |          |

| 4.3 CRT Interface                                |          |

| 4.4 IDE Interface                                |          |

| 4.4 IDE Interface                                |          |

| 4.5 FDD Interface 4.6 Keyboard Interface         |          |

|                                                  |          |

| 4.7 Mouse Interface                              |          |

| 4.8 Parallel Interface                           |          |

| 4.9 Serial Interface                             |          |

| 4.10 Power Management                            |          |

| 4.11 BIOS ROM Update Interfaces                  | 14       |

| 4.12 Speaker Interfaces                          |          |

| 4.13 Power Supply                                |          |

| 5. DATAILED DESCRIPTION OF FUNCTIONS             |          |

| 5.1 System Overview                              |          |

| 5.1.1 Memory map                                 | 16       |

| 5.1.2 DMA controllers                            | 18       |

| 5.1.3 System interrupts and interrupt controller | 19       |

| 5.1.4 Timer counters                             |          |

| 5.1.5 Real-time clock and CMOS RAM               | 21       |

| 5.1.6 I/O MAP                                    | 22       |

| 5.2 ISA Bus Interface                            | 26       |

| 5.2.1 ISA Bus signals                            | 26       |

| 5.2.2 ISA bus cycle                              | 29       |

| 5.2.3 Memory read/write cycles                   | 29       |

| 5.2.4 I/O read/write cycles                      |          |

| 5.2.5 DMA cycle                                  |          |

| 5.2.6 External bus master cycle                  |          |

| 5.2.7 External bus mastering precautions         | 39       |

| 5.2.8 Refresh cycle                              | 40       |

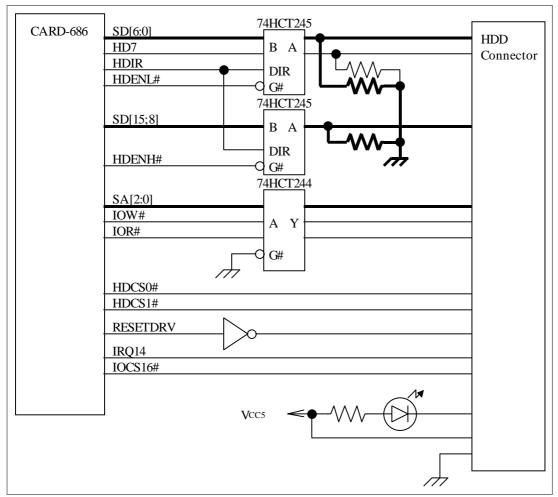

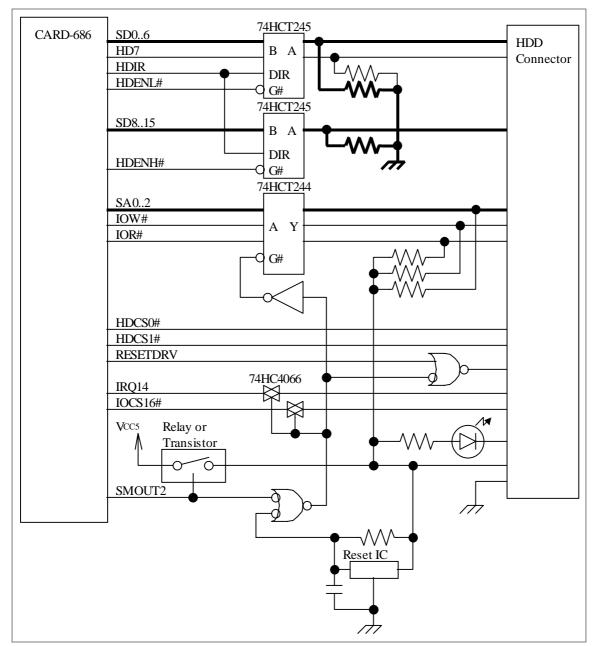

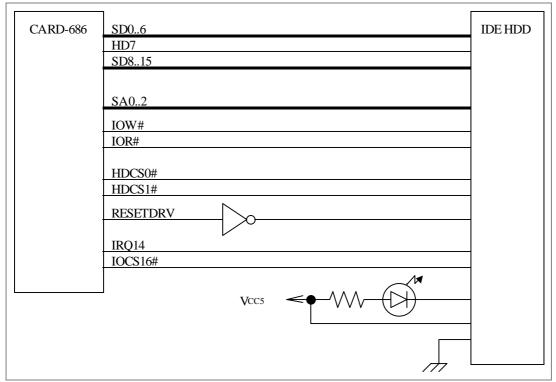

| 5.3 Hard Disk Bus Interface                      |          |

| 5.3.1 Features of the hard disk interface        |          |

| 5.3.2 Hard Disk Interface Signals                |          |

| 5.3.3 Hard disk bus cycles                       |          |

| 5.3.4 Hard disk hardware option                  |          |

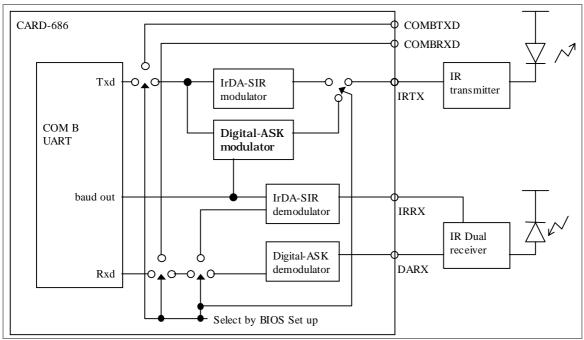

| 5.4 Serial Port Interface                        |          |

| 5.4.1 Serial port interface signals              |          |

| 5.4.2 Serial port functions                      | 49<br>50 |

| 5.4.2 Serial port functions                      |          |

| 5.4.4 Infrared Communications                    |          |

| J.4.4 IIII aica Communications                   | 33       |

| 5.5 Parallel Port Interface                                |    |

|------------------------------------------------------------|----|

| 5.5.1 Parallel Port Signals                                |    |

| 5.5.2 Parallel port operation                              | 56 |

| 5.5.3 High-speed parallel mode operation                   | 56 |

| 5.5.4 Parallel port buffering                              |    |

| 5.5.5 Pin configuration                                    | 59 |

| 5.6 Power Management                                       | 60 |

| 5.6.1 Power management signals                             | 60 |

| 5.6.2 Suspend and resume control                           | 61 |

| 5.6.3 SMOUT                                                |    |

| 5.7 Keyboard Controller                                    |    |

| 5.7.1 Keyboard controller signals                          | 64 |

| 5.7.2 Explanation of registers and commands                | 64 |

| 5.7.3 Keyboard and mouse interface                         | 66 |

| 5.8 VGA Controller                                         |    |

| 5.8.1 CRT and LCD interface signals                        | 67 |

| 5.8.2 Panel interface                                      |    |

| 5.9 Floppy Disk Controller                                 | 71 |

| 5.9.1 Floppy disk control signals                          |    |

| 5.9.2 Floppy disk interface                                |    |

| 5.10 RTC/CMOS RAM                                          |    |

| 5.10.1 Register description                                |    |

| 5.10.2 About V <sub>BK</sub>                               |    |

| 5.10.3 POWERGOOD                                           |    |

| 5.11 Output of General Purpose Timer (Watchdog Timer)      |    |

| 6 . ENVIRONMENTAL REQUIREMENTS                             |    |

| 6.1 Temperature                                            |    |

| 6.2 Humidity                                               |    |

| 6.3 Electrostatic Breakdown Immunity                       |    |

| 7 . MECHANICAL CHARACTERISTICS                             |    |

| 7.1 Insertion and Removal Force                            |    |

| 7.2 Insertions and Removals                                |    |

| 8 . DC CHARACTERISTICS (RECOMMENDED AND NOMINAL)           | 79 |

| 9 . PIN ELECTRICAL CHARACTERISTICS                         |    |

| 10 . AC CHARACTERISTICS (RECOMMENDED AND REFERENCE VALUES) |    |

| 10.1 Timing Charts                                         | 95 |

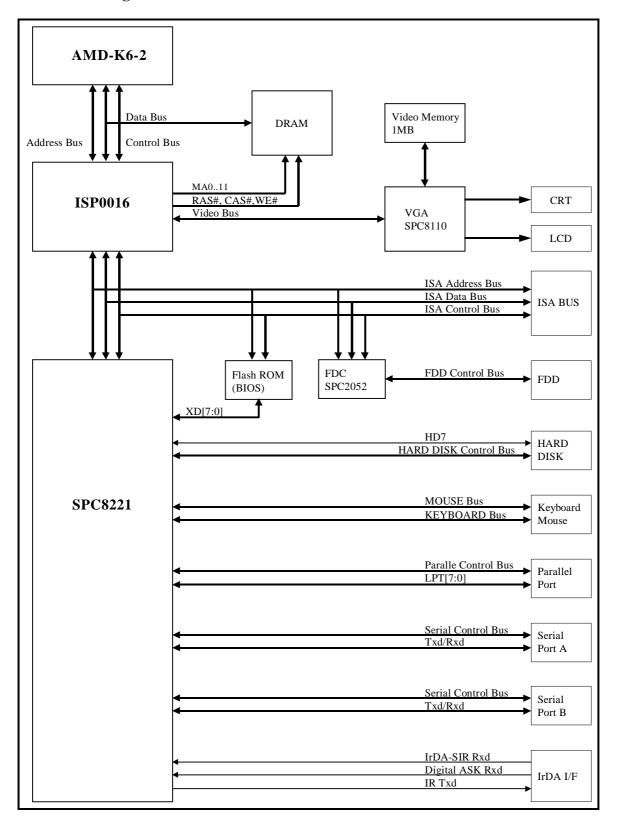

#### 1.1 BASIC SPECIFICATIONS

SCE86638 Series (CARD-686) consolidates the main board blocks of the ISA architecture into a credit card sized card. The configuration is described below.

## **CPU**

AMD-K6-2 (manufactured by AMD Corp.)

#### I/O block

ISP0016 (manufactured by Seiko Epson Corp.) SPC8221 (manufactured by Seiko Epson Corp.)

Interrupt controllers (82C59A equivalent. ×2)

Programmable timers (82C54 equivalent. ×2)

DMA controllers (82C37A A equivalent. ×2)

Memory mapper (74LS612 equivalent.)

Parallel I/O port

Serial I/O ports (16C550 equivalent. ×2) Real-time clock (146818 equivalent.)

IDE interface

• Support for large-capacity IDE HDD (8.4 GB)

#### Memory block

DRAMFlash ROM (for BIOS)32 or 64 MB256 KB

#### **Keyboard Interface block**

8042 Software emulation

- PS/2 Style Keyboard

- PS/2 Style Mouse

## Video block

SPC8110 (manufactured by Seiko Epson Corp.)

- CRT

- STN mono/color (single/dual panel)

- TFT color

- VRAM 1 MB

#### FDC block

SPC2052 (manufactured by Seiko Epson Corp.)

- Equivalent to μPD765.Drive : Support two units.

- Transfer rate: 250Kbps, 300Kbps, 500 Kbps

#### CARD-686 Model List

| Model No   | CPU Clock | DRAM  |

|------------|-----------|-------|

| SCE8663802 | 233 MHz   | 32 MB |

| SCE8663803 | 233 MHz   | 64 MB |

#### **CAUTION**

1) The surface of the CARD-686 becomes very hot during and immediately after use. To prevent accidental burns, avoid touching it.

Observe the following precautions

- Warn service personnel and other people who might come in contact with the CARD-686 that the card becomes hot.

- If appropriate, after installing the CARD-686, attach a label to it warning that it is hot.

- If appropriate, place a cover over the CARD-686 to prevent people from coming in contact with it accidentally.

- 2) Due to structural constraints, the CARD-686 emits more radiation noise that the CARD-586. Accordingly, appropriate measures must be taken to counter EMI in the customer's system.

- 3) Due to structural constraints of the CARD-686, measures must be implemented to counter static electrical noise in the customer's system.

- 4) Never touch the CARD-686's terminal contacts with your hands or metallic objects.

- 5) Never bend or drop the CARD-686 or subject it to mechanical shock.

- 6) Avoid exposure to heat, moisture, and direct sunlight.

- 7) Never insert or remove the CARD-686 while the power is on.

- 8) Unauthorized reproduction or modification of the BIOS is prohibited.

- 9) When designing products that incorporate the CARD-686, please refer to the application notes.

# 1.2 Block Diagram

Figure 1-1 CARD-686 Block Diagram

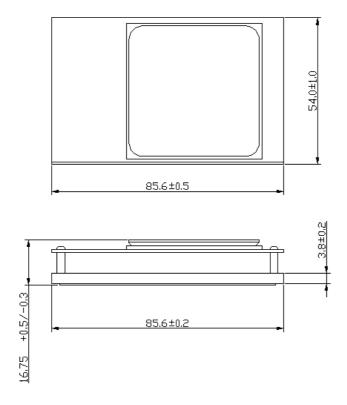

# 2. PHISYCAL SPECIFICATIONS

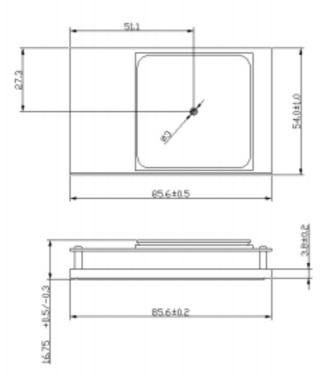

# 2.1 Dimensions

85.4mm  $\times$  54.0mm  $\times$  16.75mm

# 2.2 Weight

91(g)

Figure 2-1 CARD-686 Dimensions

# 2.3 Installation Method

The card socket side connector  $SEK6669P_{01}$  (without ejector) can be used.

Note: SEK6669P<sub>02</sub> (with ejector) cannot be used.

- Thickness of board to which socket side connector is fitted should not exceed 1.6mm.

- Socket side connector fixing should be done with screws. (Screws M2.5 × 8 hexagonal nuts)

# 3. PIN CONFIGURATION

# **CARD-686 Pin Configuration**

| 1  | GND      | 119 | GND      | 41 | COMACTS#   | 159 | COMARXD    |

|----|----------|-----|----------|----|------------|-----|------------|

| 2  | GND      | 120 | GND      | 42 | COMARTS#   | 160 | COMATXD    |

| 3  | EXDOTCLK | 121 | FPDOTCLK | 43 | COMADSR#   | 161 | COMADCD#   |

| 4  | LD6      | 122 | LD7      | 44 | IRRX       | 162 | IRTX       |

| 5  | LD4      | 123 | LD5      | 45 | LPTSTROBE# | 163 | LPTAFD#    |

| 6  | LD2      | 124 | LD3      | 46 | LPTD0      | 164 | LPTERROR#  |

| 7  | LD0      | 125 | LD1      | 47 | LPTACK#    | 165 | LPTBUSY    |

| 8  | FPVTIM   | 126 | FPHTIM   | 48 | LPTPE      | 166 | LPTSLCT    |

| 9  | FPAC     | 127 | LD8      | 49 | LPTD1      | 167 | LPTINIT#   |

| 10 | FPVCCON  | 128 | FPVEEON  | 50 | LPTD2      | 168 | LPTSLCTIN# |

| 11 | LD9      | 129 | FPBLANK# | 51 | LPTD3      | 169 | LPTD4      |

| 12 | LD11     | 130 | LD10     | 52 | LPTD5      | 170 | LPTD6      |

| 13 | LD13     | 131 | LD12     | 53 | LPTD7      | 171 | LPTDIR     |

| 14 | LD15     | 132 | LD14     | 54 | HDIR       | 172 | HD7        |

| 15 | BLUE     | 133 | BRTN     | 55 | HDENL#     | 173 | HDENH#     |

| 16 | GREEN    | 134 | GRTN     | 56 | HDCS0#     | 174 | HDCS1#     |

| 17 | RED      | 135 | RRTN     | 57 | SUSSTAT#   | 175 | VBK        |

| 18 | VSYNC    | 136 | HSYNC    | 58 | BATLOW#    | 176 | EXTSMI#    |

| 19 | LD17     | 137 | LD16     | 59 | GND        | 177 | GND        |

| 20 | RESERVE  | 138 | RESERVE  | 60 | GND        | 178 | GND        |

| 21 | MSDATA   | 139 | MSCLK    | 61 | BATWRN#    | 179 | RESERVE    |

| 22 | KBDATA   | 140 | KBCLK    | 62 | POWERGOOD  | 180 | SRBTN#     |

| 23 | FDWP#    | 141 | FDRD#    | 63 | SPKOUT     | 181 | WDTIM#     |

| 24 | FDINDEX# | 142 | FDDCHG#  | 64 | FLOAT#     | 182 | PGM        |

| 25 | FDTRK0#  | 143 | FDWE#    | 65 | ROMCE0#    | 183 | RESERVE    |

| 26 | FDWD#    | 144 | FDHIDEN  | 66 | RESERVE    | 184 | RESERVE    |

| 27 | VCC5     | 145 | VCC5     | 67 | SD7        | 185 | RESETDRV   |

| 28 | VCC5     | 146 | VCC5     | 68 | SD6        | 186 | IOCHCK#    |

| 29 | VCC3     | 147 | VCC3     | 69 | SD5        | 187 | IRQ9       |

| 30 | VCC3     | 148 | VCC3     | 70 | SD4        | 188 | DRQ2       |

| 31 | FDDS2#   | 149 | FDDS1#   | 71 | SD3        | 189 | WS0#       |

| 32 | FDMT2#   | 150 | FDMT1#   | 72 | SD2        | 190 | SMEMW#     |

| 33 | FDSIDE   | 151 | FDSTEP#  | 73 | SD1        | 191 | SMEMR#     |

| 34 | FDDIR    | 152 | RESERVE  | 74 | SD0        | 192 | IOW#       |

| 35 | RESERVE  | 153 | DARX     | 75 | IOCHRDY    | 193 | IOR#       |

| 36 | COMBDTR# | 154 | COMBRI#  | 76 | AEN        | 194 | DACK3#     |

| 37 | COMBCTS# | 155 | COMBRXD  | 77 | SA19       | 195 | DRQ3       |

| 38 | COMBRTS# | 156 | COMBTXD  | 78 | SA18       | 196 | DACK1#     |

| 39 | COMBDSR# | 157 | COMBDCD# | 79 | SA17       | 197 | DRQ1       |

| 40 | COMADTR# | 158 | COMARI#  | 80 | SA16       | 198 | REF#       |

|    |          |     |          |    | 1          |     |            |

| 81  | SA15   | 199 | SCLK     |

|-----|--------|-----|----------|

| 82  | VCC3   | 200 | VCC3     |

| 83  | VCC3   | 201 | VCC3     |

| 84  | VCC5   | 202 | VCC5     |

| 85  | VCC5   | 203 | VCC5     |

| 86  | SA14   | 204 | IRQ7     |

| 87  | SA13   | 205 | IRQ6     |

| 88  | SA12   | 206 | IRQ5     |

| 89  | SA11   | 207 | IRQ4     |

| 90  | SA10   | 208 | IRQ3     |

| 91  | SA9    | 209 | DACK2#   |

| 92  | SA8    | 210 | TC       |

| 93  | SA7    | 211 | BALE     |

| 94  | SA6    | 212 | OSC      |

| 95  | SA5    | 213 | MEMCS16# |

| 96  | SA4    | 214 | IOCS16#  |

| 97  | SA3    | 215 | IRQ10    |

| 98  | SA2    | 216 | IRQ11    |

| 99  | SA1    | 217 | IRQ12    |

| 100 | SA0    | 218 | IRQ15    |

| 101 | SBHE#  | 219 | IRQ14    |

| 102 | LA23   | 220 | DACK0#   |

| 103 | LA22   | 221 | DRQ0     |

| 104 | LA21   | 222 | DACK5#   |

| 105 | LA20   | 223 | DRQ5     |

| 106 | LA19   | 224 | DACK6#   |

| 107 | LA18   | 225 | DRQ6     |

| 108 | LA17   | 226 | DACK7#   |

| 109 | MEMR#  | 227 | DRQ7     |

| 110 | MEMW#  | 228 | MASTER#  |

| 111 | SD8    | 229 | SD12     |

| 112 | SD9    | 230 | SD13     |

| 113 | SD10   | 231 | SD14     |

| 114 | SD11   | 232 | SD15     |

| 115 | SMOUT3 | 233 | SMOUT2   |

| 116 | SMOUT1 | 234 | SMOUT0   |

| 117 | GND    | 235 | GND      |

|     | GND    | 236 | GND      |

# 4. PIN FUNCTIONS

The functions are described below for each of the interfaces.

The abbreviations in the "Type" column have the following meanings:

I: Input pinO: Output pin

O OD: Output pin, open-drain output

IO: Input /output pin

IO OD: Input / output pin, open-drain output

# 4.1 ISA Bus

| Pin Name  | Type | Functions                                                       |

|-----------|------|-----------------------------------------------------------------|

| SA[19:17] | О    | System Address Bus                                              |

| SA[16:0]  | IO   | SA19-SA0 of the bus                                             |

| LA[23:17] | IO   | Latchable Address Bus                                           |

|           |      | LA23-LA17 of the bus                                            |

| SBHE#     | IO   | System Byte High Enable Active Low                              |

|           |      | This signal indicates that SD[15:8] is effective.               |

| SD[15:0]  | IO   | System Data Bus                                                 |

|           |      | 16-bit data bus                                                 |

| IOR#      | IO   | I/O Read Active Low                                             |

|           |      | This signal requests an I/O device on the bus to output data to |

|           |      | SD[15:8] or SD[7:0].                                            |

| IOW#      | IO   | I/O Write Active Low                                            |

|           |      | This signal requests an I/O device on the bus to accept the     |

|           |      | data at SD[15:8] or SD[7:0].                                    |

| IOCS16#   | I    | I/O Chip select 16 Active Low                                   |

|           |      | This signal lets the I/O device on the bus indicate the CARD-   |

|           |      | 686 that 16-bit transfer is possible by the current I/O cycle.  |

| MEMR#     | IO   | Memory read Active Low                                          |

|           |      | This signal requests a memory device on the bus to output       |

|           |      | data to SD[15:8] or SD[7:0].                                    |

| MEMW#     | IO   | Memory write Active Low                                         |

|           |      | This signals request the memory device on the bus to accept     |

|           |      | data at SD[15:8] or SD[7:0].                                    |

| SMEMW#    | О    | System memory write Active Low                                  |

|           |      | This signal is active when a memory write cycle is started for  |

|           |      | the 0 to 1MB memory space on the bus.                           |

| SMEMR#    | О    | System memory read Active Low                                   |

|           |      | This signal is active when a memory read cycle is started for   |

|           |      | the in the 0 to 1MB memory space on the bus.                    |

| Pin Name       | Type  | Functions                                                                                                                                                                                                            |  |

|----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MEMCS16#       | I     | Memory chip select 16 Active Low This signal lets the memory device on the bus indicate the CARD-686 that 16-bit transfer is possible by the current memory.                                                         |  |

| AEN            | 0     | Address enable This signal indicates that the current cycle is a DMA cycle or a refresh cycle.                                                                                                                       |  |

| DRQ[7:5,3,1,0] | I     | DMA request Active High These signals request the CARD-686 for DMA transfer.                                                                                                                                         |  |

| DRQ2           | IO    | DRQ2 becomes an output signal when the internal FDD interface is enabled and becomes an input signal when it is disabled.                                                                                            |  |

| DACK[7:5,3:0]# | 0     | DMA acknowledge Active Low These signals indicate the DMA channel, which requested for a DMA transfer, that the request was accepted.                                                                                |  |

| TC             | О     | Terminal count Active High In a DMA transfer, this signal indicates the end of the DMA transfer                                                                                                                      |  |

| REF#           | IO OD | Refresh Active Low When this signal is active, it indicates that the cycle is a refresh cycle.                                                                                                                       |  |

| MASTER#        | I     | Master Active Low The bus master on this bus make this active in order to acquire the control authority of the bus. Before making this signal active, the bus master must make DRQn# active and must receive DACKn#. |  |

| SCLK           | 0     | System clock This is the basic 8.33-MHz ISA clock. This signal is not output when POWERGOOD is inactive. Note: The SCLK frequency varies with the CPU and the CPU clock of the CARD-PC.                              |  |

| OSC            | О     | Oscillator 14.3 MHz 50% duty clock output. This signal is not synchronized with the system clock.                                                                                                                    |  |

| IOCHCK#        | I     | I/O channel check  This signal informs the CARD-686 that a parity error or unrecoverable error has occurred in the memory or the I/O device on the bus.  When this signal becomes active, NMI occurs to the CPU.     |  |

| Pin Name                          | Type   | Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IOCHRDY                           | IO OD  | I/O channel ready This signal terminates the bus cycle. When the memory or the I/O device on the bus wants to extend the bus cycle, it can extend the cycle by setting this signal to low immediately after detecting an effective address and command. The CARD-686 continues the bus cycle until this signal becomes high. When the DMA or the bus master is transferred to the internal DRAM of the CARD-686, the CARD-686 makes IOCHRDY inactive to extend the bus.                                                                                                                                                                          |

| WS0#                              | I      | Zero wait state Active Low  Make this signal active in order to terminate the bus cycle without any wait states.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RESETDRV                          | 0      | Reset drive Active High  System initialization signal. Initialize devices on the bus by using this signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| BALE                              | 0      | Buffered address enable Active High  This signal indicates that SA[19:0] and LA[23:17] have become effective and the CPU cycle has started. During the DMA and refresh cycle, this signal becomes high.  Note: In case of the standard IBM-PC/AT, LA[23:17] becomes effective only at the beginning of the CPU cycle and devices on the bus need latch LA[23:17] by BALE. But the CARD-686 keep outputting effective addresses to LA[23:17] until the end of the cycle.                                                                                                                                                                          |

| IRQ[15,14,9] IRQ12 IRQ[11,10,7:3] | I O IO | Interrupt request  Active High  These signals request the CARD-686 for interruption  Since being used by the mouse interface, IRQ12 cannot be used on the bus.  When being used by the serial interface inside the CARD-686, IRQ[11,10,4,3] become outputs.  When being not used, they become inputs and can be used on the bus.  When being used by the parallel interface inside the CARD-686, IRQ[7,5] becomes outputs.  When being not used, they become inputs and can be used on the bus.  When being used by the FDD interface inside the CARD-686, IRQ6 become an output.  When being not used, it becomes an input and used on the bus. |

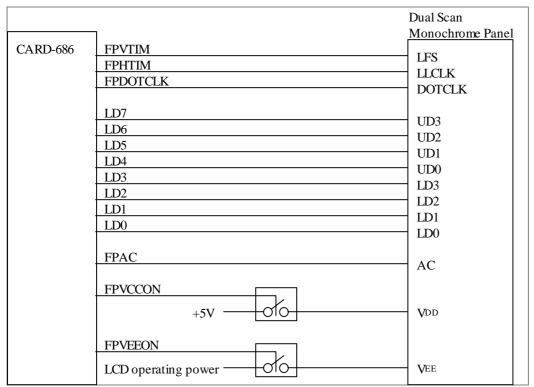

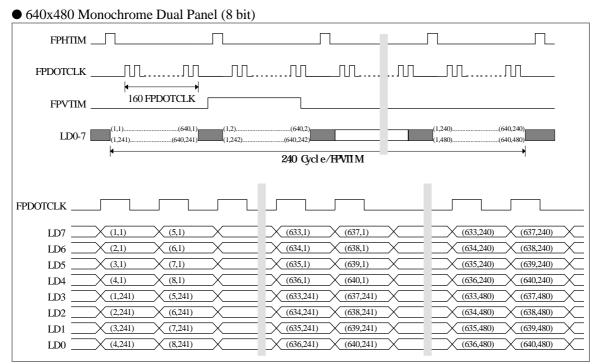

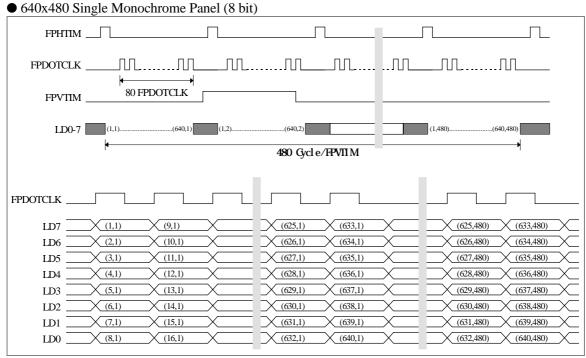

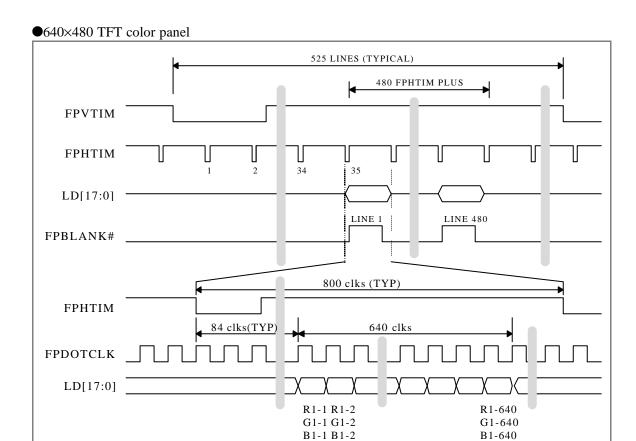

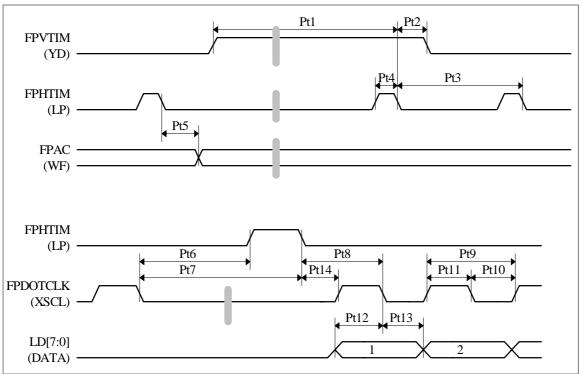

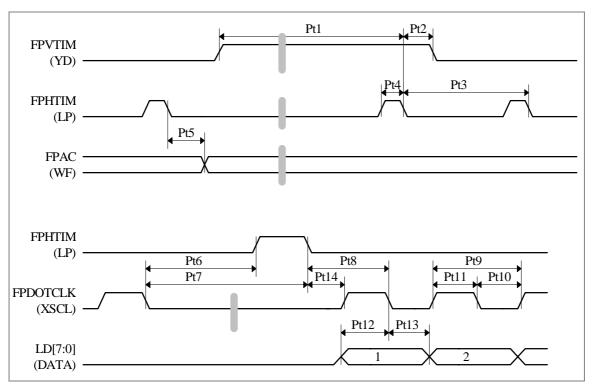

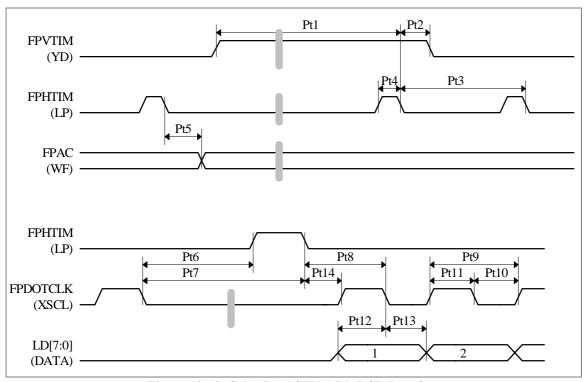

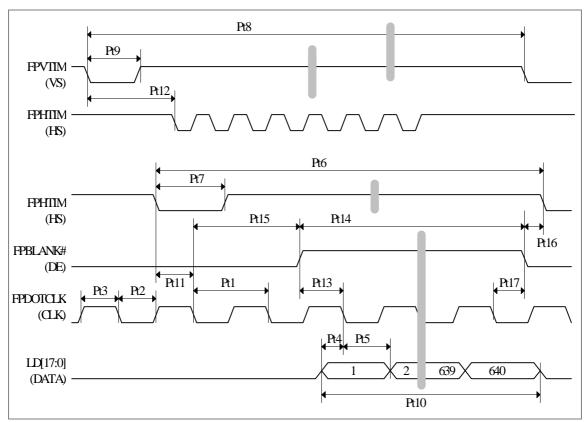

# 4.2 LCD Interface

| Pin Name | Type | Functions                                                                                                                                                          |  |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LD[17:0] | О    | Display data for flat panel display.                                                                                                                               |  |

|          |      | Flat panel display data.                                                                                                                                           |  |

| FPVTIM   | O    | Vertical display timing signal for a flat panel display.                                                                                                           |  |

|          |      | This signal indicates the display start timing of a screen for the flat panel.                                                                                     |  |

| FPHTIM   | 0    | -                                                                                                                                                                  |  |

| FFITINI  |      | Horizontal display timing signal for a flat panel display.                                                                                                         |  |

|          |      | This signal gives the timing for the start of a scan line.                                                                                                         |  |

| FPDOTCLK | O    | Data shift clock signal for a flat panel display.                                                                                                                  |  |

|          |      | This signal provides the shift clock for the display data.                                                                                                         |  |

| EXDOTCLK | 0    | Specify Flat Panel Data Shift Clock(normally not used).                                                                                                            |  |

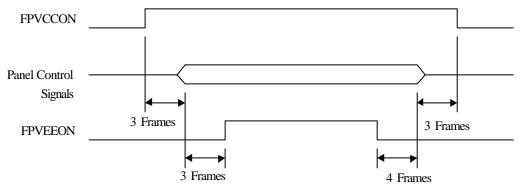

| FPVCCON  | О    | Flat panel display power supply control signal.                                                                                                                    |  |

|          |      | This signal turns on the logic power supply of the flat panel.                                                                                                     |  |

| FPVEEON  | О    | Flat panel display power supply control signal.                                                                                                                    |  |

|          |      | This signal turns on bias power of the flat panel.                                                                                                                 |  |

| FPAC     | О    | Liquid Crystal AC signal.                                                                                                                                          |  |

|          |      | This signal can be used when the simple matrix display monochrome panel requires an alternation.                                                                   |  |

| FPBLANK# | 0    | Flat panel data blank signal.                                                                                                                                      |  |

|          |      | This signal indicates the period that no data is displayed on<br>the TFT panel. This signal is generally connected to the<br>display enable (DE) of the TFT panel. |  |

# 4.3 CRT Interface

| Pin Name | Type | Functions                                                  |

|----------|------|------------------------------------------------------------|

| VSYNC    | 0    | Vertical display timing.                                   |

|          |      | This signal provides the vertical sync signal for a CRT.   |

| HSYNC    | О    | Horizontal Display Timing.                                 |

|          |      | This signal provides the horizontal sync signal for a CRT. |

| RED      | O    | Analog Color signal.                                       |

| RRTN     |      | Red return signal.                                         |

| GREEN    | O    | Color signal.                                              |

| GRTN     |      | Green return signal.                                       |

| BLUE     | 0    | Analog Color signal.                                       |

| BRTN     |      | Blue return signal.                                        |

# 4.4 IDE Interface

| Pin Name | Type | Functions                                         |                        |

|----------|------|---------------------------------------------------|------------------------|

| HDCS0#   | О    | Hard disk chip select 0                           | Active Low             |

|          |      | 1F0H~1F7H select signal.                          |                        |

| HDCS1#   | О    | Hard disk chip select 1                           | Active Low             |

|          |      | 3F6H~3F7H select signal.                          |                        |

| HDENH#   | О    | Hard disk buffer enable high                      | Active Low             |

|          |      | This signal is active during all 16-bit according | esses to the disk, and |

|          |      | can be used for buffer control of data bi         | ts DATA8-15 of the     |

|          |      | IDE drive interface.                              |                        |

| HDENL#   | O    | Hard disk buffer enable low                       | Active Low             |

|          |      | This signal is active during all disk cycles      | , and can be used for  |

|          |      | buffer control of data bits DATA0-7               | of the IDE drive       |

|          |      | interface.                                        |                        |

| HD7      | IO   | Hard disk bit 7                                   |                        |

|          |      | Bit 7 of the data bus in the hard disk inter      | face.                  |

| HDIR     | О    | Hard disk bus data direction                      |                        |

|          |      | Output for direction control of hard dis          | sk data buffer. This   |

|          |      | signal is high during read cycle.                 |                        |

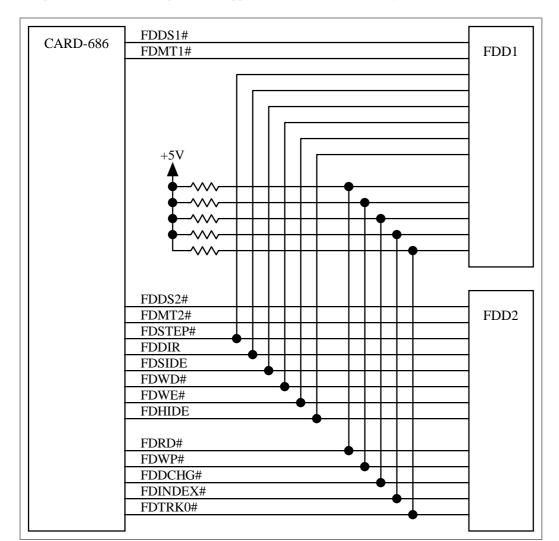

# 4.5 FDD Interface

| Pin Name | Type | Functions                                                      |                              |

|----------|------|----------------------------------------------------------------|------------------------------|

| FDDS1#   | O OD | Drive select 1                                                 | Active Low                   |

|          |      | Used as a select signal for d                                  | lrive 1.                     |

| FDDS2#   | O OD | Drive select 2                                                 | Active Low                   |

|          |      | Used as a select signal for d                                  | lrive 2.                     |

| FDMT1#   | O OD | Motor on 1                                                     | Active Low                   |

|          |      | Used as a motor on signal for                                  | or drive 1.                  |

| FDMT2#   | O OD | Motor on 2                                                     | Active Low                   |

|          |      | Used as a Motor on signal for                                  | for drive 2.                 |

| FDSTEP#  | O OD | Step                                                           | Active Low                   |

|          |      | Stepping pulses signal indicating the number of steps the head |                              |

|          |      | must move.                                                     |                              |

| FDDIR    | O OD | Direction                                                      |                              |

|          |      | This signal indicates the see                                  | ek direction.                |

|          |      | When low it indicates in                                       | ward movement, and when high |

|          |      | outward movement.                                              |                              |

| FDSIDE   | O OD | Side                                                           |                              |

|          |      | Head selection signal. When low it selects head 1, and when    |                              |

|          |      | high head 0.                                                   |                              |

| FDRD#    | I    | Read data                                                      |                              |

|          |      | Data input read from drive.                                    |                              |

| Pin Name | Type | Functions                                                    |                            |

|----------|------|--------------------------------------------------------------|----------------------------|

| FDWD#    | O OD | Write data                                                   |                            |

|          |      | Data input written to drive.                                 |                            |

| FDWE#    | O OD | Write enable                                                 | Active Low                 |

|          |      | This signal controls writing to the drive                    | ·.                         |

| FDWP#    | I    | Write Protect                                                | Active Low                 |

|          |      | This signal from the drive indicates tha write-protected.    | t the disk in the drive is |

| FDDCHG#  | I    | Disk change                                                  | Active Low                 |

|          |      | This signal from the drive indicates removed from the drive. | that the disk has been     |

| FDINDEX# | I    | Index                                                        | Active Low                 |

|          |      | This is the index detection signal from                      | the drive.                 |

| FDTRK0#  | I    | Track 0                                                      | Active Low                 |

|          |      | This signal is used to notify the sys detection track 0.     | tem that the head has      |

| FDHIDEN  | O OD | High density select                                          | Active High                |

|          |      | When high, this signal indicates high do                     | ensity.                    |

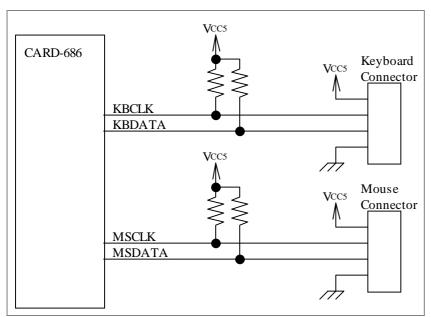

# 4.6 Keyboard Interface

| Pin Name | Type  | Functions                                         |

|----------|-------|---------------------------------------------------|

| KBCLK    | IO OD | Keyboard clock                                    |

|          |       | Clock signal for a PS/2-style keyboard interface. |

| KBDATA   | IO OD | Keyboard data                                     |

|          |       | Data signal for a PS/2-style keyboard interface.  |

# 4.7 Mouse Interface

| Pin Name | Type  | Functions                                      |

|----------|-------|------------------------------------------------|

| MSCLK    | IO OD | Mouse clock                                    |

|          |       | Clock signal for a PS/2-style mouse interface. |

| MSDATA   | IO OD | Mouse data                                     |

|          |       | Data signal for a PS/2-style mouse interface.  |

# 4.8 Parallel Interface

| Pin Name   | Type  | Functions                                                                                                              |            |

|------------|-------|------------------------------------------------------------------------------------------------------------------------|------------|

| LPTSTROBE# | IO OD | Line printer strobe                                                                                                    | Active Low |

|            |       | This signal is used as strobe for interface to read the data.  In the high-speed parallel port indicate a write cycle. |            |

| Pin Name   | Type  | Functions                                                                                                                                                                                                            |

|------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPTAFD#    | IO OD | Line printer auto feed Active Low                                                                                                                                                                                    |

|            |       | When this signal is active, a parallel printer inserts a line feed after every line.  This signal can be used as a data latch signal during write cycles and as a buffer enable signal during read cycle.            |

| LPTBUSY    | I     | Line printer busy Active High                                                                                                                                                                                        |

|            |       | This signal indicates that the printer is not able to accept data from the CARD-686.                                                                                                                                 |

| LPTACK#    | I     | Line printer acknowledge Active Low                                                                                                                                                                                  |

|            |       | This signal indicates that data transfer has been completed and also to prepare for the next transfer.                                                                                                               |

| LPTERROR#  | I     | Line printer error Active Low                                                                                                                                                                                        |

|            |       | This signal notifies the system of error in peripheral devices.                                                                                                                                                      |

| LPTPE      | I     | Line printer paper end Active High                                                                                                                                                                                   |

|            |       | This signal notifies the system that the printer is out of paper.                                                                                                                                                    |

| LPTINIT#   | IO OD | Line printer initialize Active Low                                                                                                                                                                                   |

|            |       | Initialization signal for the printer.                                                                                                                                                                               |

| LPTSLCTIN# | IO OD | Line printer select In Active Low                                                                                                                                                                                    |

|            |       | This signal selects the peripheral device connected to the parallel port.  It also serves as the address strobe in high-speed parallel port mode.                                                                    |

| LPTSLCT    | I     | Line printer selected Active High                                                                                                                                                                                    |

|            |       | Used to select the perip heral device currently connected to the port. In high-speed parallel port mode, this signal is used as an address strobe.                                                                   |

| LPTDIR     | 0     | Line printer direction                                                                                                                                                                                               |

|            |       | This signal controls the buffer direction of LPTD[7:0]. When being set to low, this signal indicates an output, and when set to high, it indicates an input. This signal outputs "low" at all times in the ISA mode. |

| LPTD[7:0]  | IO    | Line printer data bus                                                                                                                                                                                                |

|            |       | A data bus between the CARD-686 and a printer. This signal output only in the ISA mode and becomes a bit-directional signal in the PS/2 mode.                                                                        |

# 4.9 Serial Interface

| Pin Name             | Type | Functions                                                                                                                                            |

|----------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMADCD#<br>COMBDCD# | I    | Data carrier detect Active Low  This signal indicates that the modem or data terminal has detected the carrier.                                      |

| COMADTR#<br>COMBDTR# | О    | Data terminal ready Active Low  This signal indicates that the controller is ready for data transmission with respect to the modem or data terminal. |

| Pin Name | Type | Functions                                                                                                                                                                                         |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COMADSR# | I    | Data set ready Active Low                                                                                                                                                                         |

| COMBDSR# |      | This signal indicates that the modem or data terminal is ready for data transmission with respect to the controller.                                                                              |

| COMARTS# | О    | Request to send Active Low                                                                                                                                                                        |

| COMBRTS# |      | This signal indicates that controller has transmission data ready, and indicates a request to transmit data with respect to the modem or data terminal.                                           |

| COMACTS# | I    | Clear to send Active Low                                                                                                                                                                          |

| COMBCTS# |      | This input signal indicates that the modem or the data terminal has become ready to receive or the CARD-686's request to send.                                                                    |

| COMARI#  | I    | Ring indicator Active Low                                                                                                                                                                         |

| COMBRI#  |      | This signal indicates that the modem or data terminal has detected a telephone ringing signal. Alternatively, this signal can be used in the CARD-686 as a wake-up signal from the suspend state. |

| COMATXD  | О    | Serial data transmission                                                                                                                                                                          |

| COMBTXD  |      | This output is the asynchronous serial data.                                                                                                                                                      |

| COMARXD  | I    | Serial data receive                                                                                                                                                                               |

| COMBRXD  |      | This input is the asynchronous serial data.                                                                                                                                                       |

| IRTX     | 0    | Ir data Transmission                                                                                                                                                                              |

|          |      | Transmission data for infrared communications.                                                                                                                                                    |

| IRRX     | I    | IrDA-SIR format data receive                                                                                                                                                                      |

|          |      | An input terminal of IrDA-SIR format receive data                                                                                                                                                 |

| DARX     | I    | Digital ASK data receive                                                                                                                                                                          |

|          |      | An input terminal of Digital ASK format receive data.                                                                                                                                             |

# 4.10 Power Management

| Pin Name | Type | Functions                           |                                |

|----------|------|-------------------------------------|--------------------------------|

| BATLOW#  | I    | Battery low                         | Active Low                     |

|          |      | This input signal indicates the C.  | ARD-686 that the battery is    |

|          |      | dead. When this signal becomes      | active, a system management    |

|          |      | interrupt (SMI) is executed.        |                                |

| BATWRN#  | I    | Battery warning                     | Active Low                     |

|          |      | This signal is used to indicate a   | a battery capacity warning to  |

|          |      | the system.                         |                                |

| SUSSTAT# | О    | Suspend status                      | Active Low                     |

|          |      | This signal indicates that the syst | tem is in the suspended state. |

| SRBTN#   | I    | Suspend resume button               | Active Low                     |

|          |      | This signal is a suspend and        | resume request signal with     |

|          |      | respect to the system.              |                                |

| Pin Name   | Type | Functions                                                                                                                                             |

|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| EXTSMI#    | I    | External system management interrupt Active Low                                                                                                       |

|            |      | A system management interrupt is input from an external                                                                                               |

|            |      | device.                                                                                                                                               |

| SMOUT[3:0] | 0    | System management out                                                                                                                                 |

|            |      | These signals can be used for standby control of local devices (hard disk, serial driver/receiver) on the output terminals for local standby control. |

| POWERGOOD  | I    | Power good Active High                                                                                                                                |

|            |      | This signal indicates that the power supply is normal. When this signal become low, the CARD-686 is reset.                                            |

# 4.11 BIOS ROM Update Interfaces

| Pin Name | Type | Functions                              |

|----------|------|----------------------------------------|

| FLOAT#   |      | Signal to write Flash ROM (BIOS)       |

| PGM      |      | Power supply to write Flash ROM (BIOS) |

| ROMCE0#  |      | Signal to write Flash ROM (BIOS)       |

# 4.12 Speaker Interfaces

| Pin Name | Type | Functions                                      |            |

|----------|------|------------------------------------------------|------------|

| SPKOUT   | О    | Speaker Out                                    |            |

|          |      | This can be used as a digital output for speak | ker.       |

| WDTIM#   | О    | Watchdog Timer Out A                           | active Low |

|          |      | Watchdog Timer output.                         |            |

# 4.13 Power Supply

| Pin Name | Type | Functions                                             |

|----------|------|-------------------------------------------------------|

| Vcc3     |      | System Power                                          |

|          |      | 3.15 V to 3.6 V                                       |

|          |      | Power supply for internal circuits                    |

| VCC5     |      | System Power                                          |

|          |      | 5.0 V ± 5 %                                           |

|          |      | Power supply for external interfaces                  |

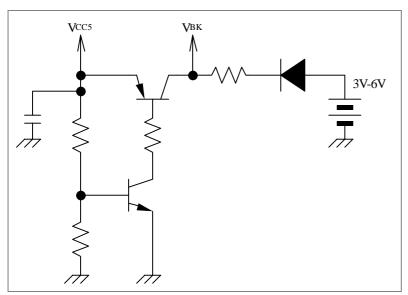

| VBK      |      | Backup power supply for real time clock               |

|          |      | When VCC5 is supplied, the same voltage as VCC5.      |

|          |      | When VCC5 is not supplied, a backup voltage should be |

|          |      | applied.                                              |

| GND      |      | System ground                                         |

|          |      |                                                       |

#### 5. DATAILED DESCRIPTION OF FUNCTIONS

# 5.1 System Overview

CARD-686 has a system configuration based on the ISA architecture. This section provides an overview of the system memory configuration and basic I/O.

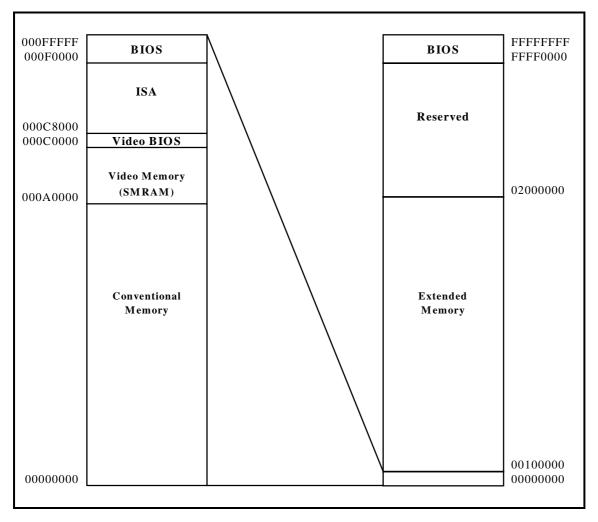

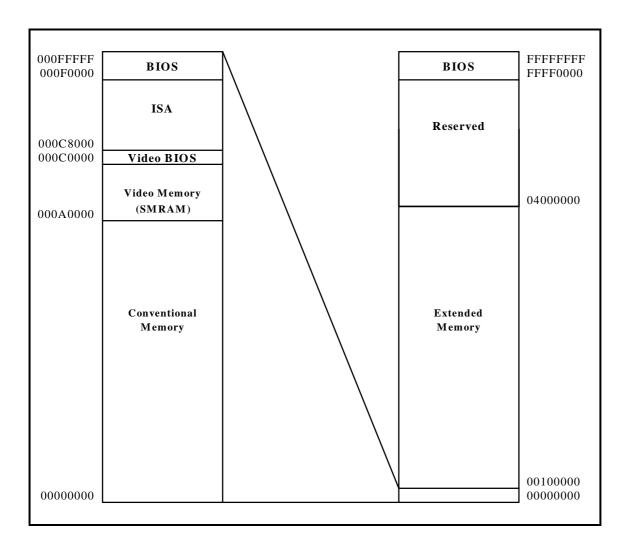

# 5.1.1 Memory map

The memory map of the CARD-686 (DRAM 32MB) becomes as shown in Figure 5-1. The CARD-686 retains the memory area of 4GB, and the lower 16MB is released for the ISA bus. When a memory is the CARD-686 is accessed even in this range, the address is not output to the ISA bus.

Figures 5-1 and 5-2 show the memory maps of DRAM 32MB and 64MB respectively. These memory maps are available when the standard BIOS of the CARD-686 is used. When the BIOS is changed, the memory maps

change.

Figure 5-1 Memory Map (DRAM 32MB

Figure 5-2 Memory Map (DRAM 64MB

#### 5.1.2 DMA controllers

The CARD-686 has two DMA controllers (equivalent to the 82C37A). The DMA channels in this system are shown in Table 5-1 and Table 5-2.

Table 5-1 DMA controllers 1

| Channel No. | Device allocated                  |

|-------------|-----------------------------------|

| СНО         | Device on the ISA bus are usable. |

| CH1         | Device on the ISA bus are usable. |

| CH2         | Floppy disk.                      |

| СН3         | Device on the ISA bus are usable. |

Table 5-2 DMA controllers 2

| Channel No. | Device allocated                   |

|-------------|------------------------------------|

| CH4         | Cascade connection to controller 1 |

| CH5         | Device on the ISA bus are usable.  |

| СН6         | Device on the ISA bus are usable.  |

| CH7         | Device on the ISA bus are usable.  |

Controller 1, which includes channels 0 to 3, is used for 8-bit data transfers. Between 8-bit I/O and 8-bit memory or 16-bit memory, transfer is possible in 8-bit units up to block of 64KB.

Controller 2, which includes channels 4 to 7, is used principally for 16-bit data transfers, and since channel 4 is connected in cascade to controller 1 it is not available to the ISA bus. Channels 5 to 7 are available to the ISA bus, and can be used for 16-bit data transfers. In this case, between 16-bit I/O and memory, transfer is possible in 16-bit units up to a block of 128KB.

The I/O addresses for the page registers used to support each DMA channel during DMA transfers are shown in T

able 5-3. The DMA controllers have only 16-bit addressing capability, are these page registers are used to make up for this.

**Table 5-3 Page Register Addresses**

| Page Register | I/O Address |

|---------------|-------------|

| DMA channel 0 | 0087h       |

| DMA channel 1 | 0083h       |

| DMA channel 2 | 0081h       |

| DMA channel 3 | 0082h       |

| DMA channel 5 | 008Bh       |

| DMA channel 6 | 0089h       |

| DMA channel 7 | 008Ah       |

| REFRESH       | 008Fh       |

Information relating to transfer timing is contained in the chapter on the ISA bus interface.

# 5.1.3 System interrupts and interrupt controller

CARD-686 interrupt types are shown below.

Table 5-4 Cause of interrupt on CARD-686

| Level | Function                                       |

|-------|------------------------------------------------|

| SMI   | External system management interrupt           |

|       | Power management functions, keyboard emulation |

| NMI   | Parity error or IOCHCK#                        |

| IRQ   | Interrupts from the Interrupt Controller       |

IRQ interrupts are caused by the two interrupt controllers (equivalent to 82C59) mounted on the CARD-686. Cause of interrupt on the interrupt controller are as follows:

**Table 5-5 Interrupt Controller Interrupt Assignments**

| Controller 1 | Controller 2 | Device                             |

|--------------|--------------|------------------------------------|

| IRQ0         |              | Timer Out 0                        |

| IRQ1         |              | Keyboard                           |

| IRQ2         |              | Cascade connection to controller 2 |

|              | IRQ8         | Real time clock                    |

|              | IRQ9         | Usable on ISA bus                  |

|              | IRQ10        | Serial port (Note)                 |

|              | IRQ11        | Serial port (Note)                 |

|              | IRQ12        | Mouse                              |

|              | IRQ13        | Co-Processor                       |

|              | IRQ14        | HDD                                |

|              | IRQ15        | Usable on ISA bus                  |

| IRQ3         |              | Serial port 2 (Note)               |

| IRQ4         |              | Serial port 1 (Note)               |

| IRQ5         |              | Parallel port 2 (Note)             |

| IRQ6         |              | FDD                                |

| IRQ7         |              | Parallel port 1 (Note)             |

#### Note:

The CARD-686 has two built-in serial ports and one built-in parallel port. Interrupt of these serial ports is selected from IRQ3,410,11 and the one of the parallel port is selected from IRQ5,7. Interrupt for which the built-in serial ports and parallel port are not used can be used on the ISA bus.

When the FDD or the HDD is not used, IRQ6,14 can be used on the ISA bus.

# 5.1.4 Timer counters

The CARD-686 incorporates two 8254 equivalent timer-counters. Each has three independent timers. The following describes the applications of each and the inputs.

**Table 5-6 Setting of Timer 1**

| Channel 0         | GATE 0    | Fixed at "On"                               |  |

|-------------------|-----------|---------------------------------------------|--|

| System Timer      | CLK IN 0  | 1.19 MHz                                    |  |

|                   | CLK OUT 0 | Connected to IRQ0 on Interrupt Controller 1 |  |

| Channel 1         | GATE 1    | Fixed at "On"                               |  |

| Refresh Request   | CLK IN 1  | 1.19MHz                                     |  |

|                   | CLK OUT 1 | Refresh request                             |  |

| Channel 2         | GATE 2    | Controlled by I/O Port 61h                  |  |

| Speaker Interface | CLK IN 2  | 1.19MHz                                     |  |

|                   | CLK OUT 2 | Used to drive the speaker interface         |  |

# Table 5-7 Setting of Timer 2

| Channel 0                    | GATE 0    | Fixed at "On"                            |  |

|------------------------------|-----------|------------------------------------------|--|

| SMI Request                  | CLK IN 0  | 32KHz                                    |  |

|                              | CLK OUT 0 | SMI request                              |  |

| Channel 1                    | GATE 1    | Fixed at "On"                            |  |

| General Purpose Timer Output | CLK IN 1  | 4KHz                                     |  |

| (Watchdog Timer)             | CLK OUT 1 | Watchdog timer output                    |  |

| Channel 2                    | GATE 2    | Controlled by the configuration register |  |

| Alarm for Power Management   | CLK IN 2  | 1.19MHz                                  |  |

| Alarm                        | CLK OUT 2 | Used to drive the speaker interface      |  |

For the detail of the timer counter, refer to the Seiko Epson's Technical Manual for Falconer Chip Set.

## 5.1.5 Real-time clock and CMOS RAM

The CARD-686 has a real time clock which provides clock and calendar functions and CMOS RAM used to hold system configuration information. The real time clock is compatible with a 146818.

Power must be supplied constantly to the V<sub>BK</sub> pin in order to maintain the operation of the real time clock and the contents of CMOS RAM. When switching between the system power supply and the backup power supply, care is required to ensure that data is not lost. Care must be paid to the power supply sequence for the CARD-686.

# 5.1.6 I/O MAP

The I/O addresses from 000h to 0FFh are assigned to the system board (basic I/O). Although the addresses from 100h to 3FFh are available for the I/O channels, because CARD-686 already has built in I/O, use the following table as a reference when expanding.

| I/O Address | Register Na | me                                     | Function               |

|-------------|-------------|----------------------------------------|------------------------|

| 000h-01Fh   | 00h RW      | DMA Channel 0 Base and Current Address |                        |

|             | 01h RW      | DMA Channel 0 Base and Current Word    | DMA Controller 1       |

|             | 02h RW      | DMA Channel 1 Base and Current Address | 82C37A equivalent.     |

|             | 03h RW      | DMA Channel 1 Base and Current Word    |                        |

|             | 04h RW      | DMA Channel 2 Base and Current Address |                        |

|             | 05h RW      | DMA Channel 2 Base and Current Word    |                        |

|             | 06h RW      | DMA Channel 3 Base and Current Address |                        |

|             | 07h RW      | DMA Channel 3 Base and Current Word    |                        |

|             | 08h WO      | Command Resister                       |                        |

|             | 08h RO      | Status Register                        |                        |

|             | 09h WO      | Request Register                       |                        |

|             | 0Ah WO      | Single-Mask Register                   |                        |

|             | 0Bh WO      | Mode Register                          |                        |

|             | 0Ch WO      | Clear Byte Pointer                     |                        |

|             | 0Dh RO      | Master Clear                           |                        |

|             | 0Dh WO      | Temporary Register                     |                        |

|             | 0Eh WO      | Clear Mask Register                    |                        |

|             | 0Fh WO      | Write all Mask Register                |                        |

| 020h-03Fh   | 20h WO      | Initialization Control Word ICW1       |                        |

|             | 20h WO      | Operation Control Word OCW2            | Interrupt controller 1 |

|             | 20h WO      | Operation Control Word OCW3            | 82C59A equivalent.     |

|             | 20h RO      | Interrupt Service Resister             |                        |

|             | 20h RO      | Interrupt Request Resister             |                        |

|             | 21h WO      | Initialization Control Word ICW2       |                        |

|             | 21h WO      | Initialization Control Word ICW3       |                        |

|             | 21h WO      | Initialization Control Word ICW4       |                        |

|             | 21h RW      | Operation Control Word OCW1            |                        |

|             | 21h RW      | Interrupt Mask Resister                |                        |

| 040h-04Fh   | 40h RW      | Channel 0 Count                        |                        |

|             | 41h RW      | Channel 1 Count                        | Timer Counter 1        |

|             | 42h RW      | Channel 2 Count                        | 8254 equivalent.       |

|             | 43h RW      | Command Register                       |                        |

| 048h-04Fh   | 48h RW      | Channel 0 Count                        |                        |

|             | 49h RW      | Channel 1 Count                        | Timer Counter 2        |

|             | 4Ah RW      | Channel 2 Count                        | 8254 equivalent.       |

|             | 4Bh RW      | Command Register                       |                        |

| 050h-057h   |             | Timer Counter 1 duplicated             |                        |

| 058h-05Fh   |             | Timer Counter 2 duplicated             |                        |

| I/O Address | Register Na | me                                     | Function               |

|-------------|-------------|----------------------------------------|------------------------|

| 060h-06Fh   | 60h R       | Keyboard controller Data Input Buffer  | Keyboard Controller    |

|             | 60h W       | Keyboard controller Data Output Buffer |                        |

|             | 61h RW      | Port B                                 |                        |

|             | 64h WO      | Keyboard controller Command Register   | Keyboard Controller    |

|             | 64h RO      | Keyboard Controller Status Register    |                        |

| 070h-07Fh   | 70h WO      | RTC/CMOS RAM Address Port and NMI      |                        |

|             |             | Mask                                   | RTC/CMOS RAM           |

|             | 71h RW      | RTC/CMOS RAM Data port                 |                        |

| 080h-09Fh   | 80h RW      | Reserved                               |                        |

|             | 81h RW      | Channel 2                              | DMA Memory Address     |

|             | 82h RW      | Channel 3                              | Mapper Page Register   |

|             | 83h RW      | Channel 1                              |                        |

|             | 84h RW      | Reserved                               |                        |

|             | 85h RW      | Reserved                               |                        |

|             | 86h RW      | Reserved                               |                        |

|             | 87h RW      | Channel 0                              |                        |

|             | 88h RW      | Reserved                               |                        |

|             | 89h RW      | Channel 6                              |                        |

|             | 8Ah RW      | Channel 7                              |                        |

|             | 8Bh RW      | Channel 5                              |                        |

|             | 8Ch RW      | Reserved                               |                        |

|             | 8Dh RW      | Reserved                               |                        |

|             | 8Eh RW      | Reserved                               |                        |

|             | 8Fh RW      | Refresh                                |                        |

| 0A0h-0BFh   | A0h WO      | Initialization Control Word ICW1       |                        |

|             | A0h WO      | Operation Control Word OCW2            | Interrupt Controller 2 |

|             | A0h WO      | Operation Control Word OCW3            | 82C59A equivalent.     |

|             | A0h RO      | Interrupt Service Resister             |                        |

|             | A0h RO      | Interrupt Request Resister             |                        |

|             | A1h WO      | Initialization Control Word ICW2       |                        |

|             | A1h WO      | Initialization Control Word ICW3       |                        |

|             | A1h WO      | Initialization Control Word ICW4       |                        |

|             | A1h RW      | Operation Control Word OCW1            |                        |

|             | A1h RW      | Interrupt Mask Resister                |                        |

| 0C0h-0DFh   | C0h RW      | DMA Channel 4 Base and Current Address |                        |

|             | C2h RW      | DMA Channel 4 Base and Current Word    | DMA Controller 2       |

|             | C4h RW      | DMA Channel 5 Base and Current Address | 82C37A equivalent.     |

|             | C6h RW      | DMA Channel 5 Base and Current Word    |                        |

|             | C8h RW      | DMA Channel 6 Base and Current Address |                        |

|             | CAh RW      | DMA Channel 6 Base and Current Word    |                        |

|             | CCh RW      | DMA Channel 7 Base and Current Address |                        |

|             | CEh RW      | DMA Channel 7 Base and Current Word    |                        |

|             | D0h W0      | Command Register                       |                        |

|             | D0h RO      | Status Register                        |                        |

|             | D2h WO      | Request Register                       |                        |

|             | D4h WO      | Mask Register                          |                        |

|             | D6h WO      | Mode Register                          |                        |

|             | D8h WO      | Clear Byte Pointer                     |                        |

| I/O Address          | Register Na   | nme                                                            | Function                     |

|----------------------|---------------|----------------------------------------------------------------|------------------------------|

|                      | DAh RO        | Master Clear                                                   |                              |

|                      | DAh WO        | Temporary Register                                             |                              |

|                      | DCh WO        | Clear Mask Register                                            |                              |

|                      | DEh WO        | Write all Mask Register                                        |                              |

| 0E0h-0EFh            | E5h RW        | CARD-686 Configuration Resister (Index)                        |                              |

|                      | E7h RW        | CARD-686 Configuration Resister (Data)                         |                              |

| 0F0h-0FFh            | F0h WO        | Mathematical Co-processor Resister                             |                              |

| 100h-1EFh            |               | 1                                                              | Can be used on the ISA bus.  |

| 1F0h-1F7h            | 1F0h RW       | Data Register                                                  |                              |

|                      | 1F1h RO       | Error Register                                                 | Hard Disk Controller         |

|                      | 1F2h RW       | Sector Count                                                   |                              |

|                      | 1F3h RW       | Sector Number                                                  |                              |

|                      | 1F4h RW       | Cylinder HIGH                                                  |                              |

|                      | 1F5h RW       | Cylinder LOW                                                   |                              |

|                      | 1F6h RW       | SDH Register                                                   |                              |

|                      | 1F7h RO       | Status Register                                                |                              |

|                      | 1F7h WO       | Command Register                                               |                              |

| 1F8h-277h            | 11 /11 11 0   | Command Register                                               | Can be used on the ISA bus.  |

| 278h-27Fh            | 278h RW       | LPT2 Data Port                                                 | can be used on the 1971 bus. |

| 27011-27111          | 279h RO       | LPT2 Status Port                                               | Parallel Port 2              |

|                      | 27Ah RW       | LPT2 Control                                                   | 1 aranci i ort 2             |

|                      | 27Ah RW       | Automatic Address Strobe Register                              |                              |

|                      | 27Ch RW       | Automatic Data Strobe Register                                 |                              |

|                      | 27Ch RW       | Automatic Data Strobe Register                                 |                              |

|                      | 27Eh RW       | Automatic Data Strobe Register  Automatic Data Strobe Register |                              |

|                      | 27En RW       |                                                                |                              |

| 280h-2F7h            | Z/FII KW      | Automatic Data Strobe Register                                 | Can be used on the ISA bus.  |

| 2F8h-2FFh            | 2F8h RO       | Receiver Buffer                                                |                              |

|                      | 2F8h WO       | Transmit Holding Buffer                                        | Serial Port 2                |

|                      | 2F8h RW       | Divider Latch Least Significant Byte                           |                              |

|                      | 2F9h RW       | Divider Latch Most Significant Byte                            |                              |

|                      | 2F9h RW       | Interrupt Enable Register                                      |                              |

|                      | 2Fah RO       | Interrupt Register                                             |                              |

|                      | 2FBh RW       | Line Controller Register                                       |                              |

|                      | 2FCh RW       | MODEM Control Register                                         |                              |

|                      | 2FDh RO       | Status Register                                                |                              |

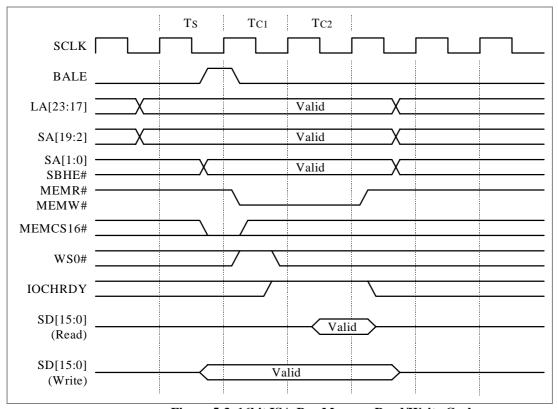

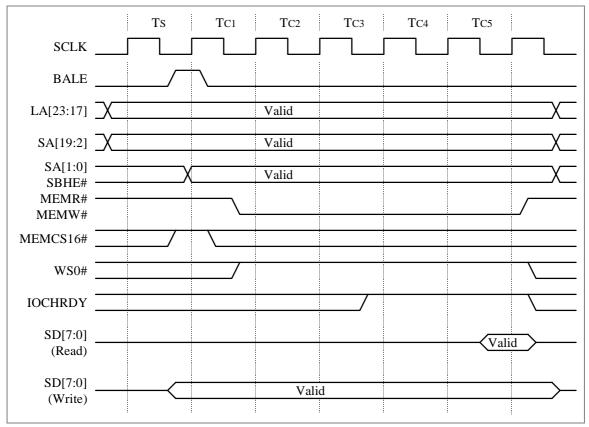

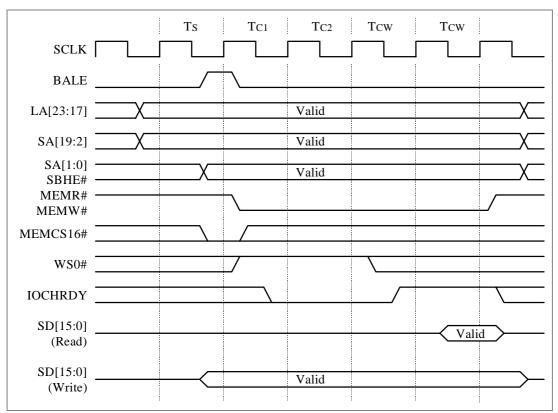

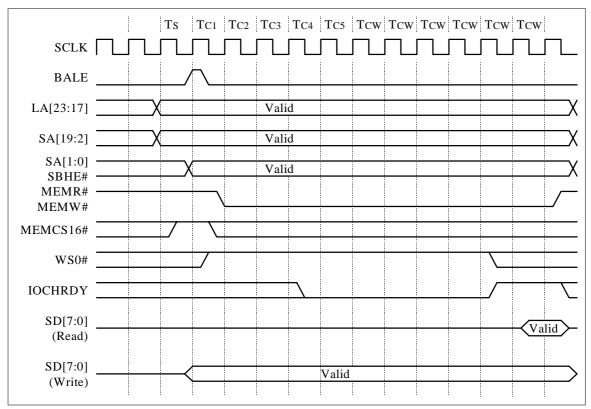

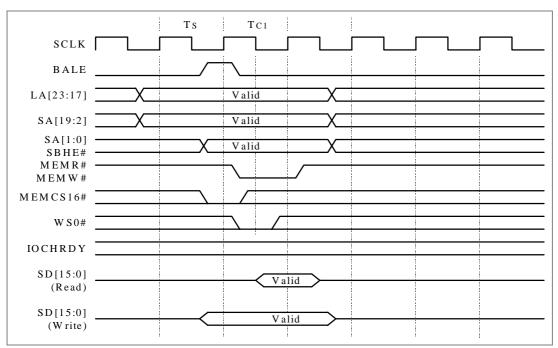

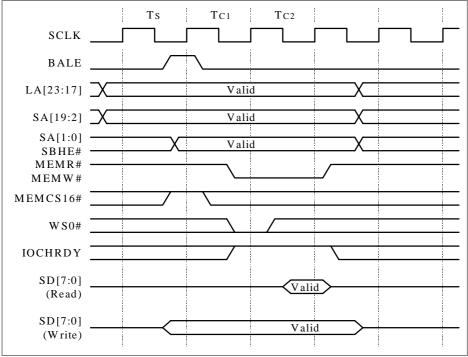

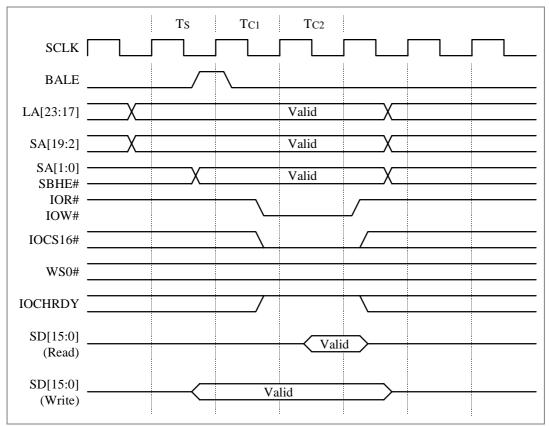

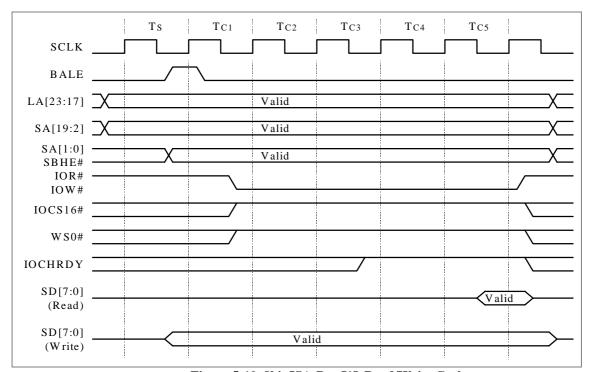

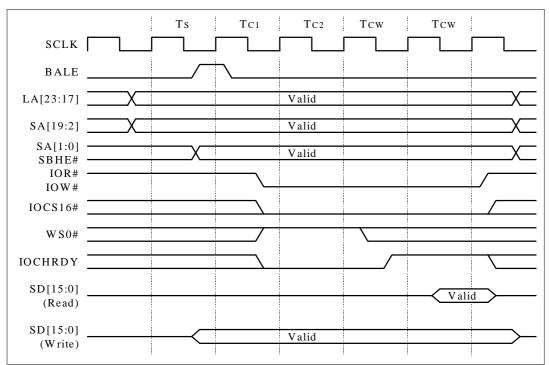

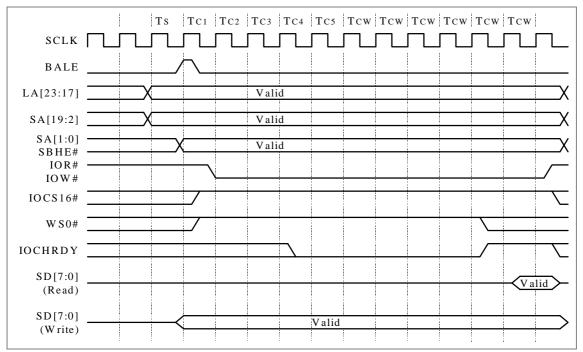

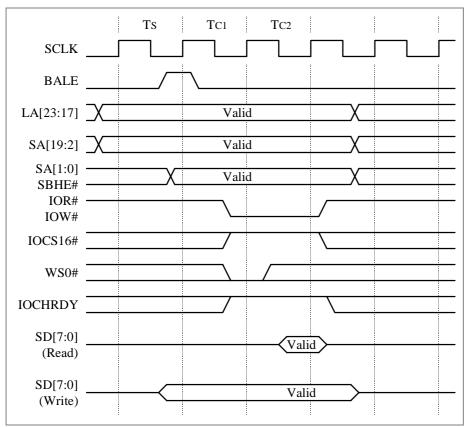

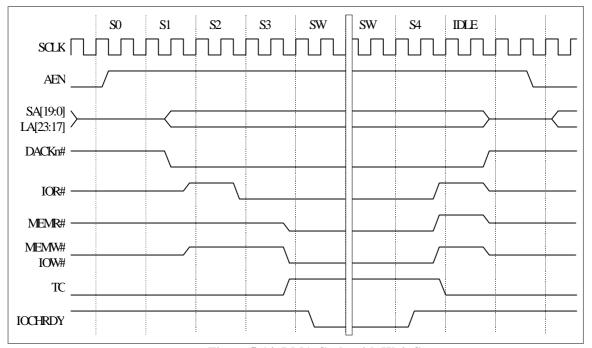

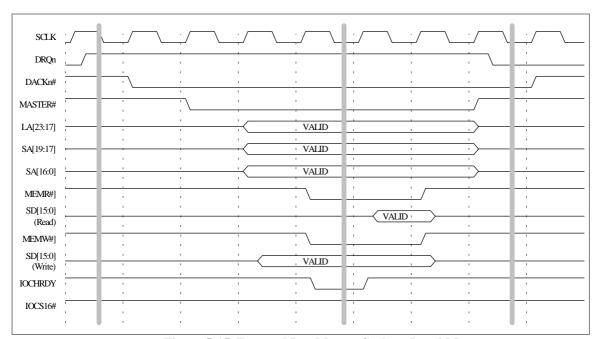

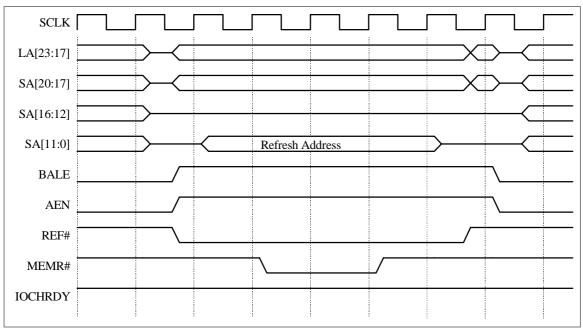

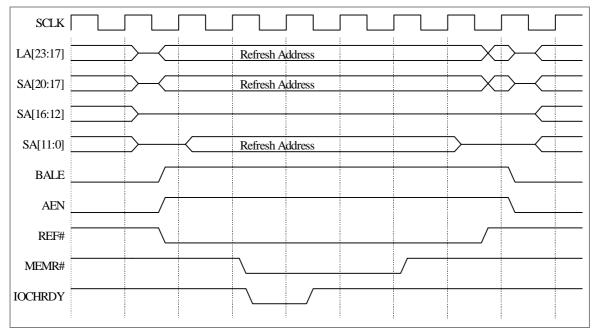

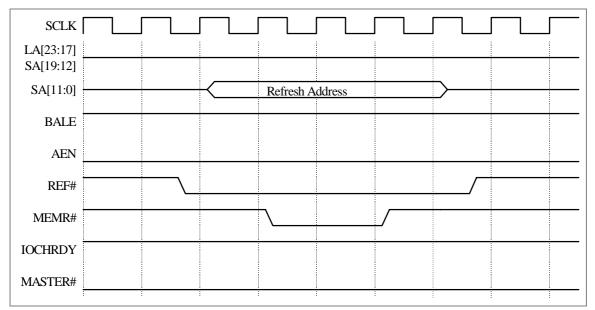

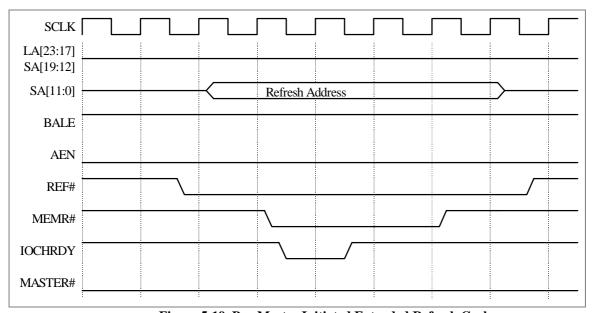

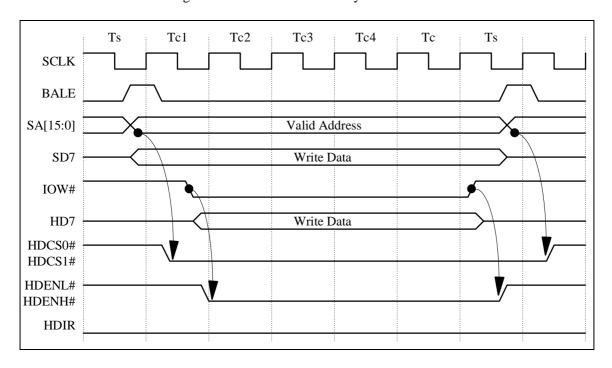

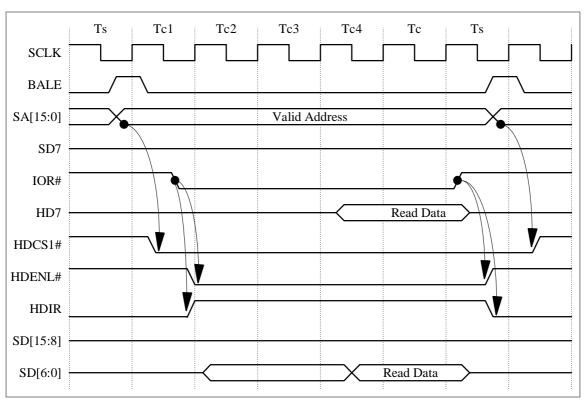

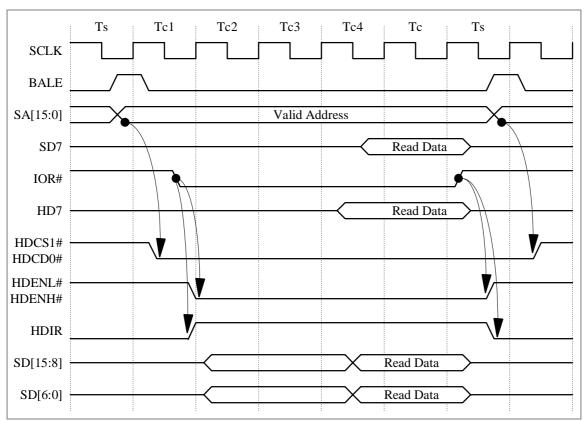

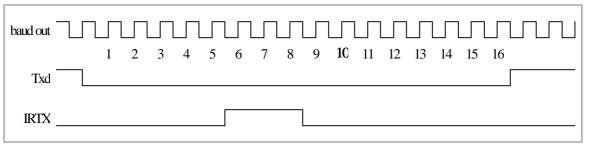

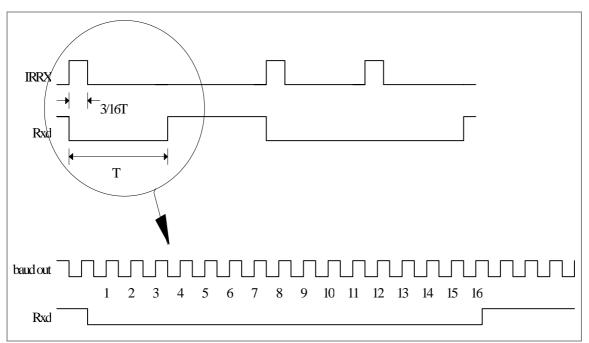

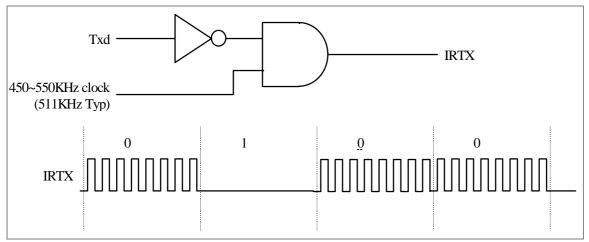

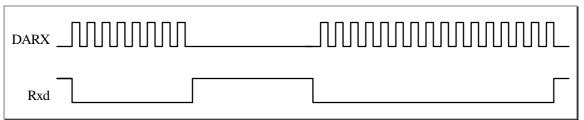

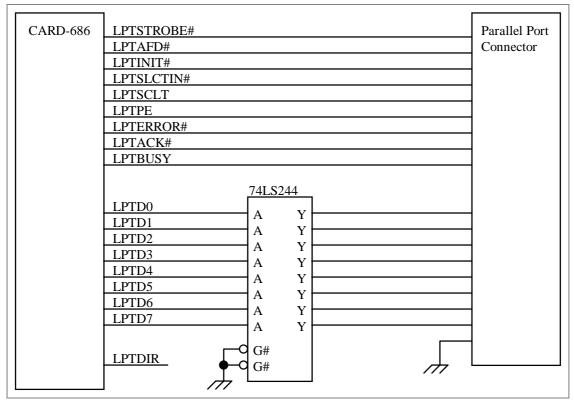

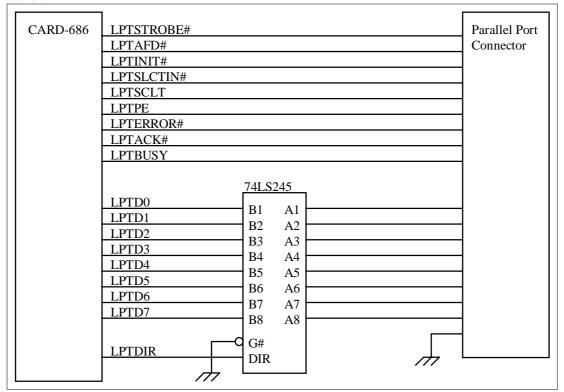

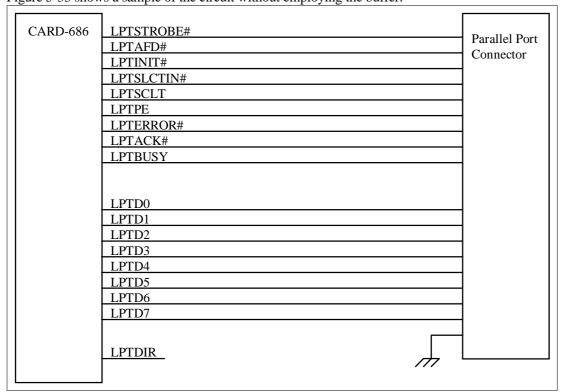

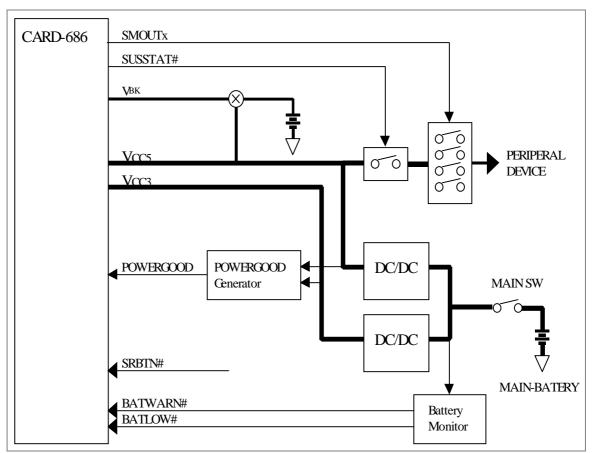

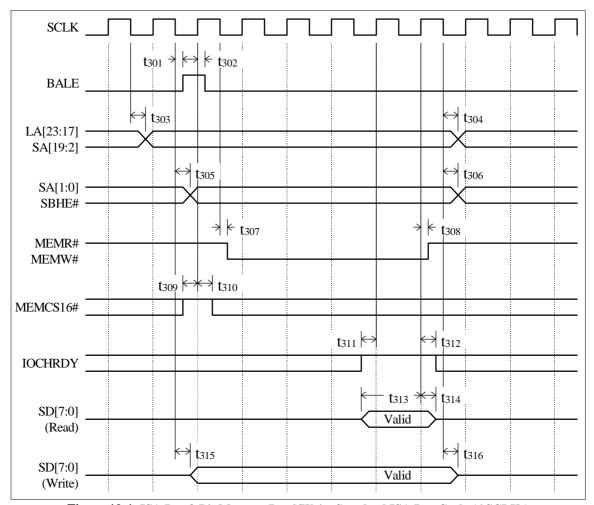

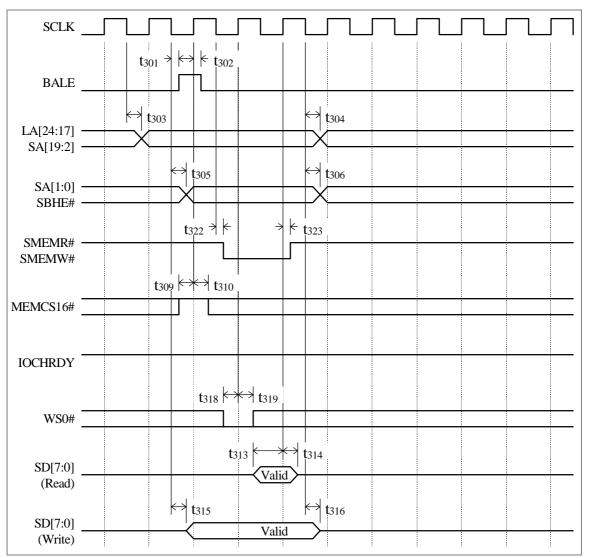

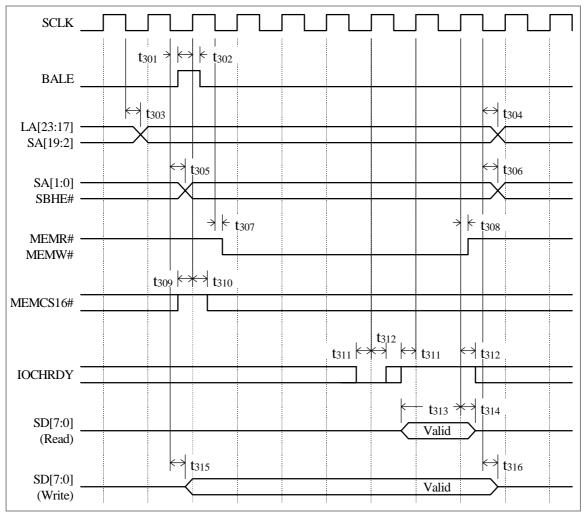

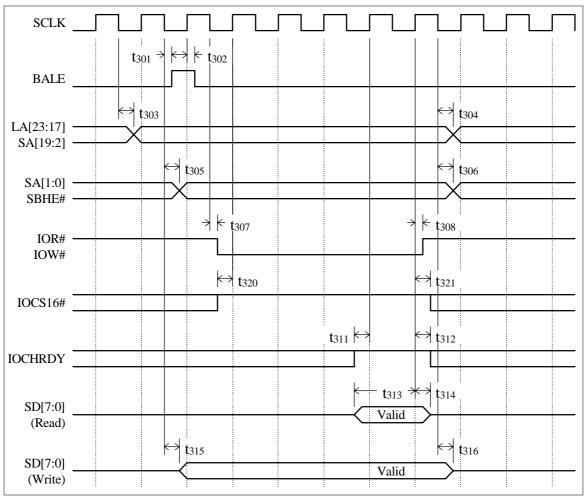

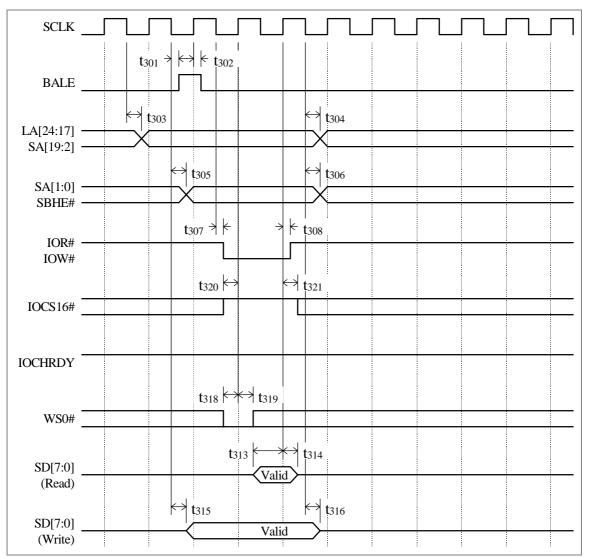

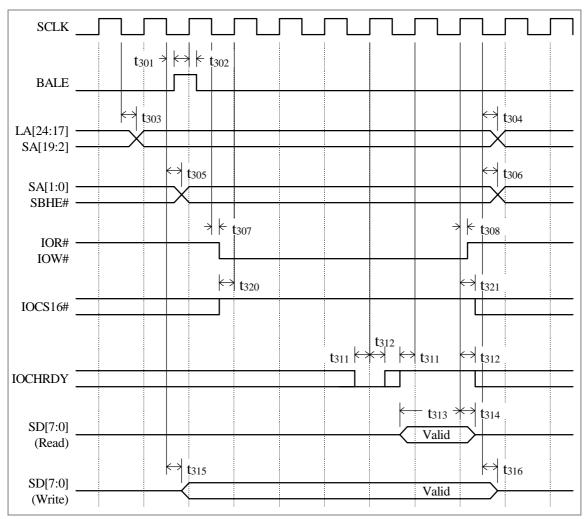

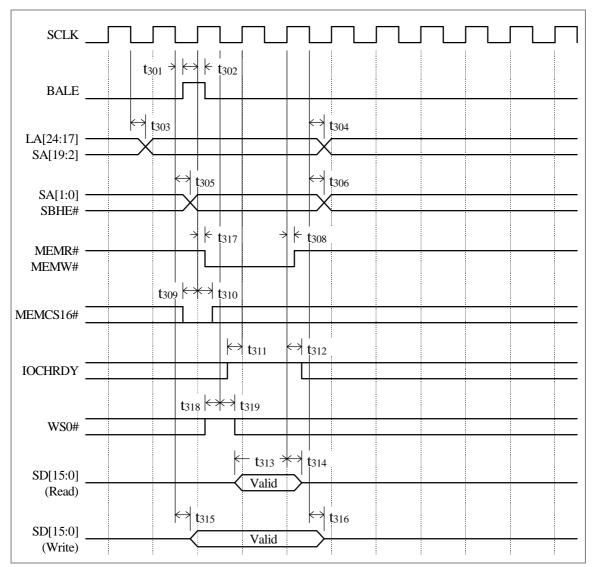

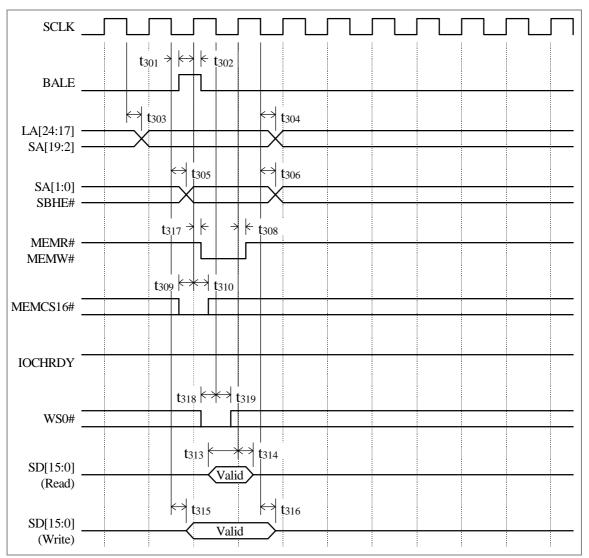

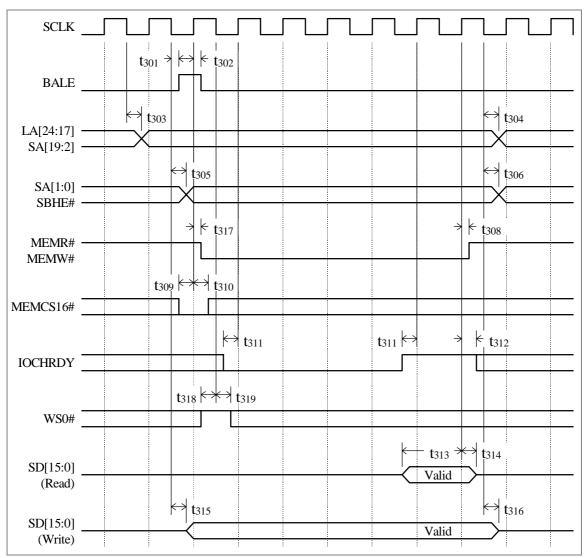

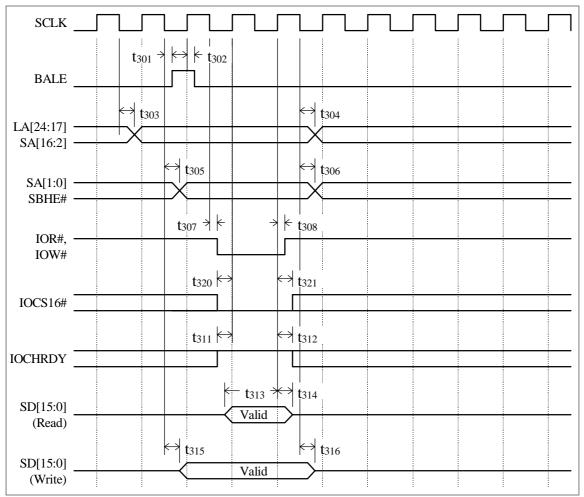

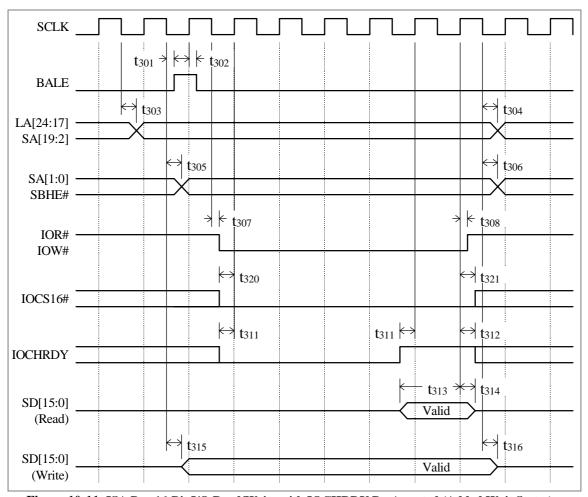

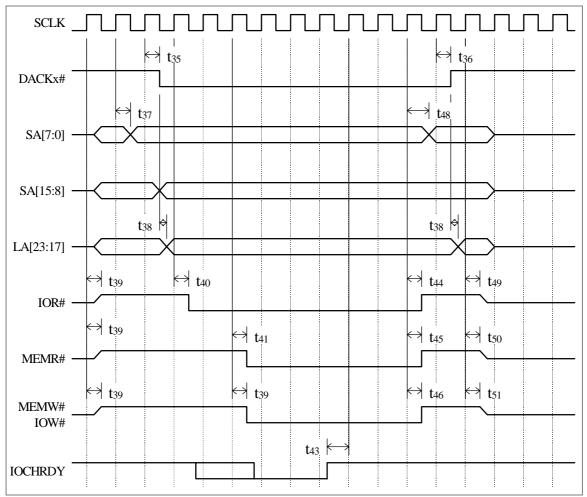

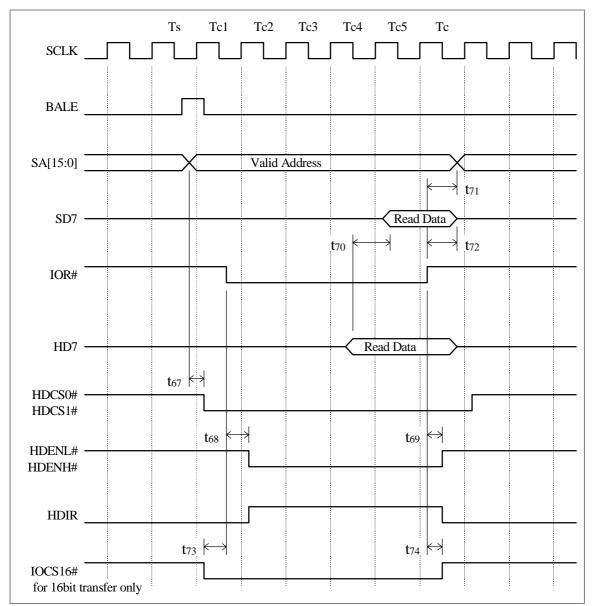

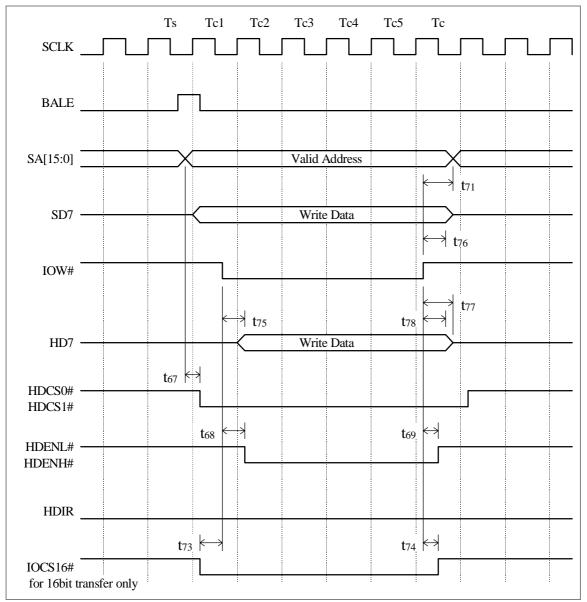

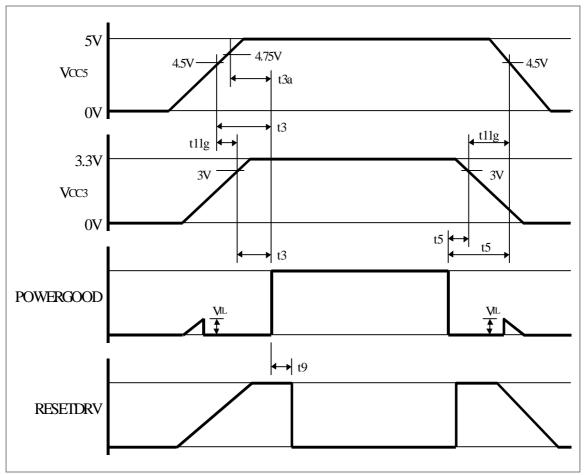

|                      | 2Feh RO       | MODEM Status Register                                          |                              |