**EPSON**

# CARD-PCI/GX

# **Hardware Manual**

SEIKO EPSON CORPORATION

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from anther government agency.

#### ©SEIKO EPSON CORPORATION 2000 All rights reserved.

CompactFlash is a trademark of Sandisk Corporation in U.S.A. CompactFlash is licensed to CFA (CompactFlash Association).

Windows and Windows NT are registered trademarks of Microsoft Corporation in U.S.A.

Geode is a trademark of National Semiconductor Corporation in U.S.A.

PC/AT is a registered trademark of International Business Machines in U.S.A.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

# CONTENTS

| 1. | 01          | erview .  |                                  | . 1 |

|----|-------------|-----------|----------------------------------|-----|

| 1  | 1.1         | System    | Overview                         | . 2 |

| 1  | .2          | Basic S   | pecification                     | . 3 |

| 1  | .3          | BIOS      |                                  | . 5 |

| 1  | .4          | Memory    | y map                            | . 6 |

| 1  | 1.5         | I/O map   | )                                | . 7 |

| 1  | .6          | DMA co    | ontroller                        | 13  |

| 1  | .7          | System    | interrupts                       | 14  |

| 1  | .8          | Timer c   | ounter                           | 15  |

| 1  | .9          | Real tin  | ne clock and C-MOS RAM           | 16  |

| 2. | Me          | echanica  | l specifications                 | 17  |

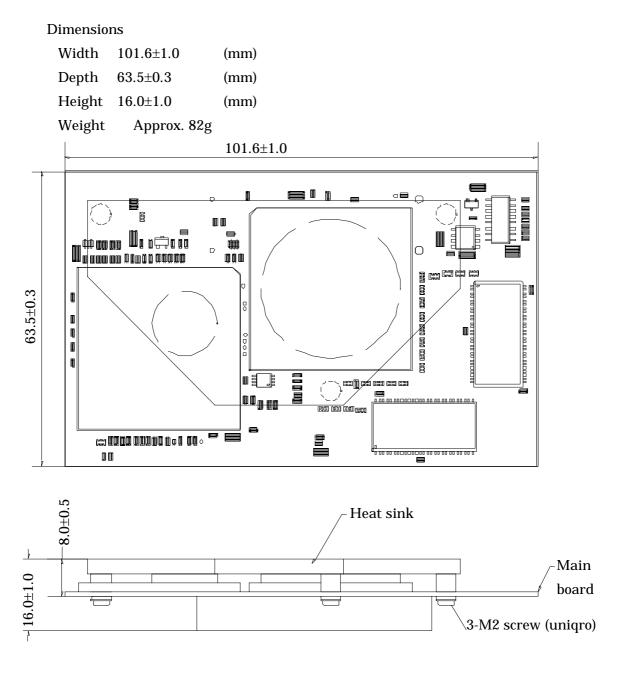

| 2  | 2.1         | Dimens    | ions and weight                  | 17  |

|    | 2.2         |           | tion method                      |     |

| 0  | T           |           |                                  |     |

| 3. | In          | terrace s | pecifications                    | 19  |

|    | 3.1         |           | figuration                       |     |

|    | 3.          |           | -pin connector pin configuration |     |

|    | 3.          | -         | pin connector pin configuration  |     |

|    | 3.2         |           | characteristics                  |     |

|    | 3.3         | •         | tions on signal functions        |     |

|    |             |           | I bus                            |     |

|    |             |           | MITED ISA bus                    |     |

|    |             |           | D                                |     |

|    |             |           | T                                |     |

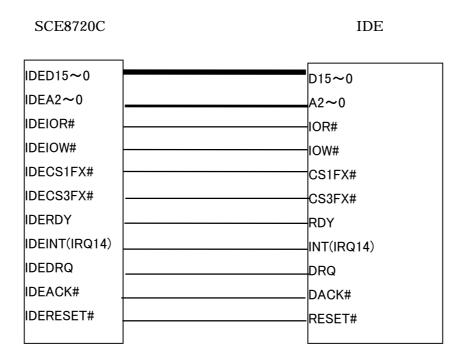

|    |             |           | rd disk (IDE)                    |     |

|    |             |           | ·B                               |     |

|    |             |           | rial interfaces                  |     |

|    |             |           | rallel interfaces                |     |

|    |             |           | yboard/mouse                     |     |

|    |             |           | 97 interfaces                    |     |

|    |             |           | wer management                   |     |

|    |             |           | wer supply                       |     |

|    | 3.          | 3.13 FD   | D                                | 57  |

| 4. | De          | etailed d | escription of interfaces         | 38  |

| Z  | <b>I</b> .1 | CRT, L    | .CD                              | 38  |

| 4  | 1.2         | Hard d    | lisk                             | 40  |

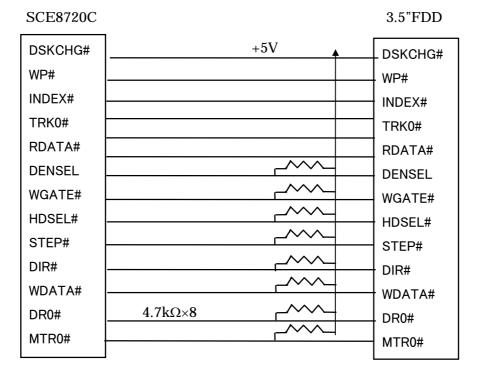

|    | 4.3        | FDD                                                                              | . 41 |

|----|------------|----------------------------------------------------------------------------------|------|

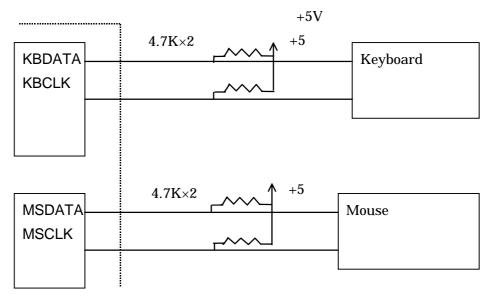

|    | 4.4        | Keyboard/mouse                                                                   | . 42 |

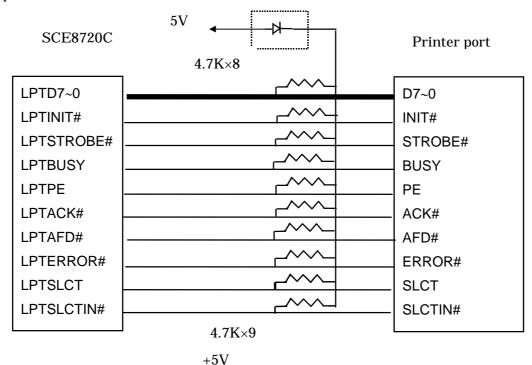

|    | 4.5        | Parallel port                                                                    | . 43 |

|    | 4.6        | Serial port                                                                      | . 44 |

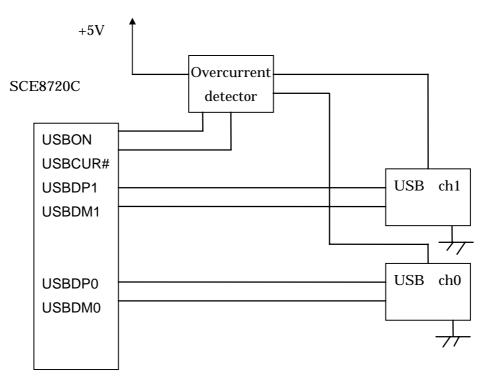

|    | 4.7        | USB                                                                              | . 44 |

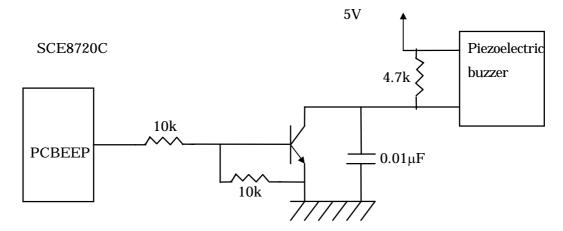

|    | 4.8        | Speaker                                                                          | . 45 |

|    | 4.9        | PCI                                                                              | 45   |

|    | 4.10       | LIMITED ISA                                                                      | . 46 |

|    | 4.11       | RTC                                                                              | . 46 |

| 5. | Pov        | ver management                                                                   | . 47 |

|    | 5.1        | Power ON/OFF                                                                     |      |

|    | 5.2        | Standby mode                                                                     |      |

|    | 5.2<br>5.3 | Power supply                                                                     |      |

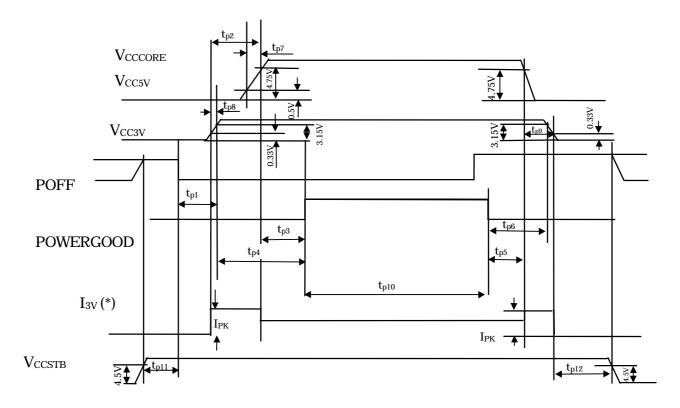

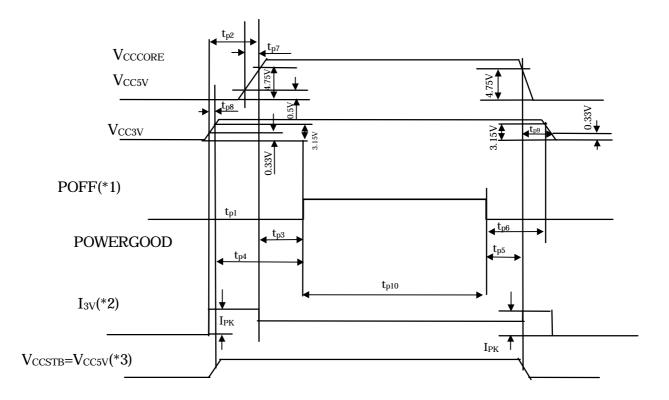

|    | 5.3<br>5.4 | Power sequence                                                                   |      |

|    | 5.4<br>5.4 | -                                                                                |      |

|    | 5.4<br>5.4 |                                                                                  |      |

|    | 5.4        | 2 Power sequence (for power supply which is not turned ON/OFF from the software) | . 51 |

| 6. | Ele        | ctrical characteristics                                                          | . 52 |

|    | 6.1        | Absolute maximum rating                                                          | . 52 |

|    | 6.2        | Recommended operating condition                                                  | . 52 |

|    | 6.3        | DC characteristics (under recommended operating condition)                       | . 53 |

|    | 6.3        | 1 PCI bus                                                                        | . 53 |

|    | 6.3        | 2 LIMITED ISA bus                                                                | . 53 |

|    | 6.3        | 3 LCD                                                                            | . 54 |

|    | 6.3        | 4 CRT                                                                            | . 54 |

|    | 6.3        | .5 FDD                                                                           | . 55 |

|    | 6.3        | .6 IDE                                                                           | . 55 |

|    | 6.3        | 7 Serial port                                                                    | . 56 |

|    | 6.3        | 8 Parallel port                                                                  | . 56 |

|    | 6.3        | 9 Keyboard/mouse                                                                 | . 57 |

|    | 6.3        | 10 USB                                                                           | . 57 |

|    | 6.3        | 11 Power management signal                                                       | . 57 |

|    | 6.3        | 12 AC97                                                                          | . 58 |

|    | 6.3        | 13 Other signals                                                                 | . 59 |

|    | 6.4        | Current consumption                                                              | . 60 |

|    | 6.4        | 1 Maximum current value                                                          | . 60 |

|    | 6.4        | 2 Typical current value 1                                                        | . 60 |

|    | 6.4        | .3 Typical current value 2                                                       | . 61 |

| 6.4.4      | Standby current                                 | 61 |

|------------|-------------------------------------------------|----|

| 7. AC cha  | aracteristics                                   | 62 |

| 7.1 PC     | CI timing                                       | 62 |

| 7.2 US     | SB timing                                       | 62 |

| 7.3 LI     | MITED ISA timing                                | 62 |

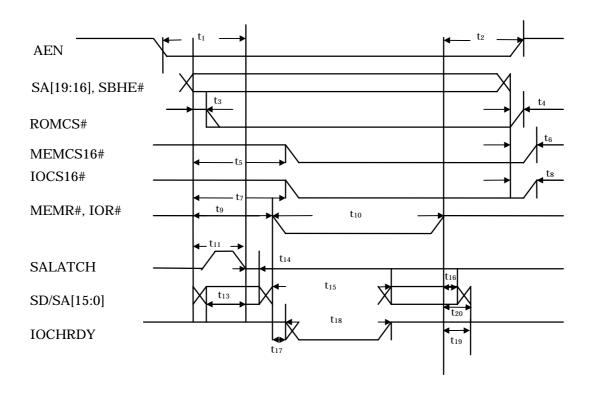

| 7.3.1      | Memory, I/O read cycle timing                   | 62 |

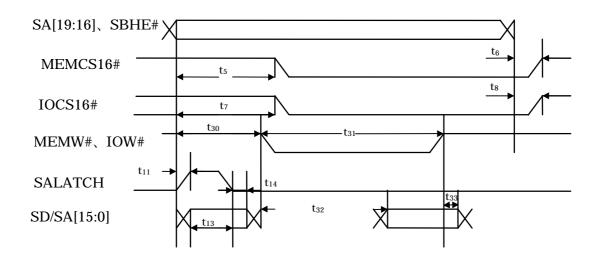

| 7.3.2      | Memory, I/O write cycle timing                  | 64 |

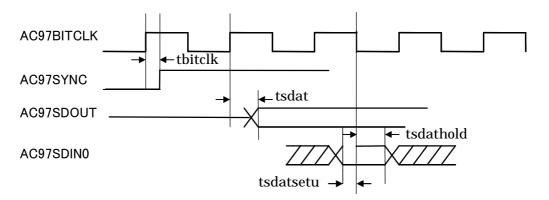

| 7.4 AC     | C97 timing                                      | 65 |

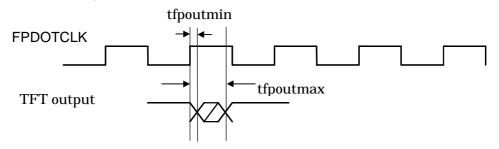

| 7.5 TF     | T timing                                        | 65 |

| 8. Cautio  | ns on use                                       | 66 |

| Appendix . | A. Peripheral circuit design                    | 67 |

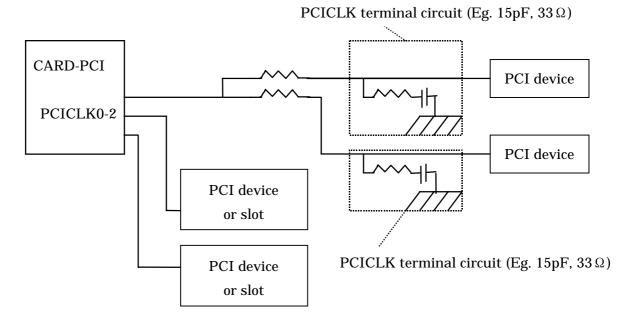

| ••         | extension of PCI bus                            |    |

| A.1.1      | Number of PCI devices                           |    |

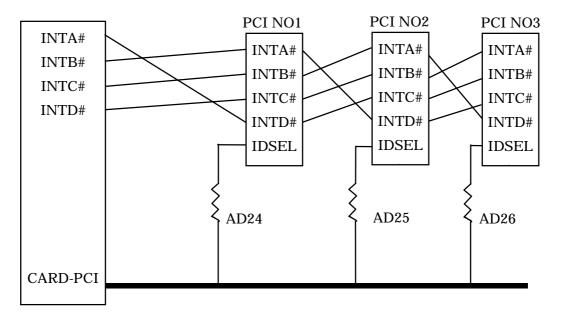

| A.1.2      | PCI device No. and wiring method for interrupts |    |

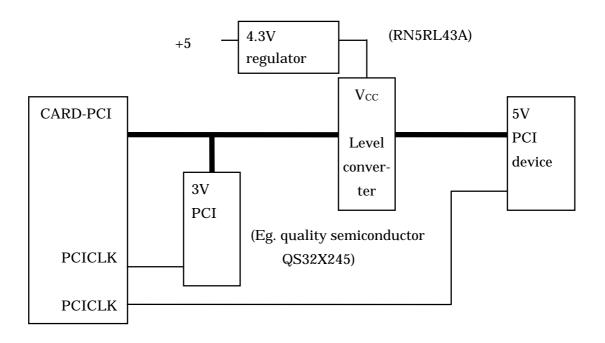

| A.1.3      | Connection of 5V device to PCI bus              |    |

| A.2 IO     | extension of LIMITED ISA bus                    | 70 |

| A.2.1      | Address decoding                                | 70 |

| A.2.2      | Pull-up of SD/SA[7:0]                           | 70 |

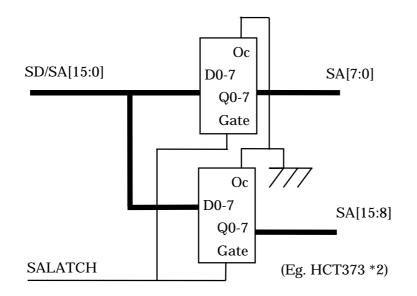

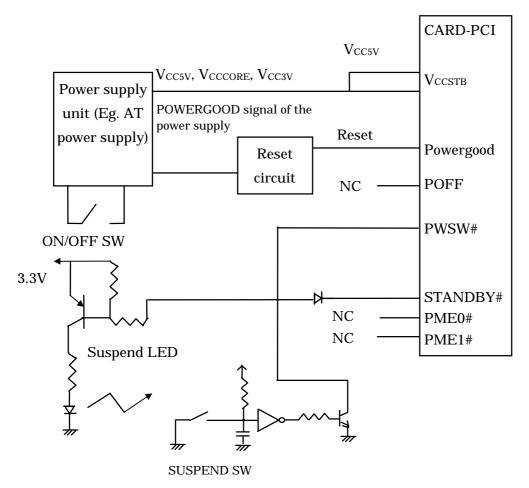

| A.2.3      | SA[15:0] latch                                  | 71 |

| A.2.4      | Number of ISA slots                             | 71 |

| A.2.5      | Pull-up resistance of IOCHRDY                   | 71 |

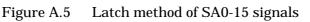

| A.2.6      | SMEMR# and SMEMW# generation                    | 72 |

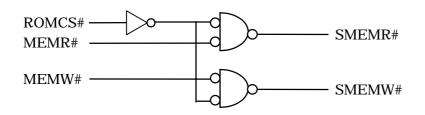

| A.2.7      | MEMCS16# generation                             | 72 |

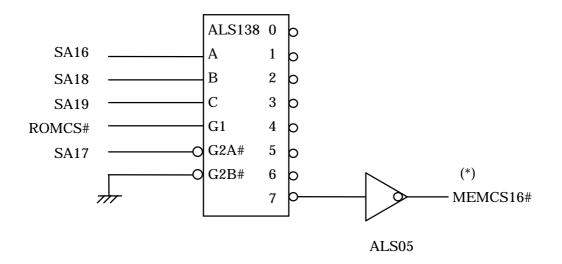

| A.3 Po     | wer supply design: Power control circuit        | 73 |

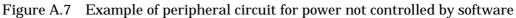

| A.3.1      | Power not requiring ON/OFF by software          | 73 |

| A.3.2      | Power requiring ON/OFF by software              | 74 |

| A.3.3      | Cautions on compatibility of CARD-PCI           | 75 |

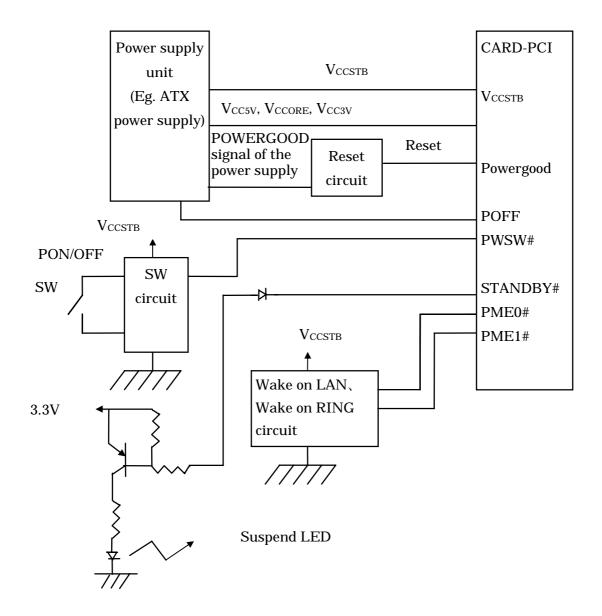

| A.3.4      | Wake on LAN signal                              | 75 |

| A.4 Ca     | nutions on artwork design                       | 76 |

| A.4.1      | Power supply line                               | 76 |

| A.4.2      | Address bus and data bus                        | 77 |

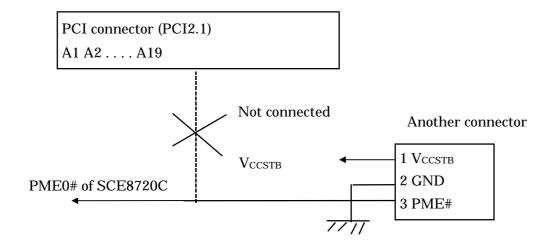

| A.4.3      | PCI signal                                      |    |

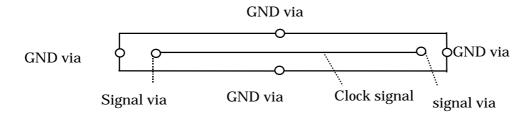

| A.4.4      | Clock signal                                    | 77 |

| A.4.5      | CRT RGB signal                                  |    |

| A.4.6      | Reset signal                                    | 78 |

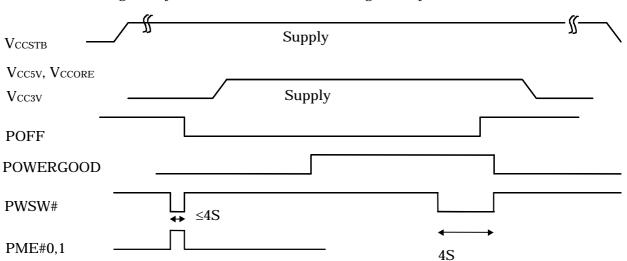

| Appendix 1 | B. Timing examples of power management signals  | 79 |

#### 1. Overview

SCE8720Cxx (CARD/PCI/GX) is the first product in SEIKO EPSON's CARD-PCI series equipped with the PCI bus. With the PCI bus, ability of enhancement, which enables various PCI devices to be connected, is realized.

By utilizing the Geode 200 MHz low voltage product, which comprises CPU core, and the companion chip manufactured by National Semiconductor, low power consumption, low cost and high quality display (CRT1280  $\times$  1024, 256-color) are all realized. Especially, this low power consumption capability is one of the most important aspects to realize fan-less, which is required in applications requiring high liability.

All these capabilities are provided within a compact size of  $101.6 \pm 1.0 \times 63.5 \pm 0.3 \times 16.0 \pm 1.0$  (mm) with 280-pin and 20-pin interface connectors.

Because SCE8720C can easily enable the core capabilities of IBM PC/AT, including BIOS, users can drastically decrease system development manpower and period.

In addition, future CARD-PCI series will also be able to be used with the same main board only requiring consideration on the card's mounting area and power supply.

#### 1.1 System Overview

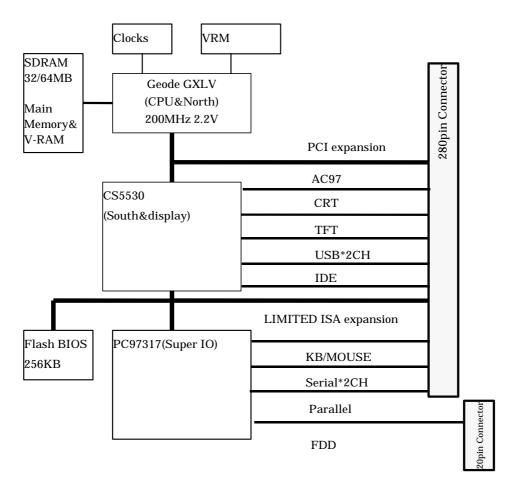

SCE8720Cxx (CARD-PCI/GX) is provided with almost all the functions usually equipped on a mother board. These functions are accessed via the 280-pin main connector and 20pin connector.

As for 280-pin connector, manufacturer's genuine part is utilized. Functions accessed via the 280-pin connector are PCI extended bus, CRT or TFT LCD panel display, 2-channel USB, primary IDE, LIMITED ISA extended bus (\*1), keyboard and mouse, 2-channel serial/parallel port and AC97 interface. FDD and a part of interrupt of ISA are accessed via the 20-pin connector.

SCE8720Cxx has Geode GX-LV 200MHz (CPU CHIP), Geode CS5530 (Companion chip), 97317 (Super IO) all built-in. As the main memory, SCE8720Cxx has a 32MB or 64MB of synchronous D-RAM and has utilized the unified memory method, in which a part of the synchronous D-RAM is used as the display memory. Generally, it is said that the unified memory method results in low-performance. However, with SCE8720Cxx, high performance is realized by compressing the data for display refreshing. In addition, SCE8720Cxx has a built-in CPU core power regulator (VRM) and a built-in CLOCK generator with built-in PLL. (\*1: LIMITED ISA = ISA with limited capability)

Figure1.1 Block diagram of SCE8720Cxx

## 1.2 Basic Specification

| Item         |             | Specific                                         | ations                                           |               |                     |         |           |

|--------------|-------------|--------------------------------------------------|--------------------------------------------------|---------------|---------------------|---------|-----------|

| CPU          |             | Geode                                            | GXLV                                             | 200MHz        | (Manufactured       | by      | National  |

|              |             |                                                  | Semiconductor)                                   |               |                     |         |           |

|              |             | (Cache memory 16KB built-in, FPU built-in)       |                                                  |               |                     |         |           |

| Main me      | mory        | Synchro                                          | onous DRA                                        | M 32MB/64N    | MB                  |         |           |

| System R     | ROM         | 256KB                                            |                                                  |               |                     |         |           |

|              |             | (System                                          | (System BIOS + VGA BIOS + Power management BIOS) |               |                     |         |           |

| Compani      | on chip     | Geode C                                          | CS5530 (Ma                                       | nufactured    | by National Semi    | icondu  | ictor)    |

|              |             | (Graphi                                          | c control, I                                     | DE AC97       | etc.)               |         |           |

| Graphic f    | function    | RAM                                              | Maximum                                          | 4MB (using    | g a part of synchro | onous   | DRAM)     |

|              |             | CRT 6                                            | 0Hz (Max.                                        | XGA: 64K-c    | olor or SXGA: 250   | 6-color | .)        |

|              |             | TFT 1                                            | 8/12/9-bit 7                                     | TFT panel su  | ipport (Max. XGA    | 64K-    | color)    |

|              |             | STN car                                          | nnot be use                                      | ed.           |                     |         |           |

|              |             |                                                  |                                                  |               |                     |         |           |

| I/O interfa  | ace         |                                                  |                                                  |               |                     |         |           |

|              | PCI         | 3.3V P                                           | PCI Version                                      | 2.1 Complia   | ance (33MHz)        |         |           |

|              |             | PCI dev                                          | vice 3 P                                         | CI master 2   |                     |         |           |

|              | LIMITED ISA | No DMA                                           | A or Master                                      | r function pr | ovided. As for AB   | 80-15,  | multiplex |

|              |             | output t                                         | to DB.                                           |               |                     |         |           |

|              |             | Some si                                          | gnals have                                       | been delete   | d as well.          |         |           |

|              | Parallel    | 1-port S                                         | SPP, ECP, I                                      | EPP (rev1.9/  | 1.7) supported.     |         |           |

|              | Serial      | <b>2-port</b> (2                                 | 16550 comp                                       | oatible) Ma   | ax.1.5Mbaud         |         |           |

|              | HDD(IDE)    | 1 device                                         | e (ANSI AT                                       | A_4 Complia   | ant)                |         |           |

|              | FDD         |                                                  |                                                  | AB 2mode, 3   | 5.5")               |         |           |

|              | Keyboard    | 1PS/2-co                                         | ompatible                                        |               |                     |         |           |

|              | Mouse       |                                                  | ompatible                                        |               |                     |         |           |

|              | USB         | -                                                |                                                  | on 1.0 comp   | liant               |         |           |

|              | Speaker     | PC beep                                          |                                                  |               |                     |         |           |

|              | AC97        | Version                                          |                                                  |               |                     |         |           |

| Super I/O    |             | PC97317 (Manufactured by National Semiconductor) |                                                  |               |                     |         |           |

| RTC          |             | MC146818A-compatible, built in Super I/O.        |                                                  |               |                     |         |           |

| Clock buffer |             | MK1491-06 (Manufactured by ICS)                  |                                                  |               |                     |         |           |

|              | limensions  | 101.6±1.0×63.5±0.3×16.0±1.0 (mm)                 |                                                  |               |                     |         |           |

| Weight       |             | Approx.                                          | 82g                                              |               |                     |         |           |

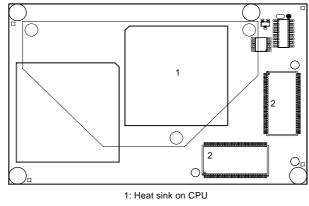

Operation environment (temperature ranges)

Maximum temperature [Tc =  $75^{\circ}$ C right above the heat sink, and Ta =  $70^{\circ}$ C around the SDRAM]

Minimum temperature  $Ta = 0^{\circ}C$

2: Ta around DRAM (peripheral temperature)

| Storage environment | Temperature | -20 to $75^{\circ}$ C (no condensation) |

|---------------------|-------------|-----------------------------------------|

|                     | Humidity    | 0 to 90% (no condensation)              |

| Current consumption | Maximum rat | ing 7.1W                                |

Power supply specifications (the following power supply is required.)

The following operational values are measured when Windows 98 is running and desktop is displayed.

| CPU_VRM power supply (V <sub>CCCORE</sub> ) 5      | 5V                                       |      |

|----------------------------------------------------|------------------------------------------|------|

| Current consumption Ty                             | rp. 408mA                                |      |

| Standby current Ty                                 | rp. 17.2 mA                              |      |

| System power (V <sub>CC3V</sub> ) 3.3V             |                                          |      |

| Current consumption Ty                             | p. 620 mA                                |      |

| Standby current Ty                                 | rp. 230 mA                               |      |

| ISA bus power supply ( $V_{CC5V}$ ) 5V             |                                          |      |

| Current consumption Ty                             | rp. 17.1 mA                              |      |

| Standby current Ty                                 | rp. 11.5 mA                              |      |

| 5V standby power (V <sub>CCSTB</sub> ) $5V$        |                                          |      |

| (Power of 5V is always su                          | pplied regardless of the ON/OFF of the p | ower |

| supply.)                                           |                                          |      |

| Current consumption Ty                             | тр. 0.35 mA                              |      |

| Backup power (V <sub>CCBAK</sub> ) 2.7 to 3.6V (vo | oltage supplied by battery)              |      |

| Current consumption Ty                             | rp. 1.2 μA                               |      |

| (When holding the C-MOS                            | 5 memory contents by the battery)        |      |

|                                                    |                                          |      |

•Power management

Power ON (PME0#, 1#, power SW) Power OFF (Soft OFF) Standby mode

#### 1.3 BIOS

SCE8720C has adopted AWARD BIOS manufactured by Phoenix. It has the power management and plug-and-play functions. With the BIOS setup menu, many configuration parameters can be set.

The Video BIOS is also stored in the same ROM.

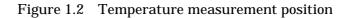

#### 1.4 Memory map

\*1: Memory size can be 32MB or 64MB, depending on the model.

\*2: With some types of Video, C0000h to CBFFFh can be occupied as VIDEO BIOS.  $\alpha$  : Area for the video memory: Max. 4MB

#### 1.5 I/O map

The I/O addresses 000h to 0FFh are assigned to the basic I/O. Although the addresses from 100h to 3FFh are for the ISA bus, SCE8720C has pre-built-in I/O.

| Table 1.1 I/O | map      |                                           |                        |

|---------------|----------|-------------------------------------------|------------------------|

| I/O Address   | Register |                                           | Function               |

| 000h-01Fh     | 00h RW   | DMA Channel 0 Base and Current<br>Address |                        |

|               | 01h RW   | DMA Channel 0 Base and Current Word       | DMA Controller 1       |

|               | 02h RW   | DMA Channel 1 Base and Current<br>Address | (82C37A<br>equivalent) |

|               | 03h RW   | DMA Channel 1 Base and Current Word       |                        |

|               | 04h RW   | DMA Channel 2 Base and Current<br>Address |                        |

|               | 05h RW   | DMA Channel 2 Base and Current Word       |                        |

|               | 06h RW   | DMA Channel 3 Base and Current<br>Address |                        |

|               | 07h RW   | DMA Channel 3 Base and Current Word       |                        |

|               | 08h WO   | Command Resister                          |                        |

|               | 08h RO   | Status Register                           |                        |

|               | 09h WO   | Request Register                          |                        |

|               | 0Ah WO   | Single-Mask Register                      |                        |

|               | 0Bh WO   | Mode Register                             |                        |

|               | 0Ch WO   | Clear Byte Pointer                        |                        |

|               | 0Dh RO   | Master Clear                              | _                      |

|               | 0Dh WO   | Temporary Register                        |                        |

|               | 0Eh WO   | Clear Mask Register                       | _                      |

|               | 0Fh WO   | Write all Mask Register                   |                        |

| 020h-021h     | 20h WO   | Initialization Control Word ICW1          | Interrupt              |

|               | 20h WO   | Operation Control Word OCW2               | Controller 1           |

|               | 20h WO   | Operation Control Word OCW3               | (82C59A                |

|               | 20h RO   | Interrupt Service Resister                | equivalent)            |

|               | 20h RO   | Interrupt Request Resister                | -                      |

|               | 21h WO   | Initialization Control Word ICW2          | -                      |

|               | 21h WO   | Initialization Control Word ICW3          | 4                      |

|               | 21h WO   | Initialization Control Word ICW4          | -                      |

|               | 21h RW   | Operation Control Word OCW1               | 4                      |

|               | 21h RW   | Interrupt Mask Resister                   |                        |

| I/O Address | Register |                                        | Function          |

|-------------|----------|----------------------------------------|-------------------|

| 022h-2Dh    | 22h WO   | Configuration Index Register           | Geode GX-LV       |

| -           | 23h RW   | Configuration Data Register            |                   |

| O2Eh-03Fh   | 2Eh RW   | Plug&Play Index Register               | Plug&Play         |

|             | 2Fh RW   | Plug&Play Data Register                |                   |

| 040h-04Fh   | 40h RW   | Channel 0 Count                        |                   |

|             | 41h RW   | Channel 1 Count                        | Timer Counter 1   |

|             | 42h RW   | Channel 2 Count                        | (8254 equivalent) |

|             | 43h RW   | Command Register                       |                   |

| 060h-06Fh   | 60h R    | Keyboard controller Data Input Buffer  | Keyboard          |

|             | 60h W    | Keyboard controller Data Output Buffer | Controller        |

|             | 61h RW   | Port B                                 |                   |

|             | 62h RW   | Keyboard controller mailbox Register   | Keyboard          |

|             | 64h WO   | Keyboard controller Command Register   | Controller        |

|             | 64h RO   | Keyboard Controller Status Register    |                   |

| 070h-07Fh   | 70h WO   | RTC/CMOS RAM Address Port and NMI      | RTC/CMOS RAM      |

|             |          | Mask                                   |                   |

|             | 71h RW   | RTC/CMOS RAM Data port                 |                   |

| 080h-09Fh   | 80h RW   | Reserved                               | DMA Memory        |

|             | 81h RW   | Channel 2                              | Address           |

|             | 82h RW   | Channel 3                              | Mapper Page       |

|             | 83h RW   | Channel 1                              | Register          |

|             | 84h RW   | Reserved                               | _                 |

|             | 85h RW   | Reserved                               | _                 |

|             | 86h RW   | Reserved                               | _                 |

|             | 87h RW   | Channel 0                              | _                 |

|             | 88h RW   | Reserved                               | _                 |

|             | 89h RW   | Channel 6                              | _                 |

|             | 8Ah RW   | Channel 7                              | _                 |

|             | 8Bh RW   | Channel 5                              | _                 |

|             | 8Ch RW   | Reserved                               |                   |

|             | 8Dh RW   | Reserved                               |                   |

|             | 8Eh RW   | Reserved                               |                   |

|             | 8Fh RW   | Refresh                                |                   |

|             | 92h RW   | Port 92                                |                   |

| I/O Address | Register      |                                     | Function            |

|-------------|---------------|-------------------------------------|---------------------|

| 0A0h-BFh    | A0h WO        | Initialization Control Word ICW1    | Interrupt           |

|             | A0h WO        | Operation Control Word OCW2         | Controller 2        |

|             | A0h WO        | Operation Control Word OCW3         | (82C59A equivalent) |

|             | A0h RO        | Interrupt Service Resister          | Interrupt           |

|             | A0h RO        | Interrupt Request Resister          | Controller 2        |

| 0A0h-BFh    | A1h WO        | Initialization Control Word ICW2    | (82C59A             |

|             |               |                                     | equivalent)         |

|             | A1h WO        | Initialization Control Word ICW3    |                     |

|             | A1h WO        | Initialization Control Word ICW4    |                     |

|             | A1h RW        | Operation Control Word OCW1         |                     |

|             | A1h RW        | Interrupt Mask Resister             |                     |

| 0C0h-0DFh   | C0h RW        | DMA Channel 4 Base and Current      | DMA                 |

|             |               | Address                             | Controller 2        |

|             | C2h RW        | DMA Channel 4 Base and Current Word | (82C37A             |

|             | C4h RW        | DMA Channel 5 Base and Current      | equivalent)         |

|             |               | Address                             | -                   |

|             | C6h RW        | DMA Channel 5 Base and Current Word | -                   |

|             | C8h RW        | DMA Channel 6 Base and Current      |                     |

|             |               | Address                             | -                   |

|             | CAh RW        | DMA Channel 6 Base and Current Word | -                   |

|             | CCh RW        | DMA Channel 7 Base and Current      |                     |

|             |               | Address                             | -                   |

|             | CEh RW        | DMA Channel 7 Base and Current Word | -                   |

|             | D0h W0        | Command Register                    | -                   |

|             | D0h RO        | Status Register                     | -                   |

|             | D2h WO        | Request Register                    | -                   |

|             | D4h WO        | Mask Register                       | -                   |

|             | D6h WO        | Mode Register                       | -                   |

|             | D8h WO        | Clear Byte Pointer                  |                     |

|             | DAh RO        | Master Clear                        | -                   |

|             | DAh WO        | Temporary Register                  | +                   |

|             | DCh WO        | Clear Mask Register                 | +                   |

|             | DEh WO        | Write all Mask Register             | +                   |

| 0F0h-0FFh   | F0h,F1h<br>WO | Mathematical Co-processor Resister  |                     |

| 100h-1EFh   |               |                                     | Usable with ISA     |

|             |               |                                     | bus                 |

| I/O Address             | Register            |                                      | Function            |

|-------------------------|---------------------|--------------------------------------|---------------------|

| 170h-177h               | 170h RW             | Data Register                        |                     |

| 1701117711              | 170h RW             | Error Register                       | Hard Disk           |

|                         | 172h RW             | Sector Count                         | Controller          |

|                         | 172h RW             | Sector Number                        |                     |

|                         | 174h RW             | Cylinder HIGH                        | -                   |

|                         | 175h RW             | Cylinder LOW                         |                     |

|                         | 176h RW             | SDH Register                         |                     |

|                         | 170h RW             | Status Register                      |                     |

|                         | 177h WO             | Command Register                     | -                   |

| 1F0h-1F7h               | 1F0h RW             | Data Register                        | Hard Disk           |

| 11.011-11.711           | 1F1h RO             | Error Register                       | Controller          |

|                         | 1F2h RW             | Sector Count                         |                     |

|                         | 1F3h RW             | Sector Number                        |                     |

|                         | 1F4h RW             | Cylinder HIGH                        | -                   |

|                         | 1F5h RW             | Cylinder LOW                         | -                   |

|                         | 1F6h RW             | SDH Register                         | -                   |

|                         | 1F0h RO             |                                      |                     |

|                         | 1F7h WO             | Status Register                      | -                   |

| 1F8h-277h               |                     | Command Register                     | Usable with ISA bus |

| 278h-27Fh               | 278h RW             | LPT2 Data Port                       | USable with ISA bus |

| 27011-271,11            | 279h RO             | LPT2 Status Port                     | Parallel Port 2     |

|                         | 27911 RO<br>27Ah RW | LPT2 Control                         |                     |

|                         | 27An RW<br>27Bh RW  |                                      | -                   |

|                         | 27Bl RW<br>27Ch RW  | Automatic Address Strobe Register    | -                   |

|                         | 27Ch RW<br>27Dh RW  | Automatic Data Strobe Register       | -                   |

|                         |                     | Automatic Data Strobe Register       | -                   |

|                         | 27Eh RW             | Automatic Data Strobe Register       | -                   |

| 280h-2F7h               | 27Fh RW             | Automatic Data Strobe Register       | Usable with ISA bus |

| 2801-2F711<br>2F8h-2FFh | 2F8h RO             | Receiver Buffer                      | USADIE WIUTISA DUS  |

| ۵۲٥۱۱-۵۲۲۱۱             | 2F8h KO<br>2F8h WO  |                                      | Serial Port 2       |

|                         |                     | Transmit Holding Buffer              | Serial Port 2       |

|                         | 2F8h RW             | Divider Latch Least Significant Byte |                     |

|                         | 2F9h RW             | Divider Latch Most Significant Byte  |                     |

|                         | 2F9h RW             | Interrupt Enable Register            |                     |

|                         | 2FAh RO             | Interrupt Register                   |                     |

|                         | 2FBh RW             | Line Controller Register             |                     |

|                         | 2FCh RW             | MODEM Control Register               |                     |

|                         | 2FDh RO             | Status Register                      |                     |

|                         | 2FEh RO             | MODEM Status Register                |                     |

|                         | 2FFh RW             | Scratch Register                     |                     |

| I/O Address | Register |                                   | Function            |

|-------------|----------|-----------------------------------|---------------------|

| 300h-377h   |          |                                   | Usable with ISA bus |

| 378h-37Fh   | 378h RW  | LPT1 Data Port                    |                     |

|             | 379h RO  | LPT1 Status Port                  | Parallel Port 1     |

|             | 37Ah RW  | LPT1 Control                      |                     |

|             | 37Bh RW  | Automatic Address Strobe Register |                     |

|             | 37Ch RW  | Automatic Data Strobe Register    |                     |

|             | 37Dh RW  | Automatic Data Strobe Register    |                     |

|             | 37Eh RW  | Automatic Data Strobe Register    |                     |

|             | 37Fh RW  | Automatic Data Strobe Register    |                     |

| 380h-3B3h   |          |                                   | Usable with ISA bus |

| 3B4h-3BAh   | 3B4h RW  | CRT Controller Index              |                     |

|             | 3B5h RW  | CRT Controller Data               | VGA Controller      |

|             | 3BAh W   | Feature Control                   | (monochrome)        |

|             | 3BAh R   | Input Status Register             |                     |

| 3BBh-3BFh   |          |                                   | Usable with ISA bus |

| 3C0h-3CFh   | 3C0h W   | Attribute Controller Index/Data   |                     |

|             | 3C1h R   | Attribute Controller Index/Data   | VGA Controller      |

|             | 3C2h W   | Miscellaneous Output              |                     |

|             | 3C2h R   | Input Status Register             |                     |

|             | 3C3h RW  | VGA Enable                        |                     |

|             | 3C4h RW  | Sequencer Index                   |                     |

|             | 3C5h RW  | Sequencer Data                    |                     |

|             | 3C6h RW  | Video DAC Pixel Mask, Hidden DAC  |                     |

|             |          | Register                          |                     |

| 3C0h-3CFh   | 3C7h W   | Pixel Address Read Mode           |                     |

|             | 3C7h R   | DAC Status                        | VGA Controller      |

|             | 3C8h RW  | Pixel Mask Write Mode             |                     |

|             | 3C9h RW  | Pixel Data                        |                     |

|             | 3CAh R   | Future Control Readback           |                     |

|             | 3CCh R   | Miscellaneous Output Readback     |                     |

|             | 3CEh RW  | Graphics Controller Index         |                     |

|             | 3CFh RW  | Graphics Controller Data          |                     |

| 3D0h-3DFh   | 3D4h RW  | CRT Controller Index              |                     |

|             | 3D5h RW  | CRT Controller Data               | VGA Controller      |

|             | 3DAh W   | Feature Control                   | (color)             |

|             | 3DAh R   | Input Status Register             |                     |

| 3E0h-3EFh   |          |                                   | Usable with ISA bus |

| I/O Address | Register                  |                                      | Function       |

|-------------|---------------------------|--------------------------------------|----------------|

| 3F0h-3F7h   | 3F0h RW Status Register A |                                      | FDD Controller |

|             | 3F1h RW                   | Status Register B                    |                |

|             | 3F2h WO                   | Digital Output Register              |                |

|             | 3F3h RW                   | Tape Drive Register                  |                |

|             | 3F4h RW                   | Main Status Register                 |                |

|             | 3F5h RW                   | Data Register                        |                |

|             | 3F6h RW                   | Alternate Status, Device Control     | IDE            |

|             | 3F7h RO                   | Digital Input Resister               | IDE 1 section  |

|             |                           | (Shared with Hard Disk Controller)   | FDD            |

| 3F8h-3FFh   | 3F7h WO                   | Diskette Control Register            | FDD Controller |

|             | 3F8h RO                   | Receiver Buffer                      |                |

|             | 3F8h WO                   | Transmit holding Buffer              | Serial Port 1  |

|             | 3F8h RW                   | Divider Latch Least Significant Byte |                |

|             | 3F9h RW                   | Divider Latch Most Significant Byte  |                |

|             | 3F9h RW                   | Interrupt Enable Register            |                |

|             | 3FAh RO                   | Interrupt ID Register                |                |

|             | 3FBh RW                   | Line Control Register                |                |

|             | 3FCh RW                   | MODEM Control Register               |                |

|             | 3FDh RO                   | Status Register                      |                |

|             | 3FEh RO                   | MODEM Status Register                |                |

|             | 3FFh RW                   | Scratch Register                     |                |

#### 1.6 DMA controller

Table 1.2 DME controller 1

SCE8720C is provided with 2 DMA controllers (82C37A equivalent) used as follows. With SCE8720C, DMA is not available from users, as the ISA bus only has limited functions.

| Channel No. | Device                                 |

|-------------|----------------------------------------|

| СНО         | Not available (cannot be used by user) |

| CH1         | Not available (cannot be used by user) |

| CH2         | Floppy disk                            |

| CH3         | Not available (cannot be used by user) |

|--|

| Channel No. | Device                                 |

|-------------|----------------------------------------|

| CH4         | Cascade connection of controller 1.    |

| CH5         | Not available (cannot be used by user) |

| CH6         | Not available (cannot be used by user) |

| CH7         | Not available (cannot be used by user) |

Controller 1, including CH0 to CH3, is used for 8-bit data transfer. Up to 64KB block transfer is possible between 8-bit I/O and 8-bit memory or 16-bit memory.

Controller 2, including CH4 to CH7, is mainly used for 16-bit data transfer, and among them CH4 is used for cascade connection of controller 1. CH5 to CH7 are not used.

Controller 2, including CH4 to CH7, is mainly used for 16-bit data transfer, and among them CH4 is used for cascade connection of controller 1. CH5 to CH7 are not used.

| Table 1.4 Divin page register |             |  |  |  |

|-------------------------------|-------------|--|--|--|

| Page register                 | I/O address |  |  |  |

| DMA channel 0                 | 0087h       |  |  |  |

| DMA channel 1                 | 0083h       |  |  |  |

| DMA channel 2                 | 0081h       |  |  |  |

| DMA channel 3                 | 0082h       |  |  |  |

| DMA channel 5                 | 008Bh       |  |  |  |

| DMA channel 6                 | 0089h       |  |  |  |

| DMA channel 7                 | 008Ah       |  |  |  |

| REFRESH                       | 008Fh       |  |  |  |

Table 1.4 DMA page register

#### 1.7 System interrupts

The causes of interrupts on SCE8720C are shown below:

| Level | Functions                            |

|-------|--------------------------------------|

| SMI   | External system management interrupt |

|       | Power management VSA                 |

|       |                                      |

| IRQ   | Interrupts by interrupt controller   |

Table 1.5Causes of interrupts

IRQ interrupts are triggered by the 2 interrupt controllers (82C59 equivalent). The causes of interrupts by interrupt controllers are shown below:

| Controller 1 | Controller 2 | Device                               |

|--------------|--------------|--------------------------------------|

| IRQ0         |              | Timer out 0                          |

| IRQ1         |              | Keyboard                             |

| IRQ2         |              | Cascade connection from controller 2 |

|              | IRQ8         | Real time clock                      |

|              | IRQ9         | Usable with ISA bus                  |

|              | IRQ10        | Serial port (*)                      |

|              | IRQ11        | Serial port (*)                      |

|              | IRQ12        | Mouse                                |

|              | IRQ13        | Co-Processor                         |

|              | IRQ14        | HDD                                  |

|              | IRQ15        | Usable with ISA bus                  |

| IRQ3         |              | Serial port 2 (*)                    |

| IRQ4         |              | Serial port 1 (*)                    |

| IRQ5         |              | Parallel port 2 (*)                  |

| IRQ6         |              | FDD                                  |

| IRQ7         |              | Parallel port 1 (*)                  |

Table 1.6Levels of interrupts by interrupt controller

\*: SCE8720C has 2 serial ports and 1 parallel port built-in. Serial port interrupts are selected from IRQ3, 4, 10 or 11, and parallel port interrupts are selected from IRQ5 or 7. Interrupts not used by the built-in serial or parallel port can then be used with ISA bus.

Also, when not using HDD, IRQ14 can be used with ISA bus.

1

#### 1.8 Timer counter

SCE8720C has a 8254-equivalent timer counter and 3 independent timers. Their usage and inputs are shown below:

| Tuble 1.7 Timer T bettings |           |                                              |

|----------------------------|-----------|----------------------------------------------|

| Channel 0                  | GATE 0    | Fixed to ON                                  |

| System timer               | CLK IN 0  | 1.19MHz                                      |

|                            | CLK OUT 0 | Connected to IRQ0 of interrupt controller 1. |

| Channel 1                  | GATE 1    | Fixed to ON                                  |

| Refresh request            | CLK IN 1  | 1.19MHz                                      |

|                            | CLK OUT 1 | Refresh request                              |

| Channel 2                  | GATE 2    | Controlled by I/O port 61h.                  |

| Speaker interface          | CLK IN 2  | 1.19MHz                                      |

|                            | CLK OUT 2 | Used to drive the speaker interface.         |

Table 1.7 Timer 1 settings

#### 1.9 Real time clock and C-MOS RAM

SCE8720C has a real time clock which provides clock and calendar functions and CMOS RAM used to hold system configuration information. The real time clock is compatible with 146818.

Power must be supplied constantly to the  $V_{CCBAK}$  in order to maintain the operation of the real time clock and the contents of CMOS RAM.

When  $V_{CCSTB}$  is supplied even while the system power is OFF, power from the  $V_{CCSTB}$  is used for backup. When both the system power and  $V_{CCSTB}$  is OFF, battery power from the  $V_{CCBAK}$  is used.

#### 2. Mechanical specifications

2.1 Dimensions and weight

Figure 2.1 Dimensional Diagram

#### 2.2 Installation method

#### CARD-PCI installation connector

280-pin connector product name 1-353906-0 Manufactured by AMP 20-pin connector product name52030-2010 (ZIF, DIP) Manufactured by Molex For more information about installation, refer to the application note.

#### 3. Interface specifications

#### 3.1 Pin configuration

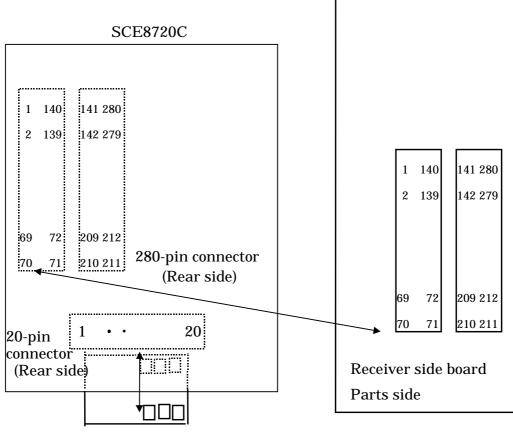

Pin configurations for the 20-pin connector (mainly FDD signal) and 280-pin connector of SCE8720C are shown in the figure.

In the figure, 280-pin connector is viewed from the rear side. Connector pin configurations on the main board, on which SCE8720C is installed, are shown in the figure. (Note that the 1 pin mark on the connector is different.)

Since the 20-pin connector is connected using the flexible flat cable (FFC), pin configurations on the receiving side board vary depending on the connector's installation method.

Flexible flat cable

Figure 3.1 Connector pin configuration

\* 280-pin connector

Most of the signals and powers of SCE8720C are connected via this connector. It consists of 2 140-pin connectors.

\* 20-pin connector

Connector for the flexible flat cable.

Signals for FDD and ISA bus interrupt signals are connected to this connector. When not using such signals, this connector is unconnected.

#### 3.1.1 280-pin connector pin configuration

| No. | Signal Name  | Block | No. | Signal Name | Block | No.  | Signal Name | Block | No. | Signal Name | Block       |

|-----|--------------|-------|-----|-------------|-------|------|-------------|-------|-----|-------------|-------------|

|     | GND          | PWR   | 140 | U U         | PWR   | 141  | 5           | PWR   |     | GND         | PWR         |

|     | ADO          | PCI   |     | CRTR        | CRT   |      | FPDOTE      | FP    |     | FPDOTCLK    | FP          |

|     | AD1          | PCI   |     | CRTG        | CRT   |      | FPVEEON     | FP    |     | FPVDDON     | FP          |

|     | AD2          | PCI   |     |             | CRT   | -    | RESERVED    | Video |     | IDEIOR#     | IDE         |

|     |              |       |     | CRTB        |       |      |             |       |     |             |             |

|     | VCC3V        | PWR   | 136 | VCC3V       | PWR   | 145  |             | PWR   |     | IDEIOW#     | IDE         |

|     | AD3          | PCI   | 135 | CRTHSYNC    | CRT   |      |             | FP    |     | IDEACK#     | IDE         |

|     | AD4          | PCI   | 134 |             | CRT   |      | FPDATA0     | FP    |     | IDED7       | IDE         |

| 8   | AD5          | PCI   | 133 | RESERVED    | AC97  | 148  | FPHSYNC     | FP    | 273 | IDECS1FX#   | IDE         |

| 9   | AD6          | PCI   | 132 | AC97RESET#  | AC97  | 149  | FPDATA1     | FP    | 272 | IDED8       | IDE         |

| 10  | AD7          | PCI   | 131 | AC97SYNC    | AC97  | 150  | FPDATA2     | FP    | 271 | IDED6       | IDE         |

| 11  | GND          | PWR   | 130 | GND         | PWR   | 151  | GND         | PWR   | 270 | GND         | PWR         |

|     | CBE0#        | PCI   |     | AC97BITCLK  | AC97  | 152  | FPDATA3     | FP    |     | IDED9       | IDE         |

|     | AD8          | PCI   |     | AC97SDIN0   | AC97  |      | FPDISPEN    | FP    |     | IDERESET#   | IDE         |

|     | AD9          | PCI   | 127 | AC97SDOUT   | AC97  |      | FPDATA4     | FP    |     | IDED5       | IDE         |

|     | AD10         | PCI   |     | PCBEEP      | MISC  |      | FPDATA5     | FP    | -   | IDECS3FX#   | IDE         |

|     | VCCSTB       | PWR   |     | VCC3V       | PWR   |      | FPDATA6     | FP    |     | IDED10      | IDE         |

|     |              |       |     |             |       |      |             |       |     |             |             |

|     | AD11         | PCI   |     | USBON       | USB   |      | FPDATA7     | FP    |     | IDED4       | IDE         |

|     | AD12         | PCI   |     | USBCUR#     | USB   |      | FPDATA8     | FP    |     | IDED11      | IDE         |

|     | AD13         | PCI   |     | USBDM0      | USB   |      | FPDATA9     | FP    |     | IDED3       | IDE         |

|     | AD14         | PCI   |     | USBDP0      | USB   |      | FPDATA10    | FP    |     | IDED12      | IDE         |

| 21  | GND          | PWR   | 120 | GND         | PWR   | 161  | GND         | PWR   | 260 | GND         | PWR         |

| 22  | AD15         | PCI   | 119 | USBDM1      | USB   | 162  | FPDATA11    | FP    | 259 | IDED2       | IDE         |

| 23  | CBE1#        | PCI   |     | USBDP1      | USB   | 163  | FPDATA12    | FP    |     | IDED13      | IDE         |

|     | PAR          | PCI   | 117 | STANDBY#    | PM    |      | FPDATA13    | FP    |     | IDED1       | IDE         |

|     | VCC5V        | PWR   |     | VCC5V       | PWR   | -    | FPDATA14    | FP    |     | IDED14      | IDE         |

|     | SERR#        | PCI   |     | POFF        | PM    |      | FPDATA15    | FP    |     |             | IDE         |

|     | PERR#        | PCI   |     | PWSW#       | PM    |      | FPDATA16    | FP    |     | IDED15      | IDE         |

|     | LOCK#        | PCI   |     | LPTD7       |       |      | FPDATA16    | FP    |     | IDEA2       | IDE         |

|     |              |       |     |             |       |      |             |       |     |             |             |

|     | STOP#        | PCI   |     | LPTD6       | LPT   |      | RESERVED    | MISC  |     | IDEA1       | IDE         |

|     | DEVSEL#      | PCI   |     | LPTD5       | LPT   |      | RESERVED    | MISC  |     | IDEA0       | IDE         |

| 31  | GND          | PWR   | 110 | GND         | PWR   | 171  | GND         | PWR   | 250 | GND         | PWR         |

|     | TRDY#        | PCI   | 109 | LPTD4       | LPT   | 172  | RESERVED    | MISC  | 249 | IDEDRQ      | IDE         |

| 33  | RESERVED     | MISC  | 108 | LPTD3       | LPT   | 173  | RESERVED    | MISC  | 248 | IDERDY      | IDE         |

| 34  | IRDY#        | PCI   | 107 | LPTD2       | LPT   | 174  | RESERVED    | MISC  | 247 | IDEINT      | IDE         |

| 35  | VCC3V        | PWR   | 106 | VCC3V       | PWR   | 175  | VCCCORE     | PWR   | 246 | POWERGOO    | РМ          |

|     | FRAME#       | PCI   |     | LPTD1       | LPT   |      | VCCCORE     | PWR   |     | IOCS16#     | ISA         |

|     | PME0#        | PM    |     | LPTD0       | LPT   | 177  | VCCCORE     | PWR   |     | IOCHRDY     | ISA         |

|     | CBE2#        | PCI   |     | LPTAFD#     | LPT   |      | VCCCORE     | PWR   |     | VCCCORE     | PWR         |

|     | AD16         | PCI   |     | LPTSLCTIN#  | LPT   |      | RESERVED    | MISC  |     | IOW#        | ISA         |

|     |              |       |     |             |       |      |             |       |     |             |             |

|     | GND          | PWR   |     | GND         | PWR   | 180  |             | PWR   | 241 | GND         | PWR         |

|     | AD17         | PCI   |     | LPTINIT#    | LPT   | 181  | MEMCS16#    | ISA   |     | IOR#        | ISA         |

|     | AD18         | PCI   |     | LPTERROR#   | LPT   |      | RESERVED    | MISC  |     | SD15/SA15   | ISA         |

| 43  | AD19         | PCI   | 98  | LPTPE       | LPT   |      | VCCCORE     | PWR   | 238 | SD14/SA14   | ISA         |

| 44  | AD20         | PCI   | 97  | LPTSLCT     | LPT   | 184  | VCCCORE     | PWR   | 237 | SD13/SA13   | ISA         |

| 45  | VCC3V        | PWR   | 96  | VCC3V       | PWR   | 185  | VCCCORE     | PWR   | 236 | SD12/SA12   | ISA         |

| 46  | AD21         | PCI   | 95  | LPTACK#     | LPT   | 186  | VCCCORE     | PWR   | 235 | SD11/SA11   | ISA         |

|     | AD22         | PCI   |     | LPTSTROBE#  |       |      | RESERVED    | MISC  |     | SD10/SA10   | ISA         |

|     | AD23         | PCI   |     | LPTBUSY     | LPT   |      | ROMCS#      | ISA   |     | VCCCORE     | PWR         |

|     | CBE3#        | PCI   |     | IRQ5        | ISA   |      | MEMW#       | ISA   |     | SD9/SA9     | ISA         |

|     | GND          | PWR   |     | GND         | PWR   |      |             | PWR   |     |             | PWR         |

|     | AD24         |       |     | PORT3       |       |      |             | ISA   |     |             | ISA         |

|     |              |       |     |             |       |      | MEMR#       |       |     | SD8/SA8     |             |

|     | AD25         | PCI   |     | PORT4       | GPIO  |      |             | ISA   |     | SD0/SA0     | ISA         |

|     | AD26         | PCI   |     | PME1#       | PM    |      | SA17        | ISA   |     | SD1/SA1     | ISA         |

|     | AD27         | PCI   |     | MSDATA      | KB/MS |      | SA18        | ISA   |     | SD2/SA2     | ISA         |

|     | VCC3V        | PWR   |     | MSCLK       | KB/MS |      |             | ISA   |     | SD3/SA3     | ISA         |

| 56  | AD28         | PCI   | 85  | VCCBAK      | PWR   | 196  | AEN         | ISA   | 225 | SD4/SA4     | ISA         |

| 57  | AD29         | PCI   | 84  | KBDATA      | KB/MS | 197  | SBHE#       | ISA   | 224 | SD5/SA5     | ISA         |

|     | AD30         | PCI   |     | KBCLK       | KB/MS |      |             | ISA   |     | SD6/SA6     | ISA         |

|     | AD31         | PCI   |     | RESERVED    | MISC  |      |             | ISA   |     | SD7/SA7     | ISA         |

|     | GND          | PWR   |     | GND         |       |      | GND         | PWR   |     | GND         | PWR         |

|     | RST#         |       | -   | RESERVED    | MISC  |      |             | ISA   |     | SALATCH     |             |

|     |              |       |     |             |       |      |             |       |     |             | ISA<br>COM1 |

|     | INTD#        | PCI   |     | RESERVED    | MISC  |      | COM2CTS#    | COM2  |     | COM1CTS#    | COM1        |

|     | INTC#        | PCI   |     | REQ1#       | PCI   |      | COM2CD#     | COM2  |     | COM1CD#     | COM1        |

|     | INTB#        | PCI   |     | GNT1#       | PCI   |      | COM2DSR#    | COM2  |     | COM1DSR#    | COM1        |

| 65  | INTA#        | PCI   | 76  | REQ0#       | PCI   | 205  | COM2DTR#    | COM2  |     | COM1DTR#    | COM1        |

|     | VCC3V        | PWR   |     | VCC3V       | PWR   |      | COM2RI#     | COM2  |     | COM1RI#     | COM1        |

|     | PCLK2        | PCI   |     | GNT0#       | PCI   |      | COM2RTS#    | COM2  |     | COM1RTS#    | COM1        |

|     | CPUFRQ       | MISC  |     | ROMDIS      | MISC  |      | COM2RXD     | COM2  |     | COM1RXD     | COM1        |

| 00  |              | PCI   |     | PCLK1       | PCI   |      | COM2TXD     | COM2  |     | COM1TXD     |             |

| 60  |              |       |     |             | IT UI | 1209 |             |       |     |             | COM1        |

|     | PCLK0<br>GND | PWR   |     | GND         |       |      | GND         | PWR   | 011 | GND         | PWR         |

| Table 3.1 | 280-pin | connector | pin | configuration |

|-----------|---------|-----------|-----|---------------|

|-----------|---------|-----------|-----|---------------|

#### CARD-PCI/GX Hardware Manual

## 3.1.2 20-pin connector pin configuration

| Table 3.2 | able 3.2 20-pin connector pin configuration |       |  |  |

|-----------|---------------------------------------------|-------|--|--|

| Pin No.   | Signal name                                 | Block |  |  |

| 1         | DSKCHG#                                     | FDD   |  |  |

| 2         | WP#                                         | FDD   |  |  |

| 3         | INDEX#                                      | FDD   |  |  |

| 4         | TRK0#                                       | FDD   |  |  |

| 5         | RDATA#                                      | FDD   |  |  |

| 6         | DENSEL                                      | FDD   |  |  |

| 7         | WGATE#                                      | FDD   |  |  |

| 8         | HDSEL#                                      | FDD   |  |  |

| 9         | STEP#                                       | FDD   |  |  |

| 10        | DIR#                                        | FDD   |  |  |

| 11        | WDATA#                                      | FDD   |  |  |

| 12        | DR0#                                        | FDD   |  |  |

| 13        | MTR0#                                       | FDD   |  |  |

| 14        | GND                                         | PWR   |  |  |

| 15        | IRQ15                                       | ISA   |  |  |

| 16        | IRQ 7                                       | ISA   |  |  |

| 17        | GND                                         | PWR   |  |  |

| 18        | IRQ4                                        | ISA   |  |  |

| 19        | GND                                         | PWR   |  |  |

| 20        | IRQ3                                        | ISA   |  |  |

Table 3.220-pin connector pin configuration

#### 3.2 Signal characteristics

This section describes characteristics of each signal. Characteristic factors are as follows:

- I/O Type of signal input/output.

- Voltage Input: Indicates the voltage level that can be input.

Output: Indicates the voltage level that can be output.

• pull-up /down

Indicates whether or not the signal is pulled-up or pulled-down inside SCE8720C.

- IoL/IOH Indicates drive ability of the output buffer sink current and source current.

- Reference PU/PD Reference value of required pull-up or pull-down resistance.

(When using all the IO port.)

• pull-up /down when not used

Indicates whether or not pull-up or pull-down is required when not using signals.

#### CARD-PCI/GX Hardware Manual

#### Descriptions on symbols indicating these factors are shown below:

Symbol description

| 2911201 4  | escription   |                                                                              |

|------------|--------------|------------------------------------------------------------------------------|

| Item       | Symbol       | Description                                                                  |

| I/O        | I/O          | Input/output                                                                 |

|            | s/t/s        | Sustained tri-state (reference PCI v2.1))                                    |

|            | I/OD         | Input and open drain output                                                  |

|            | Ι            | Input only                                                                   |

|            | 0            | Output only                                                                  |

|            | OD           | Open drain output                                                            |

|            | programmable | Input/output is set by software.                                             |

| Voltage    | 3.3V         | Output is 0 to 3.3V. Input must be 0 to 3.3V.                                |

|            | 3.3V ,5VT    | Output is 0 to 3.3V. Input can be 0 to 5V. (5V input is TTL level.)          |

|            | 5VSTB        | V <sub>CCSTB</sub> is supplied to the input/output element power supply.     |

|            | 5V           | Both input and output is 0 to 5.0V (5V input is TTL level.)                  |

| pull-up    | XpU(5V)      | Pulled-up to 5V by resistance of $x\Omega$ inside SCE8720C.                  |

| /down      | xPU(3.3V)    | Pulled-up to 3.3V by resistance of x $\Omega$ inside SCE8720C.               |

|            | xPU(5VSTB)   | Pulled-up to V <sub>CCSTB</sub> by resistance of x $\Omega$ inside SCE8720C. |

|            | xPD          | Pulled-down by resistance of x $\Omega$ inside SCE8720C.                     |

|            | weak-PU      | Pulled-up to 5V by Approx. $40k\Omega$ resistance.                           |

|            | Weak-PD      | Pulled-down by Approx. 40kΩ resistance.                                      |

| Iol/Ioh    | х/-у         | Output drivability: sink current x, source current y                         |

| Refe-      | xPU(5V)      | Pulled-up to 5V by x $\Omega$ resistance.                                    |

| rence      | XPU(5VSTB)   | Pulled-up to $V_{CCSTB}$ by x $\Omega$ resistance.                           |

| PU/PD      | XPU(3.3V)    | Pulled-up to 3.3V by x $\Omega$ resistance.                                  |

| pull-up    | PU           | Even when not using the signal in the system, some kind of pull-             |

| /down when |              | up is necessary. NC is not available.                                        |

| not used   |              |                                                                              |

Rev.A

**EPSON**

#### Signal characteristics

| Signal name            | No. of | Block | I/O   | Vol- | pull-up/ | Iol  | Іон   | Reference | When not used |

|------------------------|--------|-------|-------|------|----------|------|-------|-----------|---------------|

| 0                      |        | DIOCK | 1/0   |      |          | TOL  | TOH   |           |               |

| 280-pin connector      | pins   |       |       | tage | down     |      |       | PU/PD     | PU/PD         |

| AD[31:0],CBE[3:0]#,PAR | 37     | PCI   | I/O   | 3.3V |          | 5mA  | -2mA  |           |               |

| FRAME#,IRDY#,TRDY#,    | 7      | PCI   | s/t/s | 3.3V | 20kPU    | 5mA  | -2mA  | 8.2kPU    |               |

| STOP# ,DEVSEL#,LOCK#   |        |       |       |      | (3.3V)   |      |       | (3.3V)    |               |

| ,PERR#                 |        |       |       |      |          |      |       |           |               |

| SERR#                  | 1      | PCI   | I/OD  | 3.3V | 20kPU    | 5mA  |       | 8.2kPU    |               |

|                        |        |       |       |      | (3.3V)   |      |       | (3.3V)    |               |

| RST#                   | 1      | PCI   | 0     | 3.3V |          | 16mA | -16mA |           |               |

| REQ[1:0]#              | 2      | PCI   | Ι     | 3.3V | 20kPU    |      |       |           |               |

|                        |        |       |       |      | (3.3V)   |      |       |           |               |

| GNT[1:0]#              | 2      | PCI   | 0     | 3.3V |          | 5mA  | -2mA  |           |               |

| PCLK[2:0]              | 3      | PCI   | 0     | 3.3V |          | 8mA  | -8mA  |           |               |

| INTA#,INTB#,           | 4      | PCI   | Ι     | 3.3V |          |      |       | 2.7kPU    | PU            |

| INTC#,INTD#            |        |       |       |      |          |      |       | (3.3V)    |               |

#### Table 3.3 PCI signal characteristics

| Table 3.4  | ISA s | ional | characteristics  |

|------------|-------|-------|------------------|

| 1 abie 5.4 | IDU 3 | ngnai | character istics |

| Signal name       | No. of | Block | I/O | Vol-  | pull-up/ | Iol | Іон  | Reference | When not used |

|-------------------|--------|-------|-----|-------|----------|-----|------|-----------|---------------|

| 280-pin connector | pins   |       |     | tage  | down     |     |      | PU/PD     | PU/PD         |

| SD/SA[15:8]       | 8      | ISA   | I/O | 3.3V, | 20kPU    | 8mA | -8mA |           |               |

|                   |        |       |     | 5VT   | (3.3V)   |     |      |           |               |

| SD/SA[7:0]        | 8      | ISA   | I/O | 3.3V, | 20kPU    | 8mA | -8mA | 4.7kPU    |               |

|                   |        |       |     | 5VT   | (3.3V)   |     |      | (5V)      |               |

| SA[19:16],SBHE#   | 5      | ISA   | 0   | 3.3V  | 20kPU    | 8mA | -8mA |           |               |

|                   |        |       |     |       | (3.3V)   |     |      |           |               |

| MEMR#,MEMW#,IOR#, | 4      | ISA   | 0   | 3.3V, | 4.7kPU   | 8mA | -8mA |           |               |

| IOW#              |        |       |     | 5VT   | (5V)     |     |      |           |               |

| SALATCH           | 1      | ISA   | 0   | 3.3V  |          | 4mA | -4mA |           |               |

| AEN               | 1      | ISA   | 0   | 3.3V  |          | 8mA | -8mA |           |               |

| ROMCS#            | 1      | ISA   | 0   | 3.3V  |          | 4mA | -4mA |           |               |

| MEMCS16#,IOCS16#  | 2      | ISA   | Ι   | 3.3V, | 1kPU     |     |      |           |               |

|                   |        |       |     | 5VT   | (5V)     |     |      |           |               |

| IOCHRDY           | 1      | ISA   | Ι   | 3.3V, | 1kPU     |     |      |           |               |

|                   |        |       |     | 5VT   | (5V)     |     |      |           |               |

| IRQ[5,9,10,11]    | 4      | ISA   | Ι   | 3.3V, | 10kPU    |     |      |           |               |

|                   |        |       |     | 5VT   | (5V)     |     |      |           |               |

|                   |        |       |     | <b>V</b> /1 |          | т    | т     | DC        |               |

|-------------------|--------|-------|-----|-------------|----------|------|-------|-----------|---------------|

| Signal name       | No. of | Block | I/O | Vol-        | pull-up/ | Iol  | Іон   | Reference | When not used |

| 280-pin connector | pins   |       |     | tage        | down     |      |       | PU/PD     | PU/PD         |

| CRTHSYNC,CRTVSYNC | 2      | CRT   | 0   | 3.3V        |          | 16mA | -16mA |           |               |

| FPHSYNC,FPVSYNC   | 25     | FP    | 0   | 3.3V        |          | 8mA  | -8mA  |           |               |

| FPDATA[17:0]      |        |       |     |             |          |      |       |           |               |

| FPDOTCLK,FPDOTE,  |        |       |     |             |          |      |       |           |               |

| FPDISPEN,         |        |       |     |             |          |      |       |           |               |

| FPVEEON, FPVDDON  |        |       |     |             |          |      |       |           |               |

| CRTR,CRTG,CRTB    | 3      | CRT   | 0   | Ana         | 75PD     |      |       |           |               |

|                   |        |       |     | -log        |          |      |       |           |               |

Table 3.5 CRT, LCD signal characteristics

#### Table 3.6 IDE signal characteristics

| Signal name            | No. of | Block | I/O | Vol-  | pull-up/ | Iol | I <sub>OH</sub> | Reference | When not used |

|------------------------|--------|-------|-----|-------|----------|-----|-----------------|-----------|---------------|

| 280-pin connector      | pins   |       |     | tage  | down     |     |                 | PU/PD     | PU/PD         |

| IDED[15:8]             | 15     | IDE   | I/O | 3.3V, |          | 8mA | -8mA            |           |               |

| IDED[6:0]              |        |       |     | 5VT   |          |     |                 |           |               |

| IDED7                  | 1      | IDE   | I/O | 3.3V, | 10kPD    | 8mA | -8mA            |           |               |

|                        |        |       |     | 5VT   |          |     |                 |           |               |

| IDEA[2:0],IDEIOR#,IDEI | 9      | IDE   | 0   | 3.3V  |          | 8mA | -8mA            |           |               |

| OW#,IDEACK#,           |        |       |     |       |          |     |                 |           |               |

| IDECS1FX#,IDECS3FX#,   |        |       |     |       |          |     |                 |           |               |

| IDERESET#              |        |       |     |       |          |     |                 |           |               |

| IDERDY                 | 1      | IDE   | Ι   | 3.3V, | 1kPU     |     |                 |           |               |

|                        |        |       |     | 5VT   | (5V)     |     |                 |           |               |

| IDEINT(IRQ14)          | 1      | IDE   | Ι   | 3.3V, | 10kPU    |     |                 |           |               |

|                        |        |       |     | 5VT   | (5V)     |     |                 |           |               |

| IDEDRQ                 | 1      | IDE   | Ι   | 3.3V, | 10kPD    |     |                 |           |               |

|                        |        |       |     | 5VT   |          |     |                 |           |               |

#### Table 3.7USB signal characteristics

| Signal name       | No. of | Block | I/O | Vol-  | pull-up/ | Iol | Іон  | Reference | When not used |

|-------------------|--------|-------|-----|-------|----------|-----|------|-----------|---------------|

| 280-pin connector | pins   |       |     | tage  | down     |     |      | PU/PD     | PU/PD         |

| USBDM1, USBDP1    | 4      | USB   | I/O | 3.3V  | 15kPD    |     |      |           |               |

| USBDM0, USBDP0    |        |       |     |       |          |     |      |           |               |

| USBON             | 1      | USB   | 0   | 3.3V  |          | 4mA | -4mA |           |               |

| USBCUR#           | 1      | USB   | Ι   | 3.3V, |          |     |      | 10kPU     | PU            |

|                   |        |       |     | 5VT   |          |     |      | (5V)      |               |

| Table 3.8 | Serial port signal | l characteristics |

|-----------|--------------------|-------------------|

|-----------|--------------------|-------------------|

| Signal name         | No. of | Block  | I/O | Vol- | pull-up/ | Iol  | Іон  | Reference | When not used |