# **EPSON**

## NOTICE

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

©Seiko Epson Corporation 2000 All rights reserved.

PC/AT and VGA are trademarks of International Business Machines Corporation in U.S.A.. Windows is a registered trademark of Microsoft in U.S.A.. Ethernet is a registered trademark of Xerox Corporation in U.S.A..

CompactFlash is a trademark of Sandisk Corporation in U.S.A.. CompactFlash is licensed to CFA (CompactFlash Association).

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

| 1. Introduction                                                  | 1  |

|------------------------------------------------------------------|----|

| 2. Video Interface                                               | 2  |

| 2.1. CRT Interface                                               |    |

| 2.2. LCD Interface                                               | 2  |

| 2.3. LCD Connection                                              |    |

| 2.3.1. Signal and Power Line Connections                         |    |

| 2.3.1.1. Signal Lines                                            |    |

| 2.3.1.1.1. LCD interface                                         |    |

| 2.3.1.1.2. External Clock Input Mode                             |    |

| 2.3.1.2. Power Sequence                                          |    |

| 2.3.2. Panel Parameter Setup Method                              |    |

| 2.3.2.1. SED1355 Register Settings                               |    |

| 2.3.2.2. Hardware Portrait Mode                                  |    |

| 2.3.2.3. Frame Rate and Display Performance                      |    |

| 2.3.2.4. LCD and CRT Simultaneous Display                        |    |

| 2.3.2.5. Notes on Connecting a Monochrome LCD Panel              |    |

| 2.3.3. STARTUP.DAT Settings                                      |    |

| 2.3.4. Design Notes                                              |    |

| 3. External Buses                                                |    |

| 3.1. Memory Map                                                  |    |

| 3.2. SH Bus                                                      |    |

| 3.2.1. Notes on Operation                                        |    |

| 3.2.2. Wait Cycles                                               |    |

| 3.3. ISA bus                                                     |    |

| 3.3.1. Differences from Full ISA Bus                             |    |

| 3.3.2. 8/16-bit Devices                                          |    |

| 3.3.3. Other Notes                                               |    |

| 3.4. PCMCIA Interface                                            |    |

| 3.4.1. Access Method                                             |    |

| 3.4.1.1. Windows                                                 |    |

| 3.4.1.2. Bank Switching                                          |    |

| 3.4.2. CompactFlash card connection to the PCMCIA Slot           |    |

| 3.4.3. 8/16-bit Access                                           |    |

| 3.4.4. Interface Timing                                          |    |

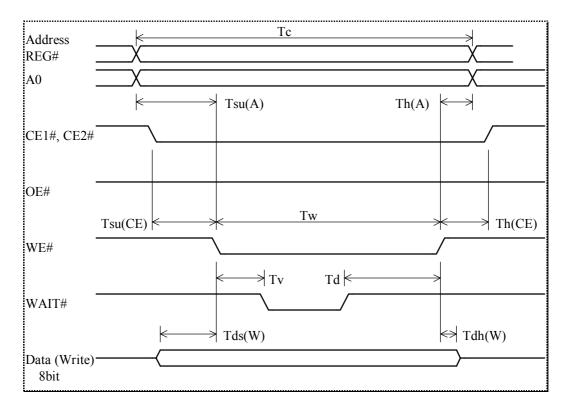

| 3.4.4.1. PCMCIA Timing                                           |    |

| 3.4.4.2. External Buffer Control Timing for Address/Data Signals |    |

| 3.4.5. Other Considerations                                      |    |

|                                                                  |    |

| 4. Serial Communication Interface                                |    |

| 4.1. Serial Interface                                            |    |

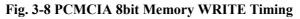

| 4.2. Infrared Communication                                      | 44 |

| 5. Parallel Port Interface                                       | 45 |

| 5.1. Design Notes                                                | 45 |

| 5.2. EPP Mode                                                    | 45 |

| 5.3. Current Flows                                               | 46 |

|                                                                  |    |

| 6.1. Design Notes                                               |    |

|-----------------------------------------------------------------|----|

| 6.2. Interface Connector Pin Layout                             |    |

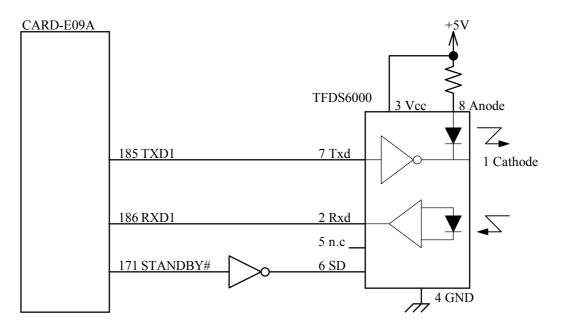

| 7. A/D and D/A Conversion                                       | 48 |

| 8. Power Management                                             | 51 |

| 8.1. CPU standby                                                |    |

| 8.2. Suspend Mode                                               |    |

| 8.2.1. Suspend/Resume Trigger Conditions                        | 52 |

| 8.2.1.1. Suspend Resume Button (SRBTN#)                         |    |

| 8.2.1.2. PTC Assignment and STARTUP.DAT Settings                |    |

| 8.2.2. LCD Panel Power On/Off Sequence                          |    |

| 8.2.3. PCMCIA Socket Power On/Off Sequence                      |    |

| 8.2.4. Notes on Pin Termination                                 |    |

| 8.3. Other Notes                                                | 61 |

| 9. Power Supply                                                 | 62 |

| 9.1. RTC Backup                                                 |    |

| 9.2. Reset Circuit                                              |    |

| 9.3. Power and POWERGOOD                                        |    |

| 9.4. PWOFF# Signal                                              |    |

|                                                                 |    |

| 10. Matters to be Noted in Use of CARD-E09A                     |    |

| 10.1. Power Supply and Grounding                                |    |

| 10.1.1. Power Connection                                        |    |

| 10.1.2. Power Line Wiring                                       |    |

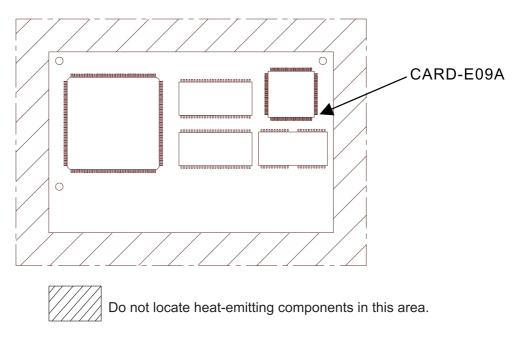

| 10.2. Matters to be Noted in Designing of Printed Circuit Board |    |

| 10.3. EMC and Static Noise Solution                             |    |

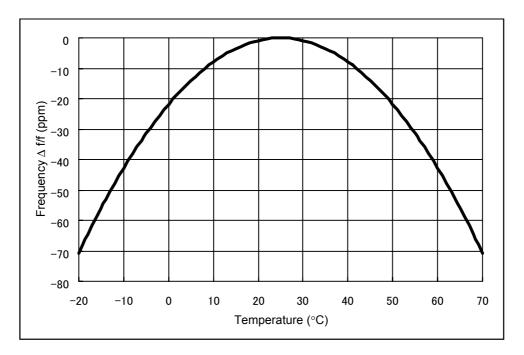

| 10.4. Accuracy of RTC                                           | 68 |

| 11. Pin Termination                                             | 69 |

| 12. Method of fixing and attachment                             | 76 |

| 12.1. Method of Attachment                                      |    |

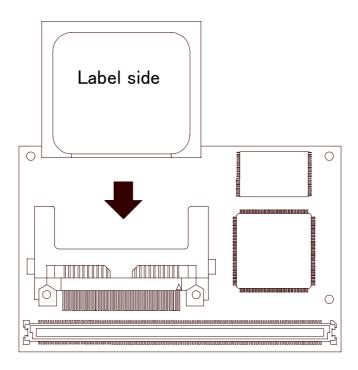

| 12.1.1. Installing a CompactFlash card                          | 76 |

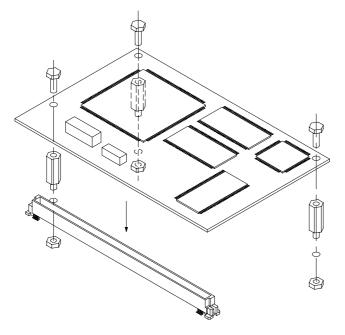

| 12.1.2. CARD-E09A attachment                                    |    |

| 12.2. Connector.                                                | 78 |

| 13. Appendix                                                    |    |

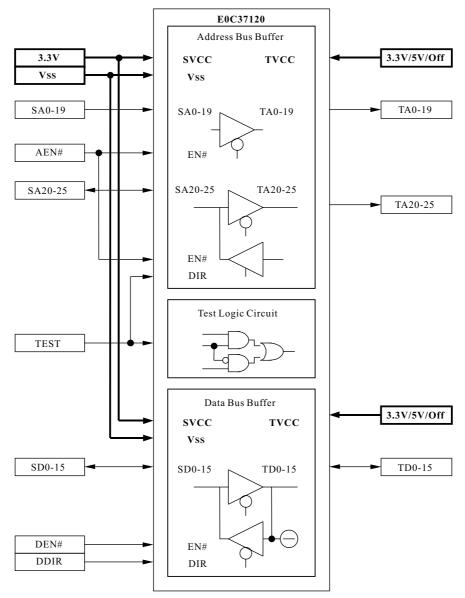

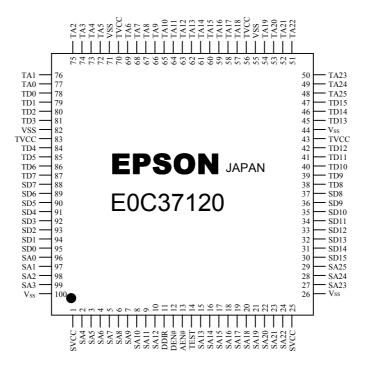

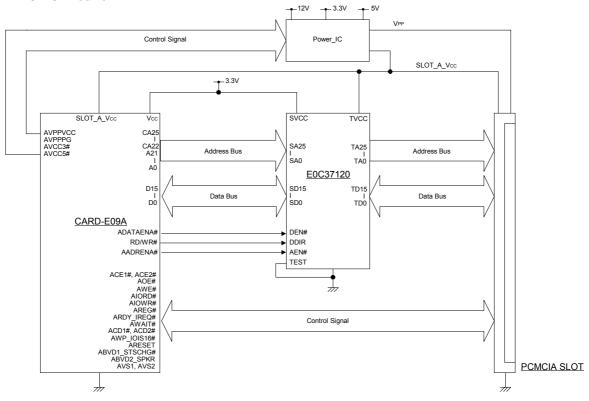

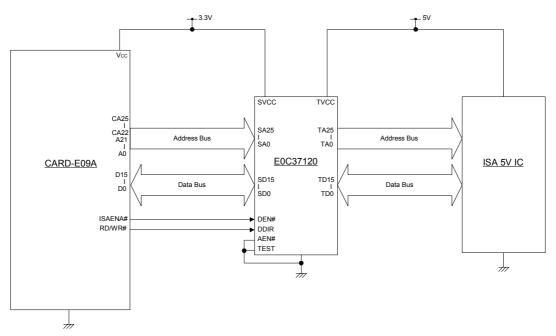

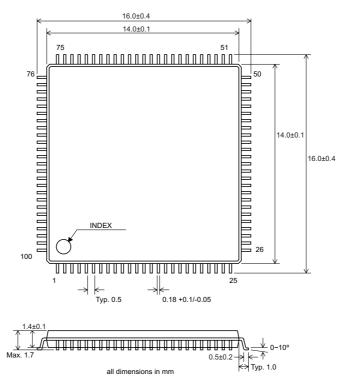

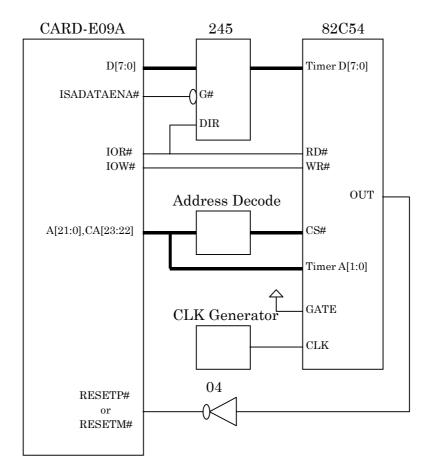

| 13.1. Multifunction Buffer IC (E0C37120)                        |    |

| 13.1.1. Overview                                                |    |

| 13.1.2. Features                                                |    |

| 13.1.3. Block Diagram                                           |    |

| 13.1.4. Connector Description                                   |    |

| 13.1.5. Electrical Characteristics                              |    |

| 13.1.6. Example Applications                                    |    |

| 13.1.7. Package Dimensions                                      |    |

| 13.1.7.1 ackage Difference Circuit Diagrams                     |    |

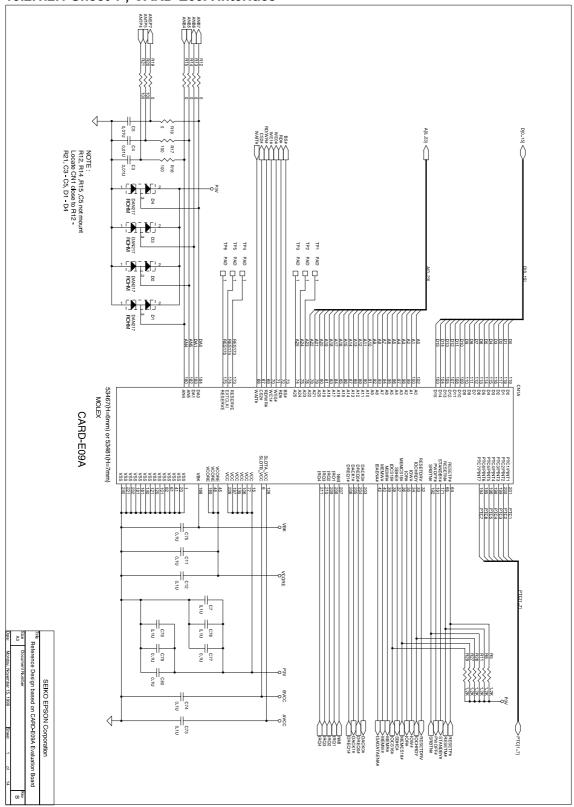

| 13.2.1. Reference Circuit Diagrams Based on Evaluation Board    |    |

| 13.2.1.1. Differences from the Evaluation Board                 |    |

| 13.2.1.2. Reference Circuit Diagrams                            |    |

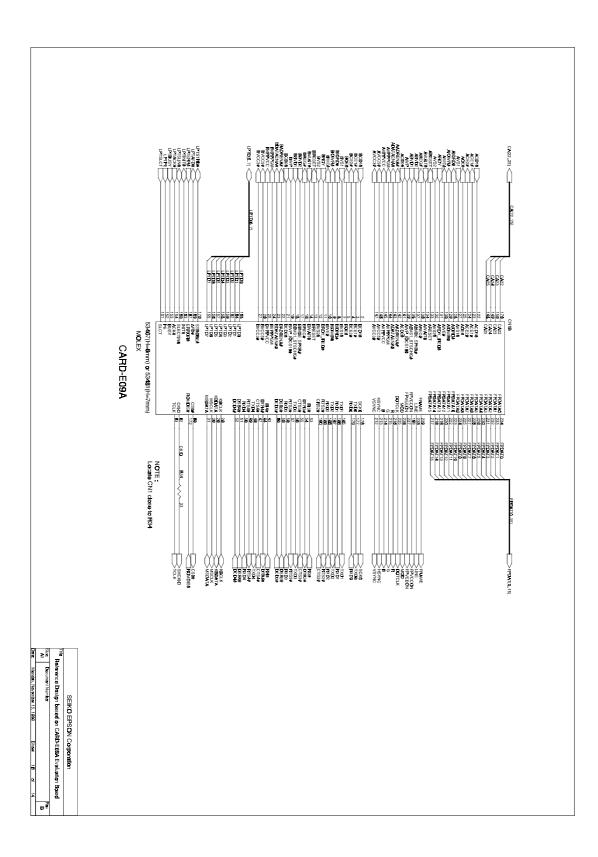

| 13.2.1.2.1 Sheet 1 ; CARD-E09A Interface                        |    |

ii

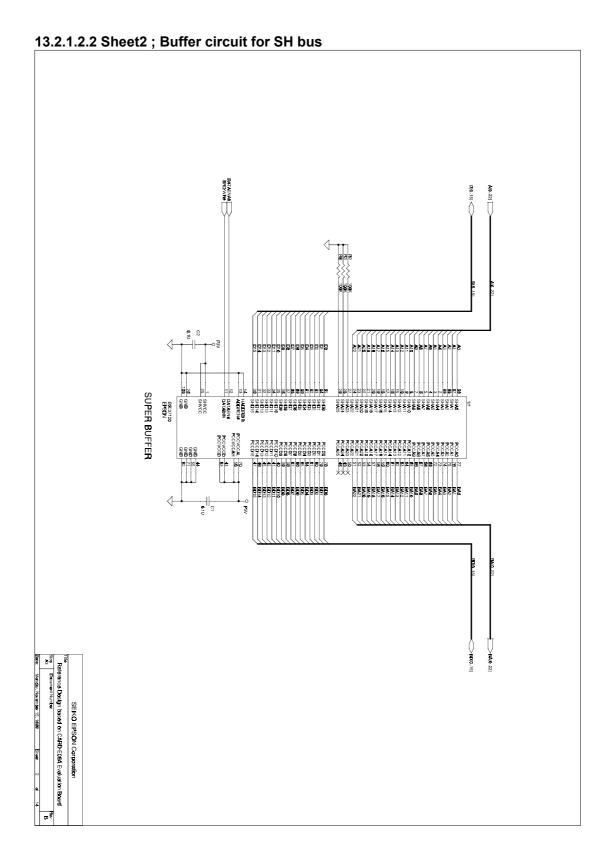

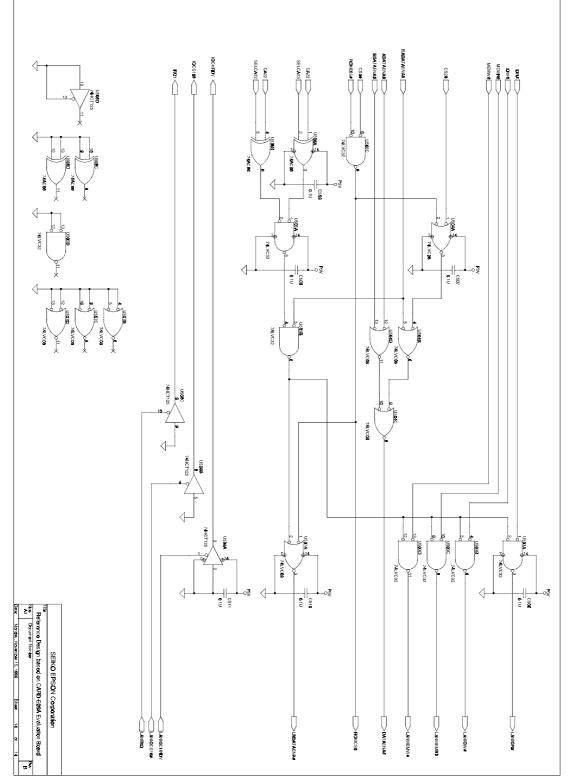

| 13.2.1.2.2 Sheet2 ; Buffer circuit for SH bus                  | 91  |

|----------------------------------------------------------------|-----|

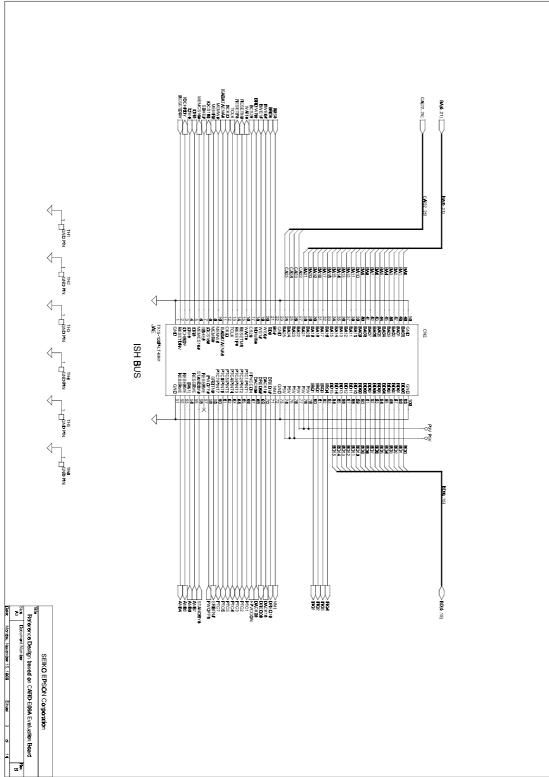

| 13.2.1.2.3 Sheet3 ; ISH bus Interface                          | 92  |

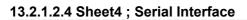

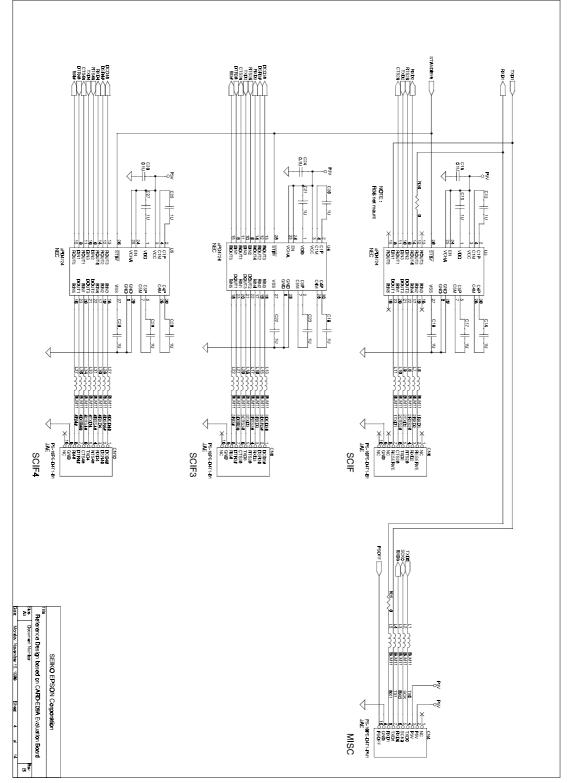

| 13.2.1.2.4 Sheet4 ; Serial Interface                           | 93  |

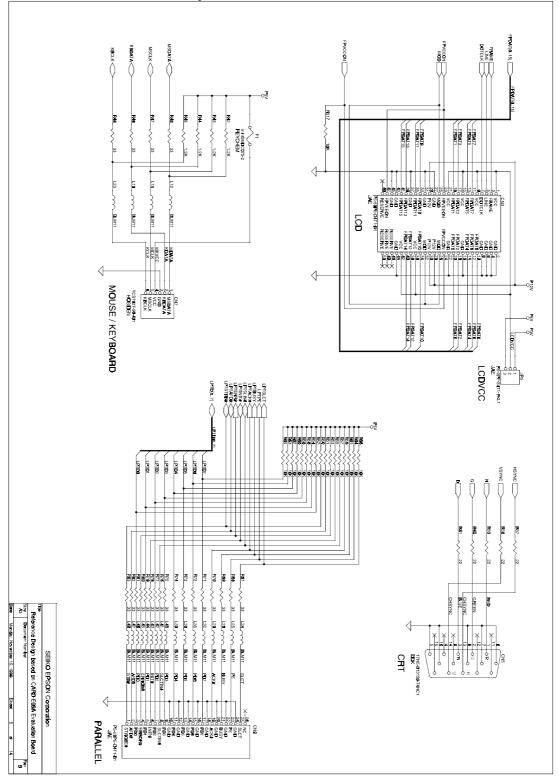

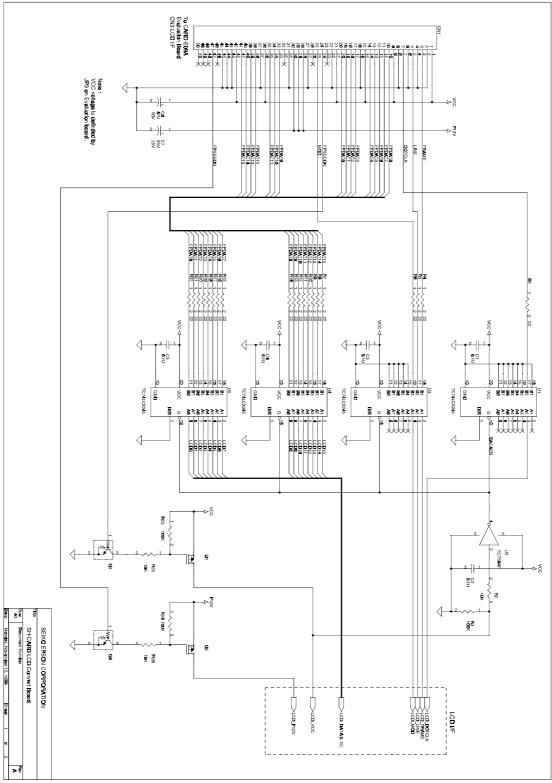

| 13.2.1.2.5 Sheet5 ; Video, Key Board/Mouse, Parallel Interface | 94  |

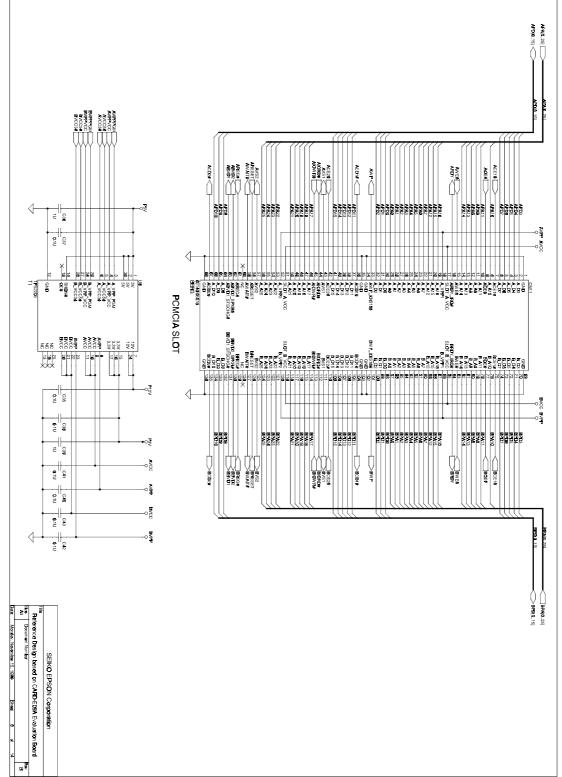

| 13.2.1.2.6 Sheet6 ; PCMCIA Interface                           | 95  |

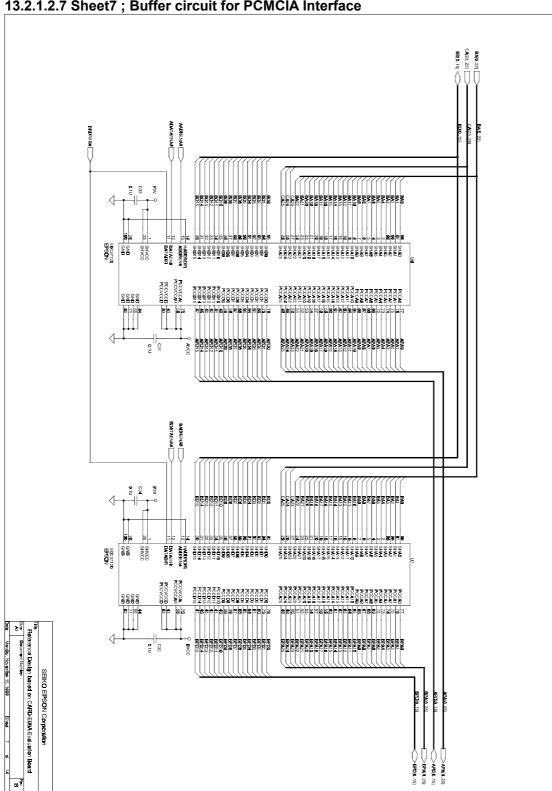

| 13.2.1.2.7 Sheet7 ; Buffer circuit for PCMCIA Interface        | 96  |

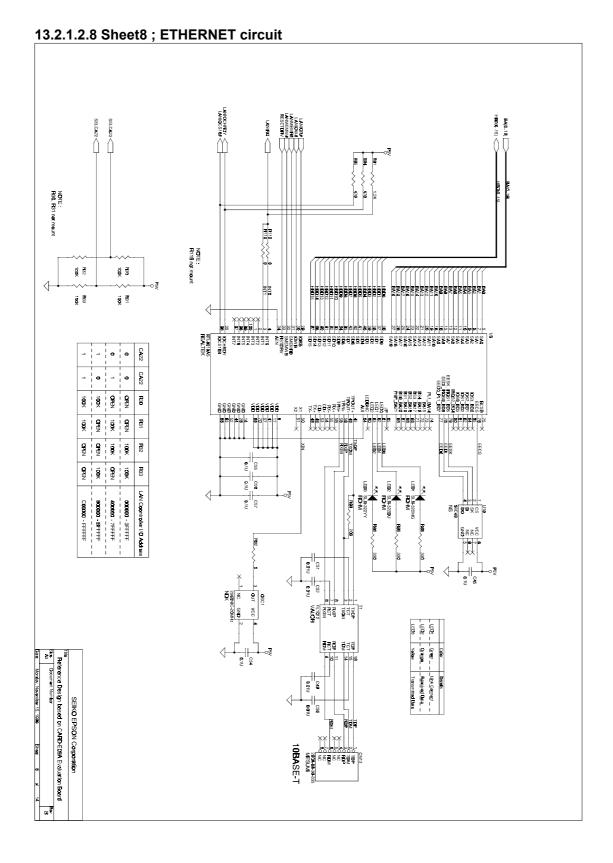

| 13.2.1.2.8 Sheet8 ; ETHERNET circuit                           | 97  |

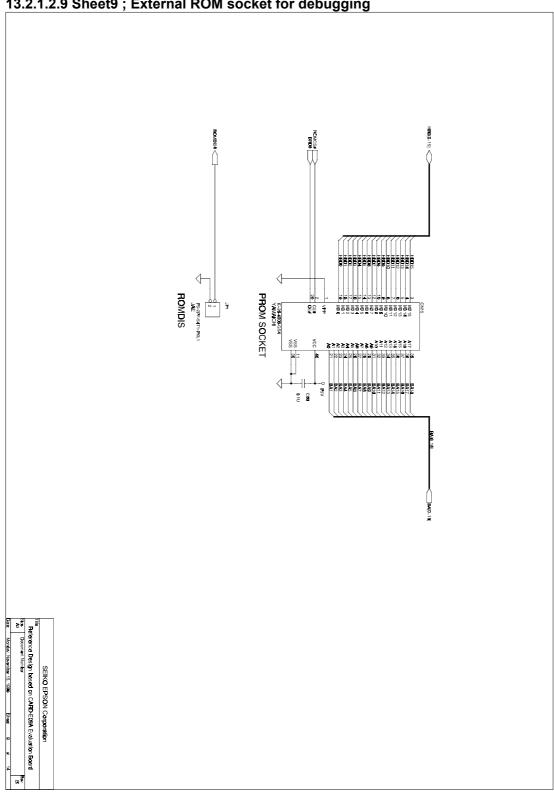

| 13.2.1.2.9 Sheet9 ; External ROM socket for debugging          | 98  |

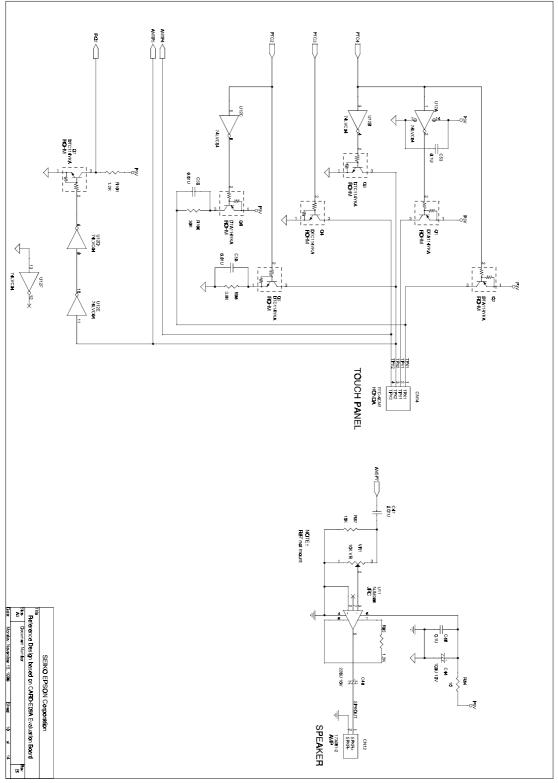

| 13.2.1.2.10 Sheet10; Touch Panel, Audio Circuit                | 99  |

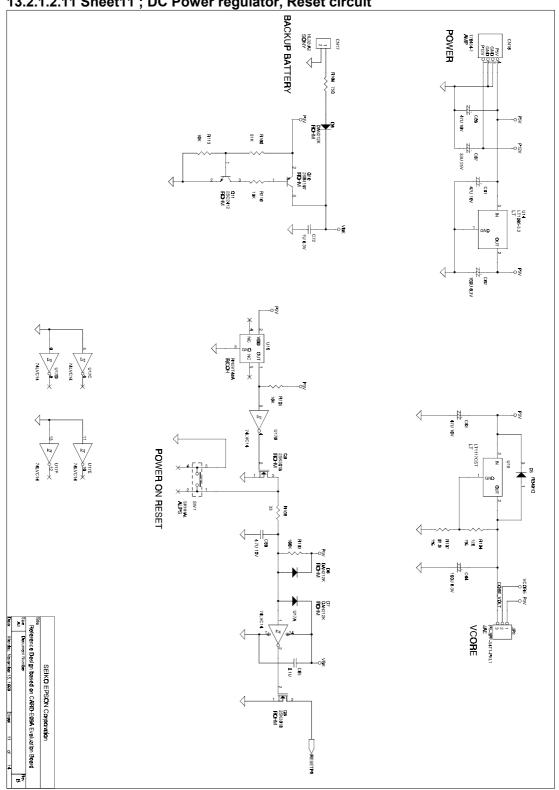

| 13.2.1.2.11 Sheet11; DC Power regulator, Reset circuit         | 100 |

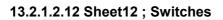

| 13.2.1.2.12 Sheet12 ; Switches                                 | 101 |

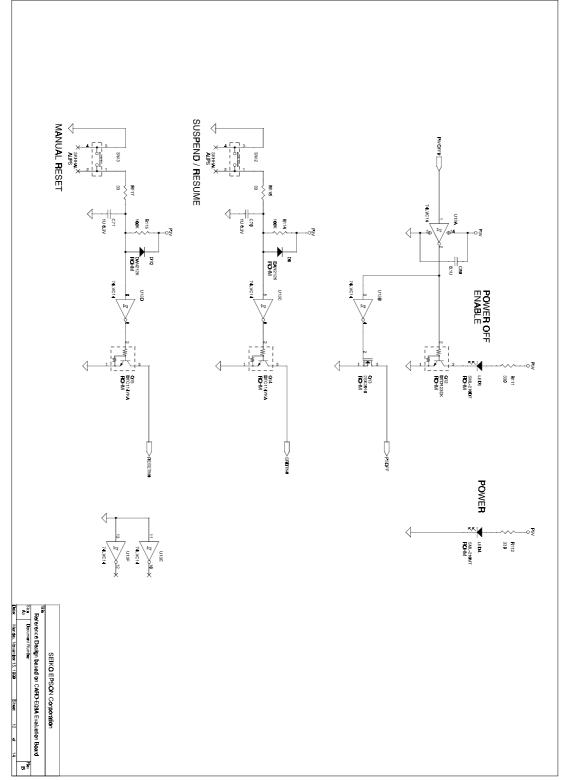

| 13.2.1.2.13 Sheet13 ; Buffer                                   | 102 |

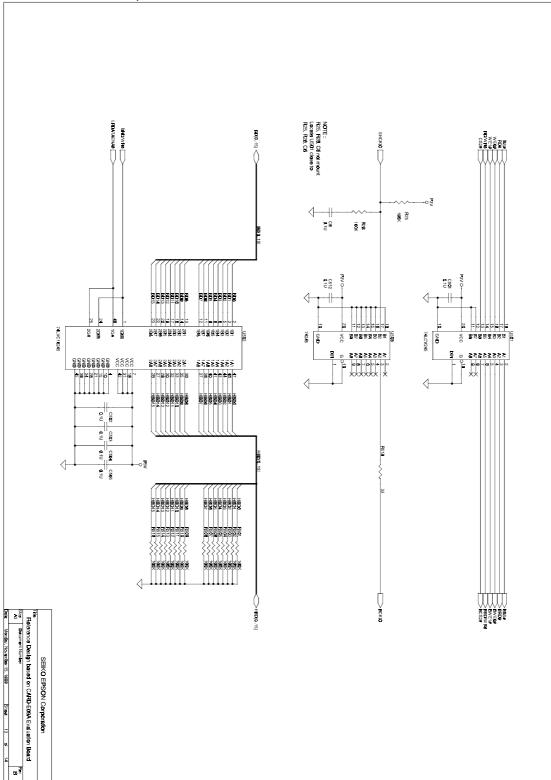

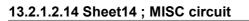

| 13.2.1.2.14 Sheet14 ; MISC circuit                             | 103 |

| 13.2.1.3. LCD Interface                                        | 104 |

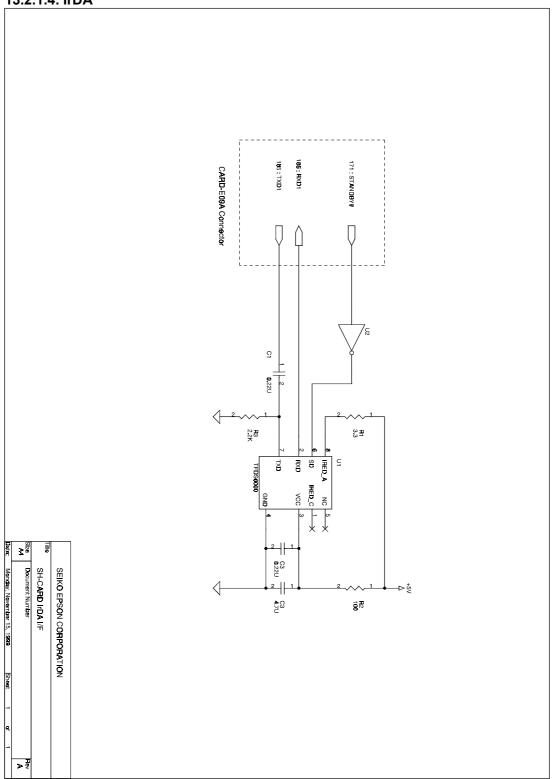

| 13.2.1.4. IrDA                                                 | 105 |

| 13.3. Methods of Using a Watchdog Timer (WDT)                  | 106 |

| 13.3.1. Method of Connecting an External Circuit               | 106 |

| 13.3.2. Method of Using the SH7709A Internal Function          | 107 |

| 13.4. Temperature Measurement Sample Data                      | 109 |

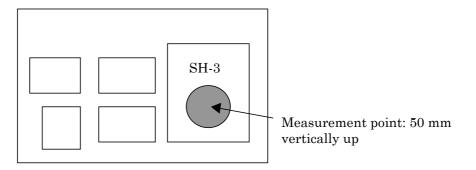

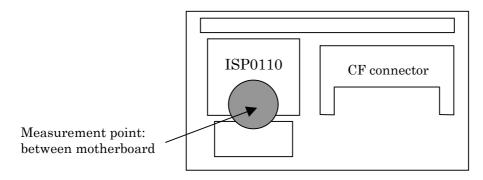

| 13.4.1. Measurement System Configurations                      | 109 |

| 13.4.2. Measurement Conditions                                 | 110 |

| 13.4.3. Measurement Results                                    | 111 |

| 13.4.4. Cautions                                               | 111 |

| 13.5. MTTF (Mean Time To Failure)                              | 111 |

# 1. Introduction

This document is an Application Note to be used for reference when designing systems using the CARD-E09A. Use it in conjunction with the "CARD-E09A Hardware Manual," "SED1355F0A Technical Manual," the "Evaluation Board Hardware Manual" supplied with the CARD-E09A evaluation kit (SCE88J0X01), and the "Windows CE Development Kit Instruction Manual" supplied with the CARD-E09A Windows CE Development Kit (SCE88J3X01).

This document assumes incorporation into an operating system created using the Windows CE Development Kit provided by Epson for the CARD-E09A. Therefore, if a different operating system is used, additional software, such as device drivers, and additional hardware, such as extra circuits on the motherboard on which the CARD-E09A is mounted may be required.

# 2. Video Interface

The CARD-E09A includes LCD controller (SED1355, Seiko Epson) with internal RAM DAC. For the video memory 2MB ( $1M \times 16$  bits, 60 ns) of EDO-RAM is connected. In terms of display device, it can drive a CRT, a LCD, or both at the same time. Video signal output switching can be specified in STARTUP.DAT (described below). The STARTUP.DAT setting not only switches between CRT and LCD panel, but can also set the panel parameters so that various LCD panels can be connected. The main difference between the CRT interface and the LCD interface is that the former is an analog output whereas the latter is a digital (TTL) output. For details, see "SED1355F0A Technical Manual."

## 2.1. CRT Interface

In Section 13.2.1.2, "Reference Circuit Diagrams," Sheet 5 "Video, Keyboard/Mouse, Parallel Interface" shows a reference circuit diagram. Only eight signal lines are required to connect the CARD-E09A to the CRT interface connector.

## 2.2. LCD Interface

The LCD interface of CARD-E09A can be connected to the following liquid display panels:

#### Interface types

- 4-bit single monochrome passive LCD panel (bus configuration:  $4 \times 1$ )

- 8-bit single monochrome passive LCD panel (bus configuration:  $8 \times 1$ )

- 4-bit single color passive LCD panel (bus configuration:  $4 \times 1$ )

- 8-bit single color passive LCD panel (bus configuration:  $8 \times 1$ )

- 16-bit single color passive LCD panel (bus configuration:  $16 \times 1$ )

- 8-bit dual monochrome passive LCD panel (bus configuration:  $4 \times 2$ )

- 8-bit dual color passive LCD panel (bus configuration:  $4 \times 2$ )

- 16-bit dual color passive LCD panel (bus configuration:  $8 \times 2$ )

- 9-bit TFT color LCD panel (color configuration: R, G, B × 3)

- 12-bit TFT color LCD panel (color configuration: R, G, B × 4)

- 16-bit TFT color LCD panel (color configuration:  $R \times 5$ ,  $G \times 6$ ,  $B \times 5$ )

#### Display sizes and colors

The panel parameter settings (see 2.3.2.) principally allow the following display sizes and colors. Although the size can be adjusted to a size other than the following, the maximum size is SVGA.

- QVGA (320 × 240), maximum 16 bpp (65,536 colors)

- VGA (640 × 480), maximum 16 bpp (65,536 colors)

- SVGA ( $800 \times 600$ ), maximum 8 bpp (256 colors)

## 2.3. LCD Connection

This describes the LCD panel connection and notes thereon. When connecting an LCD panel, follow the procedure given in this section for checking. The following is an outline.

Step 1: Check the signal and power line connections: see Section 2.3.1.

Step 2: Check the panel parameter settings: see Section 2.3.2.

Step 3: Amend the STARTUP.DAT settings as required: see Section 2.3.3.

#### 2.3.1. Signal and Power Line Connections

#### 2.3.1.1. Signal Lines

#### 2.3.1.1.1. LCD interface

Tables 2-1 to 2-3 show the connections between the CARD-E09A and the LCD panel. Refer to this together with Table 5-9, "Interface Connector Assignment" in the "SED1355F0A Technical Manual." In the following table, FPFRAME is the frame pulse, FPLINE is the line pulse, and FPSHIFT is the shift clock pulse; MOD is the bias signal for a passive panel, and the display enable signal for a TFT panel. Note that the actual names may vary from panel to panel.

| CARD           | -E09A      | Monochrome passive panel |         |       |

|----------------|------------|--------------------------|---------|-------|

|                |            | Single                   |         | Dual  |

| Connector name | Pin number | 4-bit                    | 8-bit   | 8-bit |

| FRAME          | 239        |                          | FPFRAME |       |

| LINE           | 238        |                          | FPLINE  |       |

| DOTCLK         | 235        |                          | FPSHIFT |       |

| MOD            | 236        |                          | MOD     |       |

| FPDAT0         | 234        |                          | D0      | LD0   |

| FPDAT1         | 233        |                          | D1      | LD1   |

| FPDAT2         | 232        | _                        | D2      | LD2   |

| FPDAT3         | 231        | _                        | D3      | LD3   |

| FPDAT4         | 230        | D0                       | D4      | UD0   |

| FPDAT5         | 229        | D1 D5                    |         | UD1   |

| FPDAT6         | 228        | D2 D6 U                  |         | UD2   |

| FPDAT7         | 227        | D3                       | D7      | UD3   |

| FPDAT8         | 225        | _                        | _       | _     |

| FPDAT9         | 224        | _                        | _       | _     |

| FPDAT10        | 223        | _                        | _       | _     |

| FPDAT11        | 222        | _                        | _       | -     |

| FPDAT12        | 220        |                          |         | -     |

| FPDAT13        | 219        |                          |         |       |

| FPDAT14        | 218        |                          |         | _     |

| FPDAT15        | 217        | _                        | _       | _     |

Table 2-1 Signal connector assignment (monochrome passive panel)

| Table 2-2 Signal connector assignment (color passive panel) |        |        |                    |                    |           |       |        |

|-------------------------------------------------------------|--------|--------|--------------------|--------------------|-----------|-------|--------|

| CARD                                                        | -E09A  |        |                    | Color pass         | ive panel |       |        |

|                                                             |        | Single | Single<br>format 1 | Single<br>format 2 | Single    | Dı    | ıal    |

| Connector                                                   | Pin    | 4-bit  | 8-bit              | 8-bit              | 16-bit    | 8-bit | 16-bit |

| name                                                        | number |        |                    |                    |           |       |        |

| FRAME                                                       | 239    |        |                    | FPFR.              | AME       |       |        |

| LINE                                                        | 238    |        |                    | FPLI               | NE        |       |        |

| DOTCLK                                                      | 235    |        |                    | FPSH               | IIFT      |       |        |

| MOD                                                         | 236    | MOD    | FPSHIFT2           |                    | MO        | DD    |        |

| FPDAT0                                                      | 234    | _      | D0                 | D0                 | D0        | LD0   | LD0    |

| FPDAT1                                                      | 233    | _      | D1                 | D1                 | D1        | LD1   | LD1    |

| FPDAT2                                                      | 232    | _      | D2                 | D2                 | D2        | LD2   | LD2    |

| FPDAT3                                                      | 231    | _      | D3                 | D3                 | D3        | LD3   | LD3    |

| FPDAT4                                                      | 230    | D0     | D4                 | D4                 | D4        | UD0   | UD0    |

| FPDAT5                                                      | 229    | D1     | D5                 | D5                 | D5        | UD1   | UD1    |

| FPDAT6                                                      | 228    | D2     | D6                 | D6                 | D6        | UD2   | UD2    |

| FPDAT7                                                      | 227    | D3     | D7                 | D7                 | D7        | UD3   | UD3    |

| FPDAT8                                                      | 225    | _      | _                  | _                  | D8        | _     | LD4    |

| FPDAT9                                                      | 224    | _      | _                  | -                  | D9        | _     | LD5    |

| FPDAT10                                                     | 223    | _      | _                  | _                  | D10       | _     | LD6    |

| FPDAT11                                                     | 222    | _      | -                  | _                  | D11       | _     | LD7    |

| FPDAT12                                                     | 220    | _      | -                  | —                  | D12       | _     | UD4    |

| FPDAT13                                                     | 219    | _      | -                  | _                  | D13       | _     | UD5    |

| FPDAT14                                                     | 218    | _      | -                  | _                  | D14       | _     | UD6    |

| FPDAT15                                                     | 217    | _      | -                  | _                  | D15       | _     | UD7    |

Table 2-2 Signal connector assignment (color passive panel)

| Table 2-5 Signal connector assignment (color 1F1 panel) |            |                 |         |        |  |  |

|---------------------------------------------------------|------------|-----------------|---------|--------|--|--|

| CARD-E09A                                               |            | Color TFT panel |         |        |  |  |

|                                                         |            |                 |         |        |  |  |

| Connector name                                          | Pin number | 9-bit           | 12-bit  | 18-bit |  |  |

| FRAME                                                   | 239        |                 | FPFRAME |        |  |  |

| LINE                                                    | 238        |                 | FPLINE  |        |  |  |

| DOTCLK                                                  | 235        |                 | FPSHIFT |        |  |  |

| MOD                                                     | 236        |                 | DRDY    |        |  |  |

| FPDAT0                                                  | 234        | R2              | R3      | R5     |  |  |

| FPDAT1                                                  | 233        | R1              | R2      | R4     |  |  |

| FPDAT2                                                  | 232        | R0              | R1      | R3     |  |  |

| FPDAT3                                                  | 231        | G2              |         |        |  |  |

| FPDAT4                                                  | 230        | G1 G2 G4        |         | G4     |  |  |

| FPDAT5                                                  | 229        | G0 G1 G3        |         |        |  |  |

| FPDAT6                                                  | 228        | B2 B3 B5        |         |        |  |  |

| FPDAT7                                                  | 227        | B1 B2 B4        |         |        |  |  |

| FPDAT8                                                  | 225        | B0 B1 B3        |         |        |  |  |

| FPDAT9                                                  | 224        | _               | R0      | R2     |  |  |

| FPDAT10                                                 | 223        | _               | _       | R1     |  |  |

| FPDAT11                                                 | 222        | _               | G0      | G2     |  |  |

| FPDAT12                                                 | 220        | _               | _       | G1     |  |  |

| FPDAT13                                                 | 219        | – – <u>G</u> 0  |         |        |  |  |

| FPDAT14                                                 | 218        | – B0 B2         |         |        |  |  |

| FPDAT15                                                 | 217        | – – <u>B</u> 1  |         |        |  |  |

Table 2-3 Signal connector assignment (color TFT panel)

#### Notes

- 1) Unused data lines on the CARD-E09A are driven at low level.

- 2) For single color passive panels, format 1 and 2 have different data formats. See "SED1355F0A Technical Manual."

#### 2.3.1.1.2. External Clock Input Mode

The default setting of the SED1355 LCD controller built into the CARD-E09A (referred to as "internal clock mode") is to operate synchronized to the system clock CKIO (33.2 MHz). The dot clock signal (DOTCLK) for the LCD panel is also generated by frequency division of CKIO, so depending on the LCD panel it may not be possible to meet the dot clock signal specification. The dot clock signal in internal clock mode is shown in Table 2-4 and the dot clock signal for typical LCD panels is shown in Table 2-5. The clock divisor is determined by the setting of SED1355 REG[19h].

#### Notes

DOTCLK is different from the CARD-E09A internal display reference clock signal (PCLK) for each pixel. The setting of SED1355 REG[19h] only affects PCLK, and therefore when determining DOTCLK, it is essential to check Table 2-10 "Relation between DOTCLK and PCLK," and Table 2-11 "Restrictions on PCLK settings" in Section 2.3.2, "Panel parameter settings." Table 2-4 shows the relationship for a TFT panel or the like, when DOTCLK = PCLK.

| Frequency divisor | DOTCLK [MHz] |

|-------------------|--------------|

| CKIO/1            | 33.2         |

| CKIO/2            | 16.6         |

| CKIO/3            | 11.1         |

| CKIO/4            | 8.3          |

|              | Color VGA TFT | Color VGA STN | Mono VGA STN | Mono VGA STN  |

|--------------|---------------|---------------|--------------|---------------|

|              |               | (Dual Scan)   | (Dual Scan)  | (Single Scan) |

| DOTCLK [MHz] | 25.175        | 12.587        | 6.294        | 3.147         |

Table 2-5 shows only typical frequency for the dot clock, but in general an LCD panel has minimum, reference, and maximum values stipulated for the dot clock signal. For any of the frequency divisors shown in Table 2-4, if the specification range cannot be satisfied, or if it is necessary to make fine adjustments to the dot clock signal to optimize the display performance, this cannot be supported in internal clock mode.

The above problems can be solved by operating in external clock input mode. In external clock input mode, for the SED1355 reference clock signal, CKIO is replaced by an external input to the CARD-E09A. The following procedure is required for setting external clock input mode.

#### Step 1) Connect the external clock circuit to the CARD-E09A.

To pin 174, "EXTCLKI" of the CARD-E09A interface connector, connect the most appropriate external clock source for LCD panel. Note the following points when selecting the external clock frequency and designing the circuit.

- The input voltage rating and AC characteristics rating must be strictly observed. VIL = VCC × 0.3 Max., VIH = VCC × 0.7 Min., VCC = 3.3V For the AC characteristics, refer to Chapter 8, "AC Characteristics" in the "CARD-E09A Hardware Manual."

- 2) Maximum frequency which can be set = 33.2 MHz This is based on the specification of the 2 MB EDO-RAM used in the CARD-E09A. If a clock source exceeding this frequency is connected, the display quality cannot be guaranteed.

- Select as high a frequency as possible. The clock source connected to "EXTCLKI" is used as the reference clock signal for SED1355 operation. To get the optimal performance, select as high a frequency as possible. Table 2-6 shows examples.

|                | Color VGA TFT | Color VGA STN  | Mono VGA STN   | Mono VGA STN     |

|----------------|---------------|----------------|----------------|------------------|

|                |               | (Dual Scan) #1 | (Dual Scan) #2 | (Single Scan) #3 |

| External clock | 25.175        | 25.175         | 25.175         | 25.175           |

| source [MHz]   |               |                |                |                  |

| Divisor        | 1             | 2              | 1              | 1                |

| PCLK [MHz]     | 25.175        | 12.587         | 25.175         | 25.175           |

| DOTCLK [MHz]   | 25.175        | 12.587         | 6.294          | 3.147            |

Table 2-6 Examples of external clock source

- #1) If the minimum rating of the dot clock signal specification for the LCD panel is 11.1 MHz or below, in internal clock mode a divisor of 3 can be set. In the external clock input mode, the SED1355 reference clock signal is 25.175 MHz, while in the internal clock mode it is 33.2 MHz, and therefore the internal clock mode gives better performance.

- #2) This is the example in which DOTCLK = PCLK/4. If the maximum rating of the dot clock signal specification of the LCD panel is 8.3 MHz or above, in internal clock mode a divisor of 1 can be set. As in Note #1, the internal clock mode gives better performance.

- #3) This is the example in which DOTCLK = PCLK/8. If the maximum rating of the dot clock signal specification of the LCD panel is 4.2 MHz or above, in internal clock mode a divisor of 1 can be set. As in Note #1, the internal clock mode gives better performance.

#### Step 2) Set STARTUP.DAT to external clock input mode.

The change to the external clock input mode occurs based on the STARTUP.DAT settings in the power-on sequence.

In the CARD-E09A, the SH7709A Port E register bit 2 is connected to the switchover selector for the SED1355 reference clock signal. When the external clock input mode is set, it is necessary first to edit STARTUP.DAT. For details, see Section 2.3.3, "STARTUP.DAT Settings."

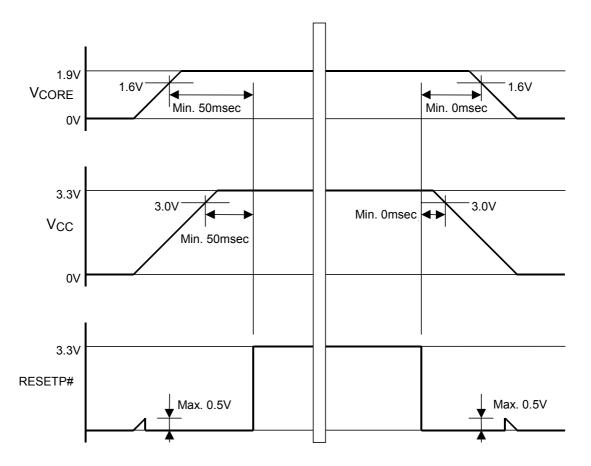

## 2.3.1.2. Power Sequence

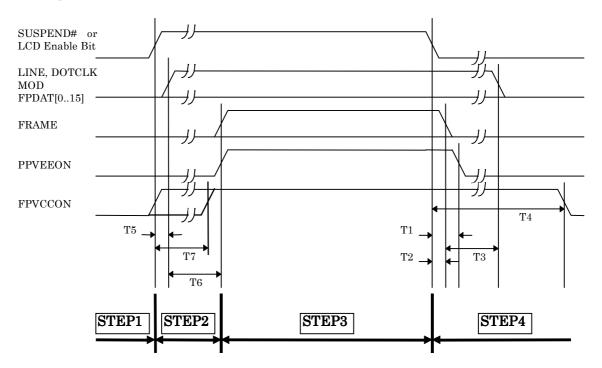

FPVCCON and FPVEEON signals are prepared for the LCD panel power control. By merely adding a power on/off circuit, the LCD panel can be powered on and off easily. An overview of the power sequence is shown in Fig. 2-1. In this figure, the power on/off timing and the suspend/resume timing are shown together. This should be seen together with Section 7.4, "Power Sequence" of the "SED1355F0A Technical Manual." Note that in the "SED1355F0A Technical Manual," FPVEEON is shown as LCDPWR. Again, FPVCCON is not an SED1355 function, but is added with the CARD-E09A specification.

Fig. 2-1 Overview of Power Sequence

| [Fig. 2-1] |                                                                                                                                                                      |                                                     |                    |       |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------------------|-------|

| Symbol     | Item                                                                                                                                                                 | Min.                                                | Max.               | Units |

| T1         | "SUSPEND# Bit" enable, or<br>"LCD Enable Bit" disable to<br>FPVEEON off                                                                                              | _                                                   | 2 Frame + Dotelk   | ns    |

| T2         | "SUSPEND# Bit" enable or<br>"LCD Enable Bit" disable to<br>FRAME inactive                                                                                            | -                                                   | 1                  | Frame |

| Т3         | FRAME inactive to LINE,<br>DOTCLK, MOD, and<br>FPDAT[015] inactive                                                                                                   | 128                                                 | -                  | Frame |

| T4         | "SUSPEND# Bit" enable or<br>"LCD Enable Bit" disable to<br>FPVCCON off                                                                                               | 10<br>(Setting can be<br>changed in<br>STARTUP.DAT) | -                  | ms    |

| T5         | "SUSPEND# Bit" disable or<br>"LCD Enable Bit" enable to<br>LINE, DOTCLK, MOD,<br>FPDAT[015] active                                                                   | -                                                   | 1 Frame + 8 Dotclk | ns    |

| T6         | LINE, DOTCLK, MOD,<br>FPDAT[015] active to<br>FRAME active, and<br>FPVEEON on                                                                                        | 128                                                 | -                  | Frame |

| T7         | "SUSPEND# Bit" disable or<br>"LCD Enable Bit" enable to<br>FPVCCON on<br><u>(Timing can be set in</u><br><u>STARTUP.DAT, and in a</u><br>resume is fixed at 0 frame) | 0<br>(This value is fixed in<br>a resume)           | 127                | Frame |

1) In the figure above, "LCD Enable Bit" indicates REG[0Dh] Bit 0 (LCD Enable).

2) "SUSPEND# Bit" indicates the SH7709A Port E register Bit 7 (in the CARD-E09A, assigned to control of SUSPEND#). The output of this port is connected internally to the CARD-E09A to the SUSPEND# pin of the SED1355. SED1355 REG[1Ah] Bit 0 (Software SUSPEND Mode) is not used.

3) For the FPVCCON on timing setting, see Section 2.3.3, "STARTUP.DAT settings."

A summary of the power sequence is now described. In the system power on/off sequence, NKLOADS.BIN (part of the loader), in the suspend/resume sequence, Windows CE HAL, respectively sets the SED1355 and SH7709A registers based on the STARTUP.DAT settings. The user simply has to make settings in STARTUP.DAT, and the following power sequence requirements can be met. Read this in conjunction with Section 2.3.3, "STARTUP.DAT settings."

#### <<\$TEP1>>

Power on sequence preparations are made.

#### For the sequence after system power on

After a system power on, NKLOADS.BIN (part of the loader) makes the initial settings based on the settings in STARTUP.DAT.

- 1) The SH7709A Port E register Bit 2 (assigned to SED1355 reference clock signal switching control in CARD-E09A) is set, and a check made of whether the internal clock mode or external clock input mode is selected.

- 2) SED1355 registers are set.

- 3) First SED1355 REG[23h] Bit 7 (Display FIFO Disable) is set to 1, (display inhibit mode), and next SED1355 REG[0Dh] Bit 0 (LCD Enable) is set to 1 for the LCD power on sequence.

#### For a resume

Previously, before the suspend, the settings in 1) and 2) above have been carried out, and the display inhibit mode setting completed. At that time, to speed up the suspend/resume display power on sequence, the display area is set to a minimum. The setting size is as follows. In this state, NKLOADS.BIN carries out the next step, A).

- HDP (horizontal display period) = 8 pixels

- HNDP (horizontal non-display period) = 32 pixels

- VDP (vertical display period) = 1 line

- VNDP (vertical non-display period) = 1 line

A) Windows CE HAL sets the SUSPEND# Bit to 1 (Disable).

#### <<STEP2>>

This is the power on sequence.

#### Sequence after a system power on

- 4) The SH7709A Port D register Bit 1 (assigned to FPVCCON control in CARD-E09A) is set, and FPVCCON is turned on. The on timing "T7" can be adjusted by a STARTUP.DAT setting.

- 5) After time T5, LINE, DOTCLK, MOD, and FPDAT[0..15] are active, and further after time T6, FRAME and FPVEEON are active. (Since FRAME operation timing is delayed by time T6 with respect to other signals, in order to prevent a broken-up display when the vertical sync cannot be obtained, the display inhibit mode is set.)

- 6) After 128 Frames (T6) from 3), the display inhibit mode is ended.

The following is an example of the calculation of T5, T6, and T7.

For settings of DOTCLK = 25.175 MHz, HDP = 640 pixels, HNDP = 160 pixels, VDP = 480 lines, VNDP = 45 lines, then T5, T6, and T7 are obtained as follows.

- $T5 = 1 (Frame) + 8 (Dotclk) = 1 \times ((HDP + HNDP) \times (VDP + VNDP) + 8) \times (1 / 25.175 MHz)$ = ((640 + 160) × (480 + 45) + 8) × (1/25.175 MHz)

- = 16.683 ms Max.

- $T6 = 128 \text{ (Frame)} = 128 \times (\text{HDP} + \text{HNDP}) \times (\text{VDP} + \text{VNDP}) \times (1/25.175 \text{ MHz})$  $= 128 \times (640 + 160) \times (480 + 45) \times (1/25.175 \text{ MHz})$

$$= 2.135$$

s Min.

- T7 = 127 (Frame) Max. =  $127 \times (HDP + HNDP) \times (VDP + VNDP) \times (1/25.175 \text{ MHz})$ =  $127 \times (640 + 160) \times (480 + 45) \times (1/25.175 \text{ MHz})$

- = 2.118 s Max. (for minimum setting, 0 Frame = 0 ns Min.)

#### Note:

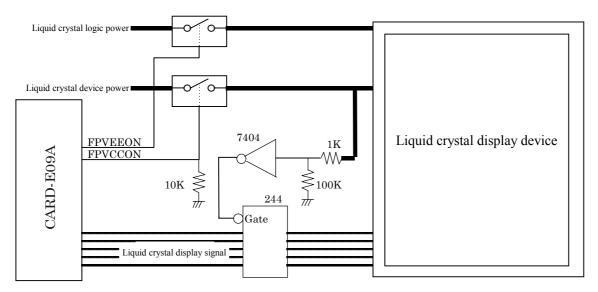

When the connected LCD panel has a specified time from logic power on until the signal lines are driven not exceeding "T5 + T6", a buffer IC must be inserted in all signal lines, and the power on sequence controlled. See Section 2.3.4, "Design Notes."

#### For a resume

B) FPVCCON is turned on. T7 = 0 Frame fixed.

- C) After time T5, LINE, DOTCLK, MOD, FPDAT[0..15] are active, and further after time T6, FRAME and FPVEEON are active.

- D) After 128 Frames (T6) from A), based on STARTUP.DAT, the proper display size is set, after which the display inhibit mode is ended.

The following is an example of the calculation of T5, T6, and T7 when DOTCLK = 25.175 MHz The display size is the minimum setting (HDP = 8 pixels, HNDP = 32 pixels, VDP = 1 line, VNDP = 1 line).

- $T5 = 1 (Frame) + 8 (Dotclk) = 1 \times ((HDP + HNDP) \times (VDP + VNDP) + 8) \times (1 / 25.175 MHz)$ = ((8 + 32) × (1 + 1) + 8) × (1/25.175 MHz)

- = 3.495 µs Max.

- $T6 = 128 \text{ (Frame)} = 128 \times (\text{HDP} + \text{HNDP}) \times (\text{VDP} + \text{VNDP}) \times (1/25.175 \text{ MHz})$

- $= 128 \times (8 + 32) \times (1 + 1) \times (1/25.175 \text{ MHz})$

- = 406.752 µs Min.

T7 = 0 s Min. (fixed)

#### <STEP3>

This is the display mode. When ending the display mode, the preparations must be made in advance.

#### Sequence before a system power off

- 7) After setting the display inhibit mode, to speed up the power off sequence, the display size is set to the minimum. The display size is as follows.

- HDP (horizontal display period) = 8 pixels

- HNDP (horizontal non-display period) = 32 pixels = 1 line

- VDP (vertical display period)

- VNDP (vertical non-display period) = 1 line

8) SED1355 REG[0Dh] Bit 0 (LCD Enable) is set to 0, and the LCD is set to the power off sequence.

#### Sequence before a suspend

Read this in combination with Section 9.3, "LCD Power Off Sequence" in the "CARD-E09A Windows CE Development Kit Instruction Manual" supplied with the CARD-E09A Windows CE Development Kit.

E) Same as 7). F) Windows CE HAL sets SUSPEND# Bit to 0 (Enable).

#### <STEP 4>

This is the power off sequence.

#### For a system power off sequence

- 9) After time T1, FPVEEON goes off, after time T2, FRAME, and then after time T3, LINE, DOTCLK, MOD, and FPDAT[0..15] are inactive.

- 10) After time T4, FPVCCON goes off.

#### For a suspend

- G) Same as 9).

- H) Same as 10).

The following is an example of the calculation of T1, T2, T3, and T4 when DOTCLK = 25.175 MHz. The display size is the minimum setting

(HDP = 8 pixels, HNDP = 32 pixels, VDP = 1 line, VNDP = 1 line).

- T1 = 2 (Frame) + 8 (Dotclk) = 2 × ((HDP + HNDP) × (VDP + VNDP) + 8) × (1 / 25.175 MHz)  $= (2 \times (8 + 32) \times (1 + 1) + 8) \times (1/25.175 \text{ MHz})$

- $= 6.673 \,\mu s \,Max.$

- T2 = 1 (Frame) =  $1 \times (HDP + HNDP) \times (VDP + VNDP) \times (1/25.175 \text{ MHz})$

- $= (8 + 32) \times (1 + 1) \times (1/25.175 \text{ MHz})$

- $= 3.177 \,\mu s$  Max.

- T3 = 128 (Frame) =  $128 \times (HDP + HNDP) \times (VDP + VNDP) \times (1/25.175 \text{ MHz})$

- $= 128 \times (8 + 32) \times (1 + 1) \times (1/25.175 \text{ MHz})$

- $= 406.752 \,\mu s$  Min.

- T4 = 10 ms Min. (No dependency on DOTCLK)

The specification of time T4 is given in Section 7.4, "Power Sequence" of the "SED1355F0A Technical Manual" as 130 Frames minimum, but in CARD-E09A, to improve the suspend/resume and power off sequence response, HDP/HNDP, and VDP/VNDP are minimized, and it is fixed at 10 ms minimum. This value is generated using the SH7709A internal timer function, and therefore in the external clock input mode does not depend on the external clock source or DOTCLK frequency. However, with a very low frequency external clock source, if 130 Frames exceeds 10 ms, it is necessary to change the STARTUP.DAT settings, and specify a larger time. For the method of changing the specified time, see Section 2.3.3, "STARTUP.DAT Settings." The reference criterion is as follows.

T4 = 130 (Frames) = 130 × (HDP + HNDP) × (VDP + VNDP) × (1/DOTCLK) < 10 ms HDP = 8, HNDP = 32, VDP = 1, VNDP = 1

If the above relation cannot be satisfied, then the setting for time T4 must be changed in STARTUP.DAT.

As described above, the LCD panel power sequence can be controlled by FPVCCON and FPVEEON. Also, the signal line power on timing is determined by the HDP, HNDP, VDP, VNDP, and DOTCLK as set in the SED1355 registers.

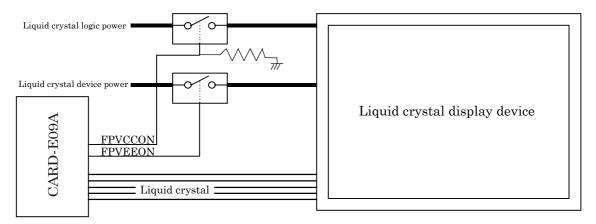

Fig. 2-2 shows an example of connections. In this example of connections, signals for the liquid crystal display are directly connected between the CARD-E09A and the liquid crystal display device, but depending on the LCD panel, the DC characteristics of the signal lines may not match those of the CARD-E09A, or there may be strict requirements for the power on/off sequence. In such cases, a buffer IC must be inserted, or other measures taken so that the LCD panel specification is met.

Fig. 2-2 Example connections

## 2.3.2. Panel Parameter Setup Method

Note the following points when setting SED1355 registers. Checking the display of the parameters which have been set can be done with the quick debugger supplied with the "CARD-E09A evaluation kit (SCE88J0X01)." For directions for using the quick debugger, see Chapter 12, "Quick Debugger" in the "CARD-E09A Windows CE Development Kit Instruction Manual" supplied with the CARD-E09A Windows CE Development Kit.

The parameters checked here are reflected in STARTUP.DAT. Read this in combination with the "SED1355F<sub>0A</sub> Technical Manual."

#### 2.3.2.1. SED1355 Register Settings

The registers which require setting are REG[01h] to REG[23h]. Except in special cases, such as direct setting from a look-up table (LUT), other registers do not require setting in STARTUP.DAT.

#### Fixed setting parameters

Registers with values have to set according to the CARD-E09A hardware specification are described below. When making settings in STARTUP.DAT, always use this setting.

| Index | Bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

|-------|------|------|------|------|------|------|------|------|

| 01h   | N/A  | 0    | 1    | 1    | N/A  | 0    | N/A  | 0    |

| 1Ah   | R/O  | N/A  | N/A  | N/A  | 0    | 0    | 1    | 0    |

| 22h   | Rsv  | 0    | 1    | 0    | 0    | 1    | Rsv  | rsv  |

| 23h   | Any  | 0    | 0    | Any  | Any  | Any  | Any  | Any  |

#### **Table 2-7 Preset register values**

N/A: Not applicable (Set to 0 in STARTUP.DAT.)

Rsv: Reserved (Set to 0 in STARTUP.DAT.)

Any: Set to any value. (See Table 2-8.)

#### **Basic settings**

Set registers shown in Table 2-8 so that they meet with the LCD panel specification. When checking the settings, read this in combination with Chapter 8, "Registers" and the timing charts for each LCD panel shown in Section 7.5, "Display Interface" in the "SED1355F0A Technical Manual."

**EPSON**

| Index      | Name                                            | Note                                                                                                                                                                                                               |

|------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 02h        | Panel type setting                              | -                                                                                                                                                                                                                  |

| 03h        | MOD rate setting                                | This is significant for a passive panel.<br>Default "00h":<br>Toggle for each frame<br>Values other than "00h":<br>Specify line number to toggle                                                                   |

| 04h        | Horizontal display width<br>(HDP) setting       | -                                                                                                                                                                                                                  |

| 05h        | Horizontal non-display period<br>(HNDP) setting | Set larger than "REG[06h] + REG[07h]".                                                                                                                                                                             |

| 06h        | Line start position setting                     | Specify the delay from the start of HNDP until a rising edge or a falling edge where LINE goes active (included in HNDP).                                                                                          |

| 07h        | LINE polarity/pulse width setting               | The pulse width (included in HNDP) is<br>automatically generated in the case of a passive<br>panel, and thus has no effect.                                                                                        |

| 08h, 09h   | Vertical display period (VDP) setting           | -                                                                                                                                                                                                                  |

| 0Ah        | Vertical non-display period<br>(VNDP) setting   | Set larger than "REG[0Bh] + REG[0Ch]".                                                                                                                                                                             |

| 0Bh        | FRAME start position setting                    | Specify the delay from the start of VNDP until a rising edge or a falling edge where FRAME goes active (included in VNDP). This is automatically generated in the case of a passive panel, and thus has no effect. |

| 0Ch        | FRAME polarity /pulse width setting             | The pulse width (included in VNDP) is<br>automatically generated in the case of a passive<br>panel, and thus has no effect.                                                                                        |

| 0Dh        | Display mode setting                            | #1)                                                                                                                                                                                                                |

| 0Eh to 12h | Screen 1 setting                                | #2) When the screen is not divided, the settings are: [0Eh]=FFh, [0Fh]=03h, [10h] to [12h]=00h.                                                                                                                    |

| 13h to 15h | Screen 2 setting                                | #2) When screen 2 is not used, set to all 00h (in the quick debugger set to 08h to drive screen 2).                                                                                                                |

| 16h, 17h   | Memory address offset setting                   | #2) #3)                                                                                                                                                                                                            |

| 18h        | Panning setting                                 | When the panning function is not used, set to 00h.                                                                                                                                                                 |

| 19h        | Dot clock signal setting                        | #4)                                                                                                                                                                                                                |

| 1Bh        | Half-frame buffer setting                       | When using dual panel, set to Enable.                                                                                                                                                                              |

| 23h        | Display FIFO setting                            | <ul> <li>#5) Normally set to 00h.</li> <li>With MCLK=PCLK (see #4) in following cases, set to 1Bh</li> <li>- for 16/15 bpp setting</li> <li>- for 16/8 bpp setting in portrait mode</li> </ul>                     |

Table 2-8 Registers which have to be set

- #1) For the hardware portrait mode (Bit 7) see Section 2.3.2.2. When operating with an OS created using Epson's "CARD-E09A Windows CE Development Kit," there are restrictions on the bpp selection (bits 4, 3, 2). The device driver only supports 8 bpp and 16 bpp modes. If another mode is set, the display quality under Windows CE cannot be guaranteed. For the CRT/LCD simultaneous display setting (bits 6, 5), see Section 2.3.2.3. For details of setting the CRT Enable (Bit 1) and LCD Enable (Bit 0) in STARTUP.DAT, see Section 2.3.3.

- #2) For details, see Chapter 10, "Display Configuration" of the "SED1355F0A Technical Manual." Note that the Windows CE device driver does not support a two-screen drive. Again, in the hardware portrait mode, the settings of REG[10h] to REG[15h] are different. See Section 2.3.2.2.

- #3) Table 2-9 illustrates example settings of the memory address offset. For hardware portrait mode see Section 2.3.2.2. The settings are different. Note that in the quick debugger LCD command, setting and entering HDP (REG[04h]), automatically displays the settings of REG[16h] and [17h].

| HDP        | Offset Address                | 16/15BPP | 8BPP | 4BPP | 2BPP | 1BPP |

|------------|-------------------------------|----------|------|------|------|------|

|            | Number of words of data       | 640      | 320  | 160  | 80   | 40   |

| 640 pixels | required for one line display |          |      |      |      |      |

|            | REG[16h] setting value        | 80h      | 40h  | A0h  | 50h  | 28h  |

|            | REG[17h] setting value        | 02h      | 01h  | 00h  | 00h  | 00h  |

|            | Number of words of data       | 320      | 160  | 80   | 40   | 20   |

| 320 pixels | required for one line display |          |      |      |      |      |

|            | REG[16h] setting value        | 40h      | A0h  | 50h  | 28h  | 14h  |

|            | REG[17h] setting value        | 01h      | 00h  | 00h  | 00h  | 00h  |

Table 2-9 Example settings of memory address offset

Note:

The number of pixels that can be represented by 1 byte is 1/2 pixel (2 bytes per 1 pixel) for 16/15 bpp, 1 pixel for 8 bpp, 2 pixels for 4 bpp, 4 pixels for 2 bpp, and 8 pixels for 1 bpp.

#4) In this register, the frequency of MCLK (memory clock) and PCLK (pixel clock) is set based on the source frequency (CKIO or external clock input source). MCLK is the video memory (EDO-RAM) reference clock signal. To minimize the current consumption during EDO-RAM access, make the setting (bit 2 = 0) so that MCLK is equal to the source frequency.

PCLK is a once-per-pixel display reference clock signal. It is not connected to the CARD-E09A interface internally. The relation between DOTCLK and PCLK is shown in Table 2-10.

Table 2-11 shows restrictions when setting PCLK. Read this in combination with Section 2.3.1.1.2, "External Clock Input Mode."

| LCD panel types                                                         | DOTCLK |

|-------------------------------------------------------------------------|--------|

| 4-bit single monochrome passive<br>(bus configuration: $4 \times 1$ )   | PCLK/4 |

| 8-bit single monochrome passive (bus configuration: $8 \times 1$ )      | PCLK/8 |

| 4-bit single color passive<br>(bus configuration: $4 \times 1$ )        | PCLK   |

| 8-bit single color passive type 1<br>(bus configuration: $8 \times 1$ ) | PCLK/4 |

| 8-bit single color passive type 2<br>(bus configuration: $8 \times 1$ ) | PCLK/2 |

| 16-bit single color passive<br>(bus configuration: $16 \times 1$ )      | PCLK/5 |

| 8-bit dual monochrome passive (bus configuration: $4 \times 2$ )        | PCLK/4 |

| 8-bit dual color passive<br>(bus configuration: $4 \times 2$ )          | PCLK   |

| 16-bit dual color passive<br>(bus configuration: $8 \times 2$ )         | PCLK/2 |

| TFT color                                                               | PCLK   |

#### Table 2-10 Relation between DOTCLK and PCLK

By setting SED1355 REG[02h] (panel type setting), the relation between DOTCLK and PCLK can be arbitrarily defined.

| Ink | Display type                                                                                                                                                                                                                                                                                |          | Maximun | n PCLK that | can be set |        |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------|-------------|------------|--------|

|     |                                                                                                                                                                                                                                                                                             | 16/15BPP | 8BPP    | 4BPP        | 2BPP       | 1BPP   |

|     | <ul> <li>Single Panel</li> <li>CRT</li> <li>Mono/Color Dual Passive Panel<br/>(Half Frame Buffer = Disable)</li> <li>CRT &amp; Single Panel simultaneous<br/>display</li> <li>CRT &amp; Mono/Color Dual Passive<br/>Panel simultaneous display<br/>(Half Frame Buffer = Disable)</li> </ul> |          |         | MCLK        |            |        |

| OFF | <ul> <li>Mono Dual Passive Panel<br/>(Half Frame Buffer = Enable)</li> <li>CRT &amp; Mono Dual Passive Panel<br/>simultaneous display<br/>(Half Frame Buffer = Enable)</li> </ul>                                                                                                           |          | MCI     | LK/2        |            | MCLK/3 |

|     | <ul> <li>Color Dual Passive Panel<br/>(Half Frame Buffer = Enable)</li> <li>CRT &amp; Color Dual Passive Panel<br/>simultaneous display<br/>(Half Frame Buffer = Enable)</li> </ul>                                                                                                         |          | MCI     | LK/2        |            | MCLK/3 |

|     | <ul> <li>Single Panel</li> <li>CRT</li> <li>Mono/Color Dual Passive Panel<br/>(Half Frame Buffer = Disable)</li> <li>CRT &amp; Single Panel simultaneous<br/>display</li> <li>CRT &amp; Mono/Color Dual<br/>Passive Panel simultaneous display<br/>(Half Frame Buffer = Disable)</li> </ul> | МС       | LK      |             | MCLK/2     |        |

| ON  | <ul> <li>Mono Dual Passive Panel<br/>(Half Frame Buffer = Enable)</li> <li>CRT &amp; Mono Dual Passive Panel<br/>simultaneous display<br/>(Half Frame Buffer = Enable)</li> </ul>                                                                                                           |          | MCLK/2  |             | MC         | LK/3   |

|     | <ul> <li>Color Dual Passive Panel<br/>(Half Frame Buffer = Enable)</li> <li>CRT &amp; Color Dual Passive<br/>Panel simultaneous display<br/>(Half Frame Buffer = Enable)</li> </ul>                                                                                                         | MCI      | .K/2    |             | MCLK/3     |        |

Table 2-11 Restrictions when setting PCLK

Note:

This table was created by extracting the items for which Nrc=4 from Table 14-1 "Maximum PCLK frequency with EDO-DRAM" in Chapter 14, "Clocking" of the "SED1355F0A Technical Manual." The Epson Windows CE device driver always has "Ink = OFF" set. When using the ink function, it is necessary to set REG[27h] to [30h].

#5) For details of setting display FIFO disable (Bit 7) in STARTUP.DAT, see Section 2.3.3, "STARTUP.DAT Settings."

#### 2.3.2.2. Hardware Portrait Mode

By setting REG[0Dh] Bit 7 to 1 the hardware portrait mode can be enabled. The hardware portrait mode is a display mode in which the display image is rotated clockwise through 90 degrees in hardware. For details, see Chapter 13, "Hardware Portrait Mode" in the "SED1355F0A Technical Manual."

In hardware portrait mode, not only the setting of REG[0Dh] Bit 7, but also the memory address offset (REG[16h], [17h]), the screen 1 setting (REG[10h], [11h], [12h]), and the screen 2 setting (REG[13h], [14h], [15h]) must be changed. For the method of making the setting in STARTUP.DAT, see Section 2.3.3. "STARTUP.DAT Settings." Note that the Epson Windows CE video driver does not support the hardware portrait mode on screen 2. This mode is available in 16 bpp and 8 bpp modes. It is not supported in hardware for 4 bpp /2 bpp /1 bpp. Note also that the cursor and ink images are not rotated.

#### Setting for memory address offset (REG[16h], [17h])

• For 16 bpp: 1024 words (fixed)

• For 8 bpp: 512 words (fixed)

#### Setting for display start address (REG[10h], [11h], [12h], [13h], [14h], [15h])

- For 16 bpp: 1024 W (words)

- For 8 bpp: (1024 W)/2 (words)

In the above, W is the number of lines on the screen after the portrait setting. For example, when a screen 640 pixels  $\times$  480 lines is rotated, W = 640. Note that in hardware portrait mode the processing size maximum value is fixed at 1024 pixels  $\times$  1024 lines. It is not possible to make a setting which exceeds this.

An example of the display address setting in hardware portrait mode is shown in Table 2-12. Note that in the quick debugger LCD command, setting HDP (REG[04h]) and setting REG[0Dh] Bit 7 to 1, automatically displays the settings of REG[10h] to [17h].

|                               | ipic of display address se | 8     |      |

|-------------------------------|----------------------------|-------|------|

| Display size                  | Register(s)                | 16BPP | 8BPP |

| 640 pixels $\times$ 480 lines | REG [10h] or [13h]         | 80h   | C0h  |

|                               | REG [11h] or [14h]         | 01h   | 00h  |

|                               | REG [12h] or [15h]         | 00h   | 00h  |

|                               | REG [16h]                  | 00h   | 00h  |

|                               | REG [17h]                  | 04h   | 02h  |

| 320 pixels $\times$ 240 lines | REG [10h] or [13h]         | C0h   | 16h  |

|                               | REG [11h] or [14h]         | 02h   | 00h  |

|                               | REG [12h] or [15h]         | 00h   | 00h  |

|                               | REG [16h]                  | 00h   | 00h  |

|                               | REG [17h]                  | 04h   | 02h  |

| Table 2-12 Example | of display addres   | s setting in hardwa | are portrait mode |

|--------------------|---------------------|---------------------|-------------------|

| Tuble - 12 Example | or anoping addition | s second in man ave | ne por trait moue |

#### 2.3.2.3. Frame Rate and Display Performance

To realize optimum display performance, the frame rate must be set close to the typical value for the LCD panel. Generally, if the LCD panel is operated at a lower frame rate, the panel may flicker, which is a factor to be considered. The frame rate can be calculated as follows. For details, see Section 14.2, "Frame Rate Calculation" in the "SED1355F0A Technical Manual."

Frame rate = DOTCLK Max. / (HDP + HNDP) × (VDP + VNDP) Horizontal frequency = DOTCLK Max. / (HDP + HNDP)

- DOTCLK = PCLK, REG[19h] Bit[2:1]

- HDP =  $((\text{REG}[04h] \text{Bit}[6:0]) + 1) \times \text{8DOTCLK}$

- HNDP = ((REG[05h] Bit[4:0]) + 1) × 8DOTCLK

- VDP = (REG[09h] Bit[1:0]) & (REG[08h] Bit[7:0]) + 1

- VNDP = (REG[0Ah] Bit[5:0]) + 1

Table 2-13 shows example calculations of the frame rate. In the CARD-E09A, the following specification of video memory is used. This table shows parts of the specification extracted from Table 14-3 "Example Frame Rates with Ink Disabled" in the "SED1355F0A Technical Manual."

- 60ns EDO-RAM

- NRC = 4, NRP = 1.5, NRCD = 2 (see detailed description of REG[22h])

| Display type                               | Resolution       | BPP     | Maximum<br>DOTCLK | Maximum<br>HNDP |       | m frame<br>[Hz] |

|--------------------------------------------|------------------|---------|-------------------|-----------------|-------|-----------------|

|                                            |                  |         | [MHz]             | [pixels]        | Panel | CRT             |

| Single Panel                               | $800 \times 600$ | 16      |                   | 56              | 65    | 55              |

| • CRT                                      |                  | 8/4/2/1 |                   | 32              | 66    |                 |

| Mono/Color Dual Passive Panel              | $640 \times 480$ | 16      |                   | 56              | 98    | 78              |

| (Half Frame Buffer = Disable)              |                  | 8/4/2/1 |                   | 32              | 101   |                 |

| CRT & Single Panel<br>simultaneous display | 640 × 240        | 16      |                   | 56              | 200   |                 |

| CRT & Mono/Color Dual                      |                  | 8/4/2/1 | 33                | 32              | 203   |                 |

| Passive Panel simultaneous<br>display      | 480 × 320        | 16      |                   | 56              | 196   |                 |

| (Half Frame Buffer = Disable)              |                  | 8/4/2/1 |                   | 32              | 200   |                 |

|                                            | $320 \times 240$ | 16      |                   | 56              | 380   | -               |

|                                            |                  | 8/4/2/1 |                   | 32              | 388   |                 |

| Color Dual Passive Panel                   | $800 \times 600$ | 16      | 11                |                 | 43    |                 |

| (Half Frame Buffer = Enable)               |                  | 8/4/2/1 | 16.5              | 32              | 66    |                 |

| Mono Dual Passive Panel                    | $640 \times 480$ | 16      | 11                |                 | 68    |                 |

| (Half Frame Buffer = Enable)               |                  | 8/4/2/1 | 16.5              |                 | 103   |                 |

Table 2-13 Frame rate calculation examples (when MCLK = 33 MHz)

Note:

The example is in internal clock mode. When using external clock input mode:

- MCLK = external clock source

- Note that maximum DOTCLK = external clock source or a division thereof, and the maximum HNDP and maximum frame rate values are different with internal clock mode.

If a bandwidth calculation is required to optimize the display performance, see Section 14.3, "Bandwidth Calculation" in the "SED1355F0A Technical Manual."

#### 2.3.2.4. LCD and CRT Simultaneous Display

If the CRT and LCD panel used have overlapping frame rate rating ranges, then by setting the video parameters within the overlap range, and simultaneously setting REG[0Dh] Bit 1 (CRT Enable) and Bit 0 (LCD Enable), the CRT and LCD panel can be driven simultaneously.

Basically, when using a CRT display, the timing must meet the VESA (Video Electronics Standards Association) standard, but for a normal multiscan CRT, the frame rate synchronization can be achieved over the range 50 Hz to 130 Hz, so check the type of CRT being used.

Most LCD panels can be adjusted within the CRT synchronization frequency (50 Hz to 130 Hz) range, and therefore to use a simultaneous CRT and LCD panel display, first the parameters must be set so that the standard value of the frame rate for the LCD panel being considered for use is satisfied, and then a check made whether the values are within the rating range for the CRT being adopted. Table 2-14 shows standard VESA specifications.

| Resolution       | Frame rate | Horizontal | DOTCLK | Standard          |  |  |

|------------------|------------|------------|--------|-------------------|--|--|

|                  | [MHz]      | frequency  | [MHz]  |                   |  |  |

|                  |            | [KHz]      |        |                   |  |  |

| $640 \times 480$ | 60         | 31.5       | 25.175 | Industry Standard |  |  |

|                  | 72         | 37.9       | 31.500 | VESA Standard     |  |  |

|                  | 75         | 37.5       | 31.500 | VESA Standard     |  |  |

| $800 \times 600$ | 56         | 35.1       | 36.000 | VESA Standard     |  |  |

|                  | 60         | 37.9       | 40.000 | VESA Standard     |  |  |

|                  | 72         | 48.1       | 50.000 | VESA Standard     |  |  |

|                  | 75         | 46.9       | 49.500 | VESA Standard     |  |  |

**Table 2-14 Standard VESA specifications**

The CARD-E09A has a maximum specification for DOTCLK of 33.2 MHz, and therefore does not meet the standard for the 800 pixel  $\times$  600 line (SVGA) resolution, but as described above, if a multiscan CRT is used, a correct display may be able to be obtained.

#### 2.3.2.5. Notes on Connecting a Monochrome LCD Panel

By setting REG[02h], bit 2 to 0, a monochrome (grayscale) LCD panel can be connected. In monochrome mode, output to the LCD panel selects only the green elements of the LUT. When simultaneous display with a CRT is selected, a color image is displayed on the CRT.

In monochrome mode, the maximum number of gray levels is 16. Even if more than 4 bpp is set, the display still has only 16 levels. Therefore, 8 bpp or 15/16 bpp settings do not increase the gray levels, but when the hardware portrait mode is used, an 8 bpp or 16 bpp setting is required. This is because the hardware portrait mode only operates in the 8 bpp and 16 bpp modes.

When operating with an OS developed using the "CARD-E09A Windows CE Development Kit," note the following points. This is because the LUT settings are optimized to display the Windows CE screen on a monochrome LCD panel. For details, see the "CARD-E09A Windows CE Development Kit Instruction Manual."

- The STARTUP.DAT setting must always be 8 bpp. This is so that 16 grayscale levels are displayed using an 8 bpp LUT for color. For details of the STARTUP.DAT settings, see Section 2.3.3.

- In the case of simultaneous display with a CRT, the CRT shows the same monochrome image as the LCD panel. This is because the setting uses the red, green, and blue elements of the LUT superimposed.

- When displaying on a monochrome LCD panel, there is no procedure to be noted during the NK.BIN (in Windows CE) build. If the monochrome LCD setting and the 8 bpp setting are made in STARTUP.DAT, then an LUT for the monochrome LCD panel is automatically used for the display.

- This function is supported from "CARD-E09A Windows CE 2.11 development kit Ver. 1.05." Note that it is not supported in previous versions.

#### 2.3.3. STARTUP.DAT Settings

In this section, the SED1355 register settings determined in Section 2.3.2, "Panel Parameter Setup Method" are reflected in STARTUP.DAT. When the system is powered on, the Epson loader transfers the parameters written in STARTUP.DAT in sequence from the beginning of the file to the SED1355 registers. The sequence of the parameters is such as to take account of the power on/off sequence, and should not be changed.

The STARTUP.DAT file can be edited simply with a text editor.

Next a summary of the settings is given. The video parameters must be set at two places in the STARTUP.DAT file: key "1355" and key "1355PROPERTY". For details, see Section 13.1, "Startup Data Overview" in the "CARD-E09A Windows CE Development Kit Instruction Manual" supplied with the Windows CE Development Kit.

Table 2-15 shows the setting format for key "1355". Here the SED1355 internal register settings are specified. This should be checked with the sequence of steps in Section 2.3.1.2, "Power Sequence."

|           |           | bie 2-15 Setting for mat for key 1555                                                 |  |  |  |

|-----------|-----------|---------------------------------------------------------------------------------------|--|--|--|

| Index     | Data      | Comment                                                                               |  |  |  |

| ;FFFF0002 | 00        | In external clock input mode (see Section 2.3.1.1.2.), remove the                     |  |  |  |

|           |           | semicolon so that it is no longer a comment.                                          |  |  |  |

| B4000023  | 80        | REG[23h] setting. Set bit 7 (Display FIFO Disable) to 1, to set the                   |  |  |  |

|           |           | display inhibit mode.                                                                 |  |  |  |

| B4000001  | Any value | REG[01h] to REG[22h] settings. Set the parameters as                                  |  |  |  |

| ••••      |           | determined in Section 2.3.2.1, "SED1355 Register Settings."                           |  |  |  |

| B4000022  |           | Here, do not set REG[0Dh].                                                            |  |  |  |

|           |           |                                                                                       |  |  |  |

|           |           | <when hardware="" in="" mode="" portrait=""></when>                                   |  |  |  |

|           |           | • REG[10h] to [12h] or REG[13h] to [15h]                                              |  |  |  |

|           |           | For 16 bpp: 1024-W                                                                    |  |  |  |

|           |           | For 8 bpp: (1024-W)/2                                                                 |  |  |  |

|           |           | W = original screen width in pixels                                                   |  |  |  |

|           |           | • REG[16h], [17h]                                                                     |  |  |  |

|           |           | For 16 bpp: 1024 fixed                                                                |  |  |  |

|           |           | For 8 bpp: 512 fixed                                                                  |  |  |  |

|           |           | <when a="" ce="" connecting="" monochrome="" panel="" windows="" with=""></when>      |  |  |  |

|           |           | REG[16h], [17h]; 8 bpp setting                                                        |  |  |  |

| B400000D  | Any value | REG[0Dh] setting. If bit 0 (LCD Enable) is set, then the LCD                          |  |  |  |

|           |           | panel power on sequence starts.                                                       |  |  |  |

|           |           | bit1 (CRT Enable) bit0(LCD Enable)                                                    |  |  |  |

|           |           | 1 0 : CRT display                                                                     |  |  |  |

|           |           | 0 1 : LCD display                                                                     |  |  |  |

|           |           | 1 1 : CRT & LCD display                                                               |  |  |  |

|           |           | distant and decidence to                                                              |  |  |  |

|           |           | <in hardware="" mode="" portrait=""></in>                                             |  |  |  |

|           |           | bit7 (Hardware Portrait Mode Enable) = 1                                              |  |  |  |

|           |           | <when a="" ce="" connected="" is="" monochrome="" panel="" windows="" with=""></when> |  |  |  |

|           |           | 8BPP : bit4 = 0, bit3 = 1, bit2 = 1                                                   |  |  |  |

|           |           |                                                                                       |  |  |  |

Table 2-15 Setting format for key "1355"

| ;;;;FFFF0004 | Any value | When FPVCCON is turned on in the next step, the delay time<br>from setting "LCD Enable" until it goes on is set in units of<br>display frames. When the delay time setting is required, remove<br>the semicolons so that this is no longer commented out.<br>Example: If delay time = 128 Frames, set to "80h". |

|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ;;;;FFFF0005 | 00        | Removing the comment semicolons turns FPVCCON on. Use this in combination with the delay time setting.                                                                                                                                                                                                          |

| FFFF0001     | 00        | Clear screen.                                                                                                                                                                                                                                                                                                   |

| B4000023     | 00        | REG[23h] setting. Set bit 7 (Display FIFO Disable) to 0, and end the display inhibit mode.                                                                                                                                                                                                                      |

| FFFFFFF      | FFFFFFF   | End of initialization                                                                                                                                                                                                                                                                                           |

Table 2-16 shows the setting format for key "1355PROPERTY". Here the data referenced when Windows CE starts is specified.

| Column          | Comment                                                                                                                 |

|-----------------|-------------------------------------------------------------------------------------------------------------------------|

| Width, Height   | Specify screen size to be displayed.                                                                                    |

|                 | Width = REG[04h] setting value (HDP)                                                                                    |

|                 | Height = REG[08h], [09h] setting value (VDP)                                                                            |

|                 | <in hardware="" mode="" portrait=""></in>                                                                               |

|                 | Width and height must be interchanged.                                                                                  |

| bpp, Frame Rate | Specify the number of bits of display data in each pixel and the frame rate.<br>bpp = REG[0Dh], setting for bits 4 to 2 |

|                 | Frame Rate = setting calculated in Section 2.3.2.3 "Frame Rate and Display Performance"                                 |

|                 | <pre><when a="" ce="" connecting="" monochrome="" panel="" windows="" with=""><br/>BPP = 8</when></pre>                 |

| Wait Time for   | Specify the delay time T4 (units: ms) when moving to suspend mode, or                                                   |

| Suspend/Resume  | resuming. See Section 2.3.1.2, "Power Sequence."                                                                        |

|                 | • "FFFFh" (default): $T4 = 10 \text{ ms Min.}$                                                                          |

|                 | • In external clock input mode, if $T4 = 10$ ms Min. cannot be satisfied, a                                             |

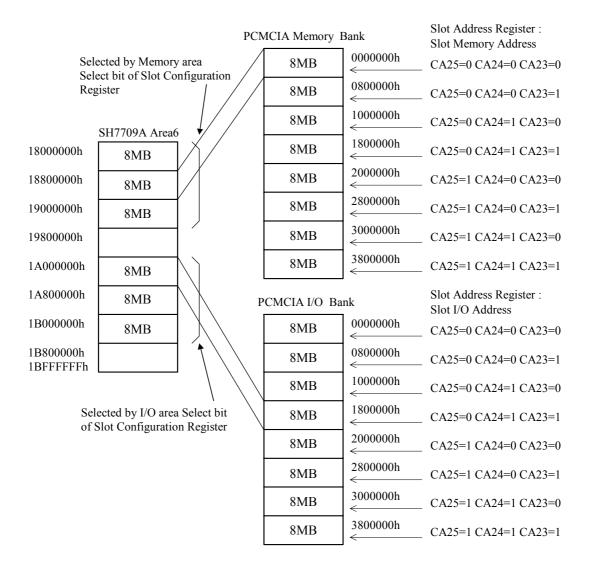

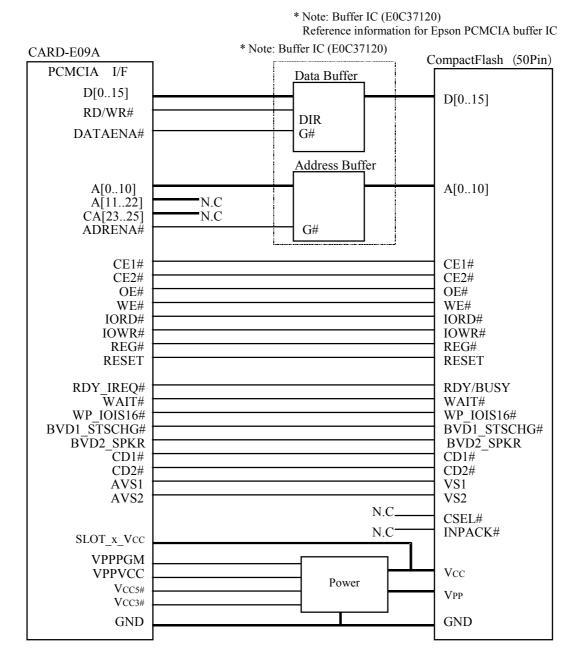

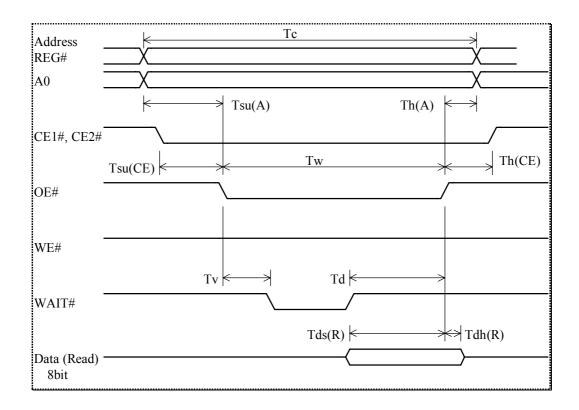

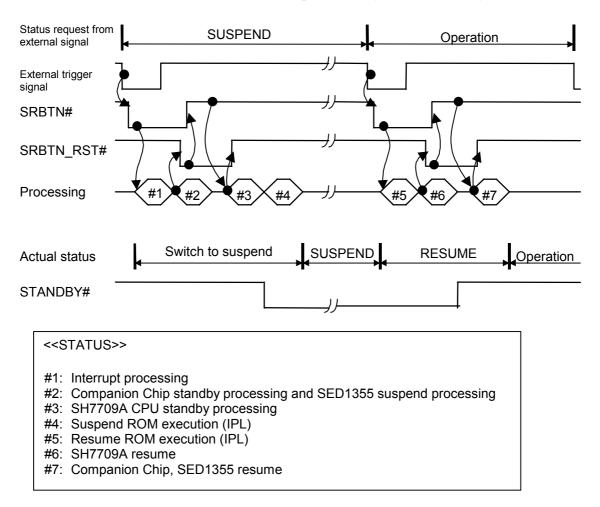

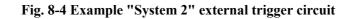

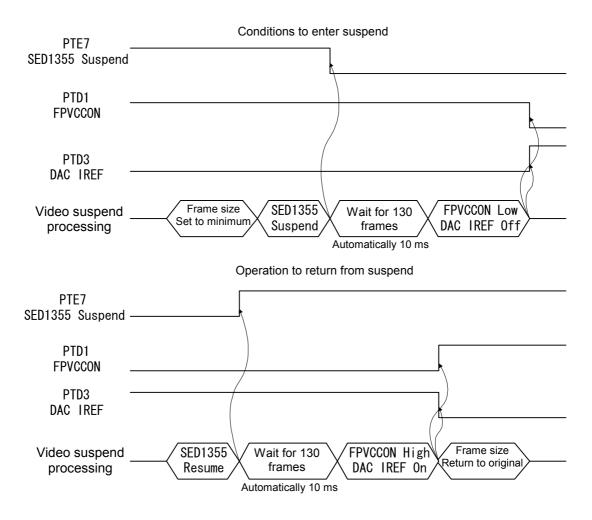

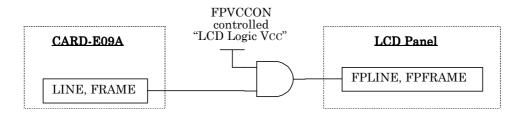

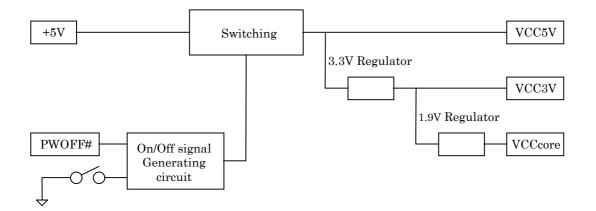

|                 | setting change is required. Set the time in units of 1 ms.                                                              |